# WESTERN DIGITAL

# PT 1482-01 (PSAT) Programmable Synchronous & Asynchronous Transmitter

#### FEATURES

- SYNCHRONOUS, ASYNCHRONOUS OR ISOCHRONOUS OPERATION

- DC TO 640K BITS/SEC, 1X CLOCK PT1482-01

- DC TO 100K BITS/SEC, 1X CLOCK PT1482

- PROGRAMMABLE MATCH (FILL) CHARACTER

- SELECTABLE 5,6,7, OR 8 BIT PER CHARACTER

- EVEN/ODD PARITY GENERATOR. PARITY IN-HIBIT

- PROGRAMMABLE CLOCK RATE 1X, 16X, 32X, OR 64X.

- AUTOMATIC START & STOP BIT GENERATION IN ASYNCHRONOUS & ISOCHRONOUS MODES

- PROGRAMMABLE 1 AND 2 STOP BITS, (1½ IN 5 LEVEL MODE)

- AUTOMATIC CHARACTER STATUS AND DE-LIMITING SIGNAL GENERATION

- THREE STATE OUTPUTS BUS STRUCTURE COMPATIBILITY

- DOUBLE BUFFERED

- TTL AND DTL COMPATIBLE INTERNAL ACTIVE PULL UP

- COMPATIBLE RECEIVER, PR1472.

#### GENERAL DESCRIPTION

The Western Digital PT1482 (PSAT) is a programmable transmitter that interfaces variable length parallel data to a serial data channel. The transmitter converts parallel characters into a serial data stream with a format compatible with all standard Synchronous, Asynchronous or Isoschronous data communications media.

Contiguous serial characters are transmitted in the Synchronous Mode with the automatic insertion of a programmable Fill (Idle) Character during the absence of parallel input data. Programming the Asynchronous Mode selects serial transmission with automatic insertion of Start and Stop Bits, Isoschronous mode selects transmission with automatic fill character insertion during the absence of parallel input data. Four internal registers and a multiplexer, in conjunction with Three-State Output Lines, provide full system versatility.

The PSAT is a TTL compatible device. The use of internal active pull-up devices and push-pull output drivers, provides direct compatibility with all forms of current sinking logic. Western Digital also offers a compatible Receiver, PR1472.

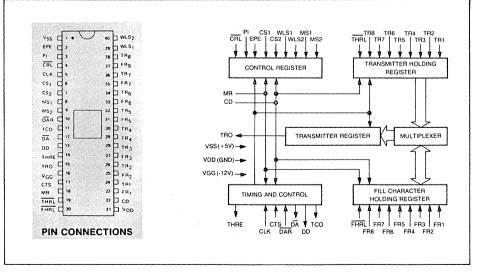

PT1482 BLOCK DIAGRAM

|   | -  |

|---|----|

|   | E  |

|   | С  |

|   | Ţ  |

|   | L  |

| K | 9  |

|   | N. |

|   | ÷. |

| PIN<br>NUMBER | I/O NAME                                           | SYMBOL                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|---------------|----------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 2           | V <sub>SS</sub> POWER SUPPLY<br>EVEN PARITY ENABLE | V <sub>ss</sub><br>EPE | + 5 Volt Supply<br>A low-level input voltage, V <sub>IL</sub> , applied to CD (pin<br>22) enables the EPE and PI Inputs.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 3             | PARITY INHIBIT                                     | PI                     | The Even Parity Enable Input and the Parity<br>Inhibit Input to the Control Register, in conjunc-<br>tion with the Control Register Load and Chip<br>Disable, select even, odd or no parity to be<br>generated by the Transmitter. A high-level input<br>voltage, $V_{\rm H}$ , applied to EPE selects even parity<br>and a low-level input voltage, $V_{\rm IL}$ , selects odd<br>parity if a low-level input voltage is applied to<br>Parity Inhibit and Chip Disable.                                                             |  |  |  |

|               |                                                    |                        | $\begin{array}{ccc} \textbf{PI} & \textbf{EPE} & \textbf{SELECTED PARITY COMMENTS} \\ \textbf{V}_{1L} & \textbf{V}_{1L} & \textbf{ODD} & \textbf{CD} = \textbf{V}_{1L} \\ \textbf{V}_{1L} & \textbf{V}_{1H} & \textbf{EVEN} & \textbf{CD} = \textbf{V}_{1L} \\ \textbf{V}_{1H} & \textbf{X} & \textbf{NONE} & \textbf{CD} = \textbf{V}_{1L} \end{array}$                                                                                                                                                                             |  |  |  |

|               |                                                    |                        | NOTE: IF CD = $V_{IH}$ , NO PROGRAMMING IS PERFORMED SINCE INPUTS ARE DISABLED.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|               |                                                    |                        | $X = either V_{IL} \text{ or } V_{IH}$ When programmed, the appropriate parity is generated following, and is contiguous with, the last data bit of a character, immediately preceding the stop element of asychronous and isochronous characters.                                                                                                                                                                                                                                                                                   |  |  |  |

|               |                                                    |                        | A high-level input voltage, V <sub>IH</sub> , applied to CD disables EPE, PI, and CRL.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 4             | CONTROL REGISTER                                   | CRL                    | A low-level input voltage, $V_{\text{IL}}$ applied to CD (pin 22) enables the CRL input.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|               |                                                    |                        | A low-level input voltage, $V_{IL}$ , applied to this<br>line enables DC Latches of the Control Register<br>and loads it with Control Bits (EPE, PI, CS <sub>1</sub> , CS <sub>2</sub> ,<br>MS <sub>1</sub> , MS <sub>2</sub> , WLS <sub>1</sub> , WLS <sub>2</sub> ). A high-level input<br>voltage, $V_{IH}$ , applied to this line disables the<br>Control Register. This line may be strobed or<br>hard-wired to a low-level input voltage, $V_{IL}$ . A<br>high-level input voltage, $V_{IH}$ , applied to CD,<br>disables CRL. |  |  |  |

| 5             | TRANSMITTER<br>REGISTER CLOCK                      | TRC                    | This is a fifty (50) percent duty cycle clock. The positive going edge of this Clock shifts data out of the Transmitter Register at a rate determined by the Control Bits $CS_1$ and $CS_2$ , and provides the basic time reference for all device functions.                                                                                                                                                                                                                                                                        |  |  |  |

| 6-7           | CLOCK RATE SELECT                                  | CS1-CS2                | A low-level input voltage, $V_{1L}$ , applied to CD<br>enables the CS <sub>1</sub> and CS <sub>2</sub> inputs. These two<br>lines select the internal clock rate divider ratio<br>to produce the transmitter bit rate defined by<br>the Truth Table below:<br>CS <sub>2</sub> CS <sub>1</sub> SELECTED CLOCK INPUT RATE<br>$V_{1L}$ $V_{1L}$ 1X BIT RATE<br>$V_{1L}$ $V_{1H}$ 16X BIT RATE                                                                                                                                           |  |  |  |

|               |                                                    |                        | V <sub>IH</sub> V <sub>IL</sub> 32X BIT RATE<br>V <sub>IH</sub> V <sub>IH</sub> 64X BIT RATE                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PIN<br>NUMBER | I/O NAME                          | SYMBOL  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                   |         | A high-level input voltage, $V_{\rm IH},$ applied to CD disables $CS_1$ and $CS_2.$                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8-9           | MODE SELECT                       | MS₁-MS₂ | These lines may be strobed or hard-wired to the appropriate input voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                                   |         | A low-level input voltage, $V_{IL}$ , applied to CD (pin 22) enables the $MS_1$ and $MS_2$ inputs. These lines select the transmitter operating mode.                                                                                                                                                                                                                                                                                                                                                                                           |

|               |                                   |         | MS <sub>2</sub> MS <sub>1</sub> MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                                   |         | $ \begin{array}{ll} V_{IL} & V_{IL} & ASYNCHRONOUS - ONE STOP BIT \\ V_{IL}^* & V_{IH}^*ASYNCHRONOUS - TWO STOP BITS \\ V_{IH} & V_{IL} & SYNCHRONOUS \\ V_{IH} & V_{IH} & ISOCHRONOUS \end{array} $                                                                                                                                                                                                                                                                                                                                            |

|               |                                   |         | *Selects 1.5 stop bits for 5-level codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                                   |         | A high-level input voltage, V <sub>IH</sub> , applied to CD<br>disables MS₁ and MS₂.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10            | DATA NOT AVAILABLE                | DAB     | A low-level input voltage, V <sub>IL</sub> , applied to CD (pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10            | RESET                             | - DAIL  | 22) enables the DAR input. A low-level input<br>voltage, V <sub>IL</sub> , applied to this line resets the Data<br>Not Available Flag. A high-level Input, V <sub>IH</sub> ,<br>applied to CD disables DAR. This input is not<br>used during asynchronous operation.                                                                                                                                                                                                                                                                            |

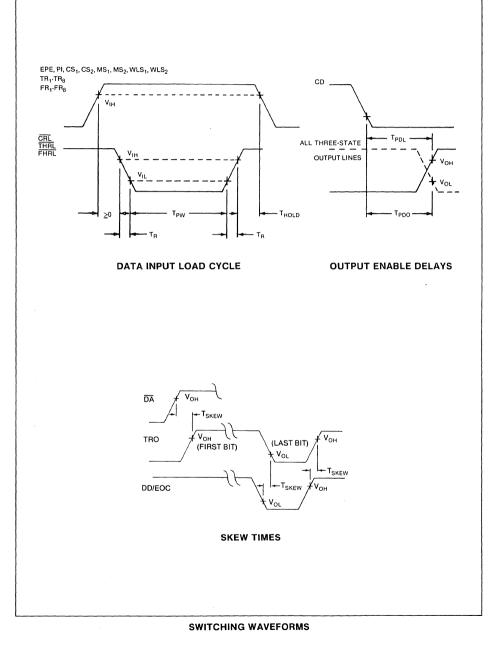

| 11            | TRANSMITTER<br>CLOCK OUTPUT       | тсо     | This output is a clock at the transmitted bit rate.<br>The negative going edge of this clock corre-<br>sponds to the center of each transmitted data<br>bit. The positive going edge corresponds to the<br>start of each data bit transmission. All wave-<br>forms in this specification are referenced to<br>TCO.                                                                                                                                                                                                                              |

| 12            | DATA NOT AVAILABLE<br>FLAG        | DA      | A low-level input voltage, $V_{IL}$ , applied to CD (pin 22) enables the $\overline{DA}$ input. A high-level output voltage, $V_{OH}$ , on this line indicates that a Fill-Character has been transmitted, since a character was not loaded into the Transmitter Holding Register by the center of the last bit of a Synchronous Character or the center of the Stop Element of an Isochronous character. A high-level input voltage, $V_{IH}$ , applied to CD disables $\overline{DA}$ . This input is not used during asynchronous operation. |

| 13            | DATA DELIMIT/<br>END OF CHARACTER | DD/EOC  | During asynchronous operation, a high-level output voltage, $V_{OH}$ , indicates data is being transmitted. A low-level output voltage, $V_{OL}$ , indicates that a Start or Stop Element is being transmitted.                                                                                                                                                                                                                                                                                                                                 |

|               |                                   |         | A low-level output voltage during synchronous<br>operation indicates that the last bit of a charac-<br>ter is being transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                |

SUCH-OZ 1

ſ

| PIN<br>NUMBER | I/O NAME                                   | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|--------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14            | TRANSMITTER<br>HOLDING REGISTER<br>EMPTY   | THRE            | A low-level input voltage applied to CD (pin 22) enables the THRE input. A high-level output voltage, $V_{OH}$ , on this line indicates the Transmitter Holding Register is empty and has transferred its contents to the Transmitter Register and may be loaded with a new character. This line goes to a low-level output voltage, $V_{OL}$ , when THRL goes to a low-level input voltage, $V_{IL}$ . A high-level input voltage, $V_{IH}$ , applied to CD disables THRE.                                                            |

| 15            | TRANSMITTER<br>REGISTER OUTPUT             | TRO             | The contents of the Transmitter Holding<br>Register are serially shifted out as an NRZ<br>waveform on this line provided that a character<br>was loaded into the Transmitter Holding Regis-<br>ter prior to DA Flag (in Synchronous or Iso-<br>chronous Modes). If a character was not loaded<br>prior to a DA Flag, the contents of the Fill-<br>Character Register are transmitted as the next<br>character.                                                                                                                         |

| 16            | V <sub>GG</sub> POWER SUPPLY               | V <sub>GG</sub> | – 12 Volts Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17            | CLEAR-TO-SEND                              | CTS             | The Clear-To-Send Control initiates or disables transmission as a function of the state of this line. A high-level input voltage, $V_{\rm IH}$ , initiates serial data transmission provided a character has been loaded into the Transmitter Holding Register. A low-level input voltage, $V_{\rm IL}$ , applied to this line during transmission allows completion of that character only, after which the output will continue to mark until a high-level input voltage is applied.                                                 |

| 18            | MASTER RESET                               | MR              | The rising edge of a high-level input voltage, $V_{\rm IH}$ , applied to this line resets timing and control logic to an idle state, sets THRE, the contents of the Fill-Character Holding Register, and TRO to a high-level output voltage, $V_{\rm OH}$ .                                                                                                                                                                                                                                                                            |

| 19            | TRANSMITTER<br>HOLDING REGISTER<br>LOAD    | THRL            | A low-level input voltage, V <sub>IL</sub> , applied to CD (pin 22) enables the THRL input. A low-level input voltage, V <sub>IL</sub> , applied to this line enables DC Latches of the Transmitter Holding Register and loads it with the Transmitter Holding Register data and forces THRE to a low-level output voltage, V <sub>OL</sub> . A high-level input voltage, V <sub>IH</sub> , applied to this line disables the Transmitter Holding Register. A high-level input voltage, V <sub>IH</sub> , applied to CD disables THRL. |

| 20            | FILL-CHARACTER<br>HOLDING REGISTER<br>LOAD | FHRL            | A low-level input voltage, V <sub>IL</sub> , applied to CD (pin 22) enables the FHRL input. A low-level input voltage, V <sub>IL</sub> , applied to this line enables DC Latches of the Fill-Character Holding Register and loads it with the Fill-Character Register data $FR_{1}$ - $FR_{8}$ . A high-level input voltage, V <sub>IH</sub> , applied to this line disables the FHRL Register. This line may be strobed or hard-wired to a low-                                                                                       |

| PIN<br>NUMBER                        | I/O NAME                                          | SYMBOL                           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S<br>E<br>C |

|--------------------------------------|---------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                                      |                                                   |                                  | level input voltage, V <sub>IL</sub> . This input is not used during asynchronous operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I<br>O<br>N |

|                                      |                                                   |                                  | A high-level input voltage, V <sub>IH</sub> , applied to CD disables FHRL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>, 1</u>  |

| 21                                   | V <sub>DD</sub> POWER SUPPLY                      | V <sub>DD</sub>                  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 22                                   | CHIP DISABLE                                      | CD                               | This line controls the disconnect associated<br>with busable inputs and Three-State outputs. A<br>high-level input voltage, V <sub>IH</sub> , applied to this line<br>removes drive from push-pull outputs causing<br>them to float. Drivers of disabled inputs are<br>required to sink or source current. The I/O Lines<br>controlled by Chip Disable are defined below:                                                                                                                                                                                                             |             |

|                                      |                                                   |                                  | $\begin{array}{c c} \textbf{INPUT LINES} & \textbf{TRI-STATE OUTPUT LINES} \\ \hline CRL & THRL & DA \\ EPE & FHRL & THRE \\ PI & FR_1 \text{-} FR_8 \\ CS_1 \text{-} CS_2 & TR_1 \text{-} TR_8 \\ \hline MS_1 \text{-} MS_2 & WLS_1 & WLS_2 \\ \hline DAR \end{array}$                                                                                                                                                                                                                                                                                                               |             |

| 23, 25<br>27, 29<br>31, 33<br>35, 37 | FILL-CHARACTER<br>HOLDING REGISTER<br>DATA INPUTS | FR <sub>1</sub> -FR <sub>8</sub> | A low-level input voltage, $V_{IL}$ , applied to CD (pin<br>22) enables the inputs of the Fill-Character<br>Holding Register and associated Load Strobe,<br>FHRL. Parallel 8-bit characters are input into<br>the Fill-Character Holding Register with the<br>FHRL Strobe (pin 20). If a character of less than<br>8 bits has been selected (by WLS <sub>1</sub> and WLS <sub>2</sub> )<br>only the least significant bits are accepted.<br>These lines may be strobed or hard-wired to the<br>appropriate input voltage. These inputs are not<br>used during asynchronous operation. |             |

|                                      |                                                   |                                  | During Synchronous or Isochronous transmission, the Fill-Character is transmitted if a character was not loaded into the Transmitter Holding Register prior to a DA Flag; i.e., the Transmitter Holding Register did not contain a character at the center of the last bit being transmitted from the Transmitter Register. A high-level input voltage, $V_{OH}$ , to be transmitted, Least Significant Bit (FR <sub>1</sub> ) to Most Significant Bit (FR <sub>n</sub> ) order.                                                                                                      |             |

|                                      |                                                   |                                  | A high-level input voltage, $V_{\text{IH}},$ applied to CD disables $\text{FR}_1\text{-}\text{FR}_8\text{-}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| 24, 26<br>28, 30<br>32, 34<br>36, 38 | TRANSMITTER<br>HOLDING REGISTER<br>DATA INPUTS    | TR₁-TR <sub>8</sub>              | A low-level input voltage, $V_{IL}$ , applied to CD (pin 22) enables the inputs to the Transmitter Hold-<br>ing Register and associated Load Strobe,<br>THRL. If a character of less than 8 bits has been<br>selected (by WLS <sub>1</sub> and WLS <sub>2</sub> ), only the least<br>significant bits are accepted. A high-level input                                                                                                                                                                                                                                                |             |

| PIN<br>NUMBER | I/O NAME    | SYMBOL                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------------|-------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               |             |                                    | voltage, V <sub>IH</sub> , will cause a high-level output<br>voltage to be transmitted, Least Significant Bit<br>(TR <sub>1</sub> ) to Most Significant Bit (TR <sub>n</sub> ) order. A high-<br>level input voltage, V <sub>IH</sub> , applied to CD disables<br>TR <sub>1</sub> -TR <sub>8</sub> .                                                                                         |  |  |

| 39-40         | WORD LENGTH | WLS <sub>1</sub> -WLS <sub>2</sub> | A low-level input voltage, $V_{1L}$ , applied to CD (pin<br>22) enables <u>the</u> inputs of the Control Register<br>and Load, CRL. Parallel 8-bit characters are<br>input into the Control Register with the CRL<br>Strobe (pin 4), WLS <sub>1</sub> and WLS <sub>2</sub> select the trans-<br>mitted character length from five (5) to eight (8)<br>bits defined by the Truth Table below: |  |  |

|               |             |                                    | WLS <sub>2</sub> WLS <sub>1</sub> SELECTED WORD LENGTH                                                                                                                                                                                                                                                                                                                                       |  |  |

|               |             |                                    | V <sub>IL</sub> V <sub>IL</sub> 5 BITS<br>V <sub>IL</sub> V <sub>IH</sub> 6 BITS                                                                                                                                                                                                                                                                                                             |  |  |

|               |             |                                    | VIH VIL 7 BITS<br>VIH VIH 8 BITS                                                                                                                                                                                                                                                                                                                                                             |  |  |

|               |             |                                    | A high-level input voltage, $V_{\rm IH}$ applied to CD disables WLS1 and WLS2, forcing them to float.                                                                                                                                                                                                                                                                                        |  |  |

#### ORGANIZATION

PT1482 block diagram is illustrated on page 1.

**Control Register** — Programming of the PSAT is accomplished by loading the 8 Bit Control Register. Mode selection, clock divisor, word length, and parity are selected when the Control Register Load signal is activated.

Transmitter Register — The Transmitter Register is used to store the outgoing data stream. The contents of this register are derived from either the Transmitter Holding Register or the Fill (Match) Character Holding Register with the Control and Timing Logic automatically adding the required start and stop bits during Asynchronous and Isoschronous Modes.

Transmitter Holding Register — The Transmitter Holding Register, a buffer register, is used to store the parallel character to be serially transmitted.

Fill Character Holding Register — The Fill Character Holding Register is used to store the Fill (Match) Character which is transmitted during the absence of characters in the Transmitter Holding Register.

Timing and Control — The Timing and Control Logic generates the required control signals to transmit Data and Fill Characters. Character transmission status signals are also derived from this logic.

#### SYNCHRONOUS MODE OPERATION

Synchronous transmission requires that characters

(programmably variable from 5 to 8 data bits plus parity) are contiguous with no start or stop bits. Since the requirement that characters are contiuous does not imply that the system servicing the transmitter always has ample time to load the Transmitter Holding Register, it is necessary that a character be transmitted when data has not been loaded into the Transmitter Holding Register. This character is defined as the Fill or Idle Character and a separate register has been provided to load this character upon initialization. The Fill-Character Holding Register is loaded by strobing the Fill-Character Holding Register Load (FHRL) line or hard-wiring it to a low-level input voltage.

Referring the Block Diagram of the Transmitter, it can be seen that the Chip Disable (CD) enables or disconnects various inputs and outputs of the P/SAT. The inputs to the Control Register, Transmitter Holding Register, Fill-Character Holding Register and their respective load strobes, CRL, THRL, and FHRL are under CD control. In addition, the Transmitter Holding Register Empty (THRE) Flag, Data Not Available (DA) Flag, and the Data Not Available Reset (DAR) are also controlled by CD. It is necessary that CD enable these lines to allow strobing information into these registers and to allow examination of these output flags. The P/SAT will enter a defined "idle" state when the Master Reset (MR) is strobed to a high-level input voltage. In this state, all timing and control logic are reset, the Transmitter Register Output continues to mark, the Transmitter Holding Register Flag is set to a high-level output voltage. the Data Delimit/End of Character (DD/EOC) Flag

SUC--02 1

is set to a low-level output voltage, and the contents of the Fill-Character Holding Register are forced to a high-level output voltage.

When the P/SAT is enabled by CD, loading the Control Register by strobing the Control Register Load (CRL) line to a low-level input voltage, defines the mode of operation, character length, selected parity if required, and the clock rate selection. Table 1 illustrates all the programmable synchronous character formats.

To initialize transmission the CTS signal must be set to a high state and the transmitter holding register must be loaded with a character to be transmitted. The transmitter will remain in an idle state until this is accomplished.

The character transferred into the Transmitter Register (from the Transmitter Holding Register or the Fill-Character Holding Register) is determined at the center of the last bit of the character being transmitted. If, at this time, no character has been loaded into the Transmitter Holding Register, the Fill-Character is loaded into the Transmitter Register at the end of the bit being transmitted

#### **Table 1. SYNC MODE CONTROL DEFINITION**

| CONTROLWORD<br>WW<br>MMLLE<br>SSSPP<br>21211E |     |      |     | /OR  | D   | CHARACT | ERFORMAT                   |        |

|-----------------------------------------------|-----|------|-----|------|-----|---------|----------------------------|--------|

|                                               |     |      | W   | W    |     |         | and setting                |        |

|                                               | М   | М    | L   | L    |     | Е       | an an Artan (Arta)<br>Arta | ADDED  |

|                                               | s   | s    | s   | s    | Ρ   | Ρ       | DATA                       | PARITY |

|                                               | 2   | 1    | 2   | 1    | 1   | Е       | BITS                       | BIT    |

|                                               | 1   | 0    | 0   | 0    | 0   | 0       | 5                          | ODD    |

|                                               | 1   | 0    | 0   | 0    | 0   | 1       | 5                          | EVEN   |

|                                               | 1   | 0    | 0   | 0    | 1   | x       | 5                          | NONE   |

|                                               | 1   | 0    | 0   | 1    | 0   | 0       | 6                          | ODD    |

|                                               | 1   | 0    | 0   | 1    | 0   | 1       | 6                          | EVEN   |

|                                               | 1   | 0    | 0   | 1    | 1   | X       | 6                          | NONE   |

|                                               | 1   | 0    | 1   | 0    | 0   | 0       | 7                          | ODD    |

|                                               | 1   | 0    | 1   | 0    | 0   | 1       | 7                          | EVEN   |

|                                               | 1   | 0    | 1   | 0    | 1   | х       | 7                          | NONE   |

|                                               | 1   | 0    | 1   | 1    | 0   | 0       | 8                          | ODD    |

|                                               | 1   | 0    | 1   | .1   | 0   | 1       | 8                          | EVEN   |

|                                               | 1   | 0    | 1   | 1    | 1   | X       | 8                          | NONE   |

|                                               | 1   |      |     |      |     |         |                            |        |

|                                               | Set | s to | SYN | IC N | lod | e       |                            |        |

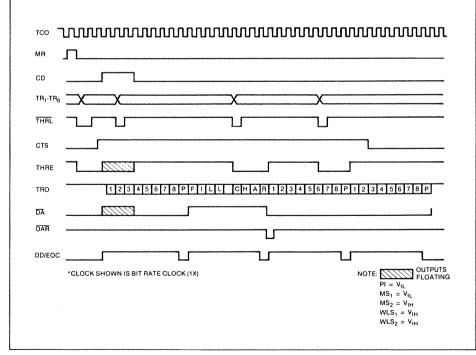

#### SYNCHRONOUS TIMING EXAMPLE

and a Data Not Available (DA) Flag is set to a highlevel output voltage. This Fill-Character will be repeatedly transmitted until a character is loaded into the Transmitter Holding Register, at which time, the Data Not Available Flag is reset, the Fill-Character will be completed and the newly loaded synchronous character will follow contiguously.

A high-level output voltage, on the THRE Flag indicates that the Transmitter Holding Register is empty and may be loaded with a character. Data on the inputs of the Transmitter Holding Register is loaded when the Transmitter Holding Register Load (THRL) line is strobed to a low-level input voltage, forcing the THRE Flag to a low-level output voltage. This data must be stable prior to THRL going to a high-level input voltage since this register is a set of DC latches which are enabled by THRL.

If the Clear-To-Send (CTS) line is at a low-level input voltage, or if the Transmitter Register is in the process of transmitting a character, the character in the Transmitter Holding Register will not be transferred down to the Transmitter Register and the THRE Flag will remain at a low-level output voltage. Raising the CTS line to a high-level input voltage or completion of transmission of a character from the Transmitter Register causes the automatic transfer of the character in the Transmitter Holding Register to the Transmitter Register which forces the THRE Flag to be set to high-level output voltage. The selected parity is added to the data during the transfer to the Transmitter Register and serial transmission is initiated as an NRZ waveform. A low-level input voltage applied to CTS during transmission allows completion of that character only, after which the device enters the idle state and the output will continue to mark until a high-level input voltage is applied.

The Data Delimit/End of Character Flag has been provided to indicate the transmission of serial data on the Transmitter Register Output. The Data Delimit/End of Character Flag is defined as a lowlevel output voltage during transmission of the last bit of a synchronous character and when the P/SAT is in the "idle" state.

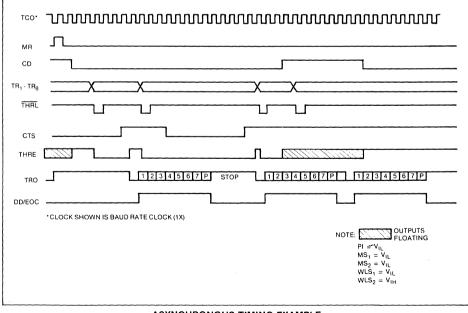

#### ASYNCHRONOUS MODE OPERATION

An asynchronous character consisting of a start bit, followed by data (programmably variable from 5 to 8 data bits), parity (if so programmed), and a stop "element" is serially transmitted, in that order, as an NRZ waveform by the P/SAT. The stop interval is referred to as an "element" since its minimum length is under program control and may be 1 or 2 bits in length. When programmed for 2 stop bits, a 5-level (bit) code will be transmitted with 1.5 stop bits.

Referring to the Block Diagram of the Transmitter, it can be seen that the Chip Disable enables or

disconnects various inputs and outputs of the P/SAT. The inputs to the Control Register, Transmitter Holding Register, Fill-Character Holding Register and their respective load strobes, CRL, THRL and FHRL are under CD control. In addition, the Transmitter Holding Register Empty Flag (THRE), the Data Not Available Flag (DA), and the Data Not Available Reset (DAR) are also controlled by CD. It is necessary that CD enable these lines to allow strobing information into these registers and to allow examination of these output flags. It should be noted that the Fill-Character Holding Register and its associated load strobe, FHRL, the Data Not Available Flag and its associated reset, DAR, play no role in asynchronous communications and are only mentioned here for completeness.

The P/SAT will enter a defined "idle" state when the Master Reset (MR) line is strobed to a highlevel input voltage. In this state, all timing and control logic are reset, the Transmitter Register Output continues to mark, the Transmitter Holding Register Empty Flag is set to a high-level output voltage, V<sub>OH</sub>, and the Data Delimit/End of Character (DD/EOC) Flag is reset to a low-level output voltage.

When the transmitter is enabled by CD, loading the Control Register by strobing the Control Register Load (CRL) line to a low-level input voltage,  $V_{IL}$ , defines the mode of operation, character length, selected parity if required and the clock rate selection. Table 2 illustrates all the programmable asynchronous formats.

Continuous transmission, transmission of characters with the minimum number of stop bits programmed, is accomplished by loading the Transmitter Holding Register within a character time of when its "Empty Flag" becomes a highlevel output voltage. A high-level output voltage, V<sub>OH</sub>, on the Transmitter Holding Register Empty (THRE) Flag indicates that the Transmitter Holding Register is empty and may be loaded with a character. Data on the inputs of the Transmitter Holding Register is loaded when the Transmitter Holding Register Load (THRL) line is strobed to a low-level input voltage, VIL, for ng the THRE Flag to a low-level output voltage, VoL. This data must be stable prior to THRL going to a high-level input voltage since this register is a set of DC latches which are enabled by THRL. If the Clear-To-Send (CTS) line is at a low-level input voltage or if the Transmitter Register is in the process of transmitting a character, the character in the Transmitter Holding Register will not be transferred down to the Transmitter Register and the THRE Flag will remain at a low-level output voltage. Raising the CTS line to a high-level input voltage or completion of transmission of a character from the Transmitter Register causes the automatic transfer of the character in the Transmitter Holding Register to the Transmitter Register and the THRE flag will be set to a high-level output voltage.

SECT-OR 1

The start bit, selected parity and stop bit(s), determined by the Control Register programming, are added to the data during the transfer to the Transmitter Register and serial transmission is initiated as an NRZ waveform.

A low-level input voltage, applied to CTS during transmission, allows completion of that character only, after which the output will continue to mark until a high-level input voltage is applied.

The Data Delimit/End of Character Flag has been provided to indicate the transmission of serial data on the Transmitter Register Output. Data Delimit is a low-level output voltage during start and stop bits and is a high-level output voltage during transmission of data and parity. Neither TRO, CTS nor DD/EOC is under control of Chip Disable.

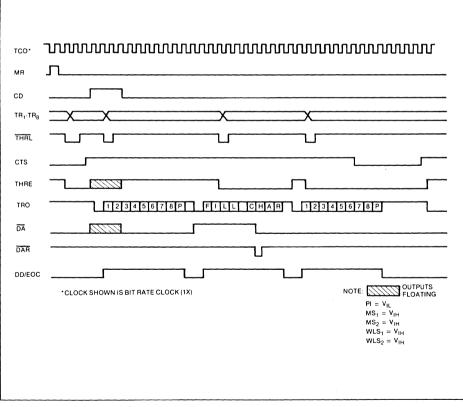

#### **ISOCHRONOUS MODE OPERATION**

In the Isochronous Mode of operation all (Synchronous Mode) definitions apply with the exception of those for the Data Delimit/End of Character (DD/EOC) Flag and the Data Not Available Flag (DA).

This is the case since lsochronous Data Transmission requires contiguous characters with the addition of a start and a single stop bit added to each character.

## Table 2. ASYNC MODE CONTROL DEFINITION

| l | CONTROL WORD                                         | CHARACTER FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | W W<br>M M L L E<br>S S S S S P P<br>2 1 2 1   E     | ADDED<br>START DATA PARITY STOP<br>BIT BITS BIT ELEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | Bit         Bits         Bit         Bits         B |

|   | Sets to ASYNC Mc                                     | ode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### ASYNCHRONOUS TIMING EXAMPLE

SHCH-OZ +

The Data Delimit/End of Character Flag is a lowlevel output voltage during start and stop bits and is a high-level output voltage during transmission of data and parity. The Data Not Available Flag ( $\overline{DA}$ ) is set to a high-level output voltage at the end of the stop bit if a character has not been loaded into the Transmitter Holding Register at the center of the stop bit. The contents of the Fill-Character Holding Register will be transferred into the Transmitter Register and repeatedly transmitted until a character is loaded into the Transmitter Holding Register. At this time, the Fill-Character will be completed and the newly loaded isochronous character will follow contiguously.

Table 3 illustrates all the programmable isochronous character formats.

#### Table 3. ISOC MODE CONTROL DEFINITION

| CONTROL WORD                                   |                 | CHARACTER FORMAT          |                        |                  |  |  |

|------------------------------------------------|-----------------|---------------------------|------------------------|------------------|--|--|

| W W<br>M M L L E<br>S S S S P P<br>2 1 2 1 I E | START<br>BIT    | DATA<br>BITS              | ADDED<br>PARITY<br>BIT | STOP<br>ELEMENTS |  |  |

| 110000                                         | Post 1 and      | 5                         | ODD                    | 1                |  |  |

| 110001                                         | 1               | 5                         | EVEN                   | 1                |  |  |

| 11001X                                         | 1               | 5                         | NONE                   | 1                |  |  |

| 110100                                         | 1               | 6                         | ODD                    | 1                |  |  |

| 110101                                         | 1. Sec. 1. Sec. | 6                         | EVEN                   | 1                |  |  |

| 11011X                                         | 1               | 6                         | NONE                   | 1                |  |  |

| 111000                                         | 1               | 7                         | ODD                    | 1                |  |  |

| 111001                                         | 1 1             | 7                         | EVEN                   | 1                |  |  |

| 11101X                                         | 1               | 7                         | NONE                   | 1                |  |  |

| 111100                                         | 1 1             | 8                         | ODD                    | 1                |  |  |

| 111101                                         | 1.00            | 8                         | EVEN                   | 1                |  |  |

| 11111X                                         | 1               | 8                         | NONE                   | 1                |  |  |

| Sets to ISOC Mod                               | le              | tetet forsende<br>Service |                        |                  |  |  |

#### **ISOCHRONOUS TIMING EXAMPLE**

SUCH-OZ 1

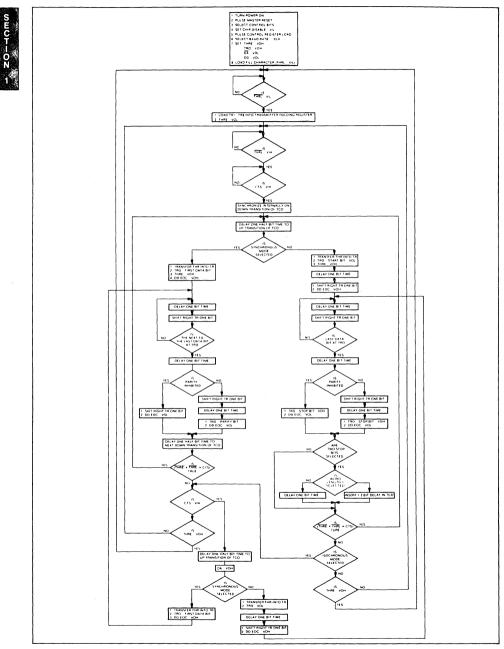

PT1482 SYNCHRONOUS ASYNCHRONOUS TRANSMITTER FLOW CHART

тсо +-CD >500ns *٦*۲ TR<sub>1</sub>-TR<sub>8</sub>  $\mathcal{A}$ THRL  $\mathcal{A}\mathcal{F}$ į >500ns -1F CTS I i 500ns 500ns |500ns 500ns 500ns  $\overline{+}$ THRE 1 1 → 250ns \_500ns 250ns -+| 250ns 250ns  $\overline{\mathcal{F}}$ \_ TRO i

S

TIMING DETAIL

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>GG</sub> Supply Voltage                      | + 0.3V to - 20V  | $V_{GG} = V_{DD} = OV$                      |

|-----------------------------------------------------|------------------|---------------------------------------------|

| V <sub>DD</sub> Supply Voltage                      | +0.3V to -20V    | NOTE: These voltages are measured           |

| Clock Input Voltage*                                | +0.3V to -20V    | with respect to V <sub>SS</sub> (Substrate) |

| Logic Input Voltage*                                | + 0.3V to - 20V  | with respect to vss (oubstrate)             |

| Logic Output Voltage*                               | +0.3V to -20V    |                                             |

| Storage Temperature Ceramic                         | -165°C to +150°C |                                             |

| Plastic                                             | -55°C to +125°C  |                                             |

| Operating Free-Air Temperature T <sub>A</sub> Range | 0°C to +70°C     |                                             |

| Lead Temperature (Soldering, 10 sec.)               | 300°C            |                                             |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{SS}$  =  $V_{CC}$  = 5V  $\pm$  5%,  $V_{DD}$  = OV,  $V_{GG}$  = - 12V  $\pm$  5%,  $T_A$  = 0°C to + 70°C unless otherwise specified)

| SYMBOL                             | PARAMETER                                                                                 | MIN.                  | MAX.   | CONDITIONS                                                                        |

|------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|--------|-----------------------------------------------------------------------------------|

| V <sub>IL</sub><br>V <sub>IH</sub> | INPUT LOGIC LEVELS'<br>Low-level Input Voltage<br>High-level Input Voltage                | V <sub>SS</sub> -1.5V | 0.8V   | v <sub>SS</sub> = 4.75V                                                           |

| V <sub>oL</sub><br>V <sub>oH</sub> | OUTPUT LOGIC LEVELS <sup>2</sup><br>Low-level Output Voltage<br>High-level Output Voltage | V <sub>SS</sub> -1.0V | 0.5V   | $V_{SS} = 5.25V$<br>$I_{OL} = -1.6mA$<br>$V_{SS} = 4.75V$<br>$I_{OH} = -100\mu A$ |

| I <sub>IL</sub>                    | INPUT CURRENT –<br>Low-level Input Current<br>(each input)                                |                       | -1.6mA | V <sub>SS</sub> = 5.25V<br>V <sub>IN</sub> = 0.4V                                 |

\*\*Not more than one output should be shorted at a time.

- NOTE: 1) Inputs under Chip Disable control when disabled (V<sub>IH</sub> applied to CD), are logically disabled and appear as a single TTL load.

- Outputs under Chip Disable control when disabled (V<sub>IH</sub> applied to CD) are logically and electrically disconnected and caused to float.

- The Three-State Output has three states;

(1) Low impedance to  $V_{CC}$  (2) Low impedance to GND (3) High impedance OFF ~ 10 Megohm.  $I_{SS}$  = 35mA ~  $I_{GG}$  = 10mA

### SWITCHING CHARACTERISTICS

$(V_{SS} = V_{CC} = 5V, V_{DD} = OV, V_{GG} = -12V, T_A = 25^{\circ}, C_L = 20pf)$

| SYMBOL                                                                     | PARAMETER                                                                                                                                                                                                                               | MIN.                                                                | MAX.                                         | CONDITIONS        |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|-------------------|

| Fc                                                                         | Clock Frequency                                                                                                                                                                                                                         | DC<br>DC                                                            | 100 KHz<br>640 KHz                           | 1482B<br>1482B-01 |

| THOLD<br>TCRL<br>TTHRL<br>TFHRL<br>TDAR<br>TMR<br>TPD<br>TSKEW<br>TR<br>TF | PULSE WIDTH<br>Hold Time<br>Control Register Load<br>Transmitter Holding Register Load<br>Fill-Character Holding RegisterLoad<br>Data Not Available Reset<br>Master Reset<br>Output Enable Delay<br>Skew Time<br>Rise Time<br>Fall Time | 20 nsec<br>250 nsec<br>250 nsec<br>250 nsec<br>200 nsec<br>500 nsec | 500 nsec<br>250 nsec<br>150 nsec<br>150 nsec |                   |

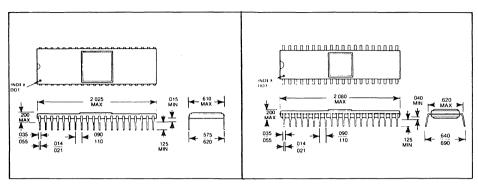

PT1482A CERAMIC PACKAGE

PT1482B PLASTIC PACKAGE

SUCH-OZ 1

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent or patent Digital Corporation. Western Digital Corporation reserves the right to change said circuitry at any time without notice.

WESTERN DIGITAL

3128 REDHILL AVENUE, BOX 2180

NEWPORT BEACH, CA 92663 (714) 557-3550,TWX 910-595-1139