## DESCRIPTION

The PT2480 is a brushed-DC motor driver for printers, home appliances, industrial equipment, and other small machines. Dual pin logic inputs controls the Hbridge driver output current flows to maniple the motor rotation in forward or reverse direction. With sufficient heat dissipation PCB area or add-on heatsinking, the peak output current may up to 3.6 Amps.

The PT2480 has built-in PWM current regulation circuits; it's a very useful function to limiting average current draws from power supply during motor rotates starts up and stalled. The PWM current regulation level is determinates by an external applied VREF reference voltage and current sense resistance attached in ISEN pin.

The PT2480 is protected from many fault conditions, including under voltage (UVLO), over current protection (OCP) and over temperature shut down (TSD). The drive will disable the H-bridge output during fault condition is met, and device will automatically recovery when fault phenomena is removed.

#### PT2480 45V/3.6A Brushed DC Motor Driver

# FEATURES

- H-Bridge Motor Driver for:

- Single brushed DC Motor,

- Single Winding of a Bipolar Stepping Motor

- Solenoid High Side Driver

- Wide Operating Voltage : 6.5V to 45V

- Low Switches RDS(on) (HS+LS) : 500mΩ(typ)

- Peak Current Output : 3.6 Amps

- H-bridge Control Interface

- PWM Current Regulation

- Low-Power Sleep Mode

- Small Package and Footprint – 8-Pin HSOP With Thermal PAD

- Protection Features

- VM Under voltage Lockout (UVLO)

- Over Current Protection (OCP)

- Over Thermal Shutdown (TSD)

- Automatic Fault Recovery

### **APPLICATIONS**

- Printers

- Home Appliances

- Industrial Equipment

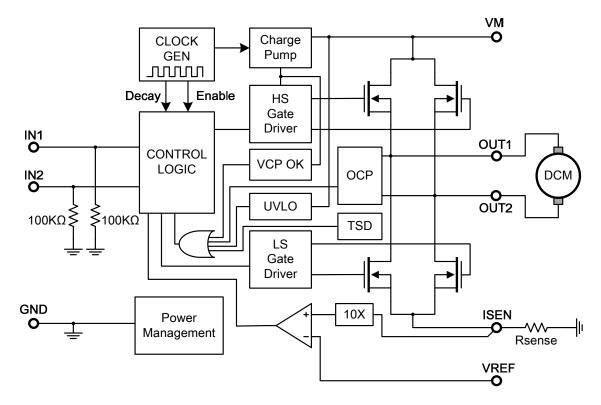

### **BLOCK DIAGRAM**

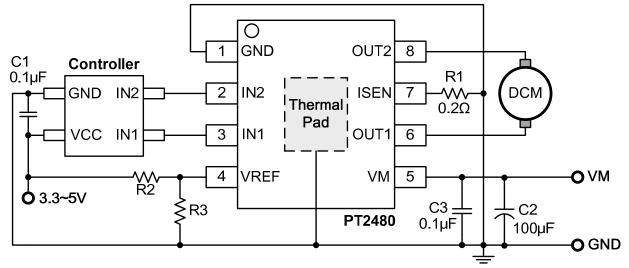

# **APPLICATION CIRCUIT**

Drives brushed DC motor with PWM current regulation function.

#### Figure 1. Typical Application Circuit

note(1) : The recommended value of R1 is from  $0.1\Omega$  to  $0.5\Omega$ , power dissipation from 0.5 to 1W. note(2) : Connects ISEN pin to power ground directly if PWM current regulation function is not necessary.

note(3) : VREF input voltage should not exceeds 5V.

# **ORDER INFORMATION**

| Valid Part Number | Package Type        | Top Code  |  |

|-------------------|---------------------|-----------|--|

| PT2480-HS         | 8-PIN, HSOP, 150MIL | PT2480-HS |  |

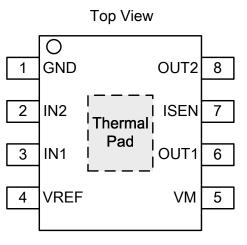

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin Name                    | Туре  | Description                                                                                                                                                                 |   |  |

|-----------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| GND                         | POWER | Ground for internal circuits, connects to power ground.                                                                                                                     |   |  |

| IN2                         | I     | Control logic input 2, with $100K\Omega$ internal pulldown.                                                                                                                 |   |  |

| IN1                         | I     | Control logic input 1, with 100K $\Omega$ internal pulldown.                                                                                                                |   |  |

| VREF                        | I     | PWM current regulation reference input, input range from 0 to 5 V.                                                                                                          |   |  |

| VM                          | POWER | Main power supply input for the IC.                                                                                                                                         |   |  |

| OUT1                        | 0     | H-bridge output 1.                                                                                                                                                          |   |  |

| ISEN                        | 0     | H-bridge low side MOSFETs ground current path, refer to the application circuit for the recommends of sense resistor connection.                                            |   |  |

| OUT2                        | 0     | H-bridge output 2.                                                                                                                                                          |   |  |

| thermal dissipation, a broa |       | Thermal pad; must be soldered to the PCB ground plane. For improves thermal dissipation, a broad, multiple layer ground planes with multiple via connection is recommended. | - |  |

### FUNCTION DESCRIPTION H-BRIDGE OUTPUT CONFIGURATION

The motor winding current direction is determinate by H-bridge output configuration, and it is maniples by control logic interface. Please refer to Table 1 for corresponds between input and output.

| IN1 | IN2 | OUT1 | OUT2 | DESCRIPTION                                                                                     |

|-----|-----|------|------|-------------------------------------------------------------------------------------------------|

| 0   | 0   | HiZ  | HiZ  | Coast mode. The H-bridge is disabled and whole chip entering sleep mode after Tslp time (~1mS). |

| 0   | 1   | L    | Н    | Reverse mode (Output current from OUT2 to OUT1)                                                 |

| 1   | 0   | Н    | L    | Forward mode (Output current from OUT1 to OUT2)                                                 |

| 1   | 1   | L    | L    | Brake mode; motor winding current flowing in between both low side MOSFETs.(slow decay)         |

Table 1. H-Bridge Output Operation

### SLEEP MODE

If both control logic input pin sets to low state(or float connection) from forward/reverse mode, the H-bride will disabled immediately, after a short delay time (Tslp, approximately 1mS) the internal circuit also disabled and whole chip will entering sleep mode, the current consumption will drops to Islp level and outputs remains in HiZ.

The internal circuit needs an enable time (Tena, approximately  $50\mu$ S) to wakes up the H-bridge from sleep mode or UVLO released. During sleep mode actives, whatever the IN1 or IN2 pin are pull-high for at least  $5\mu$ S, the chip will quit from sleep mode and H-bridge will operates after Tena time.