An Infineon Technologies Company

### Sychronous Rectified Buck MOSFET Driver IC

# PX3515

Datasheet

# **Applications**

- Core power regulation for  $\text{Intel}^{\texttt{R}}$  and  $\text{AMD}^{\texttt{R}}$   $\mu\text{processors}$

- High current DC-DC converters

- POL power converters for memory, DSP, FPGA, ASIC

# Features

- Dual MOSFET driver for synchronous rectified bridge converters

- Adjustable high-side and low-side MOSFET gate drive voltages for optimal efficiency

- High-side VCC (7V to 12V)

- Low-side PVCC (5V to 12V)

- Integrated bootstrap diode for reduced part count

- Adaptive gate drive control prevents cross-conduction

- Fast rise and fall times supports switching rates of up to 2MHz

- Capable of sinking more than 4A peak current for low switching losses

- Three-state PWM input for output stage shutdown

- VCC under-voltage protection

Ordering Information

Ambient

0 to 85°C

• Lead-free (RoHS compliant) SOIC and DFN packages

Package

10-lead DFN

### Description

The PX3515 is a dual high speed driver designed to drive a wide range of high-side and low-side power N-channel MOSFETs in synchronous rectified buck converters. When combined with the Primarion PX35XX family of Digital Multiphase Controllers or PX75XX Digital Point of Load (Di-POL<sup>TM</sup>) Controllers and N-channel MOSFETs, the PX3515 forms a complete core-voltage regulator solution for advanced micro and graphics processors as well as point-of-load applications.

The PX3515 provides the capability of driving the high-side gate and low-side gate with independent drive voltages over a range from 7V to 12V (high-side VCC) and 5V to 12V (low-side PVCC). This provides the flexibility necessary to optimize applications involving trade-offs between gate charge and conduction losses.

Adaptive zero shoot-through protection is integrated into the IC which prevents both upper and lower MOSFETs from conducting simultaneously and to minimize dead time. The PX3515 has small propagation delay from input to output with fast rise and fall times.

The PX3515 drivers also feature a three-state PWM input which, when used together with Primarion's Digital Controllers, eliminates the need for Schottky diodes that are often used in systems to protect the load from reversed output voltage events.

### PX3515 DFN Package

| 10-pin DFN (TOP VIEW) |            |     |             |       |  |

|-----------------------|------------|-----|-------------|-------|--|

| UGATE                 | 1          |     | () L<br>(10 | PHASE |  |

| BOOT                  | <u>2</u> ; |     | (9          | PVCC  |  |

| N/C                   | 3;         | GND | < <u>8</u>  | N/C   |  |

| PWM                   | [4];       |     | (7          | VCC   |  |

| GND                   | 5)<br>1)   | ×/  | (6<br>(     | LGATE |  |

Part Number

PX3515BDDG

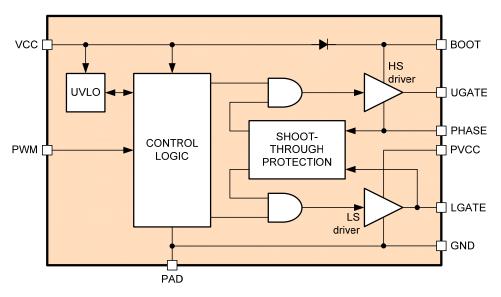

# **Functional Block Diagram**

Figure 1. Block Diagram

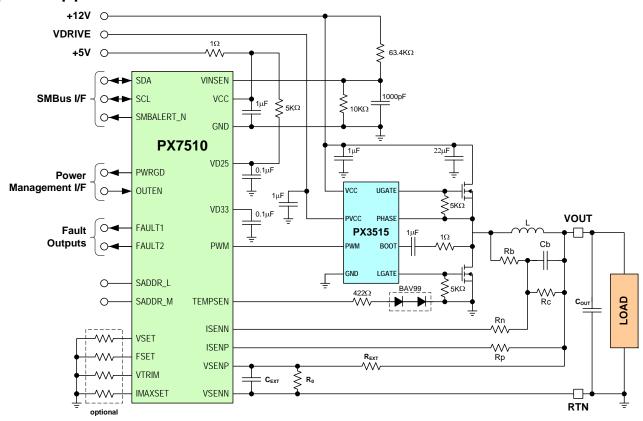

# **Typical Application**

Figure 2. Single-Phase Application with PX7510 DiPOL Controller

# **Absolute Maximum Ratings**

Stresses above those listed in Table 1 "Absolute Maximum Ratings" may cause permanent damage to the device. These are absolute stress ratings only and operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of this specification.

| Symbol                                 | Description               | Min                      | Max                     | Units | Conditions                        |

|----------------------------------------|---------------------------|--------------------------|-------------------------|-------|-----------------------------------|

| V <sub>VCC</sub>                       | VCC supply voltage (DC)   | -0.3                     | 25                      | V     |                                   |

| V <sub>PVCC</sub>                      | PVCC supply voltage (DC)  | -0.3                     | 25                      | V     |                                   |

| V <sub>BOOT</sub>                      | BOOT voltage              | -0.3                     | 45                      | V     | Referenced to GND                 |

| V <sub>BOOT</sub> - V <sub>PHASE</sub> | BOOT to PHASE voltage     | -0.3                     | 25                      | V     | Referenced to PHASE               |

| V <sub>PHASE</sub>                     | PHASE voltage, DC         | -1                       | 25                      | V     | DC                                |

| V <sub>PHASE</sub>                     | PHASE voltage, pulsed     | -20                      | 30                      | V     | Pulsed (500ns, 2% max duty cycle) |

| V <sub>PWM</sub>                       | Input voltage             | -0.3                     | 6.3                     | V     |                                   |

|                                        | UGATE                     | $V_{\text{PHASE}} - 0.3$ | V <sub>BOOT</sub> + 0.3 | V     |                                   |

|                                        | LGATE                     | -0.3                     | V <sub>PVCC</sub> + 0.3 | V     |                                   |

|                                        | ESD, Human Body Model     | 4000                     |                         | V     | JEDEC JESD22-A114-E               |

|                                        | ESD, Charged Device Model | 1000                     |                         | V     | JEDEC JESD22-C101-C               |

|                                        | ESD, Machine Model        | 300                      |                         | V     | JEDEC JESD22-A115-A               |

| TJ                                     | Junction temperature      | -25                      | 150                     | °C    |                                   |

| T <sub>STG</sub>                       | Storage temperature       | -55                      | 150                     | °C    |                                   |

#### Table 1. Absolute Maximum Ratings<sup>1</sup>

Notes:

1. At  $T_J = 25^{\circ}C$ , unless otherwise specified

# **Recommended Operating Conditions**

#### Table 2. Recommended Operating Conditions

| Symbol            | Description                                  | Min  | Nom   | Max   | Units |

|-------------------|----------------------------------------------|------|-------|-------|-------|

| V <sub>VCC</sub>  | VCC supply voltage                           | +7.0 | +12.0 | +13.2 | V     |

| V <sub>PVCC</sub> | PVCC supply voltage                          | +4.5 | +12.0 | +13.2 | V     |

| f <sub>PWM</sub>  | PWM signal transition frequency              | 0.1  |       | 2     | MHz   |

| TJ                | Junction temperature                         | 0    |       | 125   | °C    |

| TAMBIENT          | Operating ambient temperature                | 0    |       | 85    | °C    |

| $\theta_{JA(0)}$  | Thermal resistance, junction-to-air, note 2  |      | 48    |       | °C/W  |

| θ」С               | Thermal resistance, junction-to-case, note 3 |      | 7     |       | °C/W  |

Notes:

- 2.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air

- 3. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the underside of the package

# **Electrical Characteristics**

Operating conditions: VCC = +12.0V, PVCC = +12.0V,  $T_A = 25^{\circ}C$ , unless otherwise specified.

| Parameter                        | Conditions                       | Symbol                 | Min | Тур  | Max | Units |

|----------------------------------|----------------------------------|------------------------|-----|------|-----|-------|

| Supply Characteristics           |                                  |                        | •   |      |     |       |

| VCC supply current               | f <sub>PWM</sub> = 1MHz, no load | I <sub>VCC</sub>       |     | 6    |     | mA    |

| PVCC supply current              | f <sub>PWM</sub> = 1MHz, no load | I <sub>PVCC</sub>      |     | 5.5  |     | mA    |

| Quiescent current                | 1.4 ≤ V <sub>PW/M</sub> ≤ 2.2    | IPVCCQ+IVCCQ           |     | 1.9  |     | mA    |

| VCC rising threshold             | dv/dt < 2.5 kV/s                 |                        |     | 6.2  | 6.7 | V     |

| VCC falling threshold            |                                  |                        | 4.8 | 5.6  |     | V     |

| VCC hysteresis                   |                                  |                        | 400 | 650  | 950 | mV    |

| PWM Input                        |                                  |                        |     |      |     |       |

| Input current                    | $V_{PWM} = +3.3V$                | I <sub>PWM_H</sub>     |     | 450  |     | μA    |

|                                  | $V_{PWM} = 0V$                   | I <sub>PWM L</sub>     |     | -530 |     | μΑ    |

| Sink/source impedance            |                                  | R <sub>PWM</sub>       |     | 3.5  |     | kΩ    |

| Shutdown window (3-state)        | minimum pulse of 25ns            | V <sub>PWM_SD</sub>    | 1.4 |      | 2.2 | V     |

| PWM open threshold               |                                  | V <sub>PWM_O</sub>     | 1.6 | 1.8  | 2.0 | V     |

| PWM rising threshold             |                                  | V <sub>PWM_H</sub>     | 2.6 |      |     | V     |

| PWM falling threshold            |                                  | V <sub>PWM_L</sub>     |     |      | 1.0 | V     |

| PWM input slew rate              |                                  | SR <sub>PWM</sub>      | 5   |      | _   | V/µs  |

| Minimum pulse width high side    | pulse width on PWM               | t <sub>min_PWM</sub>   |     | 40   |     | ns    |

| Upper Gate (UGATE) Output        |                                  |                        |     | 1    | 1   |       |

| Shutdown hold off time           | Note 4, 3nF load                 | t <sub>PDTS_UG</sub>   |     | 25   | 40  | ns    |

| UGATE rise time                  | Note 4, 3nF load                 | t <sub>r_UG</sub>      |     | 20   |     | ns    |

| UGATE fall time                  | Note 4, 3nF load                 | t <sub>f_UG</sub>      |     | 15   |     | ns    |

| 3-state rising propagation delay | Note 4, 3nF load                 | t <sub>TSSHD_UG</sub>  |     | 25   | 45  | ns    |

| UGATE turn-on propagation delay  | Note 4, 3nF load                 | t <sub>D(ON)_UG</sub>  |     | 25   |     | ns    |

| UGATE turn-off propagation delay | Note 4, 3nF load                 | t <sub>D(OFF)_UG</sub> |     | 25   |     | ns    |

| Lower Gate (LGATE) Output        | ·                                | _(())()                |     |      |     |       |

| Shutdown hold-off time           | Note 4, 3nF load                 | t <sub>PDTS_LG</sub>   |     | 20   | 35  | ns    |

| LGATE rise time                  | Note 4, 3nF load                 | t <sub>r_LG</sub>      |     | 20   |     | ns    |

| LGATE fall time                  | Note 4, 3nF load                 | t <sub>f_LG</sub>      |     | 15   |     | ns    |

| 3-state rising propagation delay | Note 4, 3nF load                 | tTSSHD_LG              |     | 20   | 45  | ns    |

| LGATE turn-on propagation delay  | Note 4, 3nF load                 | t <sub>D(ON)</sub> LG  |     | 20   |     | ns    |

| LGATE turn-off propagation delay | Note 4, 3nF load                 | t <sub>D(OFF)_LG</sub> |     | 20   |     | ns    |

| Output Characteristics (note 3)  |                                  |                        |     | 1    | 1   |       |

| Upper drive source current       | current pulse < 20ns             | I <sub>SRC_UG</sub>    | 4   |      |     | Α     |

| Upper drive source impedance     | Note 5, $I_{SRC_UG} = 2A$        | R <sub>SRC_UG</sub>    |     | 1    |     | Ω     |

| Upper drive sink current         | current pulse < 20ns             | I <sub>SNK_UG</sub>    | 4   |      |     | A     |

| Upper drive sink impedance       | 1                                | R <sub>SNK_UG</sub>    |     | 0.9  | 1.3 | Ω     |

| Lower drive source current       | current pulse < 40ns             | Isrc_LG                | 4   |      |     | A     |

| Lower drive source impedance     | Note 6, $I_{SRC_UG} = 2A$        | R <sub>SRC_LG</sub>    | -   | 1.4  |     | Ω     |

| Lower drive sink current         | current pulse < 40ns             | Isnk_lg                | 4   |      |     | A     |

| Lower drive sink impedance       |                                  | R <sub>SNK_LG</sub>    | · · | 0.9  | 1.3 | Ω     |

#### Table 3. Electrical Characteristics

Notes:

- 4.

- Guaranteed by design, verified during characterization Incremental resistance V<sub>BOOT</sub> V<sub>UG</sub> = 4.3V @ I<sub>SRC</sub> = 2A Incremental resistance V<sub>VCC</sub> V<sub>BG</sub> = 4.4V @ I<sub>SRC</sub> = 2A 5.

- 6.

#### Table 4. Pin Function Description

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                         |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | UGATE  | Upper gate drive output. Connect to the gate of high-side power N-channel MOSFET                                                                                                                                                                                                                    |

| 2     | BOOT   | Floating bootstrap supply pin for the upper gate drive. Connect the bootstrap capacitor between this pin and the PHASE pin. The bootstrap capacitor provides the charge to turn on the upper MOSFET. See the Internal Bootstrap Device section herein for guidance in choosing the capacitor value. |

| 3     | N/C    | No connection                                                                                                                                                                                                                                                                                       |

| 4     | PWM    | The PWM signal is the control input for the driver and is to be connected to the PWM output of the controller. The PWM signal can enter three distinct states during operation. See the 3-state PWM input section herein for further details.                                                       |

| 5     | GND    | Bias and reference ground. All signals are referenced to this node. It is also the power ground return of the driver.                                                                                                                                                                               |

| 6     | LGATE  | Lower gate drive output. Connect to the gate of the low-side power N-channel MOSFET                                                                                                                                                                                                                 |

| 7     | VCC    | This pin supplies power to the upper gate , Its operating range is +6V to +12V. Place a high quality low ESR ceramic capacitor from this pin to GND.                                                                                                                                                |

| 8     | N/C    | No connection                                                                                                                                                                                                                                                                                       |

| 9     | PVCC   | This pin supplies power to the lower gate , Its operating range is +6.7V to +12V. Place a high quality low ESR ceramic capacitor from this pin to GND.                                                                                                                                              |

| 10    | PHASE  | Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin provides a return path for the upper gate drive.                                                                                                                                                     |

| Die p | baddle | Connect pad to the power circuit board power ground plane (GND), use thermal vias                                                                                                                                                                                                                   |

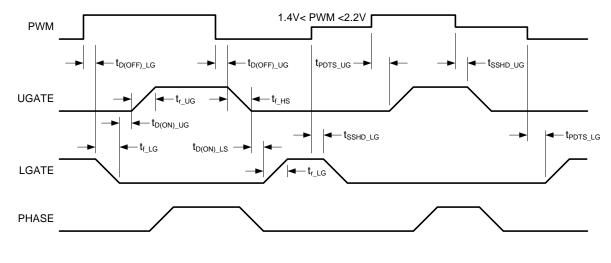

### **Timing Diagram**

### Layout Considerations

The parasitic inductances of the PCB and of the power devices' packaging (both upper and lower MOSFETs) can cause serious ringing, exceeding absolute maximum rating of the devices. Careful layout can help minimize such unwanted stress. The following advice is meant to lead to an optimized layout:

- Keep decoupling loops (PVCC-GND and BOOT-PHASE) as short as possible.

- Minimize trace inductance, especially on lowimpedance lines. All power traces (UGATE, PHASE, LGATE, GND, PVCC) should be short and wide, as much as possible.

- Minimize the inductance of the PHASE node. Ideally, the source of the upper and the drain of the lower

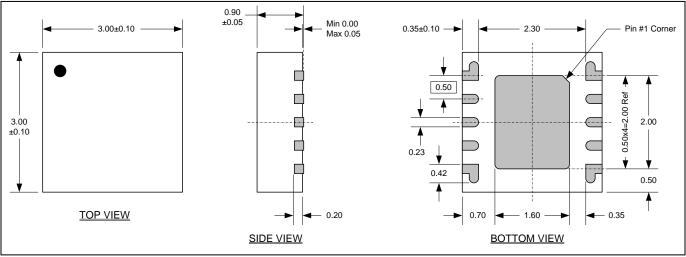

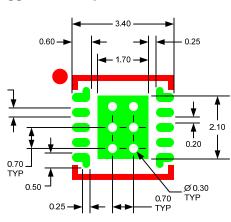

Physical Characteristics (10-lead 3mm x 3mm DFN package)

MOSFET should be as close as thermally allowable.

Minimize the current loop of the output and input power trains. Short the source connection of the lower MOSFET to ground as close to the transistor pin as feasible. Input capacitors (especially ceramic decoupling) should be placed as close to the drain of upper and source of lower MOSFETs as possible.

To optimize heat spreading, copper should be placed directly underneath the IC whether it has an exposed pad or not. The copper area can be extended beyond the bottom area of the IC and/or connected to buried copper plane(s) with thermal vias. This combination of vias for vertical heat escape, extended copper plane, and buried planes for heat spreading allows the IC to achieve its full thermal potential

Figure 3. Physical dimensions.

### Suggested land pattern

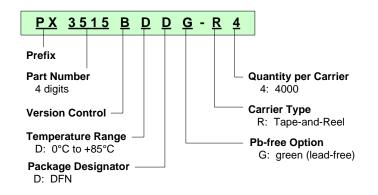

# **Ordering Information**

Printed in the USA/1002/PDF/TK/PS

This document contains characteristic data and other specifications that are subject to change without notice. Customers are advised to confirm information in this datasheet prior to using the information herein or placing an order. Primarion does not assume any liability arising from the application or use of any product or circuit described herein, neither does it convey any license under its patents or any other rights. Primarion products are not designed, intended, or authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications.

©2008, Primarion, Inc. Primarion is a registered trademark of Primarion, Inc. The Primarion logos are trademarks of Primarion, Inc. \*Other names and brands are the property of their respective owners.

2780 Skypark Drive, Suite 100, Torrance, CA 90505 1-310-602-5500 Fax 1-310-602-5559