# Interfacing Cypress MoBL<sup>®</sup> Dual-Port to Intel<sup>®</sup> PXA272 Embedded Processor

#### Introduction

The PXA272 Embedded Processor of the Intel® PCA processor family is an integrated system-on-a-chip microprocessor for high performance, dynamic and low-power portable handheld and handset devices.

The Intel PXA272 processor includes a memory interface that gives designers more flexibility as it supports a variety of external memory types.

CYDM256A16 is an asynchronous MoBL® Dual-Port memory from Cypress Semiconductor. It has a 256-Kbit shared memory array with two 16-bit data buses. The shared memory structure allows independent access from both ports to 32K address locations. The device is available in -35 and -55 speed grades in both commercial and industrial temperature ranges. Internal arbitration logic is also available to decide which port gets access when both ports try to access the same memory location at the same time.

The MoBL Dual-Port can act as an interconnect between two processing elements that share data while operating at different speeds. This application note describes how to interface the CYDM256A16 to the Intel PXA272.

# **External Memory Interface (EMI)**

The Intel PXA272's External Memory Interface is a 16/32-bit interface and it can be configured to gluelessly interface to Cypress low-power MoBL Dual-Ports.

The Cypress MoBL Dual-Port CYDM256A16 has a standard asynchronous SRAM interface. *Table 1* lists the signal connections between Intel PXA272 and Cypress MoBL Dual-Port CYDM256A16.

Table 1. PXA272 & CYDM256A16 Signal Equivalents

| PXA272 Signal<br>(I/O) |     | CYDM256A16<br>Signal (I/O) |             | Function                |  |

|------------------------|-----|----------------------------|-------------|-------------------------|--|

| CSx                    | 0   | CE I                       |             | Chip select             |  |

| WE                     | 0   | R/W                        | I           | Write enable            |  |

| ŌĒ                     | 0   | ŌE                         | OE I Output |                         |  |

| MA[14:0]               | 0   | A[14:0]                    | I           | Address                 |  |

| MD[15:0]               | I/O | DQ[15:0]                   | I/O         | Data                    |  |

| DQM[1]                 | 0   | UB                         | I           | Upper byte enable       |  |

| DQM[0]                 | 0   | LB                         | I           | Lower byte enable       |  |

| RDY                    | I   | BUSY I/O                   |             | Busy Signal             |  |

| GPIOx                  | I   | ĪNT O                      |             | Mailbox Interrupt       |  |

| GPIOx                  | 0   | SFEN I                     |             | Special Function enable |  |

Table 1. PXA272 & CYDM256A16 Signal Equivalents (continued)

| PXA272 Signal<br>(I/O) |   | CYDM256A16<br>Signal (I/O) |   | Function                                             |  |

|------------------------|---|----------------------------|---|------------------------------------------------------|--|

| External Devices       | I | ODR[4:0]                   | 0 | Output Drive Register                                |  |

| External O<br>Devices  |   | IRR[1:0]                   | I | Input Read Register                                  |  |

|                        |   | M/S                        | I | Master/Slave<br>Select: pulled up to V <sub>CC</sub> |  |

### **Layout Guidelines**

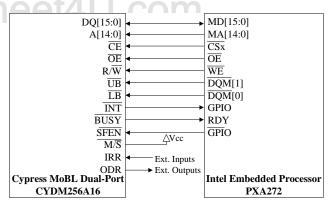

Figure 1 below shows the physical wiring between the PXA272 processor and the MoBL Dual-Port CYDM256A16. Either port of the MoBL Dual-Port may be used. *Table 2* shows the list of unused PXA272 EMI pins.

Figure 1. Wiring Diagram of PXA272 to CYDM256A16

Table 2. Unused Intel PXA272 Signals

| MA[25:15] | NC |  |  |

|-----------|----|--|--|

| CLK       | NC |  |  |

## **Voltage Compatibility**

Cypress MoBL Dual-Ports have operating voltages of 1.8V, 2.5V, and 3.0V, while the Intel PXA272 supports 1.8V, 2.5V and 3.3V I/O supply voltages. Thus, the Cypress MoBL Dual-Ports are compatible with the Intel processor PXA272 when both devices operate at the same voltage.

www.DataSheet4U.com

# **PXA272 Register Settings**

In order to properly interface the PXA272 to the Cypress MoBL Dual-Port, the MSCx register of the processor needs to be configured, while the rest of the registers can be left in their default settings. *Table 3* shows the recommended MSCx register setting, assuming the PXA272 processor is running at 520 MHz and connected to the CYDM256A16-55. The same analysis can be used to interface the processor to Dual-Ports with the -35 speed grade.

Table 3. MSCx Register Settings

| Field | Value | Description                                                             |  |  |

|-------|-------|-------------------------------------------------------------------------|--|--|

| RTx   | 001b  | Type of memory: SRAM                                                    |  |  |

| RBW   | 1b    | Data bus width: 16 bits                                                 |  |  |

| RDF   | 1111b | ROM/SRAM delay first access: 30*<br>Clock pulse equivalent of processor |  |  |

| RDN   | 1111b | ROM/SRAM delay next access: 30* clock pulse equivalent of processor     |  |  |

| RRR   | 101b  | ROM/SRAM Recovery Time                                                  |  |  |

| RBUFF | 0b    | Fast/Slow device: Slow Device                                           |  |  |

## **Timing Considerations**

This section of the application note provides a sample timing analysis of read and write operations with the PXA272 processor and MoBL Dual-Port CYDM256A16-55. Assume that the system clock of the processor runs at the maximum frequency of 520 MHz. Please note that the register setting may vary depending on the speed of the desired memory as well as the system clock frequency (refer to PXA27x Processor Family Developers Manual for detail).

#### **Read Operation**

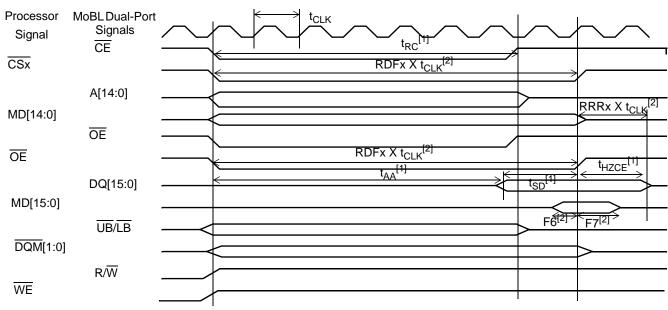

With an internal reference clock of 520 MHz (1.923-ns clock period), the register settings required to set up proper read operations are shown in *Table 3*. RDF (ROM Delay First access), which defines the number of wait states inserted in a read cycle, needs to be 30 times the REF\_CLK clock cycle. This essentially extends the chip select enable duration of a read cycle to 30 x REF\_CLK = 57.7ns. *Figure 2* shows the timing details of a read operation between the PXA272 and MoBL Dual-Port.

To initiate a read operation, the shortest read cycle needs to be at least  $t_{RC}$ . The processor will also need to wait for the maximum of  $t_{AA}$ ,  $t_{ABE}$  and  $t_{ACE}$  for the data to propagate back from the MoBL Dual-Port. The CYDM256A16-55 MoBL Dual-Port has a  $t_{RC}$ = 55 ns,  $t_{AA}$  = 45ns and  $t_{ABE}$  = 45 ns.

Read access time for the SRAM controller is configured through the RDF field of MSCx register. Referring to the Intel documentation:

(RDFx+2)\*(Time period of processor clock) ≥ Read Cycle time of the MoBL Dual-Port.

$\Rightarrow$  RDFx  $\geq$  ((Read Cycle Time of MoBL Dual-Port/Time period of processor clock) -2.

$=> RDFx \ge (55ns/1.923) - 2 = 28.6 - 2 = 26.6.$

=> RDFx > 26.6

Considering the worst case, the decoded value of RDF should be set to 30 for extra timing margin (RDF="1111").

Subsequent read operation:

Before starting a subsequent MoBL Dual-Port read, the processor should wait for at least  $t_{HZCE} = 20$ ns (max). To achieve this, we need to set the RRRx (ROM/SRAM recovery time) field of MSCx register. Referring to the Intel documentation:

$t_{OFF} \ge (RRRx^2 + 1)^* Processor Clock Period.$

Figure 2. Read Cycle

#### Notes:

- Required by the MoBL Dual-Port for proper read.

- 2. Provided by the Processor.

- => RRRx > ((tOFF/Processor Clock Period) 1)/2

- $=> RRRx \ge ((20/1.923) 1)/2 = 4.700$

Considering the worst case, the decoded value of RRR should be set to 5 for extra timing margin (RRR="101").

#### **Write Operation**

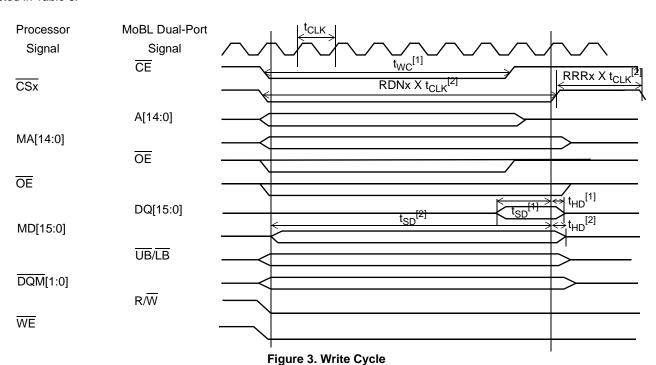

Figure 3 shows the timing detail of a write operation between the PXA272 processor and the MoBL Dual-Port.

In order to write into the MoBL Dual-Port, the minimum write cycle needs to be at least  $t_{WC}$ , while  $t_{AW}$ ,  $t_{SD}$ ,  $t_{HD}$ ,  $t_{SA}$ ,  $t_{HA}$  and  $t_{SCE}$  also need to be satisfied. Since  $t_{SA} = t_{HD} = t_{HA} = 0$ , these parameters should always be satisfied.

With  $t_{WC}$ = 55 ns and  $t_{AW}$  =  $t_{SCE}$  = 45 ns, the processor has to assert the write cycle for at least 55 ns for a correct write operation.

The write cycle time for the SRAM controller is configured through the RDNx (ROM Delay Next access) field of MSCx register. According to Intel documentation:

RDNx + 1 = number of CLK\_MEMs  $\overline{\text{WE}}$  is asserted for write access.

- => RDNx  $\geq$  (Write Cycle Time/ Time period of clock) -1.

- $=> RDNx \ge (55 \text{ ns}/1.923 \text{ ns}) 1 = 28.6 1 = 27.6.$

Considering the worst case, the decoded value of RDN should be set to 30 for extra timing margin (RDN="1111").

#### Data Bus Switching

For CYDM256A16,  $t_{HD} = 0$  ns.

Before starting the next MoBL Dual-Port write, the processor should wait for at least  $t_{\rm HD}$ . Since MoBL Dual-Ports do not support burst mode, timing will always be satisfied by the processor if the MSCx register is configured with the values listed in *Table 3*.

# Configuring the Memory Controller for PXA272

As discussed above, the memory controller must be configured to interface to the MoBL Dual-Port. Apart from the timing parameters, the data width and type of memory are also configured in the MSCx register. According to *Table 3*, using CS1, the upper 16 bits of the MSC0 (address 0x4800008) is set to "0101-1111-1111-1001".

The memory space of the PXA272 processor is divided into 6 slots: CS[5:0]. The MoBI Dual-Port can connect to any of the chip selects. *Table 4* shows the memory address space for each memory slot.

Table 4. Address Space of PXA272 Processor

heet4U.com

| Chip Select Size |       | Function                       |  |

|------------------|-------|--------------------------------|--|

| CS0              | 32 MB | Memory space for async. device |  |

| CS1–CS5          | 64 MB | Memory space for async. device |  |

Table 5 shows the timing parameter values required by the MoBL Dual-Port and the ones provided by the Intel PXA272 processor with the memory controller configuration described above.

Table 5. Timing Compatibility Table after Configuration

| Operation | Parameter         | Dual-Port<br>CYDM16A256 | Relation     | Processor<br>PXA272 |

|-----------|-------------------|-------------------------|--------------|---------------------|

| Read      | t <sub>RC</sub>   | 55ns                    | RDFx= "1111" | 57.9 ns             |

| Read      | t <sub>SA</sub>   | 0ns                     |              | Always satisfied    |

| Read      | t <sub>OHA</sub>  | 5ns                     |              | Always satisfied    |

| Read      | t <sub>ACE</sub>  | 55ns                    | RDFx= "1111" | 57.9 ns             |

| Read      | t <sub>DOE</sub>  | 30ns                    |              | Always satisfied    |

| Read      | t <sub>HZCE</sub> | 20ns                    | RRRx= "101"  | 25 ns               |

| Read      | t <sub>ABE</sub>  | 55ns                    | RDFx= "1111" | 57.9 ns             |

| Write     | t <sub>WC</sub>   | 55ns                    | RDNx= "1111" | 57.9 ns             |

| Write     | t <sub>HA</sub>   | 0ns                     |              | Always satisfied    |

| Write     | t <sub>SA</sub>   | 0ns                     |              | Always satisfied    |

| Write     | t <sub>SCE</sub>  | 25ns                    | RRRx= "101"  | 25 ns               |

| Write     | t <sub>AW</sub>   | 45ns                    | RDNx= "1111" | 57.9 ns             |

| Write     | t <sub>SD</sub>   | 30ns                    |              | Always satisfied    |

| Write     | t <sub>HD</sub>   | 0ns                     |              | Always satisfied    |

#### Conclusion

Systems using a Intel PXA272 processor can easily benefit from the performance and flexibility of a Cypress Dual-Port. As one of the industry's lowest power Dual-Ports, designing in the Cypress MoBL Dual-Port allows the customer to interconnect multiple processors in a system, where power is the most important concern, without having to compromise with performance. As this application note has shown, the Intel PXA272 can interface to the Cypress MoBL Dual-Port seamlessly.

For further information, please visit the Cypress web site at www.cypress.com. The web site also provides the latest data sheets, models, and any related documentation.

#### References

- Cypress Semiconductor, CYDM256A16, CYDM128A16, CYDM064A16, CYDM128A08, CYDM064A08 1.8V, 2.5V, 3.3V 4K/8K/16K x16 and 8K/16K x8 MoBL<sup>®</sup> Dual-Port Static RAM Data sheet, January 2005.

- Intel Inc., PXA272 Processor Design Guide, Literature Number 280000101.pdf.

- Intel inc., PXA27x Processor Family Developers Manual 2800002.pdf.

Intel is a registered trademark of Intel Corporation. MoBL is a registered trademark of Cypress Semiconductor Corporation. All product and company names mentioned in this document are the trademarks of their respective holders.

AN5035 approved kktvmp 3/31/05