# **QPA4605** 5 W, 48 V, 4.5 – 4.6 GHz, GaN PAM

#### **Product Overview**

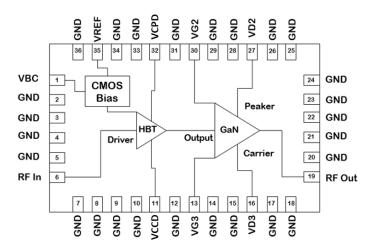

The QPA4605 is an integrated 2-stage Power Amplifier Module designed for massive MIMO applications with 5 W RMS at the device output covering frequency range from 4.5 to 4.6 GHz.

The module is 50  $\Omega$  input and output and requires minimal external components. The module is also compact and offers a much smaller footprint than traditional discrete component solutions.

The QPA4605 incorporates a driver and Doherty final stage delivering high power added efficiency for the entire module at 5 W average power.

RoHS compliant

6 x 10 mm Over Mold Laminate

### **Key Features**

- Operating Frequency Range: 4.5 4.6 GHz

- Operating Drain Voltage: +48 V

- 50 Ω input / output

- Integrated Doherty Final Stage

- Gain at 5W avg.: 25.4dB

- Power Added Efficiency at 5W avg.: 39.7%

- 6x10 mm Plastic Surface Mount Package

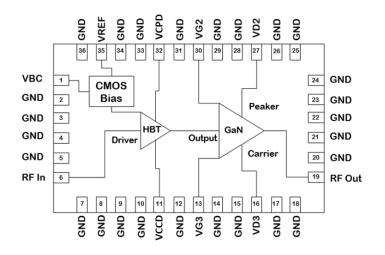

### **Functional Block Diagram**

# **Applications**

- WCDMA / LTE

- · Macrocell Base Station

- · Microcell Base Station

- Small Cell

- Active Antenna

- 5G Massive MIMO

- General Purpose Applications

### **Ordering Information**

| Part Number   | Description            |  |  |

|---------------|------------------------|--|--|

| QPA4605SR     | 7" Reel – 100 Pieces   |  |  |

| QPA4605TR13   | 13" Reel – 2500 Pieces |  |  |

| QPA4605EVB-01 | 4.5 – 4.6GHz EVB       |  |  |

### **Absolute Maximum Ratings**

| Parameter                                                           | Rating        |

|---------------------------------------------------------------------|---------------|

| Breakdown Voltage (BV <sub>DG</sub> )                               | +165 V        |

| Gate Voltage Range (V <sub>G</sub> )                                | −7 to +2 V    |

| Drain Voltage (V <sub>D</sub> )                                     | +55 V         |

| RF Input Power, pulsed, 10%, 100us                                  | +25 dBm       |

| VSWR Mismatch, P3dB Pulse (10% Duty Cycle, 100 µs Width), T = +25°C | 10:1          |

| Storage Temperature                                                 | −65 to +150°C |

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to device may reduce device reliability.

### **Recommended Operating Conditions**

| Parameter                                | Min  | Тур  | Max  | Units |

|------------------------------------------|------|------|------|-------|

| Peaker Gate Voltage (V <sub>G2</sub> )   |      | -4.2 |      | V     |

| Carrier Gate Voltage (V <sub>G3</sub> )  |      | -2.8 |      | V     |

| Supply Voltages HBT (Vcc)                |      | +5.0 |      | V     |

| CMOS Bias Controller (V <sub>BC</sub> )  | +1.8 |      |      | V     |

| CMOS Bias Controller (V <sub>REF</sub> ) | +3.3 | +5.0 | +5.5 | V     |

| Supply Voltages GaN (V <sub>D2,3</sub> ) |      | +48  |      | V     |

| Quiescent Current (I <sub>DQ3</sub> )    |      | 40   |      | mA    |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

### **Electrical Specifications**

| Parameter                                   | Conditions                             | Min  | Тур   | Max   | Units |

|---------------------------------------------|----------------------------------------|------|-------|-------|-------|

| Frequency Range                             |                                        | 4500 |       | 4600  | MHz   |

| Driver Quiescent Current ( Iccd)            |                                        |      | 55    |       | mA    |

| Carrier Quiescent Current (IDQ3)            |                                        |      | 40    |       | mA    |

| Gain <sup>1,2</sup>                         | P <sub>OUT</sub> = 37 dBm              | 23.0 | 25.4  |       | dB    |

| Power Added Efficiency (PAE) <sup>1,2</sup> | P <sub>OUT</sub> = 37 dBm              | 35.5 | 39.7  |       | %     |

| Raw ACLR <sup>1,2</sup>                     | P <sub>OUT</sub> = 37 dBm              |      | -26.5 | -20.0 | dBc   |

| Psat <sup>3</sup>                           | P <sub>IN</sub> = 24 dBm, f = 4600 MHz | 44.6 | 45.7  |       | dBm   |

| V <sub>EN</sub> Low <sup>4</sup>            |                                        | 0    |       | 0.63  | V     |

| V <sub>EN</sub> High <sup>4</sup>           |                                        | 1.17 |       | Vcc   | V     |

Test conditions unless otherwise noted:

- 1.  $V_{REF} = 5V$ ,  $V_{CC} = 5V$ ,  $V_{BC} = 1.8V$ ,  $V_{G2} = V_{G2 Set} 1.5V$ ,  $I_{DO3} = 40mA$ ,  $V_{D2} = V_{D3} = +48V$ ,  $T = +25^{\circ}C$ , using a single-carrier, 20 MHz LTE signal with 7.8 dB PAR at 0.01% CCDF on the reference design fixture.

- 2. Typical parameter value averaged over 4500, 4550, and 4600MHz frequency values.

- 3.  $V_{REF} = 5V$ ,  $V_{CC} = 5V$ ,  $V_{BC} = 1.8V$ ,  $V_{G2} = V_{G2\_Set} 1.5V$ ,  $I_{DQ3} = 40$ mA,  $V_{D2} = V_{D3} = +48V$ ,  $V_{D2} = +25$ °C, using Pulsed CW, 10% Duty Cycle, PW 100us, on the reference design fixture.

- 4. V<sub>EN</sub> guaranteed by design.

#### Thermal Information

| Parameter                                                                        | Conditions                                                                                       | Values | Units |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|-------|

| Thermal Resistance, Peak IR Surface Temperature at Average Power $(\theta_{JC})$ | T <sub>CASE</sub> = +85°C, TCH = 116°C<br>CW: P <sub>DISS</sub> = 7.59 W, P <sub>OUT</sub> = 5 W | 4.08   | °C/W  |

- 1. Thermal resistance is measured to package backside.

- 2. Refer to the following document: GaN Device Channel Temperature, Thermal Resistance, and Reliability Estimates

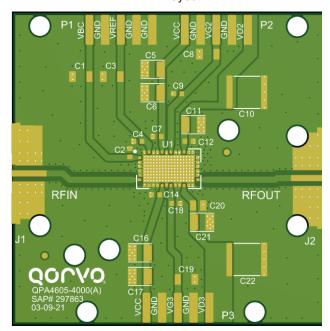

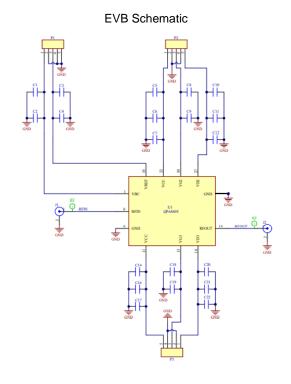

### QPA4605 4.5 - 4.6 GHz Reference Design

#### **EVB** Layout

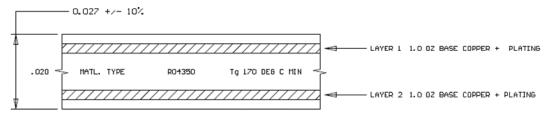

#### PCB Stackup and Material

#### Notes:

- 1. All dimensions are in inches.

- 2. PCB is soldered on a 2 in. x 2 in. copper base plate with 0.25 in. thickness.

### Bill of Materials - QPA4605 4.5 - 4.6 GHz Evaluation Board

| Reference Des.                        | Value    | Description                              | Manufacturer | Part Number          |

|---------------------------------------|----------|------------------------------------------|--------------|----------------------|

| C2, C4, C7, C9, C12,<br>C14, C18, C20 | 0.022 μF | CAP, 0.022µF, 10%, 100V, X7R, 0603       | TDK          | CGA3E2X7R2A223K080AA |

| C3, C8, C19                           | 4.7 µF   | CAP, 4.7µF, 10%, 50V, X7R, 1206          | Murata       | GRM31CR71H475KA12L   |

| C5, C6, C16, C17                      | 10 µF    | CAP, 10µF, 10%, 50V, X7R, 1210           | Murata       | GRM32ER71H106KA12L   |

| C10, C22                              | 10 µF    | CAP, 10µF, 20%, 100V, X7S, 2220          | TDK          | C5750X7S2A106M230KB  |

| C11, C21                              | 4.7 µF   | CAP, 4.7µF, 10%, 100V, X7S, 1206         | Murata       | GRM31CC72A475KE11L   |

| J1, J2                                |          | Connector, SMA, 4-Hole Panel Mount Jack  | Gigalane     | PAF-S00-000          |

| P1, P2, P3                            |          | Connector, HDR, ST, PLRZD, 5-Pin, 0.100" | AMP          | 640454-5             |

| U1                                    |          | 5 W 4.5 – 4.6 GHz PA Module              | Qorvo        | QPA4605              |

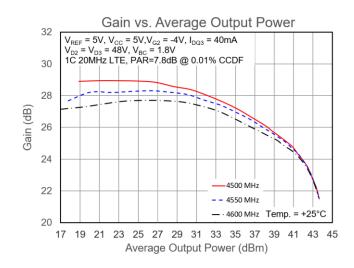

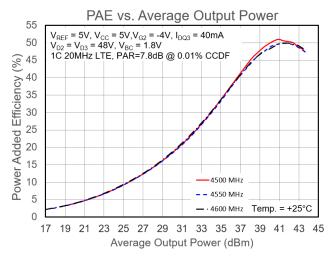

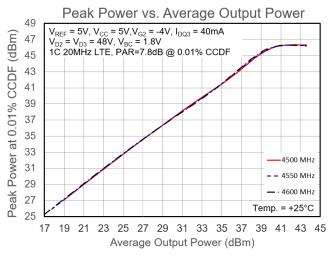

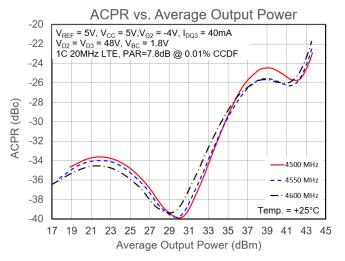

#### **Performance Plots**

Note:

Test conditions unless otherwise noted:  $V_{REF} = 5V$ ,  $V_{CC} = 5V$ ,  $V_{BC} = 1.8V$ ,  $V_{G2} = -4V$ ,  $I_{DO3} = 40$ mA,  $V_{D2} = V_{D3} = 48V$ , T = +25°C, tested using a single-carrier, 20 MHz LTE signal with 7.8 dB PAR at 0.01% CCDF on a reference design fixture.

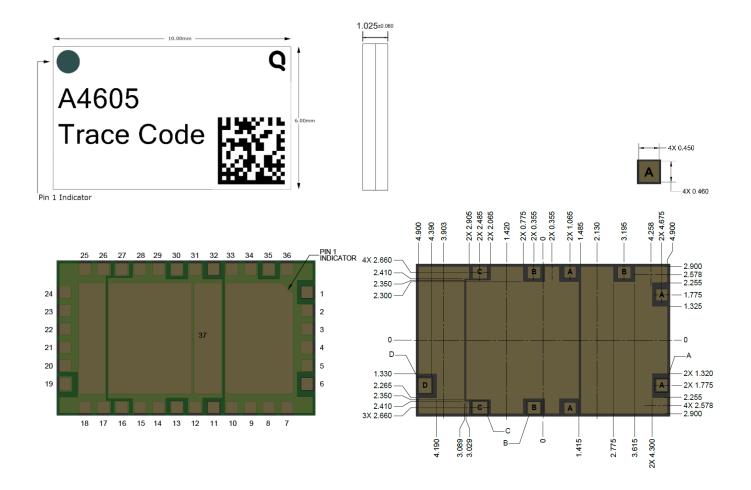

### **Package Marking and Dimensions**

Marking: Qorvo Logo

Part Number - QPA4605

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. General tolerance is ±0.05 unless otherwise shown.

- 3. Part is overmold encapsulated.

- 4. Contact plating is ENEPIG. Au nominal thickness is  $0.095 \pm 0.025 \, \mu m$ .

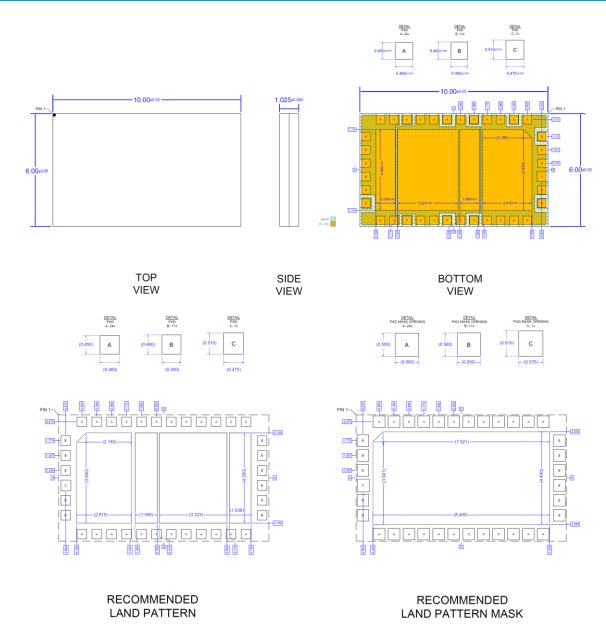

### **PCB Mounting Pattern**

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. General tolerance is ±0.05 unless otherwise shown.

- 3. Part is overmold encapsulated.

- 4. Contact plating is ENEPIG. Au nominal thickness is  $0.095 \pm 0.025 \,\mu m$ .

# **Pad Configuration and Description**

| Pad No.                                                                    | Label | Description                                                                                                                                                                                                   |

|----------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                          | VBC   | CMOS Controller Enable                                                                                                                                                                                        |

| 6                                                                          | RFIN  | RF Input                                                                                                                                                                                                      |

| 11                                                                         | VCCD  | Carrier Amplifier Driver Vcc = +5V                                                                                                                                                                            |

| 13                                                                         | VG3   | Carrier Amplifier, Gate Bias                                                                                                                                                                                  |

| 16                                                                         | VD3   | Carrier Amplifier, Drain Bias                                                                                                                                                                                 |

| 19                                                                         | RFOUT | RF Output, DC Blocked                                                                                                                                                                                         |

| 27                                                                         | VD2   | Peaking Amplifier, Drain Bias                                                                                                                                                                                 |

| 30                                                                         | VG2   | Peaking Amplifier, Gate Bias                                                                                                                                                                                  |

| 32                                                                         | VCPD  | Peaking Amplifier Driver Vcc = +5V                                                                                                                                                                            |

| 35                                                                         | VREF  | CMOS Controller +5V                                                                                                                                                                                           |

| 2,3,4,5,7,8,9,10,12,14,15,17,18,20,21,<br>22,23,24,25,26,28,29,31,33,34,36 | GND   | Internal Grounding, recommend connecting to EPAD ground                                                                                                                                                       |

| EPAD                                                                       | GND   | DC/RF Ground. Must be soldered to EVB Ground Plane over an array of vias for thermal and RF performance. Solder voids under the EPAD will result in excessive junction temperatures causing permanent damage. |

# **Biasing Procedure**

| Bias On                                                        | Bias Off                                       |

|----------------------------------------------------------------|------------------------------------------------|

| 1. Set V <sub>G2</sub> , V <sub>G3</sub> = −5V                 | 1. Set $V_{BC} = 0V$                           |

| 2. Set $V_{REF} = 5V$                                          | 2. Set V <sub>G2</sub> = V <sub>G3</sub> = -5V |

| 3. Set $V_{CC} = 5V$                                           | 3. Set $V_{D2} = V_{D3} = 0V$                  |

| 4. Set $V_{D2} = V_{D3} = 48V$                                 | 4. Set $V_{CC} = V_{REF} = 0V$                 |

| 5. Set I <sub>DQ2</sub> (Peaker) = 80mA                        |                                                |

| <ol> <li>Adjust V<sub>G2</sub> offset voltage −1.5V</li> </ol> |                                                |

| Typical V <sub>G2</sub> after offset is -4.2V                  |                                                |

| 7. Adjust V <sub>G3</sub> to get I <sub>DQ3</sub> = 40mA       |                                                |

| Typical $V_{G3} = -2.8V$                                       |                                                |

| 8. Set $V_{BC} = 1.8V$                                         |                                                |

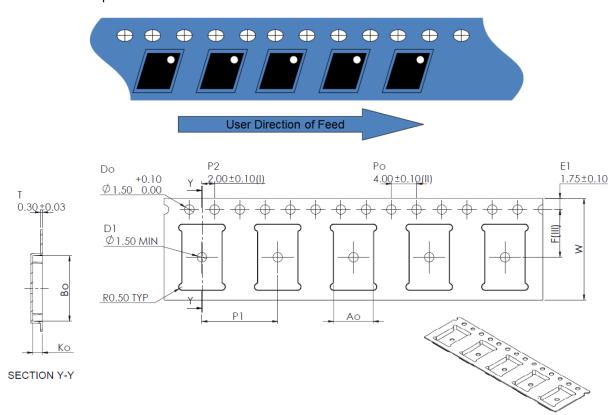

### **Tape and Reel Information – Carrier and Cover Tape Dimensions**

Tape and reel specifications for this part are also available on the Qorvo website. Standard T/R size = 2500 pieces on a 13" reel.

| Feature             | Measure                                  | Symbol | Size (in) | Size (mm) |

|---------------------|------------------------------------------|--------|-----------|-----------|

|                     | Length                                   | A0     | 0.248     | 6.30      |

| Covity              | Width                                    | В0     | 0.406     | 10.30     |

| Cavity              | Depth                                    | K0     | 0.061     | 1.55      |

|                     | Pitch                                    | P1     | 0.472     | 12.00     |

| Centerline Distance | Cavity to Perforation - Length Direction | P2     | 0.079     | 2.00      |

| Centenine Distance  | Cavity to Perforation - Width Direction  | F      | 0.295     | 7.50      |

| Cover Tape Width    |                                          | С      | 0.524     | 13.30     |

| Carrier Tape        | Width                                    | W      | 0.630     | 16.00     |

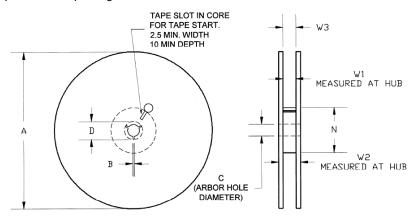

# **Tape and Reel Information – Reel Dimensions**

Packaging reels are used to prevent damage to devices during shipping and storage, loaded carrier tape is typically wound onto a plastic take-up reel. The reel size is 13" diameter. The reels are made from high-impact injection-molded polystyrene (HIPS), which offers mechanical and ESD protection to packaged devices.

| Feature | Measure              | Symbol | Size (in) | Size (mm) |

|---------|----------------------|--------|-----------|-----------|

|         | Diameter             | Α      | 12.992    | 330.00    |

| Flange  | Thickness            | W2     | 0.874     | 22.20     |

|         | Space Between Flange | W1     | 0.661     | 16.80     |

|         | Outer Diameter       | N      | 4.016     | 102.00    |

| Hub     | Arbor Hole Diameter  | С      | 0.512     | 13.00     |

| пир     | Key Slit Width       | В      | 0.079     | 2.00      |

|         | Key Slit Diameter    | D      | 0.787     | 20.00     |

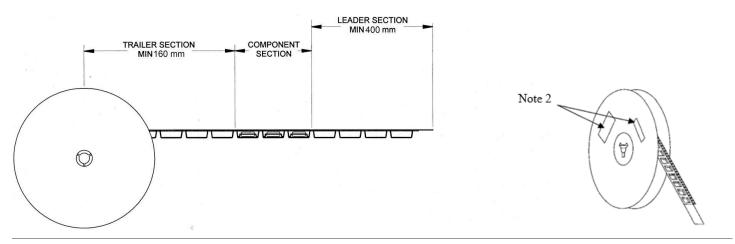

# Tape and Reel Information – Tape Length and Label Placement

- 1. Empty part cavities at the trailing and leading ends are sealed with cover tape. See EIA 481-1-A.

- 2. Labels are placed on the flange opposite the sprockets in the carrier tape.

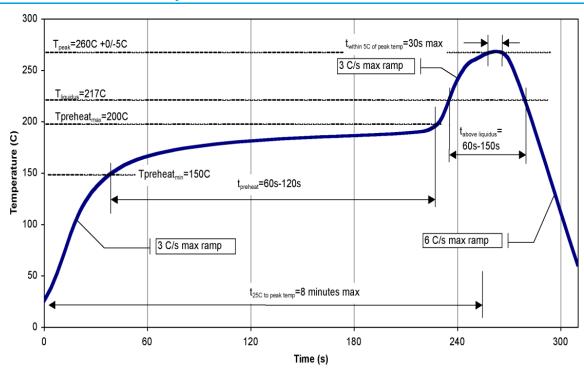

### **Recommended Solder Temperature Profile**

# **Solderability**

Compatible with lead-free (260°C max. reflow temp.) soldering processes.

Package lead plating is ENEPIG. Au nominal thickness is  $0.095 \pm 0.025 \, \mu m$ .

### **Handling Precautions**

| Parameter                      | Rating           | Standard                        |

|--------------------------------|------------------|---------------------------------|

| ESD-Human Body Model (HBM)     | Class 1B (500V)  | ANSI/ESDA/JEDEC Standard JS-001 |

| ESD-Charged Device Model (CDM) | Class C3 (1000V) | ANSI/ESDA/JEDEC Standard JS-002 |

| MSL-Moisture Sensitivity Level | Level 3          | IPC/JEDEC Standard J-STD-020    |

### **RoHS Compliance**

This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive 2015/863/EU.

This product also has the following attributes:

- Halogen Free (Chlorine, Bromine)

- · Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>O<sub>2</sub>) Free

- PFOS Free

- SVHC Free

#### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations:

Web: <u>www.qorvo.com</u> Tel: 1-844-890-8163

Email: <a href="mailto:customer.support@qorvo.com">customer.support@qorvo.com</a>

# **Important Notice**

The information contained in this Data Sheet and any associated documents ("Data Sheet Information") is believed to be reliable; however, Qorvo makes no warranties regarding the Data Sheet Information and assumes no responsibility or liability whatsoever for the use of said information. All Data Sheet Information is subject to change without notice. Customers should obtain and verify the latest relevant Data Sheet Information before placing orders for Qorvo® products. Data Sheet Information or the use thereof does not grant, explicitly, implicitly or otherwise any rights or licenses to any third party with respect to patents or any other intellectual property whether with regard to such Data Sheet Information itself or anything described by such information.

DATA SHEET INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Without limiting the generality of the foregoing, Qorvo® products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death. Applications described in the Data Sheet Information are for illustrative purposes only. Customers are responsible for validating that a particular product described in the Data Sheet Information is suitable for use in a particular application.

© 2022 Qorvo US, Inc. All rights reserved. This document is subject to copyright laws in various jurisdictions worldwide and may not be reproduced or distributed, in whole or in part, without the express written consent of Qorvo US, Inc. | QORVO® is a registered trademark of Qorvo US, Inc.