#### PRELIMINARY

# QT60325, QT60485, QT60645

## 32, 48, 64 Key QMatrix™ Keypanel Sensor ICs

- Advanced second generation QMatrix controllers

- Up to 32, 48 or 64 touch keys through any dielectric

- Panel thicknesses to 5 cm or more

- 100% autocal for life no adjustments required

- Keys individually adjustable for sensitivity, response time, and many other critical parameters

- Mix and match key sizes & shapes in one panel

- Passive matrix no components at the keys

- Moisture suppression capable

- AKS™ Adjacent Key Suppression feature

- Synchronous noise suppression

- Sleep mode with wake pin

- SPI Slave or Master/Slave interface to a host controller

- Low overhead communications protocol

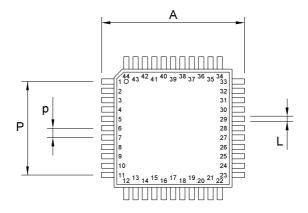

- 44-pin TQFP package

## **APPLICATIONS**

❖ Security keypanels

**❖** Appliance controls

❖ ATM machines

Automotive panels

❖ Industrial keyboards

❖ Outdoor keypads

❖ Touch-screens

❖ Machine tools

The QT60325, QT60485, and QT60645 digital charge-transfer ("QT") QMatrix™ ICs are designed to detect human touch on up to 32, 48, or 64 keys respectively using a scanned, passive X-Y matrix. It will project the keys through almost any dielectric, e.g. glass, plastic, stone, ceramic, and even wood, up to thicknesses of 5 cm or more. The touch areas are defined as simple 2-part interdigitated electrodes of conductive material, like copper or screened silver or carbon deposited on the rear of a control panel. Key sizes, shapes and placement are almost entirely arbitrary; sizes and shapes of keys can be mixed within a single panel of keys and can vary by a factor of 20:1 in surface area. The sensitivity of each key can be set individually via simple functions over the SPI port, for example via Quantum's QmBtn program. Key setups are stored in an onboard eeprom and do not need to be reloaded with each power-up.

These ICs are designed specifically for appliances, electronic kiosks, security panels, portable instruments, machine tools, or similar products that are subject to environmental influences or even vandalism. They permit the construction of 100% sealed, watertight control panels that are immune to humidity, temperature, dirt accumulation, or the physical deterioration of the panel surface from abrasion, chemicals, or abuse. To this end the devices contain Quantum-pioneered adaptive self-calibration, drift compensation, and digital filtering algorithms that make the sensing function robust and survivable. The devices use short dwell times and Quantum's patent-pending AKS™ feature to permit operation in wet environments.

The parts use a passive key matrix, dramatically reducing cost over older technologies that require an ASIC for every key. The key-matrix can be made of standard flex material (e.g. Silver on PET plastic) or ordinary PCB material to save cost.

External circuitry consists of an opamp, R2R ladder-DAC network, a common PLD, a FET switch, and a small number of resistors and capacitors which can fit into a footprint of roughly 8 sq. cm (1.5 sq. in). Control and data transfer is via a SPI port which can be configured in either a Slave or Master/Slave mode.

QT60xx5 ICs make use of an important new variant of charge-transfer sensing, transverse charge-transfer, in a matrix format that minimizes the number of required scan lines to provide a high economy of scale.

#### **AVAILABLE OPTIONS**

| T <sub>A</sub>  | TQFP       |

|-----------------|------------|

| 0°C to +70°C    | QT60325-S  |

| 0°C to +70°C    | QT60485-S  |

| 0°C to +70°C    | QT60645-S  |

| -40°C to +105°C | QT60325-AS |

| -40°C to +105°C | QT60485-AS |

| -40°C to +105°C | QT60645-AS |

## **Contents**

|   | •                                    |    |

|---|--------------------------------------|----|

| 1 | Overview                             | 4  |

|   | 1.1 Field Flows                      | 4  |

|   | 1.2 Circuit Model                    |    |

|   | 1.2 Official Wooder                  | 4  |

|   | 1.3 Matrix Configuration             | 5  |

|   | 1.4 Communications                   | 5  |

| _ |                                      |    |

| 2 | Signal Processing                    |    |

|   | 2.1 Negative Threshold               | 5  |

|   | 2.2 Positive Threshold               | 6  |

|   |                                      |    |

|   | 2.3 Hysteresis                       | 6  |

|   | 2.4 Drift Compensation               | 6  |

|   |                                      |    |

|   | 2.5 Detection Recalibration Delay    |    |

|   | 2.6 Detect Integrator ('DI')         | 7  |

|   | 2.7 Positive Recalibration Delay     | 7  |

|   | 2.7 T OSITIVE RECUMBRATION Delay     |    |

|   | 2.8 Reference Guardbanding           | 7  |

|   | 2.9 Adjacent Key Suppression (AKS™)  | 8  |

|   | 2.10 Full Recalibration              |    |

|   | 2.10 Tuli Necalibration              | 0  |

|   | 2.11 Boundary Error Reporting        | 8  |

|   | 2.12 Device Status & Reporting       | 8  |

| _ |                                      |    |

| 3 | Circuit Operation                    |    |

|   | 3.1 Part Differences                 | 9  |

|   | 3.2 Matrix Scan Sequence             | ā  |

|   |                                      |    |

|   | 3.3 Signal Path                      |    |

|   | 3.4 'X' Electrode Drives             | 9  |

|   | 3.4.1 RFI From X Lines               |    |

|   | 0.4.114 7710117                      | 9  |

|   | 3.4.2 Noise Coupling Into X lines    | 12 |

|   | 3.5 'Y' Gate Drives                  | 12 |

|   | 3.5.1 RFI From Y Lines               |    |

|   | 5.5.TRETTION TEMES                   | 12 |

|   | 3.5.2 Noise Coupling Into Y Lines    | 12 |

|   | 3.6 Burst Length & Sensitivity       | 12 |

|   | 3.7 Intra-Burst Spacing              |    |

|   |                                      |    |

|   | 3.8 Burst Spacing                    | 12 |

|   | 3.9 PLD Circuit and Charge Sampler   | 13 |

|   | 3.10 Opamps                          | 12 |

|   | 3.10 Opanips                         | 13 |

|   | 3.11 Sample Capacitors               | 13 |

|   | 3.12 R2R Resistor Ladder             |    |

|   |                                      |    |

|   | 3.13 Water Film Suppression          | 14 |

|   | 3.14 Reset Input                     | 14 |

|   | 3.15 Oscillator                      | 14 |

|   | 0.10 Coomator                        | 17 |

|   | 3.16 Startup / Calibration Times     | 14 |

|   | 3.17 Sleep_Wake / Noise Sync         | 14 |

|   | 3.18 LED / Alert Output              | 15 |

|   |                                      |    |

|   | 3.19 CSR Drive Polarity              | 15 |

|   | 3.20 Oscilloscope Sync               | 15 |

|   | 3.21 Power Supply and PCB Layout     | 15 |

|   | o.21 Tower ouppry and Tob Edyout     | 10 |

|   | 3.22 ESD / Noise Considerations      |    |

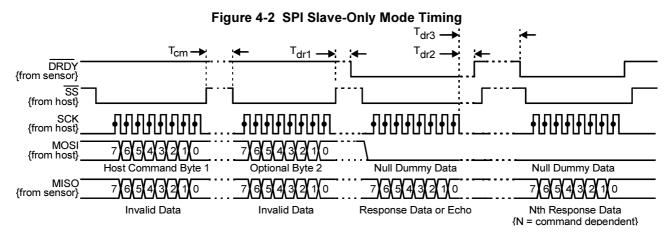

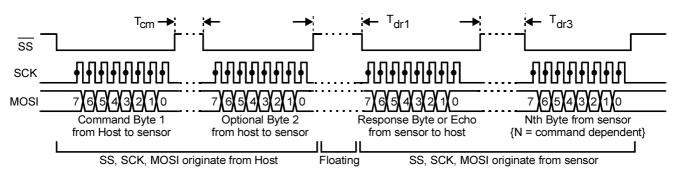

| 4 | Serial Interface                     | 16 |

|   | 4.1 Serial Port specifications       | 16 |

|   | 4.0 Pertend One Specifications       | 10 |

|   | 4.2 Protocol Overview                | 16 |

|   | 4.3 SPI Slave-Only Mode              | 16 |

|   |                                      | 18 |

|   |                                      |    |

|   | 4.5 Sensor Echo and Data Response    | 19 |

|   | 4.6 Eeprom Corruption                | 19 |

| _ | Commands & Functions                 |    |

| J | 5.4.5: 0.00                          |    |

|   | 5.1 Direction Commands               | 20 |

|   | g 0x67 - Get Command                 | 20 |

|   | 0.70 0.40                            |    |

|   |                                      |    |

|   | 5.2 Scope Commands                   |    |

|   | s 0x73 - Specific Key Scope          | 21 |

|   | S 0x53 - All Keys Scope              | 21 |

|   | 0.70 Part Kara Ocean                 | 21 |

|   | x 0x78 - Row Keys Scope              | 21 |

|   | y 0x79 - Column Keys Scope           | 21 |

|   | 5.3 Status Commands                  |    |

|   |                                      |    |

|   | 0 0x30 - Signal for Single Key       | 21 |

|   | 1 0x31 - Delta Signal for Single Key | 21 |

|   |                                      |    |

| 2                                                                         | 0x32 - Reference Value                  | 21 |

|---------------------------------------------------------------------------|-----------------------------------------|----|

| 3                                                                         |                                         |    |

| 4                                                                         |                                         | 21 |

|                                                                           | 0x34 - Cz State                         | 21 |

| 5                                                                         | 0x35 - Detection Integrator Counts      | 22 |

| 6                                                                         | 0x36 - Eeprom Checksum                  | 22 |

| 7                                                                         | 0x37 - General Device Status            | 22 |

| <s,< td=""><td>o&gt; 0x20 - Signal Levels for Group</td><td>22</td></s,<> | o> 0x20 - Signal Levels for Group       | 22 |

| !                                                                         | 0x21 - Delta Signals for Group          | 22 |

| "                                                                         | 0x22 - Reference Levels for Group       | 22 |

| #                                                                         | 0x23 - R2R Offset for Group             | 22 |

| \$                                                                        | 0x24 - Charge Cancellation for Group    | 22 |

| %                                                                         |                                         | 22 |

| е                                                                         | 0x65 - Error Code for Selected Key      | 23 |

| k                                                                         | 0x6B - Reporting of First Touched Key   | 23 |

| K                                                                         | 0x4B - Key Touch Reporting for Group    | 24 |

|                                                                           |                                         |    |

|                                                                           |                                         | 24 |

| AD.                                                                       | 0x01 - Negative Detect Threshold        | 24 |

| <br>                                                                      | 0x02 - Positive Detect Threshold        | 24 |

| ^C                                                                        | 0x03 - Negative Threshold Hysteresis    | 25 |

| ^D                                                                        | 0x04 - Positive Threshold Hysteresis    | 25 |

| ^E                                                                        | 0x05 - Dwell Time in Machine Cycles     | 25 |

|                                                                           | 0x07 - Burst Spacing                    | 25 |

| ^H                                                                        | 0x08 - Negative Drift Compensation Rate | 26 |

|                                                                           | 0x09 - Positive Drift Compensation Rate | 26 |

|                                                                           | 0x0A - Detect Integrator Limit          | 26 |

| ^K                                                                        | 0x0B - Positive Recalibration Delay     | 26 |

|                                                                           | 0x0C - Negative Recalibration Delay     | 26 |

|                                                                           | 0x0D - Intra-Burst Pulse Spacing        | 27 |

| ۸۸/                                                                       |                                         |    |

|                                                                           |                                         | 27 |

| ^0                                                                        | 0x0F - Negative Reference Error Band    | 27 |

|                                                                           | 0x10 - Adjacent Key Suppression ('AKS') | 27 |

|                                                                           | pervisory / System Functions            | 28 |

| 6                                                                         | 0x36 - Eeprom Checksum                  | 28 |

| D                                                                         | 0x44 - DAC Test                         | 28 |

| L                                                                         | 0x4C - Lock Reference Levels            | 28 |

| b                                                                         | 0x62 - Recalibrate Keys                 | 28 |

| 1                                                                         | 0x6C - Return Last Command Character    | 28 |

| r                                                                         | 0x72 - Reset Device                     | 28 |

| V                                                                         |                                         | 29 |

| W                                                                         |                                         | 29 |

| Z                                                                         | 0x5A - Enter Sleep                      | 29 |

| _<br>^Q                                                                   |                                         | 29 |

| ^R                                                                        |                                         |    |

| ^S                                                                        |                                         | 29 |

| ^T                                                                        |                                         | 29 |

|                                                                           |                                         | 30 |

| ^ <i>U</i>                                                                |                                         | 30 |

| ^ <i>V</i>                                                                |                                         | 30 |

|                                                                           | / 0x17 - Noise Sync                     | 30 |

| 5.6 Fu                                                                    | nction Summary Table                    | 32 |

|                                                                           | ning Limitations                        | 34 |

| 6 PLD S                                                                   | ource Listing                           | 35 |

| 7 Electri                                                                 | cal Specifications                      | 36 |

|                                                                           | solute Maximum Specifications           | 36 |

| 7.2 Re                                                                    | commended operating conditions          | 36 |

|                                                                           | Specifications                          | 36 |

| 7.3 DC                                                                    |                                         | 36 |

|                                                                           | ıximum Drdy Response Delays             | 37 |

|                                                                           |                                         |    |

|                                                                           | ınical                                  | 38 |

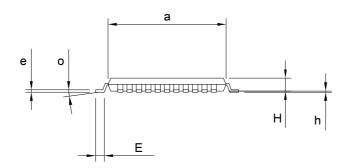

|                                                                           | mensions                                | 38 |

|                                                                           | ırking                                  | 38 |

| 9 Index                                                                   |                                         | 39 |

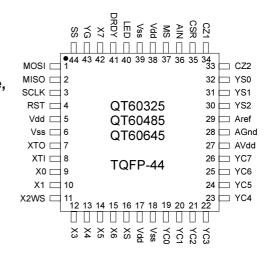

Table 1.1 Device Pin List

| Pin | Name       | Туре   | Description                                                                                              |

|-----|------------|--------|----------------------------------------------------------------------------------------------------------|

|     | MOOL       |        | Master-Out / Slave In SPI line. In Master/Slave SPI mode is used for both communication directions.      |

| 1   | MOSI       | I/O PP | In Slave SPI mode is the data input (in only).                                                           |

|     | MICO       | I/O PP | Master-In / Slave Out SPI line. Not used in Master/Slave SPI mode.                                       |

| 2   | MISO       | 1/O PP | In Slave mode outputs data to host (out only).                                                           |

| 3   | SCK        | I/O PP | SPI Clock. In Master mode is an output; in Slave mode is an input                                        |

| 4   | RST        | ı      | Reset input, active low reset                                                                            |

| 5   | Vdd        | Pwr    | +5 supply                                                                                                |

| 6   | Vss        | Pwr    | Ground                                                                                                   |

| 7   | хто        | 0      | Oscillator drive output. Connect to resonator or crystal. Can drive a charge pump circuit for Vee supply |

| 8   | XTI        | ı      | Oscillator drive input. Connect to resonator or crystal, or external clock source.                       |

| 9   | X0         | 0      | X0 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 10  | X1         | 0      | X1 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 11  | X2WS       | 0      | X2 Drive matrix scan / R2R DAC Ladder drive / Wake from Sleep / Sync to noise source                     |

| 12  | Х3         | 0      | X3 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 13  | X4         | 0      | X4 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 14  | X5         | 0      | X5 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 15  | X6         | 0      | X6 Drive matrix scan / R2R DAC Ladder drive                                                              |

| 16  | XS         | 0      | X summation / R2R DAC Ladder drive                                                                       |

| 17  | Vdd        | Pwr    | +5 supply                                                                                                |

| 18  | Vss        | Pwr    | Ground                                                                                                   |

| 19  | YC0        | 0      | Y 0 Line clamp control                                                                                   |

| 20  | YC1        | 0      | Y 1 Line clamp control                                                                                   |

| 21  | YC2        | 0      | Y 2 Line clamp control                                                                                   |

| 22  | YC3        | 0      | Y 3 Line clamp control                                                                                   |

| 23  | YC4        | 0      | Y 4 Line clamp control                                                                                   |

| 24  | YC5        | 0      | Y 5 Line clamp control                                                                                   |

| 25  | YC6        | 0      | Y 6 Line clamp control                                                                                   |

| 26  | YC7        | 0      | Y 7 Line clamp control                                                                                   |

| 27  | AVdd       | Pwr    | +5 supply for analog sections                                                                            |

| 28  | AGnd       | Pwr    | Analog ground                                                                                            |

| 29  | Aref       | Pwr    | Analog reference, connect to Vcc                                                                         |

| 30  | YS2        | 0      | Transfer switch control bit 2                                                                            |

| 31  | YS1        | 0      | Transfer switch control bit 1                                                                            |

| 32  | YS0        | 0      | Transfer switch control bit 0                                                                            |

| 33  | CZ2        | 0      | Charge cancellation drive for CZ2 capacitor                                                              |

| 34  | CZ1        | 0      | Charge cancellation drive for CZ1 capacitor                                                              |

| 35  | CSR        | 0      | Charge integrator reset line. Active high or active low (select polarity via Setups)                     |

| 36  | Ain        | I      | Analog input from amplifier                                                                              |

| 37  | MS         | I/O OD | SPI Mode / Sync out. Connect via 10k resistor to Vcc or Gnd for mode. Scope sync yields Pulse.           |

| 38  | Vdd        | Pwr    | +5 supply                                                                                                |

| 39  | Vss        | Pwr    | Ground                                                                                                   |

| 40  | LED        | 0      | Active low LED status drive / Activity indicator                                                         |

| 41  | DRDY       | O OD   | Data ready output for Slave SPI mode; active low                                                         |

| 42  | <b>X</b> 7 | 0      | X7 Drive matrix scan                                                                                     |

| 43  | YG         | 0      | Y gate control to drive Y dwell timing circuit                                                           |

| 44  | SS         | IO OD  | Slave select for SPI direction control; active low                                                       |

I/O: I = Input

O = Output

Pwr = Power pin

I/O = Bi-directional line

PP = Push Pull output drive

OD = Open drain output drive

## 1 Overview

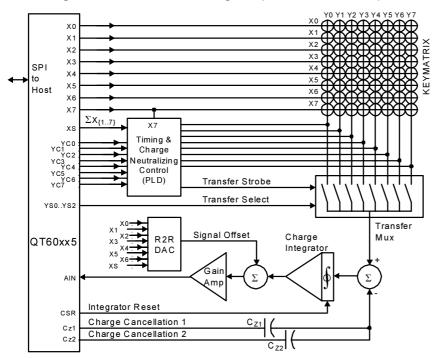

QMatrix devices are digital burst mode charge-transfer (QT) sensors designed specifically for matrix geometry touch controls; they include all signal processing functions necessary to provide stable sensing under a wide variety of changing conditions. Only a few external parts are required for operation. The entire circuit can be built within 8 square centimeters of PCB area.

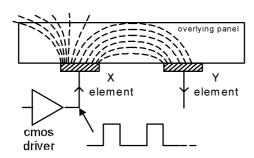

Figure 1-1 Field flow between X and Y elements

QMatrix devices include charge cancellation methods which allow for a wide range of key sizes and shapes to be mixed together in a single touch panel. These features permit the construction of entirely new classes of keypads never before contemplated, such as touch-sliders, back-illuminated keys, and complex warped panel shapes, all at very low cost.

The devices use an SPI interface running at up to 1.5MHz to allow key data to be extracted and to permit individual key parameter setup. The interface protocol uses simple single byte commands and responds with single byte responses in most cases. The command structure is designed to minimize the amount of data traffic while maximizing the amount of information conveyed.

In addition to normal operating and setup functions the device can also report back actual signal strengths and error codes.

QmBtn software for the PC can be used to program the IC as well as read back key status and signal levels in real time.

QMatrix parts employ transverse charge-transfer ('QT') sensing, a new technology that senses changes in the charge forced across an electrode by a digital edge.

The parts are electrically identical with the exception of the number of keys which may be sensed.

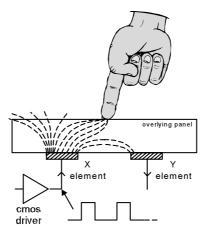

#### 1.1 Field Flows

Figure 1-1 shows how charge is transferred across an electrode set to permeate the overlying panel material; this charge flow exhibits a high dQ/dt during the

Figure 1-2 Sample Electrode Geometries

PARALLEL LINES

**SERPENTINE**

CDIDAI

edge transitions of the X drive pulse. The charge emitted by the X electrode is partly received onto the corresponding Y electrode which is then processed. The parts use 8 'X' edge-driven rows and 8 'Y' sense columns to permit up to 64 keys. Keys are typically formed from interleaved conductive traces on a substrate like a flex circuit or PCB (Figure 1-2).

The charge flows are absorbed by the touch of a human finger (Figure 1-3) resulting in a decrease in coupling from X to Y. Thus, received signals decrease or go negative with respect to the reference level during a touch.

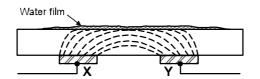

Water films cause the coupled fields to increase slightly, making water films easy to distinguish from touch.

#### 1.2 Circuit Model

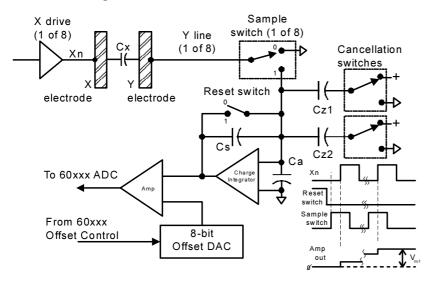

An electrical circuit model is shown in Figure 1-5. The coupling capacitance between X and Y electrodes is represented by Cx. While the reset switch is open, a sample switch is gated so that it transfers charge flows only from the rising edge of X into a charge integrator. On the falling edge of X, the switch connects the Y line to ground to allow the charge across Cx to neutralize to zero. The voltage change on the output of the charge integrator after each X edge is quite small, on the order of a few tens of millivolts. Changes due to touch are typically under 0.1% of total integrator

voltage. The X pulse can be repeated in a burst of up to 64 pulses to increase the change in integrator output voltage due to touch during an acquire (Section 3.6) to increase gain.

The charge detector is an opamp configured as an integrator with a reset switch; this creates a virtual ground input, making the Y lines appear low impedance when the sample switch is closed. This configuration effectively eliminates cross-coupling among Y lines while greatly lowering susceptibility to EMI. The circuit is also highly immune to capacitive loading on the Y lines, since stray C from Y to ground appears merely as a small parallel capacitance across a virtual ground.

The circuit uses an 8-bit ADC, with a subranging structure to effectively deliver a 14-bit total conversion 'space' (see Figure 1-6 and Section 3.3). In this way the circuit can tolerate very large

Figure 1-4 Fields With a Conductive Film

Figure 1-5 QT60xx5 Basic Circuit Model

absolute signals yet still respond to very small signal changes. Subranging is provided by two offset mechanisms which can be thought of as 'coarse' and 'fine' offsets.

The 'coarse' method uses one or two switched Cz capacitors to subtract charge from the charge integrator to create up to two step offsets, to bring the analog signal back to a more reasonable level. This action occurs during the course of the burst.

The 'fine' method of offset uses an 8-bit R2R ladder DAC driven by the X drive lines to create an offset in the amplifier stage. The DAC is driven after the burst has ceased and the charge accumulated, so there is no conflict in this dual-use of the X lines.

Figure 1-6 Circuit Block Diagram (8x8 Matrix Shown)

Short sample gate dwell times after the X edges will limit the effect of moisture spreading from key to key by taking advantage of the RC filter-like nature of continuous films; a short dwell time will limit the time that the charge has to travel through the impedance of the film (Section 3.13). This effect is independent of the frequency of burst repetition, intra-burst pulse spacing, or X drive pulse width.

Burst mode operation permits reduced power consumption and reduces RF emissions, while permitting excellent response time.

#### 1.3 Matrix Configuration

The matrix scanning configuration is shown in Figure 1-5. The 'X' drives are sequentially pulsed in groupings of bursts; an 8:1 analog mux acts as the sample switch for all 'Y' lines. At the intersection of each 'X' and 'Y' line in the matrix itself, where a key is

desired, should be an interdigitated electrode set similar to those shown in Figure 1-2. The outermost electrode or the key border should always be connected to an 'X' drive; flooding the area around keys with X fill to a width of up to 10mm can help in suppressing moisture films further.

Although it is referred to as a 'matrix', there is no restriction on where individual keys can be located. The term 'matrix' refers to the electrical configuration of keys, not the physical arrangement. Consult Quantum for application assistance on key design.

#### 1.4 Communications

The device uses two variants of SPI communications, Slave-only and Master-Slave. Over this interface is a

command and data transfer structure designed for high levels of flexibility using minimal numbers of bytes. For more information see Sections 4 and 5.

**Device variations:** Refer to Section 3.1 for differences between the parts covered by this datasheet.

## 2 Signal Processing

The devices calibrate and process all signals using a number of algorithms specifically designed to provide for high survivability in the face of adverse environmental challenges. They provide a large number of processing options which can be user-selected to implement very flexible, robust keypanel solutions.

#### 2.1 Negative Threshold

See also command ^A, page 24

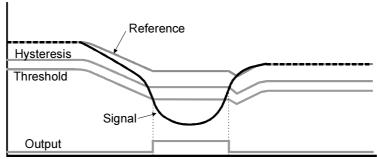

The negative threshold value is established relative to a key's signal reference value. The threshold is used to determine key touch when crossed by a negative-going signal swing after having been filtered by

the detection integrator (Section 2.6). Larger absolute values of threshold desensitize keys since the signal must travel farther in order to cross the threshold level. Conversely, lower thresholds make keys more sensitive.

As Cx and Cs drift, the reference point drift-compensates for these changes at a user-settable rate (Section 2.4); the threshold level is recomputed whenever the reference point moves, and thus it also is drift compensated.

The negative threshold is programmed on a per-key basis using the setup process described in Section 5.

#### 2.2 Positive Threshold

See also command ^B, page 24

The positive threshold is used to provide a mechanism for recalibration of the reference point when a key's signal moves abruptly to the positive. These transitions are described more fully in Section 2.7.

Positive threshold levels are programmed in using the setup process described in Section 5 on a per-key basis.

#### 2.3 Hysteresis

See also command ^C and ^D, page 25

Refer to Figure 2-1. QT60xx5 ICs employ programmable hysteresis levels of 12.5%, 25%, or 50% of the delta between the reference and threshold levels. There are different hysteresis settings for positive and negative thresholds which can be set by the user. The hysteresis is a percentage of the distance from the threshold level back towards the reference, and defines the point at which the detection will drop out. A percentage of 12.5% is less hysteresis than 25%, and the 12.5% hysteresis point is closer to the threshold level than to the reference level.

The hysteresis levels are set for all keys only; it is not possible to set the hysteresis differently from key to key on either the positive or negative hysteresis levels.

#### 2.4 Drift Compensation

See also commands ^H, ^I, page 26

Signals can drift because of changes in Cx and Cs over time and temperature. It is crucial that such drift be compensated, else false detections and sensitivity shifts can occur. The QT60xx5 compensates for drift using setups, ^H and ^I.

Drift compensation (Figure 2-1) is performed by making the reference level track the raw signal at a slow rate, but only while there is no detection in effect. The rate of adjustment must be performed slowly, otherwise legitimate detections could be ignored. The devices drift compensate using a slew-rate limited change to the reference level; the threshold and hysteresis values are slaved to this reference.

When a finger is sensed, the signal falls since the human body acts to absorb charge from the cross-coupling between X and Y lines. An isolated, untouched foreign object (a coin, or a water film) will cause the signal to rise very slightly due to an enhancement of coupling. This is contrary to the way most capacitive sensors operate.

Once a finger is sensed, the drift compensation mechanism ceases since the signal is legitimately detecting an object. Drift compensation only works

when the signal in question has not crossed the negative threshold level (Section 2.1).

The drift compensation mechanism can be made asymmetric if desired; the drift-compensation can be made to occur in one direction faster than it does in the other simply by setting ^H and ^I to different settings.

Specifically, drift compensation should be set to compensate faster for increasing signals than for decreasing signals. Decreasing signals should not be compensated quickly, since an approaching finger could be compensated for partially or entirely before even touching the touch pad. However, an obstruction over the sense pad, for which the sensor has already made full allowance for, could suddenly be removed leaving the sensor with an artificially suppressed reference level and thus become insensitive to touch. In this latter case, the sensor should compensate for the object's removal by raising the reference level relatively quickly.

The drift compensation rate can be set for each key individually, and can also be disabled completely if desired on a per-key basis.

Drift compensation and the detection time-outs (Section 2.5) work together to provide for robust, adaptive sensing. The time-outs provide abrupt changes in reference calibration depending on the duration of the signal 'event'.

Drift compensation can result in reference levels that are at the boundaries of the 8-bit signal window. When this occurs, saturation is reached and the drift compensation process stops. One of two error flags is set when the signal approaches either end of the signal window; it is up to the host to read these flags and induce a full recalibration via a recalibration command at that time (Section 2.10 and command 'b', page 28) for the key in question.

#### 2.5 Detection Recalibration Delay

See also command ^L, page 26

If a foreign object contacts a key the key's signal may change enough in the negative direction, the same as a normal touch, to create an unintended detection. When this happens it is usually desirable to cause the key to be recalibrated in order to restore its function after a time delay of some seconds.

The Negative Recal Delay timer monitors this detection duration; if a detection event exceeds the timer's setting, the key will be fast-recalibrated within its current 8-bit window. This form of recalibration is simply one of setting Reference = Signal, and does not affect Offset or Cz state; as a result this form of recalibration requires only one burst spacing interval

Figure 2-1 Thresholds and Drift Compensation

o accomplish. Only a full recalibration via a reset or a recalibration command will perform a complete recalibration involving both the R2R Offset and Cz capacitors (Section 2.10).

After a fast recalibration has taken place, the affected key will once again function normally even if it is still being contacted by the foreign object. This feature is set on a per-key basis using setup ^L. It can be disabled if desired by setting this parameter to zero, so that it will not recalibrate automatically.

## 2.6 Detect Integrator ('DI')

See also command \(^{J}\), page 26

To suppress false detections caused by spurious events like electrical noise, the QT60xx5 incorporates a 'detection integrator' or DI counter that increments with each sample where the signal passes below the negative threshold, until a user-defined DI limit is reached, at which point the detection is confirmed and the corresponding detect bit is set.

If before the DI limit is reached, the signal rises to a point between the hysteresis and threshold levels, the DI counter is decremented with each such sample to a limit of zero.

If before the DI limit is reached, the signal rises above the hysteresis level, the DI counter is immediately cleared.

When an active key is released, the DI must count down to zero before the key state is cleared. Clearing a key's DI limit disables that key although the bursts for that key continue.

The DI is extremely effective at reducing false detections at the expense of slower reaction times. In some applications a slow reaction time is desirable; the DI can be used to intentionally slow down touch response in order to require the user to touch longer to operate the key.

There are 16 possible values for the DI limit.

## 2.7 Positive Recalibration Delay

See also command ^K, page 26

A recalibration can occur automatically if the signal swings more positive than the positive threshold level. This condition can occur if there is positive drift but insufficient positive drift compensation, or if the reference moved negative due to a recalibration, and thereafter the signal returned to normal.

As an example of the latter, if a foreign object or a finger contacts a key for period longer than the Negative Recal Delay, the key is by recalibrated to a new lower reference level. Then, when the condition causing the negative swing ceases to exist (e.g. the object is removed) the signal can suddenly swing back positive to near its normal reference.

It is almost always desirable in these cases to cause the key to recalibrate to the new signal level so as to restore normal touch operation. The device accomplishes this by simply setting Reference = Signal.

The time required to detect this condition before recalibrating is governed by the Positive Recalibration Delay command. In order for this feature to operate, the signal must rise through the positive threshold level (Section 2.2) for the proscribed user-set interval determined by ^K.

After the Positive Recal Delay interval has expired and the fast-recalibration has taken place, the affected key will once again function normally. This interval can be set on a per-key basis; it can also be disabled by setting ^K to zero.

#### 2.8 Reference Guardbanding

See also commands N, O, page 27; L, page 28

QT60xx5 devices provide for a method of self-checking that allows the host device to ascertain whether one or more key reference levels are 'out of spec'. This feature can be used to determine if an X or Y line has broken, the matrix panel has delaminated from the control panel, or there is a circuit fault.

Guardbanding alerts the host controller when the reference level of a key falls outside of acceptable absolute levels. The guardband is expressed in percent of absolute reference from the reference level of each individual key. The normal reference levels can be locked into internal eeprom via the Lock command 'L' during production; deviations in references that fall outside the guardbands centered on these reference levels are then reported as errors.

The calculations required for guardbanding are performed after the device has recalibrated or been reset after the 'L' command

Positive excursion guarding is treated separately from negative excursion guarding. The possible negative settings are from 1% to 99% of absolute signal reference in steps of 1% as set by command ^O. Positive excursions can run from 10% to 1,000% in steps of 10% as set by command ^N. A setting of 0 disables the corresponding guardband direction.

Since the circuit uses a segmented ADC approach with a 'coarse' (based on Cz states) and 'fine' (based on R2R ladder drive) offsets, the determination of percentage reference deviation from 'normal' presents a problem. The contributions of the Cz caps and the R2R ladder must be factored into the determination in order to make an accurate assessment of the error band. There are three commands which set coefficients used to convert the Cz and DAC offset values to 'absolute signal' values, according to the following equation, for each key:

#### $TotalRef(k) = (C1 \times nCz) + (C2 \times Offset) + SigRef$

Where -

TotalRef(k) is the equivalent absolute reference for key 'k'; C1 is a global constant set by commands ^T and ^U; C2 is a global constant set by command ^V; nCz is the number of Cz caps switched in for key 'k'; Offset is the noted value of the R2R DAC for key 'k'; SigRef is the noted current 'window reference' for key 'k'.

The percent deviations are computed in relation to TotalRef(k) on a per-key basis at the time the 'L' command is executed. Once the L command has recorded all values of relating to TotalRef into eeprom, the part will compare the actual running reference level of each key to its corresponding computed TotalRef value to see if it falls outside the guardbands specified by global parameters 'N and 'O.

Values which correspond to the reference circuit of Figure 3-1 are:

C1 = 1513; ^T value = 0x05, ^U value = 0xE9 C2 = 8; ^V value = 0x08

Guardbanding tests should not be confused with Reference Boundary errors (Section 2.11). Guardbanding can report errors that occur even if the signal is properly centered in the ADC window, while Reference Boundary error reporting cannot. Guardband tests do however require that the key

being checked be first fully recalibrated in order to allow the Cz and DAC offset values to alter.

If a key is outside of a limit, either of bits 2 and 3 of command 'e' will be set for that key. The error will also appear as an error in a bitfield reported with command 'E'.

There is no mechanism by which keys will automatically recalibrate if the reference drifts past a guardband boundary.

#### 2.9 Adjacent Key Suppression (AKS™)

See also command ^P, page 27

QT60xx5 devices incorporate adjacent key suppression ('AKS' - patent pending) that can be selected on a per-key basis. AKS permits the suppression of multiple key presses based on relative signal strength. This feature assists in solving the problem of surface moisture which can bridge a key touch to an adjacent key, causing multiple key presses. This feature is also useful for panels with tightly spaced keys, where a fingertip might inadvertently activate an adjacent key.

AKS works for keys that are AKS-enabled anywhere in the matrix and is not restricted to physically adjacent keys; the device has no knowledge of which keys are actually physically adjacent. When enabled for a key, adjacent key suppression causes detections on that key to be suppressed if any other AKS-enabled key in the panel has a more negative signal deviation from its reference.

This feature does not account for varying key gains (burst length) but ignores the actual negative detection threshold setting for the key. If AKS-enabled keys in a panel have different sizes, it may be necessary to reduce the gains of larger keys relative to smaller ones to equalize the effects of AKS. The signal threshold of the larger keys can be altered to compensate for this without causing problems with key suppression.

Adjacent key suppression works to augment the natural moisture suppression of narrow gated transfer switches (Section 3.13), creating a more robust sensing method.

#### 2.10 Full Recalibration

See also command 'b', page 28

The devices fully recalibrate on powerup, after a hard reset, a soft reset or after a recalibrate 'b' command using an algorithm that seeks out the optimal level of R2R offset and Cz cancellation on a per-key basis. After powerup or a reset the matrix is scanned key by key and appropriate calibrations are set for each in accordance with user-defined setup information. Since the circuit can tolerate a very wide signal range, it is capable of adapting to a wide mix of key sizes and shapes having widely varying Cx coupling capacitances.

If a false calibration occurs due to a key touch or foreign object on the keys during powerup, the affected key will recalibrate again when the object is removed depending on the settings of Positive Threshold and Positive Recal Delay (Sections 2.2 and 2.7).

Full recalibration is distinct from fast-recalibration, wherein only the Reference level is quickly adjusted. Full recalibration requires 26 burst cycles to complete whereas fast recalibration requires only one cycle (Section 2.5). The time required for recalibration is dependent on the burst spacing setting ^G (Section 3.8).

Individual keys or groups of keys can be recalibrated with a single command depending on the current command scope. The time required to recalibrate many keys is not multiplicative; the cal process for multiple keys runs in parallel.

#### 2.11 Boundary Error Reporting

See also commands 'e', page 23; N, page 27

Unlike guardband error reporting, boundary error reporting only works within the active ADC signal window segment in which the key's signal resides. Complex factoring of Cz and Offset are not required for these tests, and the tests do not require that the key be recalibrated to see the error condition.

Drift compensation can cause a key's reference level to move near to the border of the ADC's 8-bit signal window; this may make a key inoperable if the reference pegs near zero, depriving the signal of the ability to move further negative when a key is touched. Normally the reference level should be reasonably centered within the ADC's current range, i.e. at a level of about 128 decimal / 0x80 hex.

The truth logic for reference level drift error reporting is:

e/b2 = Reference > 191 e/b3 = Reference < 64

where e/b2 is command 'e' bit 2, and e/b3 is command 'e' bit 3. If either bit is set, the key should be recalibrated using command 'b'. Note that guardbanding errors (Section 2.8) also use these same bits for error reporting, but guardbanding does not usually affect these bits until after a recalibration.

Each Reference Boundary error will also appear as an error in a bitfield reported from command 'E'.

There is no mechanism by which keys can be made to automatically recalibrate if the reference drifts past a window boundary.

#### 2.12 Device Status & Reporting

See also commands '7', page 22; 'e', page 23; 'E', page 23; 'k', page 23, 'K', page 24

The device can report on the general device status or specific key states including touches and error conditions, depending on the command used.

Usually it is most efficient to periodically request the general device status using command '7' first, as the response to this command is a single byte which reports back on behalf of all keys. '7' indicates if there are any keys detecting, calibrating, or in error.

If command '7' reports a condition requiring further investigation, the host device can then use commands 'e', 'E', 'k' or 'K' to provide further details of the event(s) in progress. This hierarchical approach provides for a concise information flow using minimal data transfers and low host software overhead.

Bit 4 of command 7 reports if there is a discrepancy between the eeprom and the Flash ROM backup of the eeprom in case of data corruption; it is also set whenever a Setup parameter has changed but was not yet been copied into Flash. See Section 4.6. Resetting the device will force the eeprom changes to be copied to Flash if legitimate, or it will

force an update of eeprom from Flash memory if not legitimate.

## 3 Circuit Operation

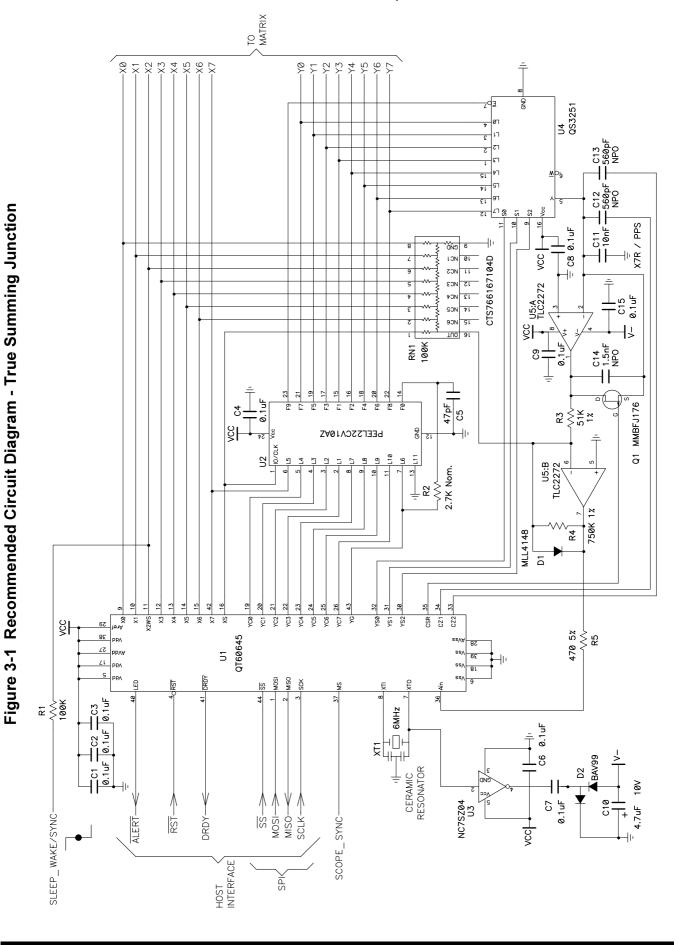

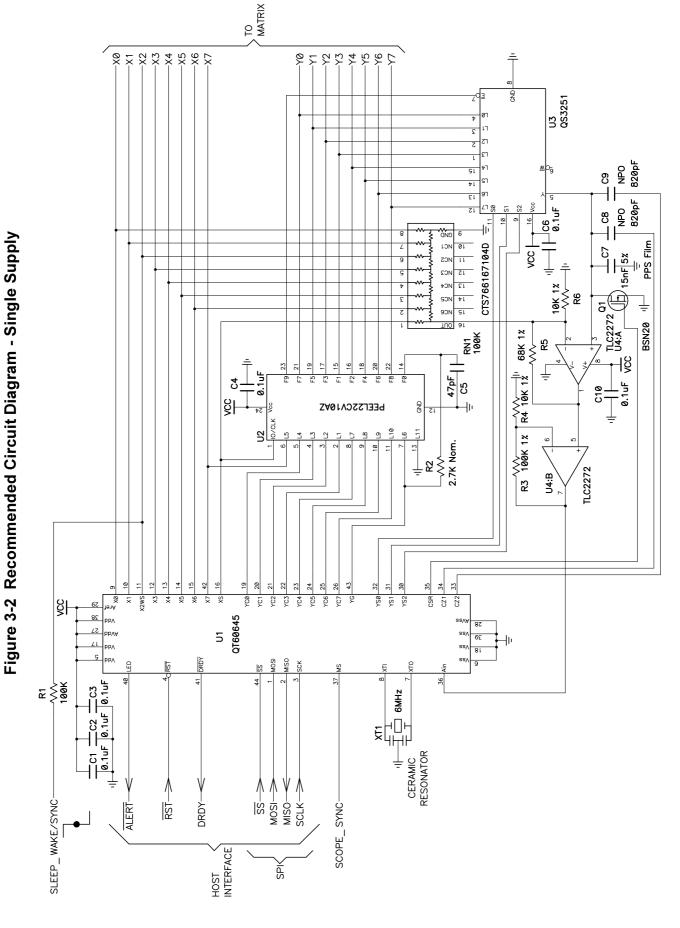

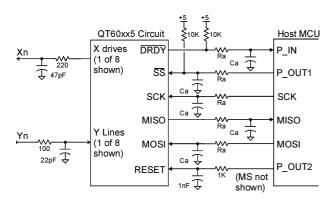

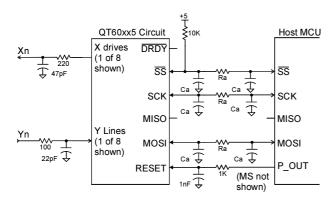

Two reference circuits are shown in Figures 3-1 and 3-2. Figure 3-1 shows a circuit having slightly greater precision and sensitivity than that of Figure 3-2, however both will perform well in most situations. Note that the Figure 3-2 circuit must have the Cs clamp control (command ^S) polarity set to 0x01 to operate properly.

#### 3.1 Part Differences

QT60xx5 parts use identical circuits and operate in identical manner in all respects, except that only the QT60645 can acquire 64 keys.

The QT60325 and QT60485 only acquire 32 and 48 keys respectively, but both still use an 8x8 matrix; any 32 or 48 keys in the matrix can be used. Unused keys must be disabled by setting their burst length to zero (command ^F). These devices have their upper keys disabled (keys 32 and 48 and up respectively). Upper keys can be enabled by first disabling undesired lower keys so that the maximum number of keys is never exceeded during the setup process.

#### 3.2 Matrix Scan Sequence

The circuit operates by scanning each key sequentially, key by key. Key scanning begins with location X=0 / Y=0. X axis keys are known as *rows* while Y axis keys are referred to as *columns*. Keys are scanned sequentially by row, for example the sequence Y0X0 Y0X1 .... Y0X3, Y1X0 Y1X1... etc.

Each key is sampled from 1 to 64 times in a burst whose length is determined by command ^F. A burst is completed entirely before the next key is sampled; at the end of each burst the resulting analog signal is converted to digital by the part's ADC. The burst length directly impacts key gain; each key can have a unique burst length in order to allow tailoring of key sensitivity on a key by key basis.

#### 3.3 Signal Path

Refer to Figures 1-4, 3-1, 3-2, and 3-3. Further descriptions can be found in Section 1.20.

Charge gate. Only one X row is pulsed during a burst. Charge is coupled across a key's Cx capacitance from the X row to all Y columns. A particular key is chosen by gating the charge from a single Y column into a charge integrator. The gate is an 8:1 analog mux whose path is selected by lines YS0, YS1, and YS2; the gate is enabled by a pulse from the PLD. The charge integrator is described below.

**Dwell time.** The gate must be switched closed just prior to the rising edge of X and must be reopened just after X has finished rising, in order to capture the charge driven across key capacitance Cx. The delay time from the rise of X to the opening of the gate is known as the Y-sample *dwell time*. Dwell time duration has a dramatic effect on the suppression of signals due to moisture films as described in Section 3.13. Dwell time is fixed in these devices to 167ns but this can be shortened using an external circuit (Section 3.9).

**Charge neutralization.** When X falls again, the charge across Cx must be neutralized. Without neutralization, Cx charge would be sampled one time only and not again during

operation. To accomplish this, the PLD always clamps all Y lines to ground except during the rise of X for the key being scanned.

Charge integrator. The first opamp is configured as an integrator with a reset switch; capacitor Cs (C14 in Figure 3-1, and C7 in Figure 3-2) performs the charge integration function. Capacitor Ca (C11 in Figure 3-1 only) acts to absorb charge momentarily before the Figure 3-1 opamp can react to absorb the charge across Cs; the value of Ca is not critical. A P-channel jfet resets Cs between bursts (n-channel mosfet in the case of Figure 3-2). The output of the opamp of Figure 3-1 swings negative, and as a consequence a negative power supply is required for that circuit; the circuit of Figure 3-2 is unipolar and requires only a positive supply.

Charge cancellation. Two Cz capacitors are used to cancel charge across Cs in stepwise fashion in order to increase signal range. These capacitors can switch during the course of a burst to reduce the final output of the amplifier chain, preventing early signal saturation due to large keys (high Cx) and/or long burst lengths. The Cz's are normally driven to +5V when not in use; switching them to ground causes a step subtraction of charge from the integrator.

**Signal amplification; offset.** At the end of the burst, the charge integrator result is amplified, and an offset from an R2R ladder DAC driven off the X drive lines is applied. This offset repositions the final analog signal as close as possible to the center of the ADC span, or at about 2.5V. The amount of offset applied is determined during the calibration process.

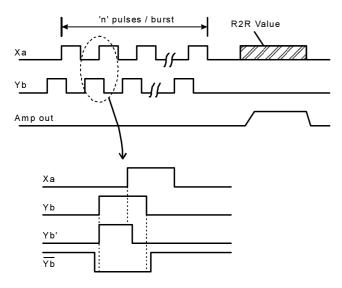

**Burst / R2R timing.** Figure 3-3 relates to a particular key being addressed by an X row line and gate control lines YSn. At the end of the burst, the X pins drive the R2R ladder network to generate a correction offset to the amplifier chain. The amplifier must stabilize to within ½ LSB (10mV) 8μs after the application of the R2R value so that the signal can be accurately sampled by the QT60xx5 on pin Ain.

**Signal gain.** Gain is directly controlled by burst length, amplifier gain, and the value of Cs. Burst length can be adjusted on a key by key basis whereas Av and Cs are fixed for all keys. See Section 3.6. The detection threshold setting also factors directly into key sensitivity.

#### 3.4 'X' Electrode Drives

The 'X' lines are directly connected to the matrix without buffering. The positive edges of these signals are used to create the transient field flows used to scan the keys. Only one X line is actively driving the matrix for scanning purposes at a time, and it will pulse for a 'burst length' for each key as determined by the 'Burst Length' Setups parameter (see command ^F, page 25 and Section 3.6).

#### 3.4.1 RFI FROM X LINES

X drive lines will radiate a small amount of RFI. This can be attenuated if required by using series resistor in-line with each X trace; the resistor should be placed near to the QT60xx5. Typical values can range from 47 to 470 ohms. Excessive amounts of R will cause a counterproductive drop in signal strength. RC networks can also be used as shown in Figure 4-4.

Inserted resistors in the X lines also have the positive effect of limiting ESD transient currents (Section 3.22).

QUANTUM

Figure 3-3 Relationship of X and Y signals

#### 3.4.2 Noise Coupling Into X lines

External noise, sometimes caused by ground bounce due to injected line noise, can couple into the X lines and cause signal interference in extreme cases. Such noise can be readily suppressed by the use of series resistors as described above. Adding a small capacitor to the matrix line on the QT60xx5 side of the R, for example 100pF to ground near the QT60xx5, will greatly help to reduce such effects.

#### 3.5 'Y' Gate Drives

There are 8 'Y' gate drives (YC0..YC7) which are active-high; only one of these lines is used during a burst for a particular key. These lines are used to control the PLD to ground all unselected 'Y' lines, making them low impedance. The selected 'Y' line in the matrix remains unclamped by the PLD during the rising edge of the 'X' drive line, during the time that the coupled charge from a single key is fed to the charge integrator via the 8:1 analog mux.

There are also 3 Y-encoded lines YS0..YS2 which select the correct switch to actuate in the analog mux for the desired 'Y' line. Line 'YG' from the controller acts to trigger the PLD's pulse generation circuit, whose pulse width following the rise of an 'X' line is dependent on an RC time constant. This pulse, 'YE', drives the enable pin of the QS3251 mux low (switch on) just before a positive-going 'X' drive pulse, and high again (switch off) just after the 'X' drive pulse. The time from the rising edge of an 'X' signal to the rising edge of 'YE' is referred to as the dwell time, and this parameter has a direct effect on the ability of the circuit to suppress moisture films (see Sections 3.9 and 3.13).

After the 'YE' pulse has ceased, the controller and circuit act to ground all 'Y' lines via the PLD just before the 'X' drive signal goes low; this restores the charge across the matrix keys to a null state, making them ready for another sample.

## 3.5.1 RFI From Y Lines

Y lines are 'virtual grounds' and do not radiate a significant amount of RFI; in fact, they act as 'sinks' for RFI emitted by the X lines since they are virtual grounds. Series-R in the Y lines is not required for RFI suppression, and in fact series-R can introduce cross-talk among keys.

#### 3.5.2 Noise Coupling Into Y Lines

External noise, sometimes caused by ground bounce due to injected line noise, can couple into the Y lines and cause signal interference in extreme cases. Such noise can be readily suppressed by adding a 100pF capacitor from each Y line to a ground plane near the QT60xx5.

## 3.6 Burst Length & Sensitivity

See also Command ^F, page 25

The signal gain in volts / pF of Cx for each key is controlled by circuit parameters as well as the burst length.

The burst length is simply the number of times the charge-transfer ('QT') process is performed on a given key. Each QT process is simply the pulsing of an X line once, with a corresponding Y line enabled to capture the resulting charge passed through the key's capacitance Cx.

QT60xx5 devices use a finite number of QT cycles which are executed in a short burst. There can be from 1 to 64 cycles in a burst, in accordance with the list of permitted values shown for command ^F, page 25. If burst length is set to zero, the burst is disabled but its time slot in the scanning sequence of all keys is preserved so as to maintain uniform timing.

Increasing burst length directly affects key sensitivity. This occurs because the accumulation of charge in the charge integrator is directly linked to the burst length. The burst length of each key can be set individually, allowing for direct digital control over the signal gains of each key individually.

Apparent touch sensitivity is also controlled by Negative Threshold (Section 2.1). Burst length and negative threshold interact; normally burst lengths should be kept as short as possible to limit RF emissions, but the threshold setting should be kept above a setting of 6 to limit false detections. The detection integrator can also prevent false detections at the expense of slower reaction time (Section 2.6).

#### 3.7 Intra-Burst Spacing

See also Command ^M, page 27

The time between X drive pulses during a burst is the intra-burst pulse spacing. This timing has no noticeable effect on performance of the circuit, but can have an impact on the nature of RF spectral emissions from the matrix panel. The setting of this function can be from 2µs through 10µs, loosely corresponding to fundamental emission frequencies from 500kHz and 100kHz respectively.

Longer spacings require more time to execute and can limit the operational settings of burst length and/or burst spacing (Section 5.7).

The intra-burst QT spacing has no effect on sensitivity or water film suppression and is not particularly important to the sensing function other than described above.

#### 3.8 Burst Spacing

See also Command \(^G\), page 25

The interval of time from the start of one burst to the start of the next is known as the *burst spacing*. This is an alterable parameter which affects all keys.

Shorter spacings result in faster response time, but due to increasing timing restrictions at shorter spacings burst lengths are restricted, limiting the amount of gain that can be

obtained; see Section 5.7. Conversely longer spacings permit higher burst lengths but slow down response time.

Spacings from 250µs to 2ms are available.

#### 3.9 PLD Circuit and Charge Sampler

The PLD should be a CMOS 22V10 type having no internal pullup or bus-keeper resistors in order to limit leakage current. ICT's PEEL22CV10AZ is a good example device, and code for this part can be found in Section 6.

The PLD performs two functions: Y line clamping and transfer switch gating.

The PLD clamps Y-lines to ground whenever key charge is not being collected. The charge integrator should only receive charge starting just before an X line goes high, to a point just after the transition (the X-Y 'dwell time'). It is an essential function of the PLD to neutralize charge keys during the negative transition of X lines; without this, charge-transfer would cease to function after a single X pulse, and multiple pulse bursts would be impossible.

The PLD also acts to generate a pulse that sets the dwell time for the QS3251 8:1 charge sampler switch. A simple PLD-based RC network controls the QS3251 gate pin 'E' starting from when line YG becomes active to a time after X7 or XS transition high. XS is the logical-OR of X0..X6; X8 and XS are OR'd together in the PLD so that any single X line can trigger the timing network.

X-Y dwell time can be measured with an oscilloscope by timing the interval from XS or X8 to 22V10 output F9. Dwell times of 70ns - 90ns work very well to suppress the effects of surface moisture films. Longer times are acceptable if such moisture is not anticipated.

R2 and/or C5 in Figure 3-1 should be adjusted to provide a timing dwell delay from the rise of an X line to the rising edge of Y-enable (QS3251) of around 75ns +/-20%. Shorter dwell times will begin to cause the suppression of human touch signals as well. If resistors and capacitors are used in line with the X and Y matrix lines for EMC and ESD suppression (Section 3.22), excessively short dwell times can seriously deteriorate signal gain. The circuit should be evaluated for the amount of signal loss by comparing delta signals due to touch both with and without the EMC circuits.

R2 and C5 can be eliminated to provide the full 167ns of dwell time output by the QT60xx5. C5 should be replaced by a connection to ground, and R2 should be open-circuited.

Source code for one type of recommended 22V10 can be found in Section 6. The 22V10 should have conventional CMOS I/O structures without 'bus-keepers' or pullup resistors in order to work optimally.

While the QS3251 is gated by the signal on its 'E' pin from the PLD, the actual switch being controlled is determined by the YS0, YS1, YS2 lines from the QT60xx5.

#### 3.10 Opamps

The amplifier chain should be configured as shown in Figures 3-1 or 3-2. The opamps should have a GBW product of at least 2MHz, have rail-rail CMOS outputs, and be able to operate from split-rail supplies (split-rail capable only in the case of Figure 3-1). To eliminate leakage current issues the amplifier should be a JFET or CMOS input type only. TI's

TLC2272 type opamp is a good example of the type of device which should be employed.

**Figure 3-1 Circuit:** The first opamp is a charge integrator whose output ranges between 0V to -2.5V. A JFET is used as a reset switch for the integration capacitor C14. Since most opamps are not fast enough to integrate the nanosecond duration transient charge pulses coming from the Y lines and the switched Cz capacitors, a large, non-critical capacitor C11 is used to temporarily store transient charge until the opamp can assimilate it over the following microseconds.

The second stage opamp must invert the first opamp output in order to provide a positive-going signal to Ain of the QT60xx5. This stage is also used to facilitate the introduction of offset from the R2R network (Section 3.12).

The second stage must be clamped with a low-C diode as shown (BAV-99 preferred) so that negative excursions of the amplifier do not under-drive the Ain pin of the device. An output resistor further limits possible Ain+ currents. Without clamping there can be high currents taken from Ain which can lead to device latchup, requiring power to be cycled to restore operation.

**Figure 3-2 Circuit:** The first opamp is a positive-gain high impedance configuration which amplifies the small voltage on Cs (C7). The reset transistor is a small-signal N-fet. C7 also receives charge cancellation capacitances C8 and C9. The R2R DAC offset is injected into the summing junction of this amplifier.

The second stage amplifier has a positive gain that provides final amplification.

This design is simpler to implement but has lower gain than the circuit of Figure 3-1.

#### 3.11 Sample Capacitors

Charge sampler capacitor Cs (C14 in Figure 3-1, C7 in Figure 3-2) should be the values shown. They should be either NP0 or C0G ceramic or PPS film for thermal stability reasons. The two Cz capacitors should be NP0 or C0G types only. The transient charge absorber C11 can be a 10% X7R type.

More information on how the Cs and Cz capacitors function is described in Section 1.2.

The values of capacitance should not be altered from the reference schematics; value changes can cause acquisition gaps to occur which can result in keys that cannot calibrate.

## 3.12 R2R Resistor Ladder

The R2R ladder network (RN1 in Figure 3-1) should have a value of 100K ohms and a precision of 7 or 8 bits. The R2R connects to the summing junction of the first or second opamp depending on the circuit; it is used to offset the analog signal down with increasing binary input value. The R2R value is determined for each key during calibration by an algorithm that seeks to put the signal Ain+ at 2.5 volts. This binary value only changes when a key is recalibrated or after powerup during the normal startup calibration cycle; drift compensation does not change R2R drive.

The R2R is driven by the matrix X lines; this is possible since Ain+ is only read after the completion of each burst, therefore this dual-use of X drive lines does not pose a conflict so long as these lines are not heavily loaded.

The rated resistance of an R2R ladder is also its Thevenin equivalent resistance which affects the scaling of the offset injected into the amplifier, in terms of mV/bit. The scaling of offset injection also affects the crossover points for the switching of each Cz capacitor. If during the calibration cycle the R2R network is found to not provide enough offset to bring the signal to the midpoint of the ADC's range, a Cz capacitor is switched in to create an additional offset.

If the R2R drive value and Cz values are not properly matched, the circuit may not be able to converge on all calibration points, i.e. there will be acquisition 'holes'. This will happen if the Cz cancellation voltage step is too large with respect to the amount of full-scale influence of the R2R ladder on the analog offset. It is recommended that the reference circuits shown in Figures 3-1 and 3-2 should not be altered to avoid problems.

#### 3.13 Water Film Suppression

Water films on the user surface can cause problems with false detection under certain conditions. Water films on their own will not normally cause false detections. The most common problem occurs when surface water bridges over 2 or more keys, and a user touches one of the keys and the water film causing an adjacent key to also trigger. Essentially, the water film transports the touch contact to adjacent keys.

The recommended circuit suppresses water coupling by means of a short sample dwell time: a short dwell time reduces the signal from resistive films by limiting the amount of time during which charge is collected. Charge from distant regions of the film take longer to return, and so a short dwell time will prevent such charge from being sensed. This effect has nothing to do with the frequency of the burst itself, it is purely a time-domain phenomenon; changing the burst or pulse spacings (i.e. sample frequency) will have no effect on water film suppression.

To create short dwell times, a CMOS PLD is configured with a simple timing circuit to control the 'Y' gate (Section 3.9).

Mechanical means can also be used to suppress crosscoupling due to moisture films, for example raised plastic barriers between keys, or placing keys in shallow wells or on raised areas to lengthen the electrical path from key to key.

AKS - Adjacent Key Suppression - is included in these devices to enhance moisture performance (Section 2.9).

#### 3.14 Reset Input

The RST' pin can be used to reset the device to simulate a power down cycle, in order to bring the part up into a known state should communications with the part be lost. The pin is active low, and a low pulse lasting at least 10µs must be applied to this pin to cause a reset.

To provide for proper operation during power transitions the devices have an internal brown-out detector set to 4 volts.

A reset command, 'r', is also provided which generates an equivalent hardware reset (page 28).

#### 3.15 Oscillator

The oscillator can use either a quartz crystal or a ceramic resonator. In either case, the XTI and XTO must both be loaded with 22pF capacitors to ground. 3-terminal resonators having onboard ceramic capacitors are commonly available and are recommended. An external TTL-compatible

frequency source can also be connected to XTI; XTO should be left unconnected.

The frequency of oscillation should be 6MHz +/-2%.

#### 3.16 Startup / Calibration Times

The QT60xx5 requires initialization times as follows:

- From very first powerup to ability to communicate:

2,000ms (One time event to initialize all of eeprom)

- Normal cold start to ability to communicate: 70ms (Normal initialization from any reset)

- 3. Calibration time per key vs. burst spacings:

spacing = 250µs: 425ms spacing = 300µs: 510ms spacing = 400µs: 680ms spacing = 500µs: 850ms spacing = 1ms: 1,700ms spacing = 2ms: 3,400ms

To the above, add 2,000ms or 70ms from (1) or (2) for the total elapsed time from reset to ability to report key detections.

Keys that cannot calibrate for some reason require 5 cal cycles before they report as errors. However, the device can report back during this interval that the key(s) affected are still in calibration via status function bits.

## 3.17 Sleep\_Wake / Noise Sync

The Sleep\_wake and Noise Sync features depend on the use of pin X2WS as an input. To prevent interference with scan line X2 during acquisitions, a resistor equal to the rating of the R2R ladder (i.e. 100K) must be used in series. The Sleep and Sync features can be used simultaneously; the part can be put into Sleep mode, but awakened by a noise sync signal which is gated in at the time desired.

Sleep mode: See also command 'Z', page 29.

The device can be put into an ultra low-power sleep mode using the 'Z' command. When this command is received, the Sleep line must be placed immediately thereafter into a logic-high state. The part will complete an ongoing burst before entering Sleep. The part can be awakened by a low transition on the X2WS pin lasting at least 5µs. One convenient way to wake the part is to connect pin X2WS to MOSI via the 100K resistor, and have the host send a null command to the device. The part will wake and the null command will not be processed. The MOSI line in turn requires a pullup resistor to prevent the line from floating low and causing an unintentional wake from sleep.

During Sleep the oscillator is shut down, and the part hibernates with microamp levels of current drain. When the part wakes, the part resumes normal functionality from the point where it left off. It will not recalibrate keys or engage in other unwarranted behavior.

Before going to sleep the part will respond with a 'Z'. In slave-only SPI mode (see Section 4.3), the SS line must be floated high by the host as soon as it receives this response; if SS does not float high, sleep will fail and the device will instead completely reset after about 2 seconds. Upon waking the part will issue another 'Z' byte back to the host.

Noise sync: See also command \(^{V}\), page 30.

External fields can cause interference leading to false detections or sensitivity shifts. Most fields come from AC power sources. RFI noise sources are heavily suppressed by the low impedance nature of the QT circuitry itself.

External noise becomes a problem if the noise is uncorrelated with signal sampling; uncorrelated noise can cause aliasing effects in the key signals. To suppress this problem the devices feature a noise sync input which allows bursts to synchronize to the noise source. This same input can also be used to wake the part from a low-power Sleep state.

The device's bursts can be synchronized to an external source of repetitive electrical signal, such as 50Hz or 60Hz, or possibly a video display vertical sync line, using the Sleep\_wake / Noise sync line. The noise sync operating mode is set by command ^W. This feature allows dominant external noise signals to be heavily suppressed, since the system and the noise become synchronized and no longer beat or alias with respect to each other. The sync occurs only at the burst for key 0 (X0Y0); the device waits for the sync signal for up to 100ms after the end of a preceding full matrix scan (after key #63), then when a negative sync edge is received, the matrix is scanned in its entirety again.

The sync signal drive should be a buffered logic signal, or perhaps a diode-clamped signal, but never a raw AC signal from the mains.

Since Noise sync is highly effective yet simple and inexpensive to implement, it is strongly advised to take advantage of it anywhere there is a possibility of encountering electric fields. Quantum's QmBtn software can show signal noise caused by nearby AC electric fields and will hence assist in determining the need to make use of this feature.

If the sync feature is enabled but no sync signal exists, the sensor will continue to operate but with a delay of 100ms from the end of one scan to the start of the next, and hence will have a slow response time.

## 3.18 LED / Alert Output

Pin 40 is designed to drive a low-current LED, 5mA maximum, active-low. The LED will glow brightly (i.e. pin 40 will be solid low) during calibration of one or more keys, for example at startup. When a key is detected, pin 40 will be low for the duration of each burst for which a key is sensed, i.e. with a very low duty cycle. Each additional key being detected will also create a low pulse for that key's burst. During all other times, the LED pin will be inactive (high).

This pin can be used to alert the host that there is key activity, in order to limit the amount of communication between the device and the host. The LED / Alert line should ideally be connected to an interrupt pin on the host that can detect a negative edge, following which the host can proceed to poll the device for key activations.

This pin also pulls low if there is a key error of any kind.

Note that in sleep mode if the LED was on just prior to sleep, it will remain on during sleep.

#### 3.19 CSR Drive Polarity

See also Command \(^{S}\), page 29

The polarity of the Cs integrator capacitor reset drive can be set for active high or active low operation using command ^S. In the reference circuit show in Figure 3-1, the JFET will reset

Cs when the drive signal is low, so 'S should be set to '0'. Figure 3-2 requires that 'S be set to '1'.

This feature allows for operation with the two basic circuit topologies which require different Cs reset control polarities.

#### 3.20 Oscilloscope Sync

See also Command ^R, page 29

'MS' pin 37 can output a positive pulse oscilloscope sync that brackets the burst of a selected key. This feature is controlled by the 'R command. More than one burst can output a sync pulse, for example if the scope of the command when set is a row or column, or is all keys. The 'R command is volatile and does not survive reset or power down.

This feature is invaluable for diagnostics; without it, observing signals clearly on an oscilloscope for a particular burst is nearly impossible.

This pin is also used as a SPI mode select pin. In order to prevent a shorted output when the oscilloscope sync is enabled, the MS pin should only be connected to ground or Vdd via a  $\geq$ 10K resistor.

This function is supported in QmBtn PC software via a checkbox.

#### 3.21 Power Supply and PCB Layout

Vdd should be 5.0 volts +/- 5%. This can be provided by a common 78L05 3-terminal regulator. LDO type regulators are usually fine but can suffer from poor transient load response which may cause erratic signal behavior.

If the power supply is shared with another electronic system, care should be taken to assure that the supply is free of digital spikes, sags, and surges which can adversely affect the circuit. The devices can track slow changes in Vcc depending on the settings of drift compensation, but signals can be adversely affected by rapid voltage steps and impulse noise on the supply rail.

0.1µF bypass caps from power to ground should be used near every supply pin of every active component in the circuit.