## R6500/1EB and R6500/1EAB Backpack Emulator

## INTRODUCTION

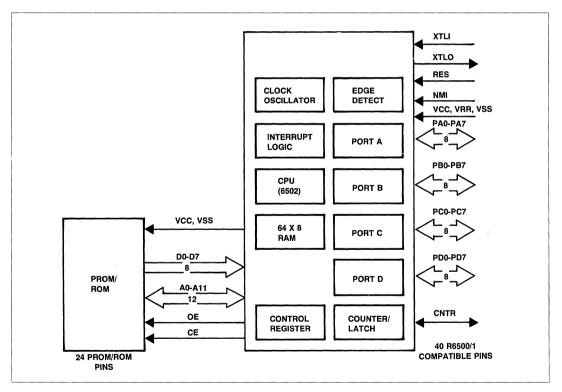

The Rockwell R6500/1EB and R6500/1EAB Backpack Emulator is the PROM prototyping version of the 8-bit, masked-ROM R6500/1 one-chip microcomputer. Like the R6500/1, the backpack device is totally upward/downward compatible with all members of the R6500/1 family. It is designed to accept standard 5-volt, 24-pin EPROMs or ROMs directly, in a socket on top of the Emulator. This packaging concept allows a standard EPROM to be easily removed, reprogrammed, then reinserted as often as desired.

The backpack devices have the same pinouts as the masked-ROM R6500/1 microcomputer. These 40 pins are functionally and operationally identical to the pins on the R6500/1, with some minor differences (described herein). The R6500/1 Microcomputer Product Description (Order No. 212) includes a description of the interface signals and their functions. Whereas the masked-ROM R6500/1 provides 2K bytes of read-only memory, the R6500/1EB will address 3K bytes of external program memory. This extra memory accommodates program patches, test programs or optional programs during breadboard and prototype development states.

## **ORDERING INFORMATION**

#### BACKPACK EMULATOR

| Part<br>Number | Memory<br>Capacity | Compatible<br>Memories | Temperature<br>Range and Speed |

|----------------|--------------------|------------------------|--------------------------------|

| R6500/1EB3     | 3K × 8             | 2732                   | 0°C to 70°C<br>1 MHz           |

| R6500/1EAB3    | 3K × 8             | 2732A<br>(250 ns)      | 0°C to 70°C<br>2 MHz           |

#### SUPPORT PRODUCTS

| Part<br>Number | Description                            |

|----------------|----------------------------------------|

| RDC-3101       | Low Cost Emulator (LCE)                |

| RDC-3030       | PROM Programmer Module                 |

| RDC-369        | 1- or 2-MHz R6500/1 Personality Module |

## FEATURES

- PROM version of the R6500/1

- Completely pin compatible with R6500/1 single-chip microcomputers

- Profile approaches 40-pin DIP of R6500/1

- Accepts 5-volt, 24-pin industry-standard EPROMs —4K memories—2732, 2732A (3K bytes addressable)

- Use as prototyping tool or for low volume production

- 3K bytes of memory capacity (4K memories)

- 64 × 8 static RAM

- Separate power pin for RAM

- Software compatibility with the R6500 family

- 32 bi-directional TTL compatible I/O lines (4 ports)

- 1 bi-directional TTL compatible counter I/O line

- 16-bit programmable counter/latch with four modes (interval timer, pulse generator, event counter, pulse width measurement)

- 5 interrupts (reset, non-maskable, two external edge sensitive, counter)

- · Crystal or external time base

- Single +5V power supply

R6500/1EB-R6500/1EAB Backpack Emulator

## **Backpack Emulator**

#### CONFIGURATION

The external memory must always occupy the upper 2K of available memory (addresses 800 through FFF) for implementation of interrupt vectors. See Memory Map. The Backpack Emulator provides a read block to the external memory where internal RAM or I/O are located in the same addresses as that occupied by external memory.

### EXTERNAL FREQUENCY REFERENCE

The external frequency reference may be a crystal or a clock. The R6500/1EB and R6500/1EAB divide the input clock by two regardless of the source.

#### **I/O PORT PULLUPS**

The emulator devices have internal I/O port pullup resistors.

#### **PRODUCT SUPPORT**

The Backpack Emulator is just one of the products that Rockwell offers to facilitate system and program development for the R6500/1.

The Low Cost Emulator (LCE) with R6500/1 Personality Module supports both hardware and software development. Complete in-circuit user emulation with the R6500/1 Personality Module allows total system test and evaluation. With the optional PROM Programmer, the LCE can also be used to program EPROMs for the development activity. When PROM programs have been finalized, the PROM device can be sent to Rockwell for masking into the 2K ROM of the R6500/1.

R6500/1EB Interface Diagram

## **Backpack Emulator**

#### DETAILED MEMORY MAP

|             |                                     | HEX        |

|-------------|-------------------------------------|------------|

|             | IRQ VECTOR HIGH                     | FFF        |

| 1           | IRQ VECTOR LOW                      | FFE        |

|             | RES VECTOR HIGH                     | FFD        |

| PROM        | RES VECTOR LOW                      | FFC        |

|             | NMI VECTOR HIGH                     | FFB        |

|             | NMI VECTOR LOW                      | FFA        |

|             | R6500/1 USER PROGRAM                | FF9<br>400 |

| PROM        | R6500/1EB EXTENDED PROGRAM AREA (1) | 3FF<br>400 |

| NOT<br>USED | UNASSIGNED                          | 400        |

|             | CONTROL REGISTER                    | 08F        |

|             | UNASSIGNED                          | 08E<br>08B |

|             | CLEAR PA1 NEG EDGE DETECTED (2)     | 08A        |

|             | CLEAR PA0 POS EDGE DETECTED (2)     | 089        |

|             | UPPER LATCH AND TRANSFER (3)        | 088        |

| Ì           | LOWER COUNT (3)                     | 087        |

| 1/0         | UPPER COUNT                         | 086        |

|             | LOWER LATCH                         | 085        |

| ł           | UPPER LATCH                         | 084        |

|             | PORT D                              | 083        |

|             | PORT C                              | 082        |

|             | PORT B                              | 081        |

|             | PORT A                              | 080        |

| NOT<br>USED | UNASSIGNED                          | 03F        |

| RAM         | USER RAM                            | 000        |

#### NOTES

- (1) Additional 1024 bytes are decoded for external memory addressing by the Backpack Emulator Device. This area can be used during debug, but cannot be used in a masked ROM R6500/1.

- (2) I/O command only; i.e., no stored data.

allows RAM mapping only at 000-03F.

Clears Counter Overflow—Bit 7 in Control Register

CAUTION: The device allows RAM mapping into 040-07F, 100-13F, 140-17F, 200-23F, 240-27F, 300-33F, and 340-37F; as well as 000-03F. The production R6500/1, however

#### **RAM MAPPING**

The Backpack Emulator allows RAM mapping into 040-07F, 100-13F, 140-17F, 200-23F, 240-27F, 300-33F and 340-37F, as well as 000-03F. The production R6500/1, however, allows RAM mapping only at 000-03F. This means that a write to location 40, for example, will write to location 0 in the Backpack Emulator, and to invalid RAM in the R6500/1 production part.

#### **I/O PORT INITIALIZATION**

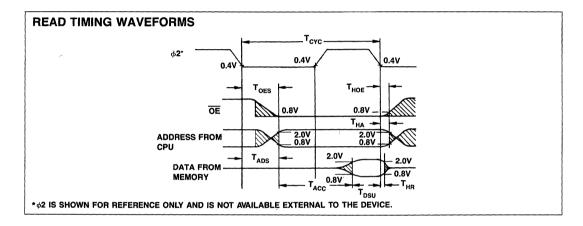

Ports A, B, C, and D and the CNTR line in the Backpack Emulator are initialized to the logic high state two  $\emptyset$ 2 clock cycles earlier than in the R6500/1. The RES line to the device must, however, still be held low for at least eight  $\emptyset$ 2 clock cycles after V<sub>CC</sub> reaches operating range. See timing diagram.

#### BACKPACK MEMORY SIGNAL DESCRIPTION

| Signal<br>Name  | Pin No.            | Description                                                                                                                                                                                                                                                                                |

|-----------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7           | 9S-11S,<br>13S-17S | Data Bus Lines. All instruction and data transfers take place on the data bus lines. The buffers driving the data bus lines have full three-state capability. Each data bus pin is connected to an input and an output buffer, with the output buffer remaining in the floating condition. |

| A0-A9           | 1S-8S,<br>23S, 24S | Address Bus Lines. The address bus lines are<br>buffered by push/pull type drivers that can drive<br>one standard TTL load.                                                                                                                                                                |

| A10             | 19S                | Address Bus Line 10. This address line has the<br>same characteristics and functions as Lines<br>A0-A9.                                                                                                                                                                                    |

| ĈĒ              | 18S                | $\overline{\text{CE}}$ is active when the address is 400-FFF. This line can drive one TTL load.                                                                                                                                                                                            |

| ŌĒ              | 20S                | Memory Enable Line. This signal provides the output enable for the memory to place information on the data bus lines. This signal is driven by the $R/\overline{W}$ signal from the CPU and then inverted by a standard TTL inverter, to form $\overline{OE}$ .                            |

| V <sub>cc</sub> | 24S                | Main Power Supply <sup>\$</sup> 5V. This pin is tied directly to pin 30 (V <sub>CC</sub> ).                                                                                                                                                                                                |

| A11             | 21S                | Address Bus Line II. This pin is tied to A11. Dur-<br>ing backup power, power is supplied only to the<br>RAM memory, and not to the PROMs.                                                                                                                                                 |

| V <sub>SS</sub> | 12S                | Signal and Power Ground (zero volts). This pin is tied directly to pin 12 ( $V_{SS}$ ).                                                                                                                                                                                                    |

|                 | _   |                   |        |       |                  |      |                 |

|-----------------|-----|-------------------|--------|-------|------------------|------|-----------------|

| V <sub>RR</sub> | •1  | A7 🗆              | •1s    | 24s   | ٥v <sub>cc</sub> | 40   | NMI             |

| (PD/ L          | 2   | A6 🖸              | 2s     | 23s   | b A8̃            | 39 🗖 | RES             |

| PD6             | 3   | A5 🗆              | 3s     | 22s   | <b>∆</b> A9      | 38 🗖 | PA0             |

| PD5 C           | 14  | A4 🗆              | 4s     | 21s   | ÞA11             | 37 🗖 | PA 1            |

| PD4             | 5   | A3 🗆              | 5s     | 20s   | DOE              | 36 🗖 | PA 2            |

| PD3             | 6   | A2 🗆              | 6s     | 19s   | þA10             | 35 🗖 | PA 3            |

| PD2             | 7   | A1 🗆              | 7s     | 18s   | ÞĈE              | 34 🗖 | PA4             |

| PD1 C           | 8   | A0 🗆              | 8s     | 17s   | p 07             | 33 🗖 | PA 5            |

| PD0             | 9   | D0 C              | 9s     | 16s   | þ D6             | 32 🗍 | PA 6            |

| XTL1            | 10  | D1 🗆              | 10s    | 15s   | D5               | 31 🗖 | PA7             |

| XTL0            | 111 | D2 🗆              | 11s    | 14s   | Þ D4             | 30 🗖 | V <sub>cc</sub> |

| V <sub>ss</sub> | 12  | v <sub>ss</sub> ⊏ | 12s    | 13s   | þD3              | 29 🗖 | PBO             |

| PC/ L           | 13  |                   |        |       | 1                | 28 🗖 | PB1             |

| PC6             | 14  | :                 | 24-PIN | SOCKE | Г                | 27   | PB2             |

| PC5             | 15  |                   |        |       |                  | 26 🗖 | PB3             |

| PC4             | 16  |                   |        |       |                  | 25   | PB4             |

| PC3             | 17  |                   |        |       |                  | 24 🗖 | PB5             |

| PC2             | 18  |                   |        |       |                  | 23 🖯 | PB6             |

| PC1             | 19  |                   |        |       |                  | 22 🗋 | PB7             |

| PC0             | 20  |                   |        |       |                  | 21   | CNTR            |

|                 |     |                   |        |       |                  |      |                 |

**Pin Configuration**

# 3

## **READ TIMING CHARACTERISTICS**

|                             |                  | 11   | lHz  | 2 MHz |      |      |  |

|-----------------------------|------------------|------|------|-------|------|------|--|

| Signal                      | Symbol           | Min. | Max. | Min.  | Max. | Unit |  |

| OE setup time from CPU      | T <sub>OES</sub> | _    | 300  | _     | 150  | ns   |  |

| Address setup time from CPU | T <sub>ADS</sub> | -    | 300  | - 1   | 150  | ns   |  |

| Memory read access time     | TACC             | -    | 525  | - 1   | 250  | ns   |  |

| Data stabilization time     | T <sub>DSU</sub> | 150  | - 1  | 100   | -    | ns   |  |

| Data hold timeRead          | T <sub>HB</sub>  | 10   |      | 10    |      | ns   |  |

| Address hold time           | THA              | 30   |      | 30    |      | ns   |  |

| OE hold time                | T <sub>HOE</sub> | 30   | -    | 30    |      | ns   |  |

| Cycle Time                  | T <sub>cyc</sub> | 1.0  | 10.0 | 0.5   | 10.0 | μs   |  |

| I/O PORT INI | TIALIZA    | ION TIMING            |

|--------------|------------|-----------------------|

|              | φ <b>2</b> |                       |

|              | RES        |                       |

| 1/0          | R6500/1EB  | \\\                   |

| PORTS        | R6500/1    |                       |

|              |            | RES TRANSITION WINDOW |

|              |            | DON'T CARE STATE      |

#### **MAXIMUM RATINGS\***

| Parameter                           | Symbol           | Value                                        | Unit |  |

|-------------------------------------|------------------|----------------------------------------------|------|--|

| Supply Voltage                      | V <sub>cc</sub>  | -0.3 to +7.0                                 | Vdc  |  |

| Input Voltage                       | V <sub>IN</sub>  | -0.3 to +7.0                                 | Vdc  |  |

| Operating Temperature<br>Commercial | T <sub>A</sub>   | T <sub>L</sub> to T <sub>H</sub><br>0 to +70 | °C   |  |

| Storage Temperature                 | T <sub>STG</sub> | - 55 to + 150                                | °C   |  |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC CHARACTERISTICS**

(V\_{CC} = 5.0V  $\pm 5\%$ , V\_{SS} = 0V; T<sub>A</sub> = 0° to 70°, unless otherwise specified)

| Parameter                                              | Symbol           | Min   | Typ1 | Max    | Unit | Test Conditions                                                  |

|--------------------------------------------------------|------------------|-------|------|--------|------|------------------------------------------------------------------|

| Input High Voltage<br>D0-D7                            | V <sub>IH</sub>  | +2.4  | -    | -      | v    |                                                                  |

| Input Low Voltage<br>D0-D7                             | V <sub>IL</sub>  | -     | -    | + 0.8  | v    |                                                                  |

| Input Leakage Current (Three-State Off)<br>D0-D7       | l <sub>in</sub>  |       | —    | ± 10.0 | μΑ   | $V_{IN} = 0.4 \text{ to } 2.4 \text{V}$ $V_{CC} = 5.25 \text{V}$ |

| Output High Voltage (Except XTLO)<br>D0-D7, A0-A11, OE | V <sub>OH</sub>  | + 2.4 |      | -      | v    | $I_{LOAD} = -100 \ \mu A$ $V_{SS} = 4.75V$                       |

| Output Low Voltage<br>D0-D7, A0-A11, OE                | V <sub>OL</sub>  | —     | -    | + 0.6  | v    | $I_{LOAD} \approx 1.6 \text{ mA}$<br>$V_{SS} = 4.75 \text{V}$    |

| I/O Port Pull-Up Resistance                            | RL               | 3.0   | 6.0  | 11.5   | Kohm |                                                                  |

| Input Capacitance<br>D0-D7                             | C <sub>IN</sub>  | —     | _    | 15     | рF   | $T_{A} = 25^{\circ}C$ $V_{IN} = 0V$ $f = 1.0 \text{ MHz}$        |

| Output Capacitance (Three-State Off)<br>A0-A11         | C <sub>OUT</sub> | -     | -    | 12     | pF   | $T_{A} = 25^{\circ}C$ $V_{IN} = 0V$ $f = 1.0 \text{ MHz}$        |

| Power Dissipation (Less EPROM)                         | PD               | _     | 800  | 1300   | mW   | $T_A = 0^{\circ}C$                                               |

Notes

1. Typical values measured at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5.0V$ .

2. Negative sign indicates outward current flow, positive indicates inward flow.

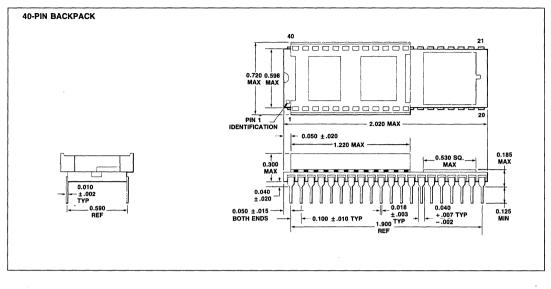

## PACKAGE DIMENSIONS