## R8A66171DD/SP

## A<sup>2</sup>RT (ADVANCED ASYNCHRONOUS RECEIVER & TRANSMITTER)

REJ03F0269-0100 Rev. 1.00 Feb.19.2008

#### DESCRIPTION

The R8A66171 is an integrated circuit for asynchronous serial data communications. It is used in combination with an 8-bit microprocessor and is produced using the silicon gate CMOS technology. R8A66171 is the succession product of M66230.

#### **FEATURES**

- Baud rate generator

- 4-byte FIFO data buffer for transmission and reception

- www.DataSheet LError detection: CRC-CCITT

- Wakeup function

- Majority-voting system by sampling three points of received data

- Transmission / reception data format ( number of bits )

Start bit 1

Data bit 8

Wakeup bit 1 or nil

Parity bit 1 or nil

Stop bit 1 or 2

Transmission speed

Access time

500Kbps (max)

ta (/RD-D): 100ns

• High output current IOH=-24mA IOL=24mA TxD, /RTS, P0, P1 pins

• Schmitt triggered input RxD, /CTS, /RESET pins

• Wide operating supply voltage range (Vcc=3.0~3.6V or Vcc=4.5~5.5V)

• Wide operating temperature range (Ta=-40~85°C)

#### **APPLICATION**

Data communication control that uses microprocessor

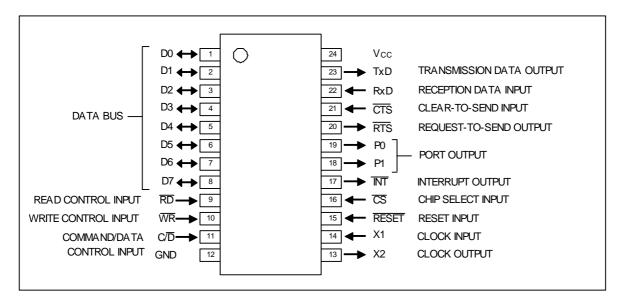

## PIN CONFIGURATION (TOP VIEW)

## **FUNCTION**

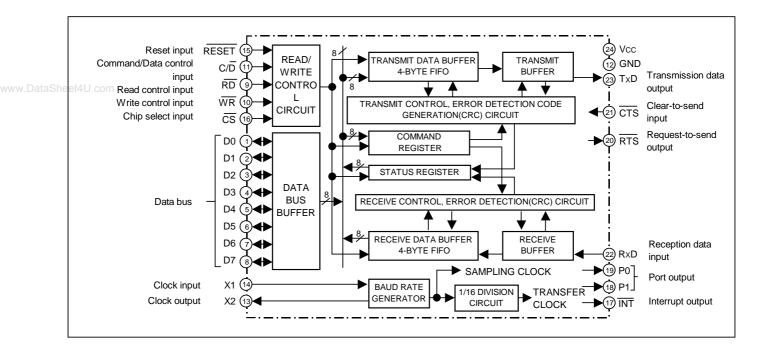

The R8A66171 is a UART (Universal Asynchronous Receiver/Transmitter) and is used in the peripheral circuit of a MCU. The R8A66171 receives parallel data, converts into serial format, and then transmits the serial data via the TxD pin. The device also receives data via the RxD pin from external circuits and converts it into parallel format, and sends the parallel data via the data bus.

## **BLOCK DIAGRAM**

#### **OPERATION**

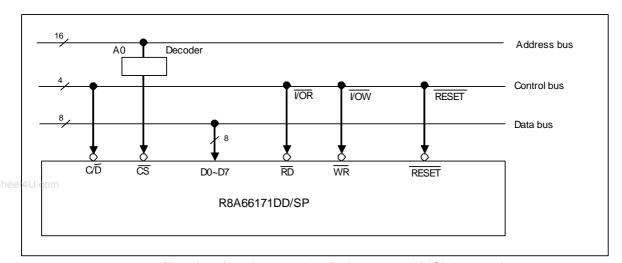

The R8A66171 is interfaced to a system bus and provides all functions needed for data communication.

Fig.1 Interface between the R8A66171 and MCU system bus

When using the R8A66171, it is necessary to program the initial setting, baud rate, character length, CRC, parity, in accordance with the communication system. Once programmed, the communication system functions are executed continuously.

When initial setting of R8A66171 is completed, data communication becomes possible. When the transmitter is transmit-enabled (TXEN) by a command instruction and /CTS is low-level, data transfer starts up. If these conditions are not satisfied, data transmission is not executed. Reception is possible when the receiver is receive-enabled (RXEN) by a command instruction.

The MCU is able to read data when the interrupt output, /INT, goes low by packet end (PE) or buffer full (BF). While receiving data, the R8A66171 checks for errors and provides status information. It checks for four types of errors: CRC, parity, overrun and framing errors. When an error occurs, R8A66171 continues operation. The error status is maintained until the error reset, (ER) is modified by a command instruction. The access method of the R8A66171 is shown Table 1.

| C/D | RD | WR | cs | R8A66171 operation                     | MPU operation       |

|-----|----|----|----|----------------------------------------|---------------------|

| L   | L  | Н  | L  | Data bus ← Receiving data buffer(FIFO) | Read receive data   |

| L   | Н  | L  | L  | Data bus → Transmit data buffer(FIFO)  | Write transmit data |

| Н   | L  | Н  | L  | Data bus ← Status register             | Read the status     |

| Н   | Н  | L  | L  | Data bus → Command register            | Write the command   |

| Х   | Н  | Н  | L  | Data bus: High impedance               | -                   |

| Х   | Χ  | Χ  | Н  | Data bus: High impedance               | -                   |

Note: X="L" or "H"

TABLE 1. Access method of the R8A66171

## PIN DESCRIPTIONS

| Pin       | Name                       | I/O              | Function                                                                                                                                                                                                                                                        |

|-----------|----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1        | Clock input                | Input            | A crystal is externally connected to these pins for generating an                                                                                                                                                                                               |

| X2        | Clock output               | Output           | internal clock. An external clock signal can be input to X1 instead of a crystal. Then X2 output opened.                                                                                                                                                        |

| RESET     | Reset input                | Input            | This reset is a master reset, therefore commands should be loaded after the reset.                                                                                                                                                                              |

| com<br>CS | Chip select input          | Input            | A low level signal on the chip select input enables the R8A66171. The device can not be accessed when the signal is high-level.                                                                                                                                 |

| C/D       | Command/Data control input | Input            | This signal distinguishes whether the information on the R8A66171 data bus is data, command or status information. When the signal is high-level, the data bus has command or status information. When the signal is low-level, the data bus has data.          |

| RD        | Read control input         | Input            | The receiving data or status information is output to the data bus from the R8A66171 by a low-level signal.                                                                                                                                                     |

| WR        | Write control input        | Input            | The data or command output from the MCU is written to the R8A66171 by a low-level signal.                                                                                                                                                                       |

| D0~D7     | Data bus                   | Input/<br>Output | This is an 8-bit bi-directional bus buffer. Command, status information, and transfer data are transferred to/from the MCU via this data bus buffer.                                                                                                            |

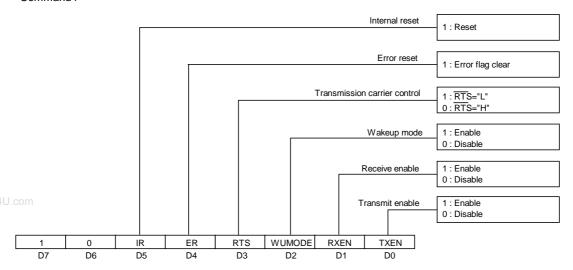

| ĪNT       | Interrupt output           | Output           | This is used as an interrupt request to MCU. The interrupt request is generated when the receive FIFO is full, the transmit FIFO is empty or the block reception is complete. D2 bit of command 6 controls the switching of low-level and high-level interrupt. |

| RxD       | Reception data input       | Input            | The serial data is sent to this pin.                                                                                                                                                                                                                            |

| TxD       | Transmission data output   | Output           | The serial data is transmitted from this pin.                                                                                                                                                                                                                   |

| P0        | Port output                | Output           | This is an ordinary port pin. This pin is controlled by the D0 bit of command 6.                                                                                                                                                                                |

| P1        | Port output                | Output           | This pin has the same function as that of P0 pin and provides information of packet transmission's completion. The switching of this function is controlled by command 6, D1 bit.                                                                               |

| CTS       | Clear-to-send input        | Input            | When the TXEN bit (D0) of command 4 is set to 1 and the /CTS input is low-level, serial data is sent from the TxD pin. This is used as the clear-to-send signal.                                                                                                |

| RTS       | Request-to-send output     | Output           | This is used as the request-to-send signal. This pin is controlled by the D3 bit of command 4.                                                                                                                                                                  |

MANA DataShoot41

#### DISCRIPTION OF FUNCTION

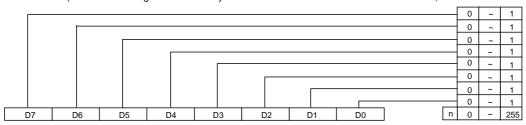

#### • Baud rate generator

The 8-bit programmable divider (baud rate generator) generates the baud rate for transmit or receive. The division rate is (n+1) with a range of n=0~255. The baud rate is calculated by the following formula:

baud rate =

$$\frac{f(X1)}{\text{prescaler division (2 or 32)} \cdot \text{baud rate generator division rate (n+1)} \cdot 16}$$

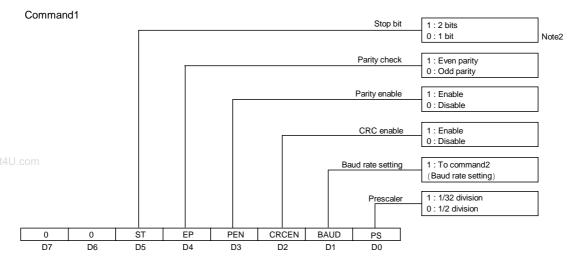

The prescaler division rate is set by the D0 bit of command1. The baud rate generator division rate is set by command2.

Example as follows:

w.DataSheet4U.com

9600bps =

$$\frac{9.8304MHz}{2 \cdot (31+1) \cdot 16}$$

#### • Block length counter

The R8A66171 can handle multiple-bytes of data as one block (packet).

Therefore, CRC of bytes is possible. The block length counter is a 6-bit programmable counter. The block length is (m+1) bytes with the allowed values of m=0~63.

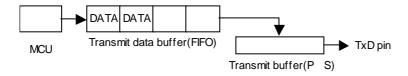

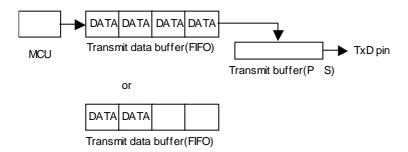

#### Transmit data buffer (FIFO)

The transmit data buffer (FIFO) consists of 4-bytes.

The transmit data buffer (FIFO) functions according to the block length.

#### Block length=1~3

When the transmit data buffer (FIFO) becomes empty (buffer empty) and /INT is set to low-active, the interrupt output /INT is set to a low-level. The MCU verifies the buffer is empty when the D2 bit of the status1 information is read. The MCU should write the block length data to the transmit data buffer (FIFO) at this moment.

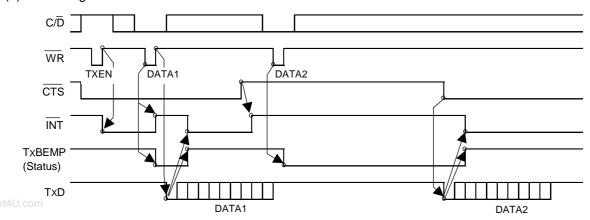

When a block of data is written to the transmit data buffer (FIFO), /CTS is low-level and TXEN is high-level, the data in the transmit data buffer (FIFO) is sent to the transmit buffer. If /CTS is high-level while data is transmitted, all data is transmitted (including the data in the transmit data buffer (FIFO)). When the buffer becomes empty, the data in the transmit data buffer (FIFO) is not be sent to the transmit buffer until MCU writes a new block of data to the transmit data buffer (FIFO). The MCU can not write new data to the transmit data buffer (FIFO) until the buffer becomes empty.

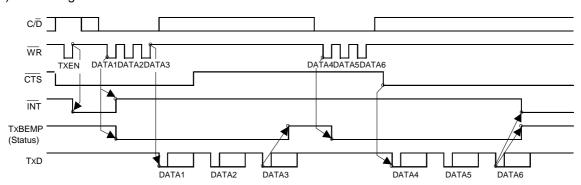

Example: Block length=2

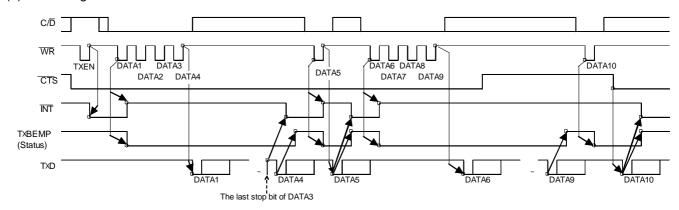

#### Block length=4 or more

When the transmit data buffer (FIFO) becomes empty and /INT is set low-active, the interrupt output /INT becomes low. The MCU verifies the buffer is empty by reading the D2 bit of the status1 information

When this happens, the MCU should write the 4-bytes of data to the transmit data buffer (FIFO). The data in the transmit data buffer (FIFO) is sent to the transmit buffer when /CTS is low-level and TXEN is high-level. When the number of bytes from the MCU becomes less than 4 at the last stage of the block transmission, the same operation should be made as the block length=1~3.

When the buffer becomes empty, the data in the transmit data buffer (FIFO) is not be sent to the transmit buffer until MCU writes data of the fixed block length to the transmit data buffer (FIFO). The MCU cannot write data to the transmit data buffer (FIFO) until the buffer becomes empty.

Example: Block length=6

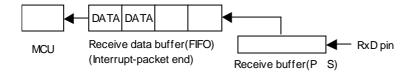

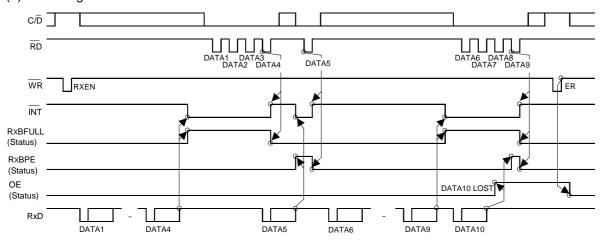

#### Receive data buffer (FIFO)

The receive data buffer (FIFO) consists of 4-bytes. The receive data buffer (FIFO) functions according to the block length.

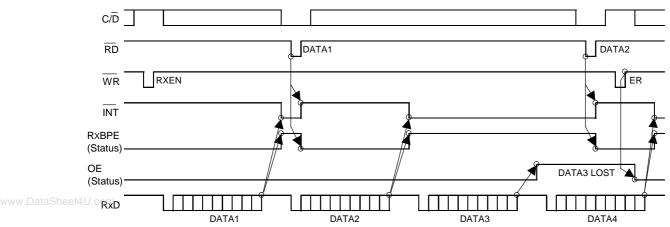

### Block length=1~3

When the data of the block length is received and /INT is set to low-level, the interrupt output /INT becomes low-level. The MCU acknowledges the packet end by setting the D0 bit of the status1 information.

In this case, the MCU should read all data from the receive data buffer (FIFO).

At the packet end, the data from the receive buffer cannot be transmitted to the receive data buffer (FIFO) until the MCU reads all data in the receive data buffer (FIFO). The MCU cannot read data in the receive data buffer until the packet end.

Example: Block length=2

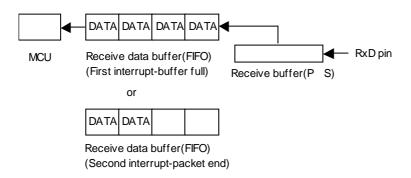

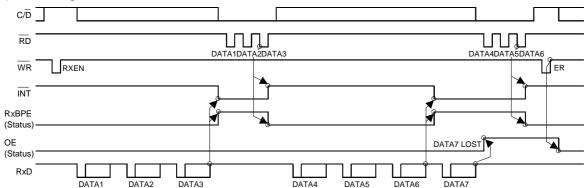

#### Block length=4 or more

When 4-byte data enters the receive data buffer (FIFO) (buffer full) and /INT is set to low-active, the interrupt output /INT becomes low-level. The MCU acknowledges the buffer full status by setting the D1 bit of the status1 information.

In this case, the MCU should read all data in the receive data buffer (FIFO).

When the last data enters the receive data buffer (FIFO), the packet end becomes the same operation as for 1~3 byte block length. If the block length is a multiple of four, the D0 and D1 bits of the status1 information are set when the last data enters the receive data buffer (FIFO). At packet end or buffer full, the new data cannot be transferred from the receive buffer to the receive data buffer (FIFO). The MCU cannot read data in the receive data buffer (FIFO) until packet end or buffer full occurs.

Example: Block length=6

#### SUPPLEMENTARY DESCRIPTION

#### **FIFO**

The major purpose is not to interrupt the MCU by each character. The MCU is interrupted when:

Transmit data buffer (FIFO) empty

Receive data buffer (FIFO) full or packet end

The MCU interruption interval is as follows:

Approximately 90µs (min) until the FIFO becomes full at 500kbps.

Approximately 36.7ms (min) until the FIFO becomes full at 1.2kbps.

Read/write operation by the MCU should be made for all data in FIFO at once.

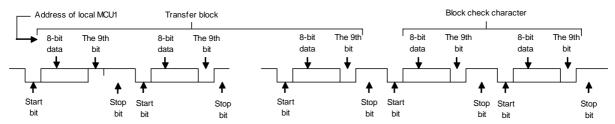

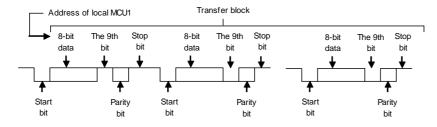

#### Wakeup

The wakeup mode of the R8A66171 can be set by setting the D2 bit of command4 to "1". In wakeup mode, a 9<sup>th</sup> bit is automatically added (the wakeup bit).

www.DataSheet4U.comOnly the 9<sup>th</sup> bit of the first byte is "1", and the remainder blocks 9<sup>th</sup> bits are set to "0".

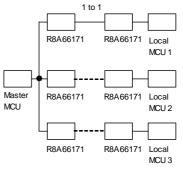

The wakeup is used when one master MCU and multiple local MCU are connected by serial I/O.

Examples of wakeup are shown below.

Initial setting

The initial setting should be made by the input of each command.

Wakeup mode

The wakeup mode of the R8A66171 is activated by setting D2 bit of the command4 to "1". Command5 can be input as the second byte of command4 by setting D2 bit of the command4 to "1" and each address is input. In the wakeup mode, the 9th bit is automatically added. Others remain the same.

Wakeup and data transfer (between master MCU and local MCU1)

Data is transmitted from the master MCU to each local MCU.

The first byte should hold the address of the local MCU. (in this case local MCU1.)

Each local R8A66171 checks the data (address) against command5 (each address) when the first byte (address) is received. The R8A66171 which matches the address starts to accept the following data (wakeup).

The R8A66171 which does not match the address, only accepts data, where the 9<sup>th</sup> bit is "1".

#### When CRC is enabled

When parity is enabled

Note: The wakeup function is automatically canceled when the transfer block data has been read by the MCU. (The wakeup mode continues.)

#### Error detection

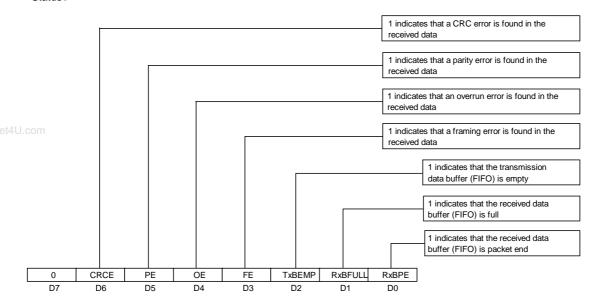

#### (1)Parity error

When a parity error occurs, D5 bit of status1 information is set. The data is send to the receive data buffer (FIFO).

#### (2)Framing error

When a framing error occurs, D3 bit of the status1 information is set. The data is sent to the receive data buffer (FIFO).

#### (3)Overrun error

When data is received before all data in the receive data buffer (FIFO) has been read by MCU, D4 bit of the status1 information is set as an overrun error.

In this case, the new data in the receive buffer are lost.

## www.DataSheet4U.com (4)CRC error

When an error occurs after receiving block check character, D6 bit of the status1 information is set. The above error information is maintained until D4 bit of command4 is set.

#### • Error reset

When D4 bit of command4 is 1, D3 bit, D4 bit, D5 bit and D6 bit of status1 are reset.

When an error reset pulse occurs, D4 bit of command4 becomes 0.

Again, D4 bit of command4 need not be adjusted to 0.

#### Internal reset

When D5 bit of command4 becomes 1, all command status information is reset, and the signal based on reset command status information is output to each output.

When an internal reset pulse occurs, D5 bit of command4 becomes 0.

Again, D5 bit of command4 need not be adjusted to 0.

#### SUPPLEMENTARY DESCRIPTION

Comparison between parity check and CRC

#### Parity check

Parity check needs only one additional bit and is highly efficient. The formula is straightforward, and includes even parity and odd parity checks. In both cases, one bit is added.

## CRC

The CRC poly-nominal expression is CRC-CCITT X<sup>16</sup>+X<sup>12</sup>+X<sup>5</sup>+1.

CRC deals with data characters in transmitted or received blocks. (Start, stop and wakeup bits are excluded.)

When the CRC is enabled, the transmit and receive data consists of block length (1~64 bytes) + 2 bytes (block check characters). The following table shows the comparison between parity check and CRC.

| Parity check | Burst error is not detected. (50% of which can be detected.)                  |  |

|--------------|-------------------------------------------------------------------------------|--|

| CRC          | Burst error can be detected. (Burst error detection rate is more than 99.9%.) |  |

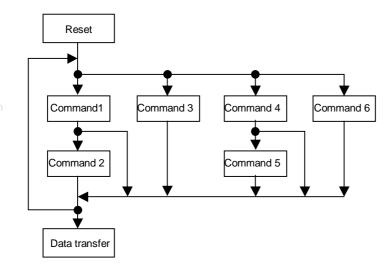

## **PROGRAMMING**

The command must be loaded first to the R8A66171 by the MCU before data communication. R8A66171 has 6 command registers.

Data transfer is possible when commands have been loaded to these command registers after reset.

The flowchart of the initial setting is shown in the following diagram.

Flowchart of the R8A66171 initial setting

## **COMMAND-INSTRUCTION FORMAT**

The commands are decoded by D7 and D6.

Note 1 : Priority is given to parity enable, if parity enable and CRC enable are both "1" (D3, D2=1).

Note 2 : TxD output wave is Stop bit (D5) setup value +1 (always).

Command2 (Baud rate setting. The second byte when D1 bit of the command1 is set to "1".)

Command3 (Block length setting)

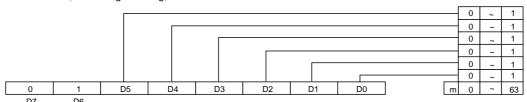

#### Command4

Command5 (Address setting. The second byte when D2 bit of the command4 is set to "1".)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

#### Command6

## STATUS INFORMATION

- Status 1 and 2 cannot address setting from external pin. Discrimination of status used to D7 bit.

- · Status 1 and 2 has read mutually. (There are not continuity read of same status.)

#### Status1

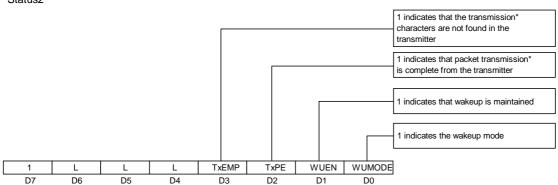

#### Status2

\* Transmitter = Transmit data buffer (FIFO) + Transmit buffer

## TRANSMISSION FORMAT

#### Transmit format

#### Parity enabled

MCU R8A66171

Data character (8 bits)

#### Assembled data format

| Start bit | Data sharester ( 9 hits ) | Wakeup bit       | Parity bit       | Stop bit     |

|-----------|---------------------------|------------------|------------------|--------------|

| ( 1 bit ) | Data character ( 8 bits ) | ( nil or 1 bit ) | ( nil or 1 bit ) | (1~2 bits)+1 |

#### Transmitter output

TxD mark condition (1 bit) Data character (8 bits) Wakeup bit Parity bit Stop bit (nil or 1 bit) (nil or 1 bit) (1~2 bits) + 1

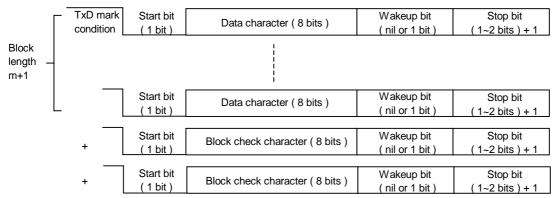

## CRC enabled

MCU R8A66171

Data character (8 bits)

#### After assembly

| Start bit | Data abarcator ( 9 hita ) | Wakeup bit       | Stop bit     |

|-----------|---------------------------|------------------|--------------|

| ( 1 bit ) | Data character ( 8 bits ) | ( nil or 1 bit ) | (1~2 bits)+1 |

#### Transmitter output

## TRANSMISSION FORMAT

#### Receive format

#### Parity enabled

#### Receiver input

| RxD mark  | Start bit | Data character ( 8 bits ) | Wakeup bit       | Parity bit       | Stop bit     |

|-----------|-----------|---------------------------|------------------|------------------|--------------|

| condition | ( 1 bit ) | Data character ( 8 bits ) | ( nil or 1 bit ) | ( nil or 1 bit ) | ( 1~2 bits ) |

#### Receive format

| Start bit | Data character ( 8 bits ) | Wakeup bit       | Parity bit       | Stop bit   |

|-----------|---------------------------|------------------|------------------|------------|

| ( 1 bit ) | Data Character ( 8 bits ) | ( nil or 1 bit ) | ( nil or 1 bit ) | (1~2 bits) |

www.DataSheet4U.comR8A66171 MCU

Data character (8 bits)

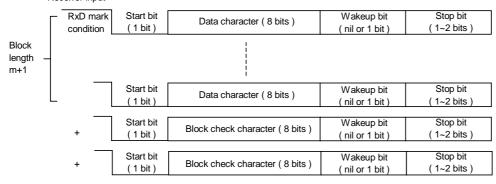

#### CRC enabled

#### Receive format

| Start bit | Data character ( 8 bits ) | Wakeup bit       | Stop bit     |

|-----------|---------------------------|------------------|--------------|

| ( 1 bit ) | Data character ( 0 bits ) | ( nil or 1 bit ) | ( 1~2 bits ) |

R8A66171 MCU

Data character (8 bits)

## ABSOLUTE MAXIMUM RATINGS (Ta=-40~85°C, unless otherwise noted)

| Symbol | Parameter           | Conditions                                                         | Ratings      | Unit     |

|--------|---------------------|--------------------------------------------------------------------|--------------|----------|

| Vcc    | Supply voltage      | Value using the CND pin                                            | -0.5~+7.0    | <b>V</b> |

| VI     | Input voltage       | _                                                                  | -0.5~Vcc+0.5 | V        |

| VO     | Output voltage      | Conditions  Value using the GND pin as reference  Actually mounted | -0.5~Vcc+0.5 | V        |

| Pd     | Power dissipation   | Actually mounted                                                   | 500          | mW       |

| Tstg   | Storage temperature |                                                                    | -65~150      | °C       |

## RECOMMENDED OPERATING CONDITIONS (Ta=-40~85°C, unless otherwise noted)

| Symbol           | Parameter             |                       |     | Unit |     |       |

|------------------|-----------------------|-----------------------|-----|------|-----|-------|

| Symbol Parameter |                       | ı                     | Min | Тур  | Max | Offic |

| Vcc              | Supply voltage        | 5.0V                  | 4.5 | 5.0  | 5.5 | V     |

|                  |                       | 3.3V                  | 3.0 | 3.3  | 3.6 | V     |

| GND              | Ground                |                       |     | 0    |     | V     |

| t4 <b>Topr</b> m | Operating temperature | Operating temperature |     |      | 85  | °C    |

## **ELECTRICAL CHARACTERISTICS**

5.0V version support specifications (Ta=-40~85 °C,Vcc=3.0~3.6V,GND=0V, unless otherwise noted)

| Cymphol | Doromotor                           | Toot conditions              | Limits   |     |                                                            | Unit |

|---------|-------------------------------------|------------------------------|----------|-----|------------------------------------------------------------|------|

| Symbol  | Parameter                           | Test conditions              | Min      | Тур | 0.25×Vcc 0.2×Vcc 0.8×Vcc 0.65×Vcc  0.55  1.0 -1.0 5.0 -5.0 | Unit |

| VIH     | High-level input voltage            | /RD, /WR, C//D, /CS, D0~D7   | 0.75×Vcc |     |                                                            | V    |

| VIL     | Low-level input voltage             | 7 /KD, /WK, C//D, /C3, D0~D7 |          |     | 0.25×Vcc                                                   | V    |

| VIH     | High-level input voltage            | - X1                         | 0.8×Vcc  |     |                                                            | V    |

| VIL     | Low-level input voltage             | ] ^1                         |          |     | 0.2×Vcc                                                    | V    |

| VT+     | Positive threshold voltgage         |                              | 0.35×Vcc |     | 0.8×Vcc                                                    | V    |

| VT-     | Negative threshold voltage          | RxD, /CTS, /RESET            | 0.2×Vcc  |     | 0.65×Vcc                                                   | V    |

| VH      | Hysteresis width                    |                              | 0.4      |     |                                                            | V    |

| VOH     | High-level output voltage           | IOH=-8mA /INT, D0~D7         | Vcc-0.8  |     |                                                            | V    |

| νОП     | High-level output voltage           | IOH=-24mA TxD, /RTS, P0, P1  | VCC-0.6  |     | 0.25×Vcc 0.2×Vcc 0.8×Vcc 0.65×Vcc  0.55 1.0 -1.0 5.0 -5.0  | V    |

| VOL     | Low-level output voltage            | IOL=8mA /INT, D0~D7          |          |     | 0.55                                                       | V    |

| VOL     | Low-level output voltage            | IoL=24mA TxD, /RTS, P0, P1   |          |     | 0.55                                                       | V    |

| IIH     | High-level input current            | VI=Vcc                       |          |     | 1.0                                                        | μA   |

| IIL     | Low-level input current             | VI=GND                       |          |     | -1.0                                                       | μΑ   |

| IOZH    | Off-state high-level output current | VO=Vcc                       |          |     | 5.0                                                        | μΑ   |

| IOZL    | Off-state low-level output current  | VO=GND                       |          |     | -5.0                                                       | μΑ   |

| ICC     | Static supply current               | VI=Vcc, GND                  |          |     | 40                                                         | mΑ   |

3.3V version support specifications (Ta=-40~85 °C,Vcc=3.0~3.6V,GND=0V, unless otherwise noted)

| Symbol   | Parameter                           | Test conditions             |          | Unit |          |       |

|----------|-------------------------------------|-----------------------------|----------|------|----------|-------|

| Syllibol | Farameter                           | rest conditions             | Min      | Тур  | Max      | Offic |

| VIH      | High-level input voltage            | /RD, /WR, C//D, /CS, D0~D7  | 0.75×Vcc |      |          | V     |

| VIL      | Low-level input voltage             | /KD, /WK, C//D, /C3, D0~D7  |          |      | 0.25×Vcc | V     |

| VIH      | High-level input voltage            | - X1                        | 0.8×Vcc  |      |          | V     |

| VIL      | Low-level input voltage             |                             |          |      | 0.2×Vcc  | V     |

| VT+      | Positive threshold voltgage         |                             | 0.35×Vcc |      | 0.8×Vcc  | V     |

| VT-      | Negative threshold voltage          | RxD, /CTS, /RESET           | 0.2×Vcc  |      | 0.65×Vcc | V     |

| VH       | Hysteresis width                    |                             | 0.4      |      |          | V     |

| VOH      | High-level output voltage           | IOH=-4mA /INT, D0~D7        | Vcc-0.6  |      |          | V     |

|          |                                     | IOH=-12mA TxD, /RTS, P0, P1 | VCC-0.0  |      |          | _ v   |

| VOL      | Low-level output voltage            | IoL=4mA /INT, D0~D7         |          |      | 0.4      | V     |

| VOL      | Low-level output voltage            | IOL=12mA TxD, /RTS, P0, P1  |          |      | 0.4      |       |

| IIH      | High-level input current            | VI=Vcc                      |          |      | 1.0      | μΑ    |

| IIL      | Low-level input current             | VI=GND                      |          |      | -1.0     | μΑ    |

| IOZH     | Off-state high-level output current | VO=Vcc                      |          |      | 5.0      | μA    |

| IOZL     | Off-state low-level output current  | VO=GND                      |          |      | -5.0     | μΑ    |

| ICC      | Static supply current               | VI=Vcc, GND                 |          |      | 25       | mΑ    |

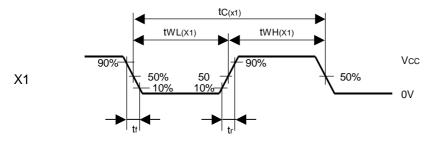

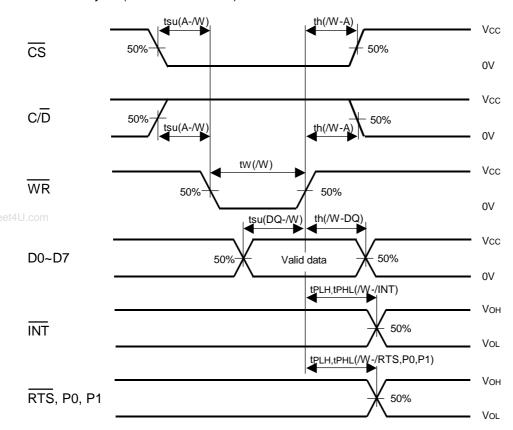

## TIMING REQUIREMENTS (Ta=-40~85 °C,Vcc=4.5~5.5V or Vcc=3.0~3.6V, unless otherwise noted)

| Symbol       | Parameter                                   | Test                      | Limits for 5.0V |      | Limits for 3.3V |     |      | Unit |     |       |

|--------------|---------------------------------------------|---------------------------|-----------------|------|-----------------|-----|------|------|-----|-------|

| Symbol       | i arameter                                  |                           | conditions      | Min  | Тур             | Max | Min  | Тур  | Max | Offic |

| tc1(X1)      | Clock frequency                             |                           |                 | 62.5 |                 |     | 66.6 |      |     | ns    |

| twH1(X1)     | Clock high-level pulse width                | (Except Wakeup, CRC mode) |                 | 30   |                 |     | 32   |      |     | ns    |

| twL1(X1)     | Clock low-level pulse width                 |                           |                 | 30   |                 |     | 32   |      |     | ns    |

| tc2(X1)      | Clock frequency                             |                           | 1               | 80   |                 |     | 90   |      |     | ns    |

| twH2(X1)     | Clock high-level pulse width                | (Wakeup, CRC mode)        |                 | 38   |                 |     | 42   |      |     | ns    |

| twL2(X1)     | Clock low-level pulse width                 |                           |                 | 38   |                 |     | 42   |      |     | ns    |

| tr(X1)       | Clock rise time                             |                           |                 |      |                 | 20  |      |      | 25  | ns    |

| tf(X1)       | Clock fall time                             |                           |                 |      |                 | 20  |      |      | 25  | ns    |

| tsu(A-/R)    | Address setup time before read (/CS, C//D)  |                           |                 | 0    |                 |     | 0    |      |     | ns    |

| th(/R-A)     | Address hold time after read (/CS, C//D)    |                           |                 | 0    |                 |     | 0    |      |     | ns    |

| tw(/R)       | Read pulse width                            |                           |                 | 100  |                 |     | 110  |      |     | ns    |

| tsu(A-/W)    | Address setup time before write (/CS, C//D) |                           |                 | 0    |                 |     | 0    |      |     | ns    |

| th(/W-A)     | Address hold time after write (/CS, C//D)   |                           |                 | 0    |                 |     | 0    |      |     | ns    |

| tw(/W)       | Write pulse width                           |                           |                 | 100  |                 |     | 110  |      |     | ns    |

| tsu(DQ-/W)   | Data setup time before write                |                           |                 | 50   |                 |     | 55   |      |     | ns    |

| th(/W-DQ)    | Data hold time after write                  |                           |                 | 5    |                 |     | 6    |      |     | ns    |

| trec(/RESET) | Recovery time between write                 |                           |                 | 100  |                 |     | 110  |      |     | ns    |

| tw(/RESET)   | Reset pulse width                           |                           |                 | 100  |                 |     | 110  |      |     | ns    |

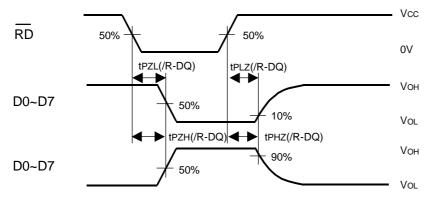

# SWITCHING CHARACTERISTICS (Ta=-40~85°C,Vcc=4.5~5.5V or Vcc=3.0~3.6V, unless otherwise noted)

| Symbol        | Parameter                                         | Test | Limits for 5.0V |     | Limits for 3.3V |     |     | Unit |       |

|---------------|---------------------------------------------------|------|-----------------|-----|-----------------|-----|-----|------|-------|

| Gymbol        | r arameter                                        |      | Min             | Тур | Max             | Min | Тур | Max  | Offic |

| tpzh(/R-DQ)   | Data suitaut analyla tima after your              |      |                 |     | 100             |     |     | 110  | ns    |

| tPZL(/R-DQ)   | Data output enable time after read                |      |                 |     | 100             |     |     | 110  | ns    |

| tphz(/R-DQ)   | Data cutavit disable time after read              |      |                 |     | 85              |     |     | 95   | ns    |

| tPLZ(/R-DQ)   | Data output disable time after read               |      |                 |     | 85              |     |     | 95   | ns    |

| tPLH(/R-/INT) | //NIT output proposation time ofter road data     |      |                 |     | 170             |     |     | 185  | ns    |

| tPHL(/R-/INT) | INT output propagation time after read data       |      |                 |     | 170             |     |     | 185  | ns    |

| tPLH(/W-/INT) | INT output propagation time after write data      |      |                 |     | 150             |     |     | 165  | ns    |

| tphl(/W-/INT) | yiivi output propagation time after write data    |      |                 |     | 150             |     |     | 165  | ns    |

| tplh(/W-/INT) | INT output propagation time after write command   |      |                 |     | 100             |     |     | 110  | ns    |

| tphl(/W-/INT) | (command 4)                                       |      |                 |     | 100             |     |     | 110  | ns    |

| tPLH(/W-/INT) | INT output propagation time after write command   |      |                 |     | 100             |     |     | 110  | ns    |

| tPHL(/W-/INT) | (command 6)                                       |      |                 |     | 100             |     |     | 110  | ns    |

| tPLH(/W-P0)   | P0 output propagation time after write command    |      |                 |     | 70              |     |     | 75   | ns    |

| tPHL(/W-P0)   | r o output propagation time after write command   |      |                 |     | 70              |     |     | 75   | ns    |

| tPLH(/W-P1)   | P1 output propagation time after write command    |      |                 |     | 70              |     |     | 75   | ns    |

| tPHL(/W-P1)   | i i output propagation time after write command   |      |                 |     | 70              | -   |     | 75   | ns    |

| tPLH(/W-/RTS) | RTS output propagation time after write command   |      |                 |     | 70              |     |     | 75   | ns    |

| tphl(/W-/RTS) | yrcro output propagation time after write command |      |                 |     | 70              |     |     | 75   | ns    |

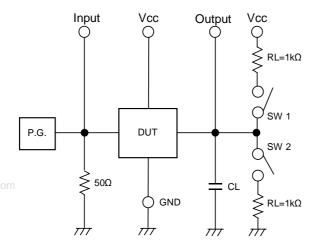

## **TEST CIRCUIT**

| Parameter  | SW 1   | SW 2   |

|------------|--------|--------|

| tPLH, tPHL | Open   | Open   |

| tPLZ       | Closed | Open   |

| tPHZ       | Open   | Closed |

| tPZL       | Closed | Open   |

| tPZH       | Open   | Closed |

- (1) The pulse generator (PG) has the following characteristics (10%~90%) tr=3ns, tf=3ns

- (2) The capacitance CL=150pF includes stray wiring capacitance and the probe input capacitance.

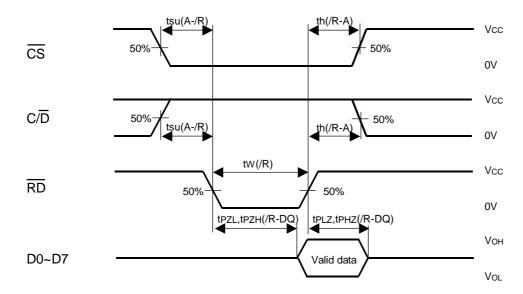

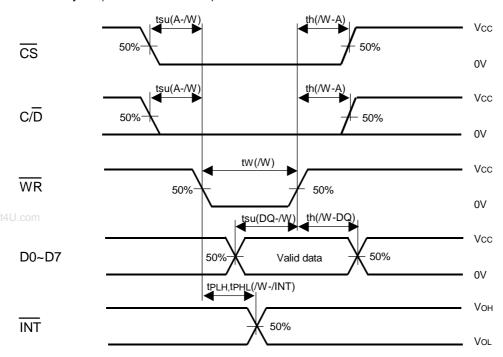

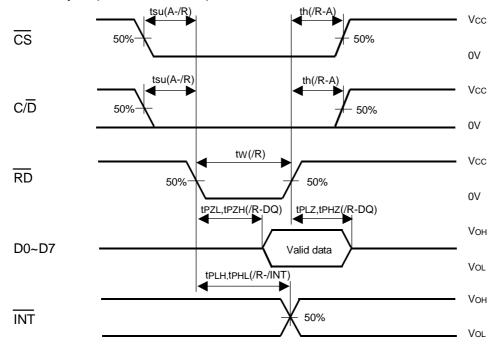

## **TIMING DIAGRAM**

Input/output waveform at read data and read status

## **Clock Timing**

Write control cycle (MCU R8A66171)

## Read control cycle (R8A66171 MCU)

## Write data cycle (MCU R8A66171)

## Read data cycle (R8A66171 MCU)

## Transmitter control and flag timing

## (1) Block length=1

## (2) Block length=3

## (3) Block length=5

## Receiver control and flag timing

## (1) Block length=1

## (2) Block length=3

## (3)Block length=5

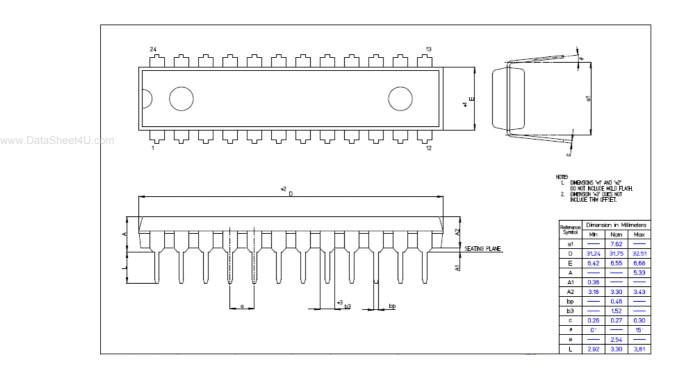

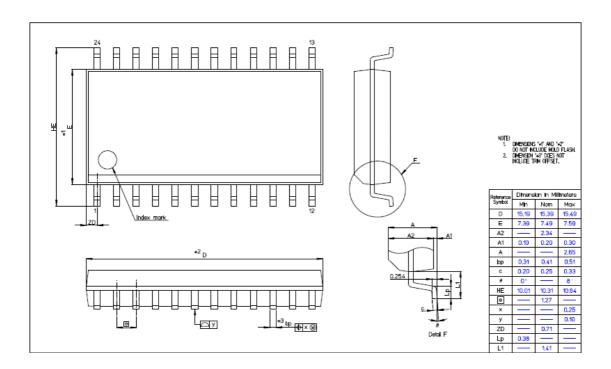

## PACKAGE OUTLINE

| Product Name | Package   | RENESAS Code | Previous Code |

|--------------|-----------|--------------|---------------|

| R8A66171DD   | 24pin DIP | PRDP0024AF-A | 24P4X-A       |

| R8A66171SP   | 24pin SOP | PRSP0024DF-A | 24P2X-B       |

All trademarks and registered trademarks are the property of their respective owners.

## Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. Initis document is provided for reference purposes only so that Renease customers may select the appropriate Reneases products for their use. Ranesas neither makes may not only the rights of any other rights of rany other rights of Reneases and Third Products of Reneases and Third Reneases and Products of the technology described in this document.

2. Reneases shall have no liability for damages or infingement of any intellectual property or other rights arising out of the use of any information in this document, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass and regulations, and procedures required by such laws and regulations, and procedures are such as the development of the date of t

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

RENESAS SALES OFFICES

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com