# RC7222-A1 Multi-Functional Ethernet Converter

# Datasheet V1.00 Dec.2009

# **Copyright Notice**

All copyrights of this document belong to Raycom. Contents of this document are subject to change without notice, which are suitable for reading by employees, agents and clients of Raycom during their usage of relevant products. Without written permission of Raycom, copying, reprinting of this document by any entity or individual is strictly forbidden.

# **Revision History**

| Version | Date      | Description          |

|---------|-----------|----------------------|

| V1.00   | 2009-12-4 | Preliminary Released |

# Contents

| 1 Overview     |                                     | 6 |

|----------------|-------------------------------------|---|

| 2 Features     |                                     | 6 |

| 3 Pin Descript | ions                                | 9 |

| 3.1 Pin Assig  | nment                               | 9 |

| 3.2 Pin Desc   | ription                             | 9 |

| 4 Functional D | Descriptions                        | 9 |

| 4.1 Block Dia  | agram 1                             | 9 |

| 4.2 WAN Inte   | erface 1                            | 9 |

| 4.2.1 WAN      | I Interface Multiplexing (MUX) 1    | 9 |

| 4.2.1.1        | Input/output Multiplexing Pin1      | 9 |

| 4.2.1.2        | Alarm output multiplexing pin2      | 0 |

| 4.2.2 Optic    | cal Interface2                      | 1 |

| 4.2.2.1        | Low-speed Serial Data Channel 2     | 1 |

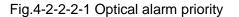

| 4.2.2.2        | Optical Alarm                       | 1 |

| 4.2.3 E1 Ir    | iterface2                           | 3 |

| 4.2.3.1        | E1 Alarm                            | 3 |

| 4.2.4 WAN      | I interface loopback 2              | 4 |

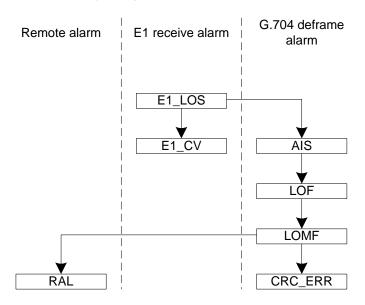

| 4.2.4.1        | Optical Interface Loopback          | 5 |

| 4.2.4.2        | E1 Interface Loopback               | 7 |

| 4.2.4.3        | Remote Loopback Controlled by MCU 2 |   |

| 4.2.5 Timir    | ng In WAN Interface2                | 9 |

| 4.2.6 Ethe     | rnet Loopback Prevention            | 0 |

| 4.3 Timeslot   | Assignment3                         | 1 |

|                | slot Assignment Configuration       |   |

| 4.4 ST_BUS     | Bus                                 | 4 |

| 4.5 MII Interf | ace3                                | 5 |

| 4.5.1 MII Ir   | nterface                            | 5 |

| 4.5.2 MDIC     | D Interface                         | 6 |

| 4.5.3 MAC      | Work Mode                           | 7 |

|                | amer/Deframer                       |   |

| 4.6.1 Mana     | agement frame 4                     | 0 |

| 4.7 SDRAM Interface                         | 43 |

|---------------------------------------------|----|

| 4.7.1 SDRAM Pin                             | 43 |

| 4.7.2 Buffer Size Adjustment                | 44 |

| 4.7.3 Frame Statistic                       | 45 |

| 4.8 SA Bit Application                      | 48 |

| 4.9 Test Function                           | 49 |

| 4.9.1 SDRAM Test                            | 49 |

| 4.9.2 Bit Error Test                        | 49 |

| 4.9.3 Test Indicators                       | 50 |

| 4.10 Software Reset                         | 51 |

| 5 Management Description                    | 52 |

| 5.1 Register Address Organization           | 52 |

| 5.2 Management Interface (UART/I2C)         | 53 |

| 5.3 UART Instructions                       | 54 |

| 5.4 I <sup>2</sup> C Instruction            | 57 |

| 5.5 Register Description                    | 58 |

| 5.5.1 MIB Register                          | 58 |

| 5.5.2 Management Frame Register             | 79 |

| 5.5.3 Global Register                       | 81 |

| 6 Application                               | 83 |

| 6.1 Ethernet Bridge System                  | 83 |

| 6.2 Ethernet Optical Modem                  |    |

| 7 Electrical Characteristics                | 85 |

| 7.1 Absolute Maximum Ratings                | 85 |

| 7.2 Normal Operating Conditions             | 85 |

| 7.2.1 Power Consumption                     | 86 |

| 7.3 DC Characteristics                      | 86 |

| 7.4 AC Characteristic                       | 87 |

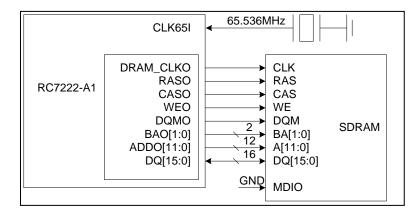

| 7.4.1 MII Interface Timing                  | 87 |

| 7.4.2 SDRAM Interface Timing                | 88 |

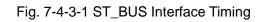

| 7.4.3 ST_BUS Interface Timing               | 90 |

| 7.4.4 Serial Configuration Interface Timing | 91 |

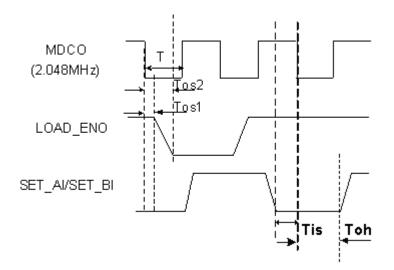

| 8 Package Information                       | 92 |

# Figure Index

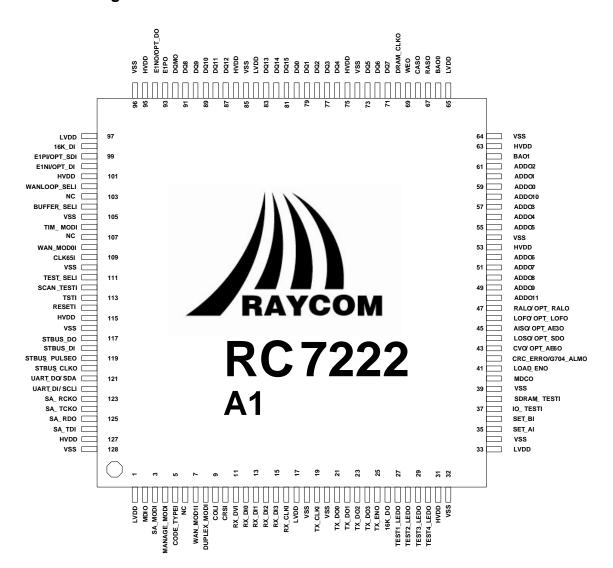

| Fig.3-1-1 Pin Assignment           | 9  |

|------------------------------------|----|

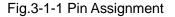

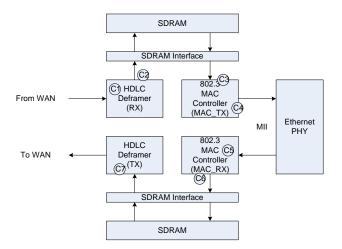

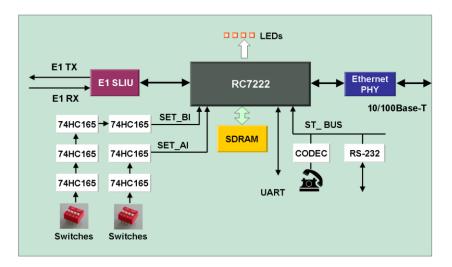

| Fig.4-1-1 RC7222-A1 Block Diagram  | 19 |

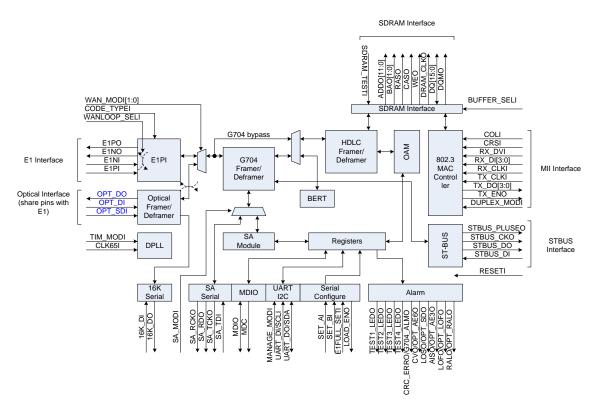

| Fig.4-2-2-1 Optical alarm priority | 22 |

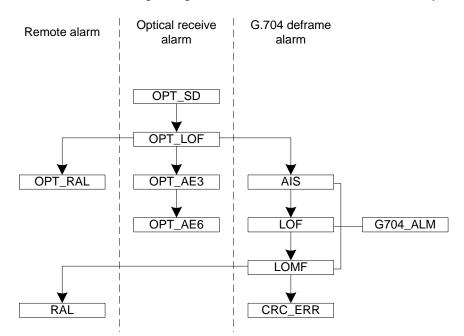

| Fig.4-2-3-1-1 E1 alarm priority    | 24 |

|                                    |    |

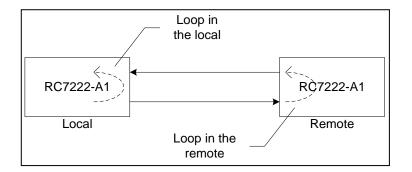

| Fig.4-2-4-1-1 Optical Interface loopback                             |    |

|----------------------------------------------------------------------|----|

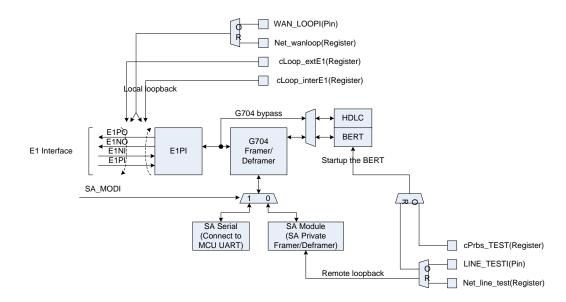

| Fig.4-2-4-2-1 E1 Interface Loopback                                  | 27 |

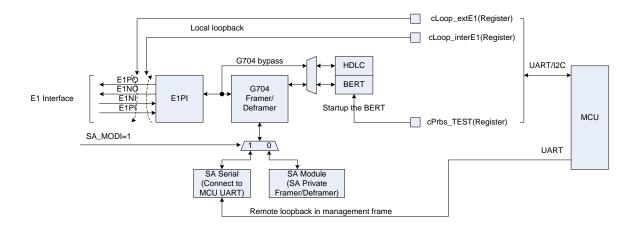

| Fig.4-2-4-3-1 MCU Remote Controlling via SA Interface                | 29 |

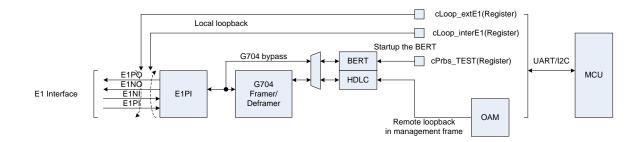

| Fig.4-2-4-3-2 MCU Remote Controlling via HDLC Management Frame       | 29 |

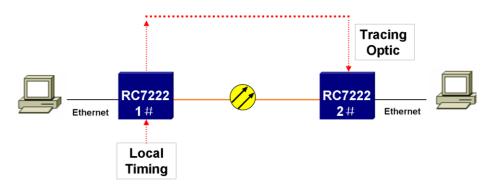

| Fig.4-2-5-1 Timing Application                                       | 30 |

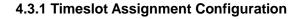

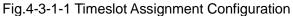

| Fig.4-3-1-1 Timeslot Assignment                                      | 31 |

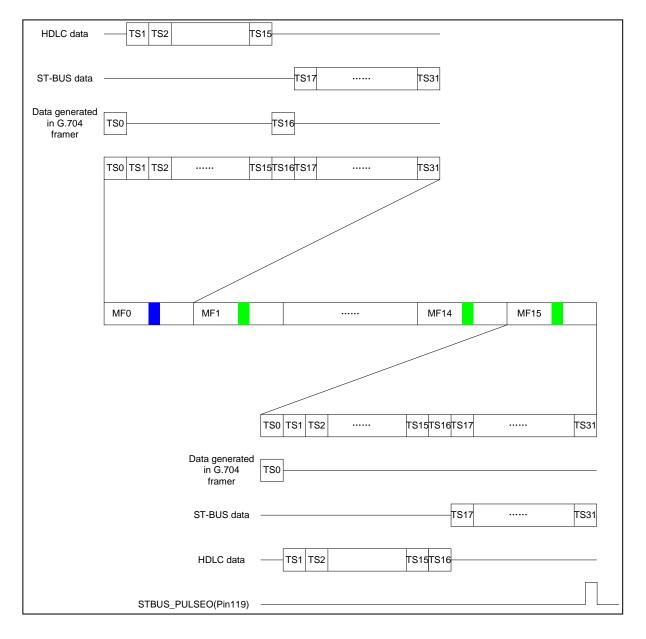

| Fig.4-3-1-1 Timeslot Assignment Configuration                        | 33 |

| Fig.4-3-1-2 Serial configuration interface schematic diagram         | 34 |

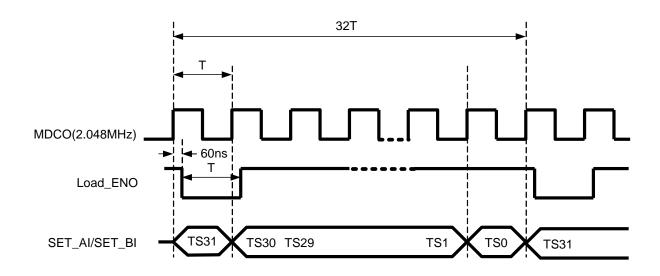

| Fig.4-4-1 ST_BUS schematic diagram                                   | 35 |

| Fig.4-5-1-1 MII Interface Connection                                 | 36 |

| Fig.4-5-2-1 Management Interface Connection                          | 37 |

| Fig.4-6-1 RJ017 HDLC frame format                                    | 40 |

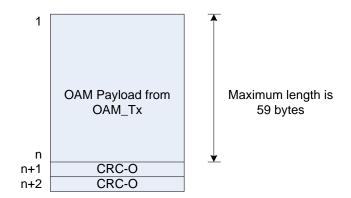

| Fig.4-6-1-1 Management frame format                                  | 41 |

| Fig.4-7-1-1 Connection between RC7222-A1 and SDRAM                   | 44 |

| Fig.4-7-2-1 SDRAM buffer schematic diagram.                          | 44 |

| Fig.4-9-2-1 Bit Error Test Illustration                              | 50 |

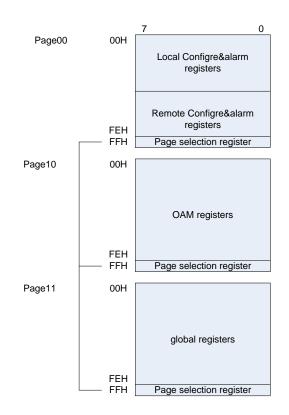

| Fig.5-1-1 Register Address Organization                              | 53 |

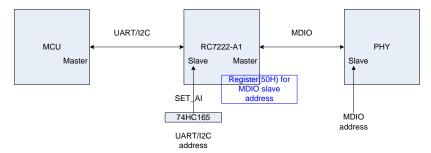

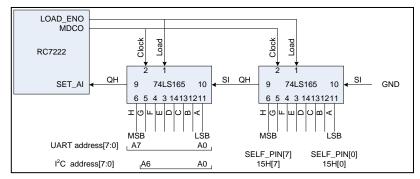

| Fig.5-2-1 Device address for management and Use-defined signal input | 54 |

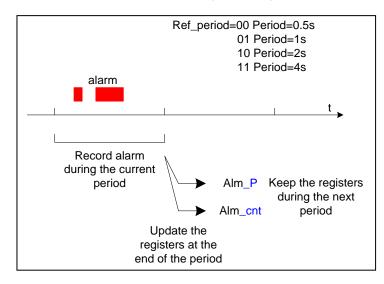

| Fig. 5-5-1-1 the update of Statistic and latch register              | 59 |

| Fig. 6-1-1 Ethernet Bridge System Structure                          | 83 |

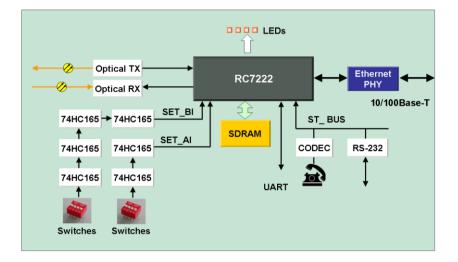

| Fig. 6-2-1 Ethernet Optical Modem Structure                          | 84 |

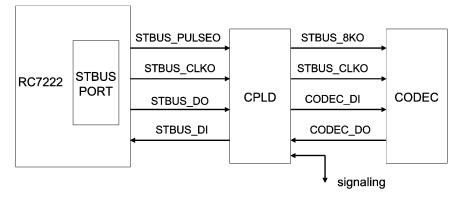

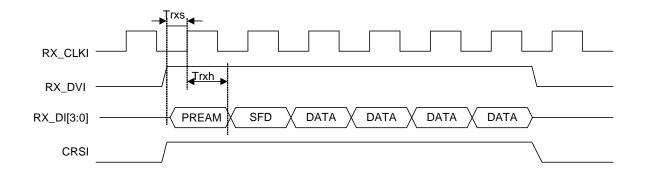

| Fig. 7-4-1-1 MII Receive Timing                                      | 87 |

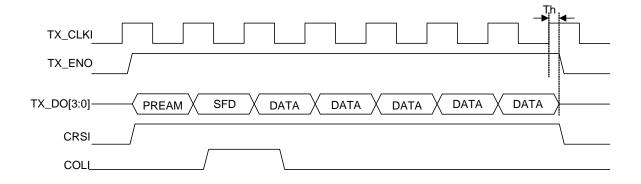

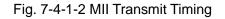

| Fig. 7-4-1-2 MII Transmit Timing                                     | 87 |

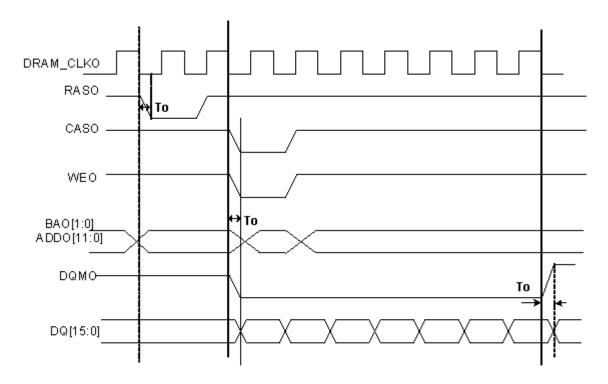

| Fig. 7-4-2-1 SDRAM interface timing for write                        | 88 |

| Fig. 7-4-2-2 SDRAM interface timing for read                         | 89 |

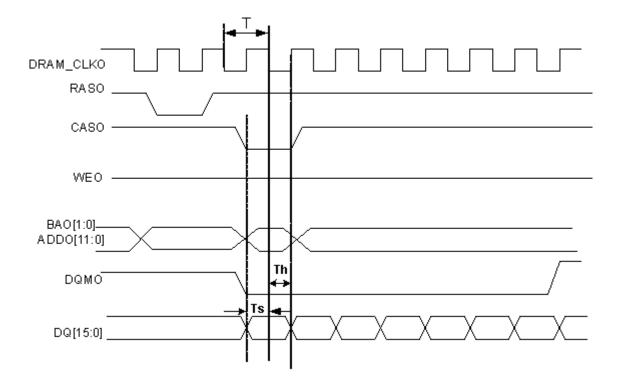

| Fig. 7-4-3-1 ST_BUS Interface Timing                                 | 90 |

| Fig. 7-4-4-1 Serial Configuration Interface Timing                   | 91 |

| Fig. 8-1 RC7222-A1 Package                                           | 92 |

# Table Index

| Table 3-2-1 Pin Descriptions (Arranged as pin No.)                      | . 10 |

|-------------------------------------------------------------------------|------|

| Table 4-2-1-1 WAN interface description                                 | . 19 |

| Table 4-2-1-2 WAN Interface Alarm Specification                         | . 20 |

| Table 4-2-4-1 WAN Interface loopback                                    | . 24 |

| Table 4-5-3-2 Ethernet interface work mode configuration                | . 38 |

| Table 4-6-1-1 Management frame transmitting and receiving               | . 42 |

| Table 4-9-3-1 Test Indicators                                           | . 50 |

| Table 5-3-1 UART Instructions of Configuration and Inquiry              | . 54 |

| Table 5-3-2 UART acknowledge instructions                               | . 54 |

| Table 5-3-3 Descriptions for UART configuration and inquiry instruction | . 55 |

| Table 5-3-4 Descriptions for UART Acknowledged Frame                    | . 56 |

| Table 5-4-1 I2C configuration and inquiry instruction Frame Format       | 57 |

|--------------------------------------------------------------------------|----|

| Table 5-4-2 I2C write operations to register                             | 57 |

| Table 5-4-3 I2C read operation to register                               | 58 |

| Table 5-5-1-1 MIB register (Page00)                                      | 60 |

| Table 5-5-2-1 Management Frame Register(Page10)                          | 79 |

| Table 5-5-3-1 Global Register(Page11)                                    | 81 |

| Table 7-1-1 Absolute Maximum Ratings (VSS = 0V)                          | 85 |

| Table 7-2-1 Recommended Operating Conditions                             | 85 |

| Table 7-3-1 DC Characteristics (HVDD=3.3VDC±0.3V, VSS=0V, Tj=-40°C~85°C) | 86 |

| Table 7-4-1-1 Timing Specifications of MII Interface                     | 87 |

| Table 7-4-2-1 Timing Specifications of SDARM Interface                   | 89 |

| Table 7-4-3-1 Timing specification of ST_BUS Interface                   | 90 |

| Table 7-4-4-1 Timing specification of Serial configuration interface     | 91 |

| Table 8-1 Package Dimension                                              | 92 |

# **1** Overview

The RC7222-A1 is a highly integrated ASIC for transmitting Ethernet frames over TDM. The TDM interface is called Wide Access Network(WAN), which includes E1(framed or unframed) or PDH optical port. HDLC protocol is adopted to encapsulate the Ethernet frames, which is compatible with the protocol in the RJ017.

The RC7222-A1 supports mapping of the registers from the remote to the local over the PDH optical frame overhead or SA bits in the G.704 frame, that the MCU in local device can get information of the remote device only from registers of the local RC7222-A1. The RC7222-A1 also supports user-defined management frame, which can be encapsulated and transmitted together with Ethernet frames in HDLC format. Then the MCU can access for each other even over unframed E1.

In addition the RC7222-A1 can be configured by pins that is the RC7222-A1 can work well without MCU.

# 2 Features

- Ethernet Interface

- Standard Media Independent Interface (MII) and MDIO management interface for connection to Ethernet PHY

- > 10M/100Mbps, full/half duplex supported, fully IEEE 802.3 compatible

- > Frames with length from 64 to 2031 bytes transparently transferred

- Illegal frames such as CRC error packets, undersized packets (less than 64 bytes) and oversized packets (more than 2031 bytes) discarded

- > PAUSE flow control ability in full duplex mode

- > Exhaustive alarm detection and performance statistic

- E1/FE1 Interface

- > Compatible with ITU-T recommendations: G.703, G.704, G.706 and G.732

- > Optional line code: HDB3 or NRZ

- Local oscillator or the clock recovered from the line for Timing source, more flexible for different applications

- Optical Interface

- 4.096Mbps for channel rate,1B1C coding, with embedded line Clock Data Recovery (CDR) unit

- A transparent user-defined asynchronous channel with 16KHz sampling frequency through optical frame overhead, which can be used as UART channel less than 4800bps.

- > TTL interface

- Local oscillator or the clock recovered from the line for Timing source, more flexible for different applications

- G.704 framer /deframer

- Support G.704 framer/deframer or G.704 bypass(Unframed E1)

- PCM30/31 selectable

- CRC-4/Non-CRC-4 multiframe auto adaptive for G.704 deframer, CRC-4 multiframe for G.704 framer only

- > A transparent synchronous 20Kbps data path provided by spare bits (SA) in FE1 mode

- Ethernet frame encapsulation

- > HDLC encapsulation, compatible with RJ017

- Management frame

- > HDLC encapsulation, transmitted with Ethernet frame in the same channel

- External 64Mbit SDRAM with cache from 32 to 512 frames

- Network Management

- > 19200bps UART interface and 100Kbps I<sup>2</sup>C interface available for access

- 8-bit device address

- Register mapping of the remote RC7222-A1 through SA bits and register mapping of the PHY through MDIO

- > Software reset, that is the MCU can reset the chip through the register

- Perfect alarm detection and performance statistic, provides performance statistic record with time in seconds

- Automatic line loop-back detection and stop transferring Ethernet frame to MII when a line loop-back is detected, and this method has been registered as patent

- Embedded BERT and various loop back for troubleshooting

- 0.25um CMOS

- Voltages: Core 2.5V; I/O 3.3V

- 128-pin LQFP package

# 3.1 Pin Assignment

# **3.2 Pin Description**

Symbol explanation

- I: Input

- O: Output

- IO: Bi-directional

- PU: Pull-up resistor

PD: Pull-down resistor

Schmitt: Schmitt input

Z: High impedance

Power: Power pin

| Pin | Pin Name    | Туре        | Descriptions                                                                                                                                                                                                                                                    |

|-----|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LVDD        | Power       | 2.5V                                                                                                                                                                                                                                                            |

| 2   | MDIO        | IO<br>(6mA) | MII Management interface: data input/output.                                                                                                                                                                                                                    |

| 3   | SA_MODI     | l (PD)      | Usage of the data path formed by the spare bits in<br>G.704:<br>1 = transparent user-defined data channel;<br>0 = RC7222-A1-specific data path                                                                                                                  |

| 4   | MANAGE_MODI | I           | Management access interface selection:<br>1 = I <sup>2</sup> C interface;<br>0 = UART interface                                                                                                                                                                 |

| 5   | CODE_TYPEI  | l (PD)      | E1 line code type:<br>1 = NRZ code;<br>0 = HDB3 code                                                                                                                                                                                                            |

| 6   | NC          | -           | Not used, connect high level or nothing.                                                                                                                                                                                                                        |

| 7   | WAN_MOD1I   | l (PD)      | <ul> <li>WAN interface options selection, combined with the signal WAN_MOD0I (PIN108).</li> <li>WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;</li> <li>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;</li> <li>Refer to section 4.2.1.1 for details.</li> </ul> |

| 8   | DUPLEX_MODI | I           | Duplex mode for RC7222-A1 MAC<br>1= MAC module works in half-duplex mode;<br>0= MAC module works in full-duplex mode                                                                                                                                            |

| 9  | COLI        | I       | MII collision signal, provided by Ethernet PHY. This       |

|----|-------------|---------|------------------------------------------------------------|

|    |             |         | signal is high when a collision is detected on the media.  |

| 10 | CRSI        | 1       | MII carrier sense signal, provided by Ethernet PHY. This   |

| 10 |             |         | signal is high if the media is not idle.                   |

| 11 |             |         | MII receive data valid indication, active high, sampled by |

| 11 | RX_DVI      |         | the rising edge of RX_CLKI                                 |

| 12 | RX_DI0      |         |                                                            |

| 13 | RX_DI1      |         | MII receive data input, sampled synchronously with the     |

| 14 | RX_DI2      |         | rising edge of RX_CLKI                                     |

| 15 | RX_DI3      |         |                                                            |

| 10 |             | I       | MII receiving clock, provided by Ethernet PHY. The         |

| 16 | RX_CLKI     |         | clock frequency is 2.5MHz or 25MHz                         |

| 17 | LVDD        | Power   | 2.5V                                                       |

| 18 | VSS         | Power   | Ground                                                     |

| 10 |             | I       | MII transmitting clock, provided by Ethernet PHY. The      |

| 19 | TX_CLKI     |         | clock frequency is 2.5MHz or 25MHz                         |

| 20 | VSS         | Power   | Ground                                                     |

| 21 | TX_DO0      |         |                                                            |

| 22 | TX_DO1      |         | MII transmit data output, presented synchronously with     |

| 23 | TX_DO2      | O (6mA) | the rising edge of TX_CLKI                                 |

| 24 | TX_DO3      |         |                                                            |

|    |             | O (6mA) | MII transmit enable, asserted high, synchronous with       |

| 25 | TX_ENO      |         | the rising edge of TX_CLKI.                                |

|    |             |         | Output signal for 16Kbps auxiliary data path in optical    |

| 26 | 16K_DO      | O (3mA) | interface mode (WAN_MOD1I/WAN_MOD0I=11),                   |

|    |             |         | otherwise NC.                                              |

| 27 | TEST1_LEDO  | _       | Chip work status output, LED indicator can be              |

| 28 | TEST2_LEDO  | 0       | connected outside to indicate the work status. For more    |

| 29 | (3mA) (3mA) |         | detailed information please refer to the section 4.9.3     |

| L  | l           | I       | I                                                          |

| 30 | TEST4_LEDO        |                         |                                                            |

|----|-------------------|-------------------------|------------------------------------------------------------|

| 31 | HVDD              | Power                   | 3.3V                                                       |

| 32 | VSS               | Power                   | Ground                                                     |

| 33 | LVDD              | Power                   | 2.5V                                                       |

| 34 | VSS               | Power                   | Ground                                                     |

|    |                   |                         | Serial input signal for network management address         |

|    |                   |                         | and user-defined information.                              |

| 35 | SET_AI            | I                       | 74HC165 can be connected outside to implement              |

|    |                   |                         | parallel-to serial conversion, refer to section 5.2 for    |

|    |                   |                         | more.                                                      |

|    |                   |                         | Serial input signal for bandwidth configuration.           |

| 00 |                   |                         | 74HC165 can be connected outside to implement              |

| 36 | SET_BI            | I                       | parallel-to serial conversion, refer to section 4.3.1 for  |

|    |                   |                         | more.                                                      |

| 07 |                   |                         | It is used for chip test purpose,                          |

| 37 | IO_TESTI          | I (PD)                  | It should connect ground in normal use                     |

|    |                   | I (PD)                  | External SDRAM test function enable:                       |

|    |                   |                         | 1 = SDRAM test mode;                                       |

| 38 | SDRAM_TESTI       |                         | 0 = normal                                                 |

|    |                   |                         | Note: The test result will be output via pin TEST_LEDO,    |

|    |                   |                         | refer to section 4.9.1 for more.                           |

| 39 | VSS               | Power                   | Ground                                                     |

|    |                   |                         | 2.048MHz clock output, timing source for MDIO of MII       |

| 10 | MDCO              | $O(0, \infty, \Lambda)$ | management interface, as well as work clock of the         |

| 40 |                   | O (6mA)                 | external 74HC165 connected with serial input of SET_AI     |

|    |                   |                         | and SET_BI. Refer to <i>Fig. 7.4.3</i> for timing diagram. |

|    |                   | O (6mA)                 | Shift control signal for serial configuration data input,  |

| 41 | LOAD_ENO          |                         | direct connection to 74HC165. Timing diagram in Fig        |

|    |                   |                         | 7.4.3.                                                     |

|    | Note: Pin42-Pin47 | is alarm o              | utput pins for WAN interface, high level indicates alarm   |

٦

|    | occurring. Alarm inhibit has been preprocessed in interior chip. Refer to section 4.2.1 |                |                                                          |

|----|-----------------------------------------------------------------------------------------|----------------|----------------------------------------------------------|

|    | for more                                                                                |                |                                                          |

|    |                                                                                         |                | If E1 is set as the WAN interface (WAN_MODI=01): This    |

| 42 | CRC_ERRO/                                                                               | O (3mA)        | pin acts as a CRC error indicator;                       |

| 42 | E1_ALMO                                                                                 |                | If optical interface is selected (WAN_MODI=11): This pin |

|    |                                                                                         |                | acts as an AIS or LOF indicator.                         |

|    |                                                                                         |                | In E1 mode(WAN_MODI=01): this pin indicates the          |

| 43 | CVO/                                                                                    | $O(2m\Lambda)$ | alarm of Code Violation;                                 |

| 43 | OPT_AE6O                                                                                | O (3mA)        | In Optic mode (WAN_MODI=11): it indicates BER of         |

|    |                                                                                         |                | 10 <sup>-6</sup> .                                       |

|    |                                                                                         |                | In E1 mode (WAN_MODI=01): this pin is the indicator of   |

| 44 | LOSO/                                                                                   | O(2mA)         | LOS alarm;                                               |

| 44 | OPT_SDO                                                                                 | O (3mA)        | In Optic mode (WAN_MODI=11): it indicates the optical    |

|    |                                                                                         |                | LOS alarm.                                               |

|    |                                                                                         |                | In E1 mode (WAN_MODI=01): this pin is the indicator of   |

| 45 | AISO/                                                                                   | O (3mA)        | G.704 AIS alarm;                                         |

|    | OPT_AE3O                                                                                |                | In Optic mode (WAN_MODI=11): it indicates BER of         |

|    |                                                                                         |                | 10 <sup>-3</sup> .                                       |

|    | LOFO/                                                                                   |                | In E1 mode, this pin is the indicator of LOF alarm;      |

| 46 | OPT_LOFO                                                                                | O (3mA)        | In Optic mode (WAN_MODI=11): it indicates the optical    |

|    |                                                                                         |                | LOF alarm.                                               |

|    |                                                                                         |                | In E1 mode (WAN_MODI=01): this pin is the indicator of   |

| 47 | RALO/                                                                                   | O (3mA)        | RAL alarm;                                               |

|    | OPT_RALO                                                                                | 0 (0117)       | In Optic mode (WAN_MODI=11): it indicates the remote     |

|    |                                                                                         |                | alarm of optical line.                                   |

| 48 | ADDO11                                                                                  |                |                                                          |

| 49 | ADDO9                                                                                   | O (6mA)        | SDRAM address outputs, with ADDO11 the most              |

| 50 | ADDO8                                                                                   |                | significant bit, and ADDO0 the lowest significant bit.   |

| 51 | ADDO7                                                                                   |                | Significant bit, and ADDOU the lowest significant bit.   |

| 52 | ADDO6                                                                                   |                |                                                          |

| 53 | HVDD      | Power       | 3.3V                                                                               |

|----|-----------|-------------|------------------------------------------------------------------------------------|

| 54 | VSS       | Power       | Ground                                                                             |

| 55 | ADDO5     |             |                                                                                    |

| 56 | ADDO4     |             |                                                                                    |

| 57 | ADDO3     |             | CDDAM address subsuts with ADDAM the most                                          |

| 58 | ADDO10    | O (6mA)     | SDRAM address outputs, with ADDO11 the most                                        |

| 59 | ADDO0     |             | significant bit, and ADDO0 the least significant bit.                              |

| 60 | ADDO1     |             |                                                                                    |

| 61 | ADDO2     |             |                                                                                    |

| 62 | BAO1      | O (6mA)     | SDRAM BANK address, most significant bit (MSB)                                     |

| 63 | HVDD      | Power       | 3.3V                                                                               |

| 64 | VSS       | Power       | Ground                                                                             |

| 65 | LVDD      | Power       | 2.5V                                                                               |

| 66 | BAO0      | O (6mA)     | SDRAM BANK address, least significant bit (LSB)                                    |

| 67 | RASO      |             | Row Address Strobe, Column Address Strobe, Write                                   |

| 68 | CASO      | O (6mA)     | Enable signal outputs. Combined for SDRAM                                          |

| 69 | WEO       |             | controlling.                                                                       |

| 70 | DRAM_CLKO | O (6mA)     | Reference clock for the SDRAM, generated by dividing the CLK65I frequency by half. |

| 71 | DQ7       | 10          |                                                                                    |

| 72 | DQ6       |             | Data bus interface to SDRAM                                                        |

| 73 | DQ5       | (6mA)       |                                                                                    |

| 74 | VSS       | Power       | Ground                                                                             |

| 75 | HVDD      | Power       | 3.3V                                                                               |

| 76 | DQ4       |             |                                                                                    |

| 77 | DQ3       |             |                                                                                    |

| 78 | DQ2       | IO<br>(6mA) | Data bus interface to SDRAM                                                        |

| 79 | DQ1       | - (6mA)     |                                                                                    |

| 80 | DQ0       |             |                                                                                    |

| 81 | DQ15              |             |                                                              |

|----|-------------------|-------------|--------------------------------------------------------------|

| 82 | DQ14              |             |                                                              |

| 83 | DQ13              |             |                                                              |

| 84 | LVDD              | Power       | 2.5V                                                         |

| 85 | VSS               | Power       | Ground                                                       |

| 86 | HVDD              | Power       | 3.3V                                                         |

| 87 | DQ12              |             |                                                              |

| 88 | DQ11              |             |                                                              |

| 89 | DQ10              | IO<br>(6mA) | Data bus interface to SDRAM                                  |

| 90 | DQ9               | (onia)      |                                                              |

| 91 | DQ8               |             |                                                              |

| 92 | DQMO              | O (6mA)     | Data inhibit signal for SDRAM, direct connection to          |

| 32 | DQMO              | O (OIIIA)   | LDQM and UDQM of SDRAM                                       |

|    | Note :PIN94/PIN99 | PIN100 ar   | e shared pins for E1 and optical interface, refer to section |

|    | 4.2.1.1           |             |                                                              |

|    |                   |             | When E1 is set as the WAN interface (WAN_MODI=01):           |

| 93 | E1PO              | O (6mA)     | HDB3 mode: HDB3+ output                                      |

|    |                   |             | NRZ mode: clock signal output                                |

|    |                   |             | When E1 is set as the WAN interface(WAN_MODI=01):            |

|    |                   |             | HDB3 mode: HDB3- output                                      |

| 94 | E1NO/OPT_DO       | O (6mA)     | NRZ mode: data signal output                                 |

|    |                   |             | When optical is set as the WAN                               |

|    |                   |             | interface(WAN_MODI=11): it outputs optical data.             |

| 95 | HVDD              | Power       | 3.3V                                                         |

| 96 | VSS               | Power       | Ground                                                       |

| 97 | LVDD              | Power       | 2.5V                                                         |

|    |                   |             | When optical is set as the WAN                               |

| 98 | 16K_DI            | I           | interface(WAN_MODI=11): it is data input of the 16Kbps       |

|    |                   |             | data channel. Refer to section 4.2.2.1 for more.             |

| 99  | E1PI/OPT_SDI | I      | When E1 is set as the WAN interface (WAN_MODI=01),<br>HDB3+ code is inputted(HDB3 mode) or NRZ clock<br>signal is inputted (NRZ mode);<br>When optical is set as the WAN<br>interface(WAN_MODI=11): optical LOS indication signal<br>input from external transceiver. Low level for LOS alarm. |  |  |

|-----|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 100 | E1NI/OPT_DI  | Ι      | When E1 is set as the WAN interface(WAN_MODI=01):,<br>HDB3- code is inputted(HDB3 mode) or NRZ data is<br>inputted (NRZ mode);<br>When optical is set as the WAN<br>interface(WAN_MODI=11): optical interface data is<br>inputted                                                              |  |  |

| 101 | HVDD         | Power  | 3.3V                                                                                                                                                                                                                                                                                           |  |  |

| 102 | WANLOOP_SELI | l (PD) | Local loop-back mode configuration for WAN:<br>1 = loop-back enable;<br>0 = loop-back disable<br>Refer to Fig.4-1-1 for the loop back point and section<br><b>4.2.4</b> for more.                                                                                                              |  |  |

| 103 | NC           | -      | Not used, connect low level or nothing                                                                                                                                                                                                                                                         |  |  |

| 104 | BUFFER_SELI  | l (PD) | Buffer size selection: (See section <b>4.7.2</b> for detailed description)<br>1 = large buffer mode;<br>0 = small buffer mode                                                                                                                                                                  |  |  |

|     |              |        | <u> </u>                                                                                                                                                                                                                                                                                       |  |  |

| InterfaceTiming source selection for WAN interface:1= local oscillator;0= tracing line timingWhen two devices are used to transmit Ethernet data,<br>one device can be set as local oscillator, the other<br>device can be set as either local oscillator or tracing line<br>timing; when two devices are used to transmit voice<br>service, one should be set as local oscillator and the<br>other must be set as inclaine timing. Refer to section<br><b>42.5</b> for more.107NC-108NAN_MODOI110NC-109CLK65II109CLK65II110VSSPower111TEST_SELI112SCAN_TESTI113TSTI114RESETII<br>(Schmit)115HVDDPower116VSSPowerGround117STBUS_DO118STBUS_DI119STBUS_DI110STBUS_DI111STBUS_DI112STBUS_DI113STBUS_DI114STBUS_DI115HVDD116STBUS_DI117STBUS_DI118STBUS_DI119STBUS_DI110STBUS_DI111STBUS_DI112STBUS_DI113STBUS_DI114STBUS_DI115HVDD116STBUS_DI117STBUS_DI118STBUS_DI119STBUS_DI110STBUS_DI111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | r            | 1         |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----------|--------------------------------------------------------------|

| 106       IIM_MODI       I       0 = tracing line timing<br>When two devices are used to transmit Ethernet data,<br>one device can be set as local oscillator, the other<br>device can be set as local oscillator or tracing line<br>timing; when two devices are used to transmit voice<br>service, one should be set as local oscillator and the<br>other must be set as tracing line timing. Refer to section<br><b>4.2.5</b> for more.         107       NC       -       Not used. Connect to ground or nothing         108       WAN_MODOI       I (PU)       WAN interface options selection, combined with the<br>signal WAN_MOD1I (PIN7).         108       WAN_MODOI       I (PU)       WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section <b>4.2.1.1</b> for details.         109       CLK65I       I       65.536MHz (± 50ppm) clock.         110       VSS       Power       Ground         111       TEST_SELI       I       Pins for chip test, must be grounded.         111       TSTI       I       Pins for chip test, must be grounded.         112       SCAN_TESTI       I       Reset signal for the chip:<br>0 = reset;<br>1 = work normally.         114       RESETI       I       Reset signal for the chip:<br>0 = reset;<br>1 = work normally.         115       HVDD       Power       3.3V         116       VSS       Power       Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |              |           | Timing source selection for WAN interface:                   |

| 106TIM_MODIIWhen two devices are used to transmit Ethernet data,<br>one device can be set as local oscillator, the other<br>device can be set as local oscillator or tracing line<br>timing; when two devices are used to transmit voice<br>service, one should be set as local oscillator and the<br>other must be set as tracing line timing. Refer to section<br><b>4.2.5</b> for more.107NC-Not used. Connect to ground or nothing108WAN_MODOII (PU)WAN interface options selection, combined with the<br>signal WAN_MOD1I (PIN7).108WAN_MODOII (PU)WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section <b>4.2.1.1</b> for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.114RESETII0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DLESEO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              |           | 1 = local oscillator;                                        |

| 106TIM_MODIIIone device can be set as local oscillator, the other<br>device can be set as either local oscillator or tracing line<br>timing; when two devices are used to transmit voice<br>service, one should be set as local oscillator and the<br>other must be set as tracing line timing. Refer to section<br><b>4.2.5</b> for more.107NC-Not used. Connect to ground or nothing108WAN_MODOII (PU)WAN interface options selection, combined with the<br>signal WAN_MOD11/PIN7).108WAN_MODOII (PU)WAN_MOD11/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD11/WAN_MOD0I=11, it is Optical interface;<br>Refer to section <b>4.2.1.1</b> for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTII0 = reset;<br>1 = work normally.113TSTIIest signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |              |           | 0 = tracing line timing                                      |

| 106TIM_MODIIIdevice can be set as either local oscillator or tracing line<br>timing; when two devices are used to transmit voice<br>service, one should be set as local oscillator and the<br>other must be set as tracing line timing. Refer to section<br><b>4.2.5</b> for more.107NC-Not used. Connect to ground or nothing108WAN_MODOII (PU)WAN_MOD11/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD11/WAN_MOD0I=01, it is Cptical interface;<br>WAN_MOD11/WAN_MOD0I=11, it is Optical interface;<br>Refer to section <b>4.2.1.1</b> for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELII9112SCAN_TESTII9113TSTIPins for chip test, must be grounded.114RESETII<br>(Schmitt)0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |              |           | When two devices are used to transmit Ethernet data,         |

| Image: Section of the section of th | 100 |              |           | one device can be set as local oscillator, the other         |

| Image: service in the service in the service in the service in the set as local oscillator and the other must be set as tracing line timing. Refer to section <b>4.2.5</b> for more.107NC-Not used. Connect to ground or nothing108WAN_MODOII (PU)WAN interface options selection, combined with the signal WAN_MOD1I (PIN7).108WAN_MODOII (PU)WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section <b>4.2.1.1</b> for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTIIPins for chip test, must be grounded.113TSTI0 = reset;<br>1 = work normally.114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106 |              | 1         | device can be set as either local oscillator or tracing line |

| Image: set in the |     |              |           | timing; when two devices are used to transmit voice          |

| Image: NCImage: Algorithm of the section           |     |              |           | service, one should be set as local oscillator and the       |

| 107NC-Not used. Connect to ground or nothing108NR-Not used. Connect to ground or nothing108WAN_MODOII (PU)WAN interface options selection, combined with the<br>signal WAN_MOD1I (PIN7).<br>WAN_MODD1=01, it is E1 interface;<br>WAN_MODD1/WAN_MODOI=11, it is Optical interface;<br>Refer to section 4.2.1.1 for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELII65.536MHz (± 50ppm) clock.112SCAN_TESTIIPins for chip test, must be grounded.113TSTIIPins for chip test, must be grounded.114RESETIISeset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |              |           | other must be set as tracing line timing. Refer to section   |

| 108WAN_MODOII (PU)WAN interface options selection, combined with the<br>signal WAN_MOD1I (PIN7).108WAN_MODOII (PU)WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section 4.2.1.1 for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.111TSTIIPins for chip test, must be grounded.113TSTII0 = reset;<br>1 = work normally.114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |              |           | <b>4.2.5</b> for more.                                       |

| 108WAN_MODOII (PU)signal WAN_MOD11 (PIN7).<br>WAN_MOD11/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD11/WAN_MOD0I=11, it is Optical interface;<br>Refer to section 4.2.1.1 for details.109CLK651I65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.111TSTIIPins for chip test, must be grounded.113TSTIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.114HVDDPower3.3V115HVDDPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 107 | NC           | -         | Not used. Connect to ground or nothing                       |

| 108WAN_MODOII (PU)WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;<br>WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section 4.2.1.1 for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.111TSTIIPins for chip test, must be grounded.113TSTIIPins for chip test, must be grounded.114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |              |           | WAN interface options selection, combined with the           |

| WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;<br>Refer to section 4.2.1.1 for details.109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTIIPins for chip test, must be grounded.113TSTIIPower114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |              |           | signal WAN_MOD1I (PIN7).                                     |

| Image: Note of the state of  | 108 | WAN_MOD0I    | I (PU)    | WAN_MOD1I/WAN_MOD0I=01, it is E1 interface;                  |

| 109CLK65II65.536MHz (± 50ppm) clock.110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTIIPins for chip test, must be grounded.113TSTIIPins for chip test, must be grounded.114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |              |           | WAN_MOD1I/WAN_MOD0I=11, it is Optical interface;             |

| 110VSSPowerGround111TEST_SELIIPins for chip test, must be grounded.112SCAN_TESTIIPins for chip test, must be grounded.113TSTIIPins for chip test, must be grounded.114RESETIIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |              |           | Refer to section 4.2.1.1 for details.                        |

| 111TEST_SELI112SCAN_TESTII113TSTIPins for chip test, must be grounded.113TSTIPins for chip test, must be grounded.114RESETII115HVDDPower116VSSPower117STBUS_DOO (6mA)118STBUS_DII119STBUS_PULSEOO (6mA)STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109 | CLK65I       | I         | 65.536MHz (± 50ppm) clock.                                   |

| Indext relationIPins for chip test, must be grounded.112SCAN_TESTIIPins for chip test, must be grounded.113TSTIReset signal for the chip:<br>0 = reset;<br>1 = work normally.114RESETII<br>(Schmitti)0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110 | VSS          | Power     | Ground                                                       |

| 113TSTI113TSTI114RESETII<br>(Schmitt)114RESETIReset signal for the chip:<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIISTBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 | TEST_SELI    |           |                                                              |

| Indext NetworkIndext NetworkReset signal for the chip:<br>0 = reset;<br>1 = work normally.114RESETIIndext Network0 = reset;<br>0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 112 | SCAN_TESTI   | I         | Pins for chip test, must be grounded.                        |

| 114RESETII<br>(Schmitt)0 = reset;<br>1 = work normally.115HVDDPower3.3V116VSSPowerGround117STBUS_DOO (6mA)ST_BUS data output118STBUS_DIIST_BUS data input119STBUS_PULSEOO (6mA)ST_BUS multi-frame alignment pulse (500Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113 | TSTI         |           |                                                              |