### Datasheet

### **Standard Products RDC5028C 16-Bit Monolithic Tracking Rad Tolerant Resolver-To-Digital Converter** www.aeroflex.com/RDC

### May 7, 2014

### **FEATURES**

- □ Enhanced version of the ACT5028B

- Radiation performance

- Total dose: 1 Mrad(Si), Dose rate = 50 300 rads(Si)/s

- SEL:Immune up to 100 MeV-cm<sup>2</sup>/mg

- $\Box$  +5VDC power only

- □ Programmable: By using a few non critical external resistors and capacitors

- Resolution: 10, 12, 14 or 16 bit resolution

- Bandwidth

- Tracking rate

- $\Box$  Low power: +5V (a) 20 mA typ

- □ 45 to 30,000 Hz carrier frequency range

- □ Accuracy:

- 10.0 Arc Minutes if not compensated by INL correction factors.

- 5.3 Arc Minutes using INL correction factors.

- Differential instrument amplifiers resolver input

- $\Box$  -55° to +125°C operating temperature

- □ Digital interface logic voltage of 3.3V to 5V

- Designed for aerospace and high reliability space applications

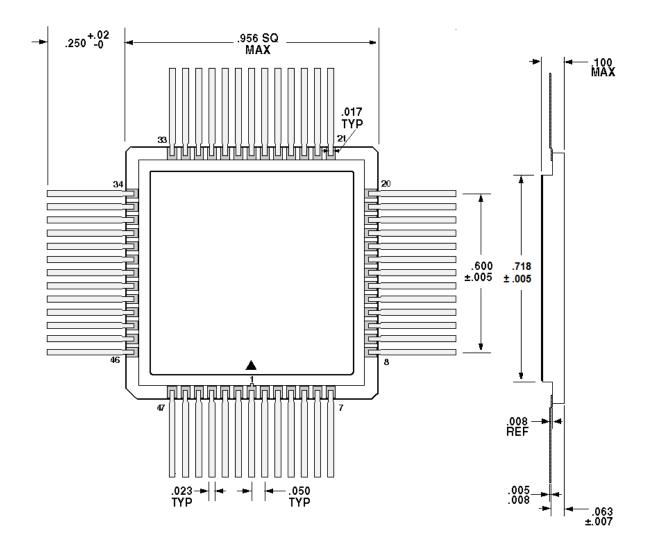

- □ Packaging Hermetic

- 52 Pin Ceramic QUAD flat package (CQFP), .956" SQ x .100" Ht

- Weight: 5.0g max

- □ Evaluation board available for test and evaluation. See Aeroflex Application note AN5028-1

### □ Aeroflex Plainview's Radiation Hardness Assurance Plan is DLA Certified to MIL-PRF-38534, Appendix G.

### APPLICATIONS

This single chip Resolver-to-Digital Converter (RDC) is used in shaft angle control systems, and is suitable for space or other radiation environments that require > 1 Mrad(Si) total dose tolerance. The part is latchup free in heavy ion environments (e.g., geosynchronous orbits) and is estimated to experience SEU induced errors of less than 15 minutes of arc at a rate of 1 per device per 2 years when operating dynamically.

### THEORY OF OPERATION

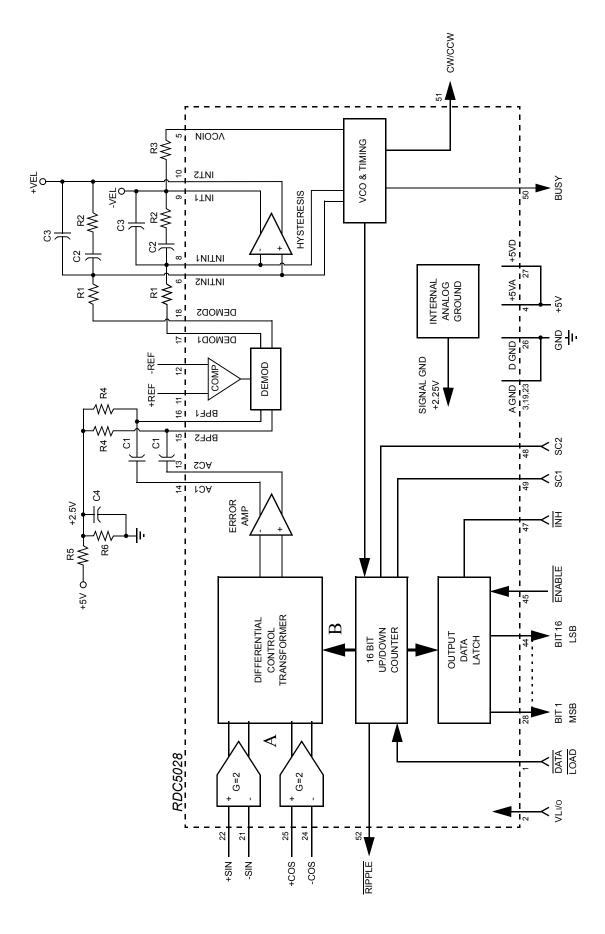

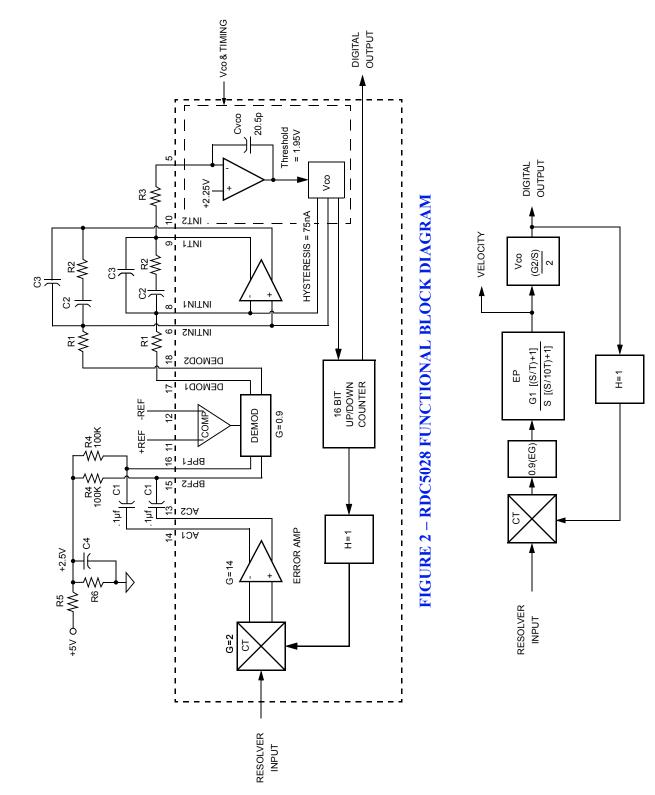

The RDC5028 converter is a single CMOS Type II tracking resolver to digital converter monolithic chip. It is implemented using precision analog circuitry and digital logic. For flexibility, the converter bandwidth, dynamics and velocity scaling are externally set with passive components. Refer to Figure 1, RDC5028 Block Diagram.

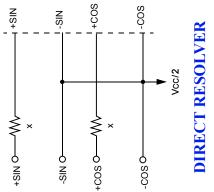

The converter is powered from +5VDC. Analog signals are referenced to signal ground, which is nominally VCC/2. The converter consists of three main sections; the Analog Control Transformer (CT), the Analog Error Processor (EP) and the Digital Logic Interface.

The CT has two analog resolver inputs (Sin and Cos) that are buffered by high impedance input instrumentation type amplifiers and the 16 bit digital word which represents the output digital angle. The CT performs the ratiometric trigonometric computation of:

SIN(A) sin(wt) COS(B) - COS(A) sin(wt) SIN(B) = SIN(A-B) sin(wt)

Utilizing amplifiers, switches, logic and resistors in precision ratios. "A" represents the resolver angle, "B" represents the digital angle and sin(wt) represents the resolver reference carrier frequency.

The Error Processor is configured as a critically damped Type II loop. The AC error, SIN (A-B) sin (wt) is full wave demodulated using the reference squared off as its drive. This DC error is integrated in an analog integrator yielding a velocity voltage which in turn drives a Voltage Controlled Oscillator (VCO). Note in the block diagram, hysterisis is added to prevent dithering and disables counting when the error is less than 1 LSB. This VCO is an incremental integrator (constant voltage input to position rate output) which, together with the velocity integrator, forms a Type II loop. A lead is inserted to stabilize the loop and a lag is inserted at a higher frequency to attenuate the carrier frequency ripple. The error processor drives the 16 bit digital output until it nulls out. Then angle "A" = "B". The digital output equals angle input to the accuracy of the precision control transformer. The various error processor settings are done with external resistors and capacitors so that the converter loop dynamics can be easily controlled by the user. The digital logic interface has a separate power line, VLI/O that sets the interface logic 1 level. It can be set anywhere from +3V to the +5V power supply.

# FIGURE 1 – RDC5028 BLOCK DIAGRAM

### **PIN DESCRIPTIONS**

| SIGNAL                                                                                                                                                          | DIRECTION | PIN                                                                                          | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +SIN<br>-SIN                                                                                                                                                    | INPUT     | 22<br>21                                                                                     | Analog Sine input from Synchro or Resolver. 1.3Vrms nominal                                                                                                                                                                                                                                                                                                                     |

| +COS<br>-COS                                                                                                                                                    | INPUT     | 25<br>24                                                                                     | Analog Cosine input from Synchro or Resolver. 1.3Vrms nominal                                                                                                                                                                                                                                                                                                                   |

| +REF<br>-REF                                                                                                                                                    | INPUT     | 11<br>12                                                                                     | Analog Reference input is typically a sine wave @ 1.3Vrms                                                                                                                                                                                                                                                                                                                       |

| BIT 1 (MSB)<br>BIT 2<br>BIT 3<br>BIT 4<br>BIT 5<br>BIT 6<br>BIT 7<br>BIT 8<br>BIT 9<br>BIT 10<br>BIT 11<br>BIT 12<br>BIT 13<br>BIT 14<br>BIT 15<br>BIT 16 (LSB) | BIDIR     | 28<br>29<br>30<br>31<br>32<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44 | Digital angle data. Parallel format. Natural binary positive logic.<br>Bit 1, most significant bit = 180°, Bit 2 = 90°, Bit 3 = 45° and so on.<br>In the 10 bit mode, Bit 10 is the LSB. Bits 11-16 are 0s.<br>In the 12 bit mode, Bit 12 is the LSB. Bits 13-16 are 0s.<br>In the 14 bit mode, Bit 14 is the LSB. Bits 15-16 are 0s.<br>In the 16 bit mode, Bit 16 is the LSB. |

| SC1<br>SC2                                                                                                                                                      | INPUT     | 49<br>48                                                                                     | $\begin{array}{c c} \text{Digital input. Sets the resolution.} \\ \underline{SC1} & \underline{SC2} & \underline{\text{Resolution}} \\ \hline 0 & 0 & 10 \text{ bit} \\ 0 & 1 & 12 \text{ bit} \\ 1 & 0 & 14 \text{ bit} \\ 1 & 1 & 16 \text{ bit} \end{array}$                                                                                                                 |

| ENABLE*                                                                                                                                                         | INPUT     | 45                                                                                           | Logic 0 enables digital angle output. Otherwise it is high impedance.                                                                                                                                                                                                                                                                                                           |

| ĪNH*                                                                                                                                                            | INPUT     | 47                                                                                           | Logic 0 freezes the digital angle output so that it can be safely read.                                                                                                                                                                                                                                                                                                         |

| DATALOAD*                                                                                                                                                       | INPUT     | 1                                                                                            | Logic 0 enables the digital angle lines to be inputs to preset the angle.<br>Logic 1 is for normal digital angle output.                                                                                                                                                                                                                                                        |

| BUSY                                                                                                                                                            | OUTPUT    | 50                                                                                           | A logic 1 pulse when the digital angle changes by 1 LSB.                                                                                                                                                                                                                                                                                                                        |

| CW/CCW                                                                                                                                                          | OUTPUT    | 51                                                                                           | For turns counting. Logic 1 = counting up (CW), logic 0 = counting down (CCW).                                                                                                                                                                                                                                                                                                  |

| RIPPLE*                                                                                                                                                         | OUTPUT    | 52                                                                                           | Ripple clock for turns counting. A logic 0 pulse = a $0^{\circ}$ transition in either direction.                                                                                                                                                                                                                                                                                |

| AC1<br>AC2                                                                                                                                                      | OUTPUT    | 14<br>13                                                                                     | Differential AC error output                                                                                                                                                                                                                                                                                                                                                    |

| BPF1<br>BPF2                                                                                                                                                    | INPUT     | 16<br>15                                                                                     | Differential AC error input to demodulator                                                                                                                                                                                                                                                                                                                                      |

| DEMOD1<br>DEMOD2                                                                                                                                                | OUTPUT    | 17<br>18                                                                                     | Differential DC error output                                                                                                                                                                                                                                                                                                                                                    |

| INTIN1<br>INTIN2                                                                                                                                                | INPUT     | 8<br>6                                                                                       | Differential DC input to differential velocity integrator                                                                                                                                                                                                                                                                                                                       |

| INT1<br>INT 2                                                                                                                                                   | OUTPUT    | 9<br>10                                                                                      | Differential velocity output                                                                                                                                                                                                                                                                                                                                                    |

| VCOIN                                                                                                                                                           | INPUT     | 5                                                                                            | Input to Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                          |

| Vcc<br>Vdd                                                                                                                                                      | POWER     | 4<br>27                                                                                      | Analog Power In<br>Digital Power In                                                                                                                                                                                                                                                                                                                                             |

| A GND<br>D GND                                                                                                                                                  | POWER     | 3, 19, 23<br>26                                                                              | Analog Power ground<br>Digital Power ground                                                                                                                                                                                                                                                                                                                                     |

| VLI/O                                                                                                                                                           | POWER     | 2                                                                                            | Digital input/output DC power supply. Sets logic 1 level. +3V to +5V                                                                                                                                                                                                                                                                                                            |

\* Indicates Active Low Signal

### **ABSOLUTE MAXIMUM RATINGS\***

| PARAMETER                                           | VALUE                     |

|-----------------------------------------------------|---------------------------|

| Operating Temperature                               | -55°C to +125°C           |

| Storage Temperature                                 | -65°C to +150°C           |

| Positive Power Supply Voltage (VCC = VDD)           | -0.5 V to +7.0 V          |

| Analog Output Current (Output Shorted to GND)       | 32 mA Max                 |

| Digital Output Current (Output Shorted to GND)      | 18.6 mA Max               |

| Analog Input Voltage Range                          | -0.5 V to + (VCC + 0.5 V) |

| Digital Input Voltage Range                         | -0.5 V to + (VDD + 0.5 V) |

| Thermal Resistance $\mathcal{O}_{JC}$ Specification | 1.25°C/W                  |

| Maximum Junction Temperature                        | 135°C                     |

| Lead Temperature (soldering, 10 seconds)            | 300°C                     |

| ESD Class 2 MIL-STD-883 Method 3015, 8              | 2000 V to 3999 V          |

\* Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. These are stress ratings only; functional operation beyond these operating conditions is not recommended and extended exposure beyond these operating conditions may effect device reliability.

### OPERATING CONDITIONS (TA = -55°C to +125°C)

| POWER SUPPLY         | PARAMETER         | MIN | ТҮР    | MAX | UNIT |

|----------------------|-------------------|-----|--------|-----|------|

| $V_{DD} = V_{CC}$    | Operating Voltage | 4.5 | 5      | 5.5 | VDC  |

| IDD + ICC <u>9</u> / | Operating Current | -   | 20     | 35  | mA   |

| VLI/O                | Interface Voltage | 3   | 3.3, 5 | 5.5 | VDC  |

### ELECTRICAL CHARACTERISTICS 2/, 5/, 6/(TA = -55°C to +125°C)

| PARAMETER                                 | CONDITIONS                                                              | MIN    | ТҮР  | MAX     | UNITS   |

|-------------------------------------------|-------------------------------------------------------------------------|--------|------|---------|---------|

| Accuracy <u>4</u> / <u>8</u> / <u>9</u> / | Add 1 LSB for total Error,<br>Using INL correction factors.             | -      | +/-2 | +/-5.0  | Minutes |

|                                           | Add 1 LSB for total Error,<br>Not compensated by INL correction factors | -      | +/-4 | +/-10.0 | Minutes |

| Repeatability                             |                                                                         | -      | -    | 1       | LSB     |

| Resolution per LSB                        | 10 Bit Mode                                                             | 0.35   | -    | -       | Degrees |

|                                           |                                                                         | 21.1   | -    | -       | Minutes |

|                                           | 12 Bit Mode                                                             | 0.09   | -    | -       | Degrees |

|                                           |                                                                         | 5.27   | -    | -       | Minutes |

|                                           | 14 Bit Mode                                                             | 0.022  | -    | -       | Degrees |

|                                           |                                                                         | 1.32   | -    | -       | Minutes |

|                                           | 16 Bit Mode                                                             | 0.0055 | -    | -       | Degrees |

|                                           |                                                                         | 0.33   | -    | -       | Minutes |

| Max Tracking Rate                         | SC1 SC2 Bits Used                                                       |        |      |         |         |

| 10 Bit Mode <u>3</u> /                    | 0 0 B1 - B10                                                            | 1024   | -    | -       | RPS     |

| 12 Bit Mode <u>3</u> /                    | 0 1 B1 - B12                                                            | 256    | -    | -       | RPS     |

| 14 Bit Mode <u>3</u> /                    | 1 0 B1 - B14                                                            | 64     | -    | -       | RPS     |

### ELECTRICAL CHARACTERISTICS 2/, 5/, 6/ (TA = -55°C to +125°C)

| PARAMETER                | CONDITIONS   | MIN  | ТҮР | MAX | UNITS |

|--------------------------|--------------|------|-----|-----|-------|

| 16 Bit Mode <u>3</u> /   | 1 1 B1 - B16 | 16   | -   | -   | RPS   |

| VCO Frequency <u>3</u> / |              | 1.05 | -   | -   | MHz   |

### ELECTRICAL SPECIFICATIONS 2/, 5/, 6/(TA = -55°C to +125°C)

| ANALOG SIGNAL INPUTS                                   | SYM                    | PARAMETER                                                | MIN          | ТҮР   | MAX   | UNITS |

|--------------------------------------------------------|------------------------|----------------------------------------------------------|--------------|-------|-------|-------|

| SIN, COS, REF, VCOIN,<br>INTIN1, INTIN2,<br>BPF1, BPF2 | VSIN,<br>VCOS,<br>VREF | Voltage measurement made between $\pm$ inputs <u>9</u> / | 1.0          | 1.3   | 1.5   | VRMS  |

|                                                        | Fref                   | Frequency <u>1</u> /                                     | 45           | -     | 30K   | Hz    |

|                                                        |                        | DC Resistance $3/$                                       | 2.5          | -     | -     | MΩ    |

|                                                        |                        | Capacitance <u>3</u> /                                   | -            | 5     | 15    | pF    |

|                                                        |                        | DC Bias on -Sin, -Cos <u>3</u> /                         | -            | Vcc/2 | -     | VDC   |

|                                                        |                        | Bias Current <u>3</u> /                                  |              |       |       |       |

|                                                        |                        | +25°C                                                    | -100         | -     | +100  | nA    |

|                                                        |                        | +125°C                                                   | -1000        | -     | +1000 | nA    |

| DIGITAL INPUTS                                         |                        |                                                          |              |       |       |       |

| ENABLE, DATALOAD                                       | VIL                    | Logic Low                                                | -            | -     | 0.8   | VDC   |

| $\frac{SC2}{INH}$ , SC1, $\frac{3}{2}$                 | VIH                    | Logic High                                               | 2            | -     | -     | VDC   |

|                                                        | Iin                    | Leakage Current                                          |              |       |       |       |

|                                                        |                        | +25°C                                                    | -200         | -     | +200  | nA    |

|                                                        |                        | +125°C                                                   | -2000        | -     | +2000 | nA    |

|                                                        |                        | DC Resistance                                            | 2.5          | -     | -     | MΩ    |

|                                                        |                        | Capacitance                                              | -            | 5     | 15    | pF    |

| DIGITAL OUTPUTS                                        |                        |                                                          |              |       |       |       |

| BUSY, RIPPLE                                           | VOL                    | Logic Low @ 1.6mA                                        | -            | -     | 0.3   | VDC   |

| CW/CCW <u>3</u> /                                      | Voh                    | Logic High @ -1.6mA                                      | VL I/O - 0.8 | -     | -     | VDC   |

| DIGITAL I/O                                            |                        |                                                          |              |       |       |       |

| B1 - B16 <u>7/ 3/</u>                                  | VIL                    | Logic Low                                                | -            | -     | 0.8   | VDC   |

|                                                        | VIH                    | Logic High                                               | 2            | -     | -     | VDC   |

|                                                        | VOL                    | Logic Low @ 1.6mA                                        | -            | -     | 0.3   | VDC   |

|                                                        | Voh                    | Logic High @ -1.6mA                                      | VLI/O - 0.8  | -     | -     | VDC   |

|                                                        | IIN                    | Leakage Current                                          |              |       |       |       |

|                                                        |                        | +25°C                                                    | -200         | -     | +200  | nA    |

|                                                        |                        | +125°C                                                   | -2000        | -     | +2000 | nA    |

|                                                        | Iz                     | High-Z Leakage Current                                   |              |       |       |       |

|                                                        |                        | +25°C                                                    | -200         | -     | +200  | nA    |

|                                                        |                        | +125°C                                                   | -2000        | -     | +2000 | nA    |

### TIMING SPECIFICATIONS <u>6</u>/

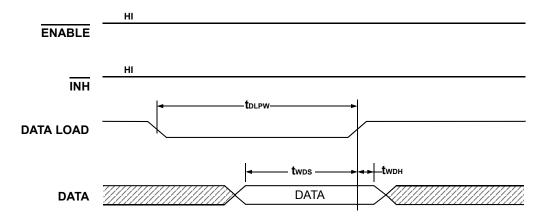

| DIGITAL OUTPUT                                  | SYM          | COMMENTS                           | MIN     | TYP <u>2</u> / | MAX | UNITS |

|-------------------------------------------------|--------------|------------------------------------|---------|----------------|-----|-------|

| Busy                                            | tlh          | Rise Time                          | -       | 20             | 85  | ns    |

|                                                 | tHL          | Fall Time                          | -       | 20             | 85  | ns    |

| CW/CCW, Ripple, B1- B16                         | tlh          | Rise Time                          | -       | 45             | 120 | ns    |

|                                                 | tHL          | Fall Time                          | -       | 45             | 100 | ns    |

| Busy Pulse Width                                | <b>t</b> BPW |                                    | 300     | 400            | 600 | ns    |

| Busy to Data Stable <u>3</u> /                  | tBDS         | Enable = Low                       | -       | -              | 350 | ns    |

| Ripple Pulse Width                              | <b>t</b> rpw |                                    | 140     | 200            | 300 | ns    |

| Busy to Ripple <u>3</u> /                       | tbr          |                                    | -       | 100            | 150 | ns    |

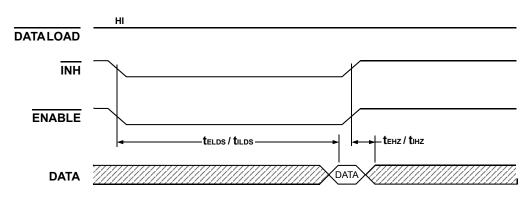

| <b>READ DATA</b> <u>3</u> / (Enable & INH would | l normall    | y be tied together, Data Load =    | Logic H | i)             |     |       |

| Enable Low to Data Stable                       | telds        |                                    | -       | -              | 70  | ns    |

| Enable High to Data Hi-Z                        | tenz         |                                    | -       | -              | 70  | ns    |

| INH Low to Data Stable                          | tilds        |                                    | -       | -              | 400 | ns    |

| INH High to Data Change                         | tihz         |                                    | -       | -              | 150 | ns    |

| WRITING DATA <u>3</u> / (Enable & INH =         | = Logic H    | li)                                | -       |                |     |       |

| Data Load Pulse Width                           | tdlpw        | Transparent Trailing Edge<br>Latch | 200     | -              | -   | ns    |

| Data Setup to Data Load                         | twds         |                                    | 60      | -              | -   | ns    |

| Data Hold                                       | twdh         |                                    | 10      | -              | -   | ns    |

Notes

1/@ 10 Bits, FREF > 4 x BWCL

a 12 Bits, FREF > 8 x BWCL

(a) 14 Bits, FREF > 12 x BWCL

(a) 16 Bits, FREF > 16 x BWCL

2/ All typical values are measured at +25°C.

$\underline{3}$  / Characteristics are guaranteed by design, not production tested.

4/ Accuracy applies over the full operating Power Supply voltage range, Full operating Temperature range, Reference Frequency range, 10% Signal Amplitude variation and 10% Reference Harmonic distortion.

5/ For ESD protection the RDC5028 features limiting resistors in series with diodes. Proper ESD precautions are strongly recommended to avoid functional damage or performance degradation.

6/ All testing at nominal voltage.

7/ All unused inputs shall be tied to Ground. Bit 1 is always the MSB.

8/ See Application Note 1, page 16 and Table II, page 19 "Using INL Error Correction Factors to Improve Accuracy"

9/ Specification de-rated to reflect Total Dose Rate (1019 condition A) to 1 Mrad(Si) @ 25°C.

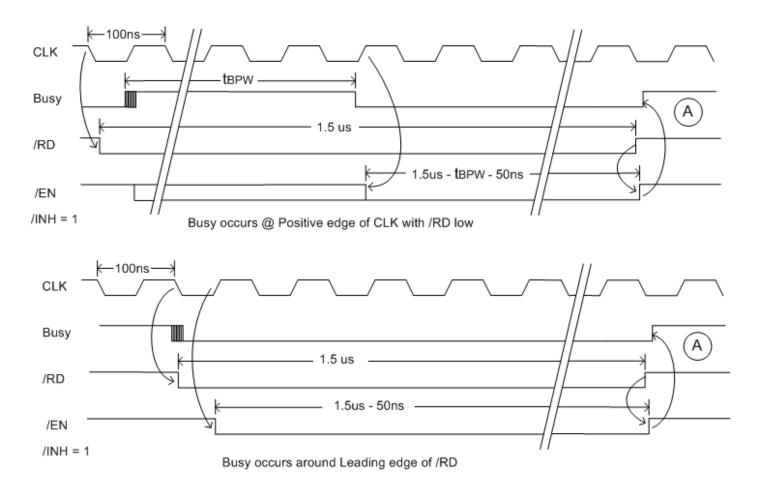

### **READ CYCLE**

### WRITE CYCLE

### FIGURE 2 - RDC5028 TIMING DIAGRAMS

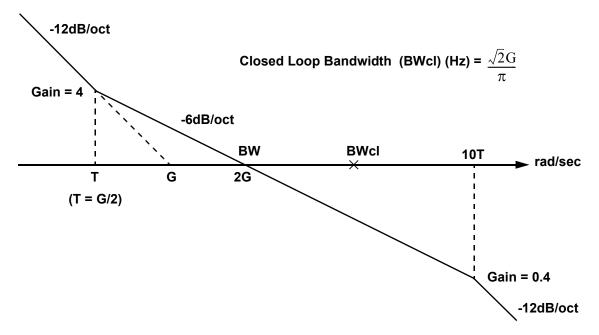

FIGURE 4 – RDC5028 OPEN LOOP BODE PLOT

### **TRANSFER FUNCTION AND BODE PLOT**

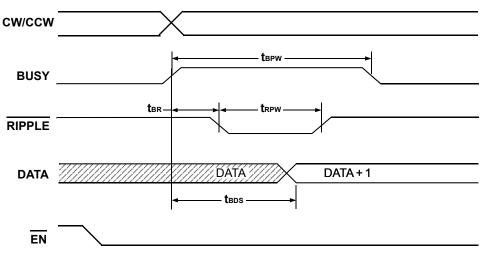

The dynamic performance of the converter can be determined from its Functional Block Diagram, Transfer Function Diagram and Bode plots, as shown in Figures 2, 3 and 4.

### **PROCEDURE FOR SELECTING RDC BANDWIDTH COMPONENTS \***

Input: Carrier Frequency (Fc) in Hz [47 to 30,000 Hz] Input: Nominal Resolver Input Level in Vrms [1Vrms min. to 1.5Vrms max.] Input: Resolution in bits; 10, 12, 14 or 16 bits Input: Closed Loop Bandwidth (BWcl) in Hz [10 bit; BWcl = Fc/4 max.] [12 bit; BWcl = Fc/8 max.] [14 bit; BWcl = Fc/12 max.]

Input: Maximum Tracking Rate in RPS (RPS = rotations per second) [16 bit; 16 RPS max.] [14 bit, 64 RPS max.] [12 bit; 256 RPS max.] [10 bit, 1024 RPS max.]

[16 bit: BWcl = Fc/16 max.]

Input: Hysteresis in LSBs. Recommended is 1 LSB for 16 & 14 bits and 0.7 LSBs for 12 & 10 bits.

EG = Nominal Resolver Input Level.0027[16 bit] orEG = Nominal Resolver Input Level.011[14 bit] orEG = Nominal Resolver Input Level.043[12 bit] orEG = Nominal Resolver Input Level.17[10 bit]G = 2.22 • BWcl $G^2 = EG • 0.45 • G1 • G2$

SCD5028-2 Rev G 5/7/2014

### **PROCEDURE FOR SELECTING RDC BANDWIDTH COMPONENTS \* (Cont)**

Hysteresis recommended values HYS = 0.7 [10 & 12 bit] or HYS = 1 [14 & 16 bit] or  $R1_{(ohms)} = 6 \cdot 10^6 \cdot EG \cdot HYS$ G2 = Maximum Tracking Rate •  $2^{15}$ [16 bit] or G2 = Maximum Tracking Rate •  $2^{13}$ [14 bit] or G2 = Maximum Tracking Rate •  $2^{11}$ [12 bit] or G2 = Maximum Tracking Rate •  $2^9$ [10 bit]  $R3_{(ohms)} = (25 \cdot 10^9)/G2$  $G1 = G^2 / (EG \bullet .45 \bullet G2)$  $C2_{(farads)} = 1/(G1 \bullet R1)$  $C3_{(farads)} = C2/10$  $R2_{(ohms)} = 2/(G \bullet C2)$

\* Software Program SW5028-2 available at Aeroflex WEB site.

### **RDC5028 EXAMPLE CALCULATIONS**

Carrier Frequency = 800 Hz Nominal Resolver Input Level = 1.3Vrms Resolution = 14 bits Closed Loop Bandwidth (BWcl) = 20 Hz Maximum Tracking Rate in RPS = 1 Hysteresis = 1 LSB EG = Nominal Resolver Input Level • .011 [14 bit] = 1.3 • .011 = .014 G = 2.22 • BWcl = 2.22 • 20 = 44.4 HYS = 1 [14 bit]  $R1_{(ohms)} = 6 \cdot 10^{6} \cdot EG \cdot HYS = 6 \cdot 10^{6} \cdot .014 \cdot 1 = 84K$ . Use closest standard resistor = 84.5K 1% G2 = Maximum Tracking Rate •  $2^{13}$  = 8192 [ $2^{13}$  for 14 bits]  $R3_{(ohms)} = (25 \cdot 10^9)/G2 = (25 \cdot 10^9)/8192 = 3,050K$ . Use closest standard resistor = 3.01M 1% or 3M 5%  $G^2 = EG \bullet 0.45 \bullet G1 \bullet G2$  $\begin{array}{l} G1 = G^2 / (EG \bullet .45 \bullet G2) = 44.4^2 / (.014 \bullet .45 \bullet 8192) = 38.2 \\ C2_{(farads)} = 1 / (G1 \bullet R1) = 1 / (38.2 \bullet 84.5 \text{K}) = .31 \mu \text{F}. \text{ Use closest standard capacitor} = .33 \mu \text{F} \ 10\% \end{array}$  $C3 = C2/10_{(farads)} = C2/10 = .33\mu/10 = .033\mu F$  $R2_{(ohms)} = 2/(G \cdot C2) = 2/(44.4 \cdot .33\mu) = 136.5K$ . Use closest standard resistor = 137K 1%

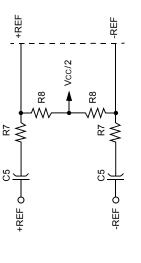

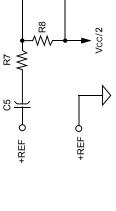

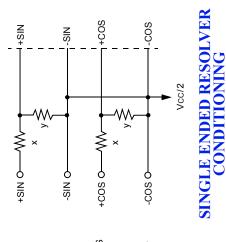

### SIGNAL AND REFERENCE INPUT CONDITIONING

Inputs to the converter should be 1.3 Vrms nominal, resolver format referenced to Vcc/2 nominal Figure 5 shows various input configurations.

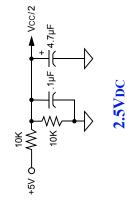

### **REFERENCE CONDITIONING**

Most resolvers have a LEADING input to output phase shift. A simple C-R leading phase shift network (Figure 5 – Reference Conditioning) from the resolver reference to the RDC's reference input will provide the compensating phase shift required to bring the signals in phase. If the resolver has a LAGGING input to output phase shift an R-C lagging phase shift network (low pass network) would be required.

Note the C-R phase lead circuit on the input to the Demodulator (BPF1 and BPF2) in Figure 1 should be considered when calculating the total system phase compensation.

The formula for calculating the phase shift network is as follows:

Phase angle = ArcTan

$$\frac{1}{6.28 \text{ x} (\text{R7 + R8}) \text{ x C}}$$

F<sub>RFF</sub>

Select a convenient capacitor value and perform the following calculation to determine the proper resistor value.

$$R = \frac{1}{(Tan (Phase Angle)) \times F_{REF} \times 6.28 \times C}$$

### **POWER UP INITIALIZATION**

The RDC5028 RDC converter can provide incorrect data output if a unit step of 180° (starting at any angle) is introduced to the Sin / Cos input.

This is difficult to reproduce since a Resolver will never provide a unit step function to the RDC chip.

The only time this would be a concern is during power up, if the Resolver is set to 180°. The RDC will initialize its internal counter to 0000h which simulates the unit step function mentioned above. In practice this error condition during power up is difficult to produce because of the dynamics associated with all the variables when power is first applied.

If the system designer does nothing to accommodate this potential problem the system could see an error at power on, however, this error will be self corrected once the Resolver begins to rotate. If the Resolver does not rotate, the error can be corrected by writing to the RDC5028 any angle except 180°.

### **VELOCITY CONTROL**

The RDC5028 RDC exhibits nonlinearity below 4 degrees/sec due to an anti-dither circuit that was added to reduce the effects of any noise condition that may exist. This result can be seen in the least significant bit or on the velocity output pins 9 & 10 on this device.

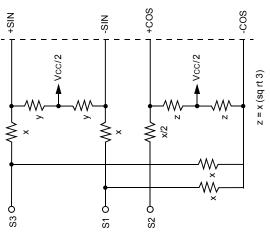

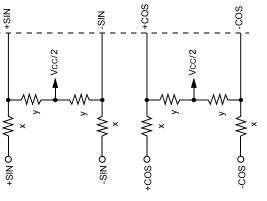

# DIFFERENTIAL REFERENCE CONDITIONING (FLOATING REFERENCE)

### SINGLE ENDED REFERENCE CONDITIONING

-REF

+REF

## DIFFERENTIAL RESOLVER CONDITIONING

### **READING THE ACT 5028B**

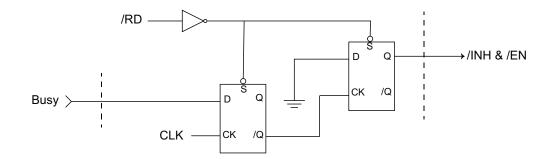

The Busy signal is asynchronous to the Read signal created by the interface circuit that reads it. Because of the asynchronous nature of the system (inherent with other Resolver to Digital Converters) the designer must be careful when reading the digital interface.

The implementation of reading the RDC is accomplished in one of two ways, using a CPU/MPU or using an FPGA. The best method for reading the counter may also depend on the rep rate of the counter clock that can vary from 0 to  $1\mu$ S.

The Busy pulse is instrumental in reading stable data from the RDC5028. The Busy pulse will be present for the following two situations:

- 1) When ever data is incremented or decremented in the RDC counter.

- 2) Directly after the trailing positive going edge of /INH (see A within example 5 timing diagram).

Based on 1 above there are many methods that can be implemented to synchronize the reading of data from the RDC5028, below are a few examples:

- Example 1: If the only time a read will occur is after the RDC has stopped (0 rps) there will be no Busy signal to contend with.

- Example 2: Knowing the Busy rep rate an Interrupt to a CPU or Logic can be developed from the Busy pulse for the system to Read the RDC chip as long as the read is guaranteed to occur prior to the next Busy pulse.

- Example 3: As long as the resolver is rotating the Busy Pulse can be used to indicate stable data to be sampled on leading or trailing edge.

- Example 4: Ignore Busy and perform two reads back to back and compare, if they are equal you have good data. The designer should be aware of the rep rate of Busy which is equal to the clock rate of the counter. In most cases the angular velocity is < 3 rps in which case with a 16 bit counter rep rate would be (1 / 2<sup>16</sup> \* 3) 5µS. In this situation the reads would like to be within 5µs of each other and the LSB would be ignored. Although this method would be easier to implement with a CPU it could also be done in an FPGA.

- Example 5: The circuit below ignores the Busy signal but insures sampling of stable data. The clock should be a least 10MHz, the /RD pulse should be a minimum of 1.2µs (to insure minimum /INH pulse width of 400ns), the sampling of data should be taken on the rising edge of the signal /RD. The /RD signal is synced up with the CLK such that the sampling on the D latch occurs on the opposite edge of the /RD transition.

### FIGURE 6 – CIRCUIT TIMING WAVEFORMS

| PIN # | FUNCTION  | PIN # | FUNCTION    | PIN # | FUNCTION     |

|-------|-----------|-------|-------------|-------|--------------|

| 1     | DATA LOAD | 19    | A GND       | 37    | BIT 9        |

| 2     | VL I/O    | 20    | N/C         | 38    | BIT 10       |

| 3     | A GND     | 21    | -SIN        | 39    | BIT 11       |

| 4     | A+5V      | 22    | +SIN        | 40    | BIT 12       |

| 5     | VCOIN     | 23    | A GND       | 41    | BIT 13       |

| 6     | INTIN2    | 24    | -COS        | 42    | BIT 14       |

| 7     | N/C       | 25    | +COS        | 43    | BIT 15       |

| 8     | INTIN1    | 26    | D GND       | 44    | BIT 16 (LSB) |

| 9     | INT1      | 27    | D+5V        | 45    | ENABLE       |

| 10    | INT2      | 28    | BIT 1 (MSB) | 46    | N/C          |

| 11    | +REF      | 29    | BIT 2       | 47    | INH          |

| 12    | -REF      | 30    | BIT 3       | 48    | SC2          |

| 13    | AC2       | 31    | BIT 4       | 49    | SC1          |

| 14    | AC1       | 32    | BIT 5       | 50    | BUSY         |

| 15    | BPF2      | 33    | N/C         | 51    | CW/CCW       |

| 16    | BPF1      | 34    | BIT 6       | 52    | RIPPLE       |

| 17    | DEMOD1    | 35    | BIT 7       |       |              |

| 18    | DEMOD2    | 36    | BIT 8       |       |              |

### TABLE I – RDC5028 PIN OUT DESCRIPTIONS (CQFP PACKAGE)

### FIGURE 7 – 52 PIN CERAMIC QUAD FLAT PACKAGE (CQFP) OUTLINE

### **APPLICATION NOTE 1**

### **USING INL ERROR CORRECTION FACTORS TO IMPROVE ACCURACY:**

The information provided in this section is to address the constant Integral Nonlinearity (INL) that exists at each angle of the RDC5028 Resolver to Digital Converter (RDC). This error is repeatable from chip to chip and provides a look up Table of offsets that can be added to the output of the Resolver to Digital Converter to obtain the 5.3 minute accuracy.

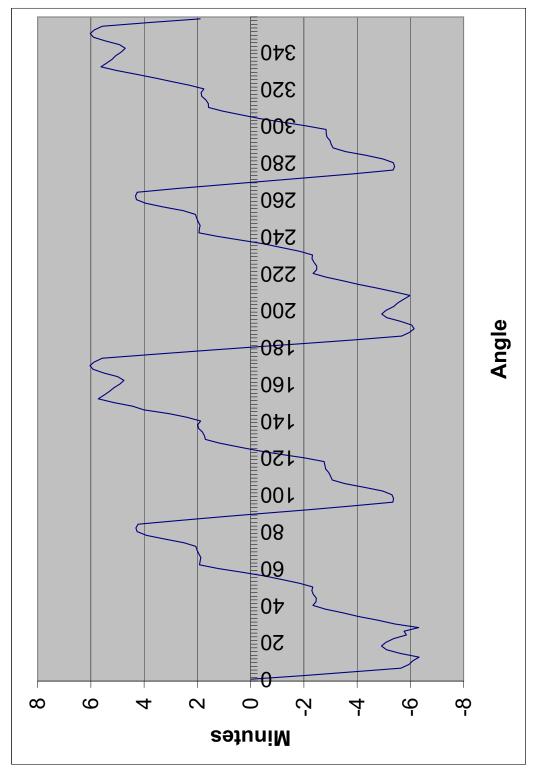

Figure 8 shows the error in Minutes that exists at  $2^{\circ}$  increments for the full  $360^{\circ}$ . Note that the INL error from  $0^{\circ}$  to  $180^{\circ}$  is basically the same as the error between  $180^{\circ}$  and  $360^{\circ}$ . Table II has the angle and correction factor (in Minutes) that must be added to zero out the INL error.

A simple calculation can be performed to derive a correction factor for angles that fall between the angles listed in Table II herein.

AL = Larger Angle AS = Smaller Angle CL = Correction Factor associated with larger Angle CS = Correction Factor associated with smaller Angle NA = New Angle NCF = New Correction Factor

Formula: NCF = CS + (((NA - AS) / (AL - AS)) \* (CL - CS))

Example:

Require the correction factor @ 15<sup>o</sup> for 5028-3-1

NCF = 5.10687 + (((15 - 14) / (16 - 14)) \* (5.61783 - 5.10687)) NCF = 5.10687 + (((1) / (2)) \* .51096) NCF = 5.10687 + (.5 \* .51096) NCF = 5.10687 + .25548 NCF = 5.36235 minutes

| Angle | Correction<br>Factor | Angle | Correction<br>Factor | Angle | Correction<br>Factor | Angle | Correction<br>Factor |

|-------|----------------------|-------|----------------------|-------|----------------------|-------|----------------------|

| 0     | 0.020387             | 90    | 0.557245             | 180   | 0.018688             | 270   | 0.535159             |

| 2     | 2.013632             | 92    | 2.253179             | 182   | 2.047610             | 272   | 2.242985             |

| 4     | 3.864167             | 94    | 3.867565             | 184   | 3.923629             | 274   | 3.864167             |

| 6     | 5.646746             | 96    | 5.342640             | 186   | 5.679026             | 276   | 5.356231             |

| 8     | 5.951268             | 98    | 5.370238             | 188   | 5.963160             | 278   | 5.411012             |

| 10    | 6.097790             | 100   | 5.311191             | 190   | 6.140263             | 280   | 5.360460             |

| 12    | 6.327559             | 102   | 4.961630             | 192   | 6.050635             | 282   | 4.982017             |

| 14    | 5.617827             | 104   | 4.284177             | 194   | 5.641612             | 284   | 4.331747             |

| 16    | 5.106868             | 106   | 3.543865             | 196   | 5.111965             | 286   | 3.572746             |

| 18    | 4.917005             | 108   | 3.066884             | 198   | 4.923800             | 288   | 3.095766             |

| 20    | 5.080516             | 110   | 3.004440             | 200   | 5.094107             | 290   | 3.026526             |

| 22    | 5.374844             | 112   | 2.936898             | 202   | 5.368048             | 292   | 2.981070             |

| 24    | 5.856053             | 114   | 2.821787             | 204   | 5.533258             | 294   | 2.864260             |

| 26    | 5.761329             | 116   | 2.789923             | 206   | 5.751135             | 296   | 2.840891             |

| 28    | 6.313892             | 118   | 2.758059             | 208   | 5.989399             | 298   | 2.836209             |

| 30    | 5.408785             | 120   | 2.010951             | 210   | 5.400290             | 300   | 2.075510             |

| 32    | 4.777203             | 122   | 1.092252             | 212   | 4.768708             | 302   | 1.180596             |

| 34    | 4.060675             | 124   | 0.222822             | 214   | 4.062374             | 304   | 0.317962             |

| 36    | 3.463072             | 126   | -0.47841             | 216   | 3.471566             | 306   | -0.38497             |

| 38    | 2.811103             | 128   | -1.18305             | 218   | 2.821297             | 308   | -1.06413             |

| 40    | 2.339220             | 130   | -1.69741             | 220   | 2.346015             | 310   | -1.58528             |

| 42    | 2.458559             | 132   | -1.73267             | 222   | 2.480645             | 312   | -1.58996             |

| 44    | 2.467469             | 134   | -1.81210             | 224   | 2.479361             | 314   | -1.67959             |

| 46    | 2.354057             | 136   | -1.95779             | 226   | 2.381239             | 316   | -1.83547             |

| 48    | 2.300107             | 138   | -1.98626             | 228   | 2.305203             | 318   | -1.86054             |

| 50    | 2.332801             | 140   | -1.87711             | 230   | 2.326006             | 320   | -1.75479             |

| 52    | 1.849025             | 142   | -2.40166             | 232   | 1.837133             | 322   | -2.29293             |

| 54    | 1.188562             | 144   | -3.07912             | 234   | 1.171573             | 324   | -2.97718             |

| 56    | 0.523002             | 146   | -4.01311             | 236   | 0.497518             | 326   | -3.61556             |

| 58    | -0.33114             | 148   | -4.43062             | 238   | -0.34473             | 328   | -4.32699             |

| 60    | -1.21076             | 150   | -5.13696             | 240   | -1.22435             | 330   | -5.04352             |

| 62    | -1.92219             | 152   | -5.72437             | 242   | -1.94088             | 332   | -5.62413             |

| 64    | -1.89799             | 154   | -5.51329             | 244   | -1.92687             | 334   | -5.40795             |

| 66    | -1.87039             | 156   | -5.30390             | 246   | -1.89418             | 336   | -5.20707             |

| 68    | -1.94813             | 158   | -5.13530             | 248   | -1.97361             | 338   | -5.06734             |

| 70    | -2.01057             | 160   | -4.91062             | 250   | -2.02926             | 340   | -4.86136             |

| 72    | -2.05603             | 162   | -4.76070             | 252   | -2.07132             | 342   | -4.70974             |

| 74    | -2.50413             | 164   | -4.99474             | 254   | -2.52961             | 344   | -4.92339             |

| 76    | -3.23255             | 166   | -5.51759             | 256   | -3.26992             | 346   | -5.45983             |

| 78    | -3.90830             | 168   | -5.92152             | 258   | -3.94058             | 348   | -5.90113             |

| 80    | -4.26466             | 170   | -6.03663             | 260   | -4.29014             | 350   | -6.02644             |

| 82    | -4.31011             | 172   | -5.87312             | 262   | -4.32540             | 352   | -5.86972             |

| 84    | -4.22645             | 174   | -5.57369             | 264   | -4.25703             | 354   | -5.57199             |

| 86    | -2.72929             | 176   | -3.78432             | 266   | -2.75308             | 356   | -3.78602             |

| 88    | -1.10131             | 178   | -1.88282             | 268   | -1.11321             | 358   | -1.89811             |

### TABLE II – CORRECTION FACTORS (MINUTES)

### **ORDERING INFORMATION**

| MODEL                                | DLA SMD #                          | SCREENING                                                                                                                                 | PACKAGE |

|--------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|

| RDC5028-3-1-7 <u>1</u> /             |                                    | Commercial Flow, +25°C testing only                                                                                                       |         |

| RDC5028-3-1-S <u>1</u> /             | -                                  | Military Temperature, -55°C to +125°C<br>Screened in accordance with the individual Test Methods<br>of MIL-STD-883 for Space Applications | CQFP    |

| RDC5028-301-1S<br>RDC5028-301-2S     | 5962-0423503KXC<br>5962-0423503KXA | In accordance with DLA SMD                                                                                                                |         |

| RDC5028-931-1S<br>RDC5028-931-2S     | 5962H0423503KXC<br>5962H0423503KXA | In accordance with DLA Certified RHA Program Plan to<br>RHA Level "H", 1 Mrad(Si)                                                         |         |

| RDC5028, Evaluation board <u>2</u> / | -                                  | -                                                                                                                                         | -       |

Notes

1/ Dash #'s:

The first dash number indicates the revision of silicon:

-3 = Rev. C

The second dash number indicates the wafer lot run.

-1 = First diffusion lot

2/ See Application note AN5028-1

### **EXPORT CONTROL:**

This product is controlled for export under the International Traffic in Arms Regulations (ITAR). A license from the U.S. Government is required prior to the export of this product from the United States.

20