ATMX150RHA

## Introduction

REG200RHA is a radiation-hardened linear voltage regulator including Power-on-Reset (POR) and Power Fail Detector (PFD) capability. It operates between 3V to 5.5V and provides a fixed 1.8V output voltage while sourcing up to 200 mA of load current.

A 470 nF external capacitor has to be connected to the regulator output V<sub>OUT</sub> to ensure stability and noise rejection. The following table lists the physical parameters of the regulator.

#### Table 1. Physical Parameters

| Parameter      | Value                    |

|----------------|--------------------------|

| Supply Voltage | 3V to 5.5V               |

| Placement      | Core (next to periphery) |

| Height         | 744.8 μm                 |

| Width          | 481.6                    |

| Area           | 0.359 mm <sup>2</sup>    |

# **Table of Contents**

| Intr | oduction1                                   | I |

|------|---------------------------------------------|---|

| 1.   | Pin Description                             | 3 |

| 2.   | Operating Modes Description                 | 1 |

| 3.   | Bandgap Calibration                         | 5 |

| 4.   | Specifications                              | 5 |

| 5.   | Radiation Hardness7                         | 7 |

| 6.   | Typical Application                         | 3 |

| 7.   | Testability Requirements                    | ) |

| 8.   | Testability Information11                   |   |

| 9.   | Integration Guidelines                      | 2 |

|      | 9.1. Placement and General Rules            | 2 |

|      | 9.2. Supplies Routing and Decoupling12      | 2 |

|      | 9.3. Analog Signals Routing                 | ) |

|      | 9.4. Routing Constraints                    |   |

| 10.  | Revision History14                          | 1 |

| Mic  | rochip Information15                        |   |

|      | The Microchip Website15                     | 5 |

|      | Product Change Notification Service         | 5 |

|      | Customer Support15                          | 5 |

|      | Microchip Devices Code Protection Feature15 | 5 |

|      | Legal Notice15                              |   |

|      | Trademarks                                  | 5 |

|      | Quality Management System                   |   |

|      | Worldwide Sales and Service                 |   |

# 1. Pin Description

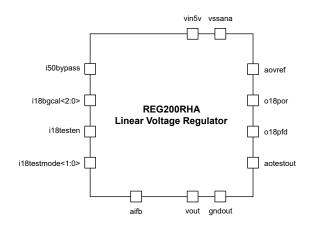

The following figure shows the package diagram of the regulator.

#### Figure 1-1. Package Diagram

The following table lists the pin details of the package.

| Pin Name         | I/O | Related Supply | Description                                                        |

|------------------|-----|----------------|--------------------------------------------------------------------|

| vin5v            | I/O | —              | Input power supply                                                 |

| vssana           | I/O | —              | Input ground                                                       |

| i18bgcal<2:0>    | I   | vout           | Internal bandgap voltage reference calibration bits, see Table 3-1 |

| i50bypass        | 1   | vin5v          | Enables Bypass mode when set to 1                                  |

| i18testen        | I   | vout           | Enables Test mode when set to 1                                    |

| i18testmode<1:0> | I.  | vout           | Test mode selection bits, see Table 4-1                            |

| vout             | I/O | _              | Regulated voltage output. Used as an input in Bypass mode          |

| gndout           | I/O | -              | Regulated voltage ground                                           |

| aifb             | I   | —              | Regulated voltage sense input                                      |

| aovref           | 0   | -              | Bandgap reference voltage output                                   |

| o18por           | 0   | vout           | PoR signal equals to 1 during reset                                |

| o18pfd           | 0   | vout           | PFD equals to 1 when fail is detected                              |

| aotestout        | 0   | _              | Output pin in Test mode to get few regulator outputs               |

#### Table 1-1. Pinout

# 2. Operating Modes Description

The voltage regulator can operate in the following modes:

| i50bypass | i18testen | Operating Mode                                                                                                                                                                                                                                          |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | 0         | Normal mode: Regulator can provide full load. PoR and PFD functions are enabled. Bandgap reference voltage is available.                                                                                                                                |

| 0         | 1         | Test mode: Different voltages are accessible through aotestout pin, depending on i18testmode<1:0> setting. Full load capability is available. POR and PFD functions are disabled, $v(ol8por) = v(ol8pfd) = 0$ . Bandgap reference voltage is available. |

| 1         | 0         | Bypass mode: No output regulated voltage, the 1.8V supply voltage is provided<br>by an external source. POR and PFD functions are enabled. Bandgap reference<br>voltage is available.                                                                   |

| 1         | 1         | Bypass and Test mode: Useful to characterize internal blocks of the regulator, power supplied by vout. POR and PFD functions are disabled. Bandgap reference voltage is available.                                                                      |

#### Table 2-1. Operating Mode Table

#### Notes:

- The regulator must be supplied with power through the pin vin5v, even in Bypass mode.

- In Bypass mode, the power ON/OFF rising and falling edges, on the pin vout, induce charging current in the external decoupling capacitor C<sub>L</sub>. This current must not be greater than I<sub>LOAD</sub> max. (C<sub>L</sub> and I<sub>LOAD</sub> values are given in the section 4. Specifications.)

# 3. Bandgap Calibration

The voltage regulator embeds its own reference voltage. Three calibration bits are available to adjust the reference voltage ( $V_{REF}$ ) and consequently the output regulated voltage ( $V_{OUT}$ ). For precision applications, the calibration might be necessary to compensate the process fluctuation during the fabrication.

The dynamic adjustment of the output regulated voltage is not allowed. The calibration bits must be set before the voltage regulator start-up. The typical calibration step is vcal\_step = 5 mV.

| i18bgcal<2> | i18bgcal<1> | i18bgcal<0> | Reference Voltage                  |

|-------------|-------------|-------------|------------------------------------|

| 0           | 0           | 0           | V <sub>REF</sub> + (3 x vcal_step) |

| 0           | 0           | 1           | V <sub>REF</sub> + (1 x vcal_step) |

| 0           | 1           | 0           | V <sub>REF</sub> + (1 x vcal_step) |

| 0           | 1           | 1           | V <sub>REF</sub>                   |

| 1           | 0           | 0           | V <sub>REF</sub> - (1 x vcal_step) |

| 1           | 0           | 1           | V <sub>REF</sub> - (2 x vcal_step) |

| 1           | 1           | 0           | V <sub>REF</sub> - (3 x vcal_step) |

| 1           | 1           | 1           | V <sub>REF</sub> - (4 x vcal_step) |

#### Table 3-1. Reference Voltage

The calibration is done during the production final test. The relevant settings of i18bgcal<2:0> is stored in the product and used at each start-up.

# 4. Specifications

The following table lists the specification details over the operating temperature range (Tj = -55 °C to 145 °C), V<sub>IN</sub> = 3.3V, and CL = 470 nF, unless otherwise noted. The listed typical values are at Tj = 25 °C.

| Parameter                  |                                                                      | Test Condition                                                 | Min   | Тур  | Max   | Unit   |

|----------------------------|----------------------------------------------------------------------|----------------------------------------------------------------|-------|------|-------|--------|

| V <sub>IN</sub>            | Input voltage range                                                  | -                                                              | 3     | -    | 5.5   | V      |

| LOAD                       | Output rated current                                                 | —                                                              | 0     | —    | 200   | mA     |

| load_start_up <sup>1</sup> | Maximum load current during start-up                                 | Vin > 3V                                                       | _     | —    | 3     | mA     |

| CL                         | External decoupling capacitor                                        | -                                                              | 446.5 | 470  | 493.5 | nF     |

| R <sub>ESR</sub>           | Decoupling capacitor ESR                                             | —                                                              | —     | —    | 0.5   | Ω      |

| RISE                       | Input voltage rising                                                 | From 0V to V <sub>IN</sub> min.                                | 1e-6  | —    | 1     | s      |

| V <sub>OUT</sub>           | Output regulated voltage                                             | —                                                              | 1.68  | 1.8  | 1.95  | V      |

| V <sub>REF</sub>           | Internal reference voltage                                           | Tj = 25 °C                                                     | —     | 0.9  | —     | V      |

| T <sub>COREF</sub>         | Reference temperature coefficient                                    | -                                                              | —     | 121  | _     | ppm/°C |

| ΔV <sub>OUT(ΔVIN)</sub>    | Line regulation                                                      | $3V \le V_{IN} \le 5.5V$                                       | _     | 1    | _     | %      |

|                            | Transient line regulation                                            | $\Delta V_{IN} / \Delta t = 1 V / \mu s$                       | _     | 5    | _     | %      |

| ΔV <sub>OUT(ΔILOAD)</sub>  | Load regulation                                                      | $0 \text{ mA} \le I_{LOAD} \le 200 \text{ mA}$                 | _     | 1    | _     | %      |

|                            | Transient load regulation                                            | $\Delta I_{LOAD}/\Delta t = 100 \text{ mA}/\mu \text{s}$       | —     | 5    | —     | %      |

| V <sub>DO</sub>            | Dropout voltage<br>(V <sub>IN</sub> = V <sub>OUT</sub> (nom) - 0.1V) | I <sub>LOAD</sub> = 200 mA                                     | -     | -    | 500   | mV     |

| Z <sub>DO</sub>            | Output impedance in dropout                                          | $3V \le V_{IN} \le V_{OUT} + V_{DO}$                           | _     | 1    | -     | Ω      |

| PWR                        | Ground pins current                                                  | $0 \text{ mA} \le I_{LOAD} \le 200 \text{ mA},$<br>Normal mode | —     | -    | 500   | μΑ     |

| FB                         | aifb pin current                                                     | —                                                              | —     | —    | 10    | μA     |

| PSRR                       | Power Supply Rejection                                               | F = 100 Hz, I <sub>LOAD</sub> = 200 mA                         | 40    | —    | —     | dB     |

|                            | Ratio                                                                | F = 10 kHz, I <sub>LOAD</sub> = 200 mA                         | 20    | —    | —     |        |

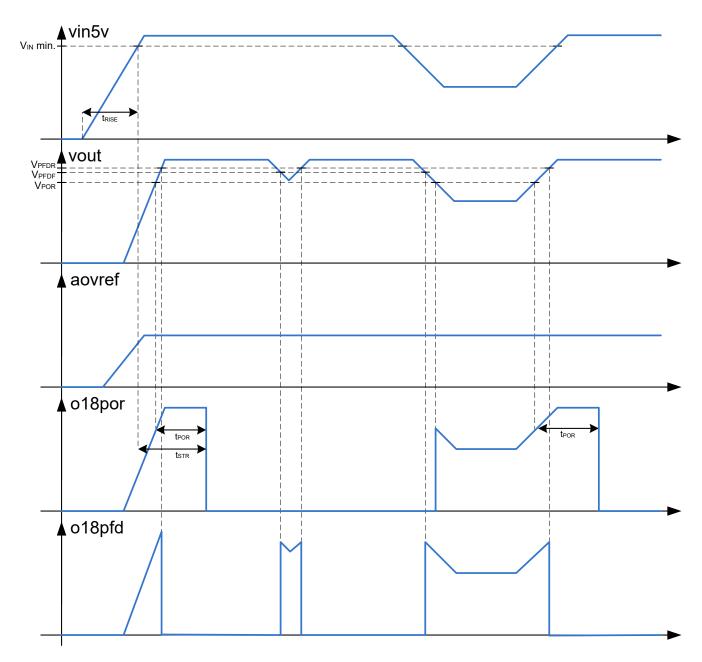

| t <sub>str</sub>           | Startup time                                                         | —                                                              | —     | —    | 1     | ms     |

| V <sub>POR</sub>           | PoR threshold                                                        | —                                                              | —     | 1.60 | —     | V      |

| t <sub>POR</sub>           | PoR delay time                                                       | -                                                              | —     | —    | 500   | μs     |

| V <sub>PFDF</sub>          | PFD falling threshold                                                | —                                                              | _     | 1.65 | _     | V      |

| V <sub>PFDR</sub>          | PFD rising threshold                                                 | -                                                              | _     | 1.70 | _     | V      |

#### Note:

1. When o18por = 1, the regulator is in the start-up condition, meaning the POR threshold has not been reached.

**Note:** The output regulated voltage is  $V_{OUT} = 1.8V$ . It can vary between 1.68V and 1.95V because of IR drops, undershoots, and overshoots coming from the current consumption on the regulator output pin vout.

The minimum and maximum values of V<sub>OUT</sub> have taken already into account the minimum and maximum variation of V<sub>REF</sub>, T<sub>COREF</sub>,  $\Delta V_{OUT(\Delta VIN)}$ , and  $\Delta V_{OUT(\Delta ILOAD)}$ . Typical values are given for information purpose only.

# 5. Radiation Hardness

The following table lists the radiation tolerance related specifications.

| Parameter | Conditions                                                                                                    | Range                                     |

|-----------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| TID       | ESCC 22900 and MIL-STD-883 TM 1019 - RT<br>Input supply voltage V <sub>IN</sub> max and Dose Rate < 360 rad/h | 100 krad(Si) RHA (tested 150<br>krad(Si)) |

| SEL       | ESCC 25100 and JESD57A<br>Input supply voltage V <sub>IN</sub> max and Tj = 125 °C                            | > 60 MeV.cm <sup>2</sup> /mg              |

| SET/SEU   | Input supply voltage $V_{IN}$ min and Tj = 25 °C                                                              | > 60 MeV.cm <sup>2</sup> /mg              |

#### Table 5-1. Radiation Tolerance Specification

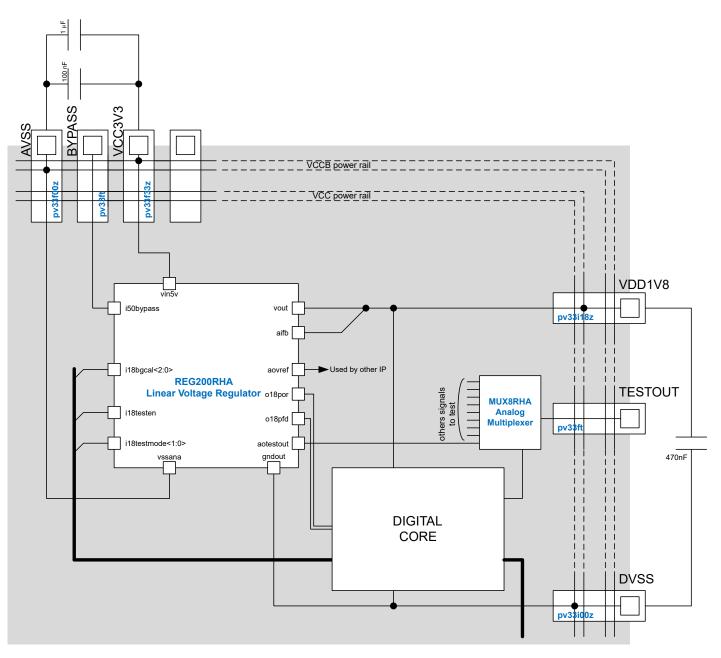

# 6. Typical Application

The following figures describe a 3.3V circuit with a 1.8V digital core power supplied by the REG200RHA. The voltages on the regulator pins (vin5v and i50bypass) must not exceed the I/O buffer power supply voltage (in this case, 3.3V).

The regulator output pin (vout) is connected to the VCC power rail and to the circuit power supply grid.

The external decoupling capacitors have to be connected to the power supply buffers of the regulator.

### Figure 6-1. Typical Application Scheme

#### Figure 6-2. Typical Timing Characteristics

# 7. Testability Requirements

Unless otherwise specified at the DSR, the  $V_{OUT}$  parameter must be measured when the asic is in active and non-active mode and at the minmum and maximum values on the vin5v pin.

For this test, the pin oatestout must be accessible through a primary I/O.

# 8. Testability Information

The regulator have access to a test pin, aotestout, which allows to make measurement to characterize the regulator performance as listed in the following table.

Table 8-1.

Test Mode Output Selection

| i18testmode<1> | i18testmode<0> | Information Available on aotestout  |

|----------------|----------------|-------------------------------------|

| 0              | 0              | Internal bandgap reference voltage  |

| 0              | 1              | Internal POR signal                 |

| 1              | 0              | Internal Power Fail Detector signal |

| 1              | 1              | Regulated voltage feedback signal   |

When i18testmode<1:0> = (0, 0), the internal bandgap reference voltage is available on aotestout. The measurement must be done with high impedance probe (active probe recommended).

When i18testmode<1:0> = (0, 1), the internal POR signal is available on aotestout while the POR pin, o18por, is forced to 0. Therefore, the product can run normally while the POR voltage is measured.

When i18testmode<1:0> = (1, 0), the internal PFD signal is available on aotestout while the PFD pin, o18pfd, is forced to 0. Therefore, the product can run normally while PFD voltage is measured.

When i18testmode<1:0> = (1, 1), the regulated voltage feedback signal is available on aotestout. Therefore, the regulated voltage coming from the core is accessible while a current sinks through the pin  $V_{OUT}$  of the regulator.

## 9. Integration Guidelines

The following sections describe the various integration guidelines.

### 9.1 Placement and General Rules

This cell is very sensitive to electrical noise. Therefore, it must be placed in the quietest part of the circuit. It is preferably placed close to the I/O buffers that are connected to vin5v and vssana, in order to reduce the resistivity of the power lines.

The wires used to connect the voltage regulator must be as wide as their corresponding pins.

**Note:** Never place several voltage regulators in parallel to increase the current capability.

### 9.2 Supplies Routing and Decoupling

The power supply and ground pins (vin5v and vssana) as well as the regulated output and the created ground pins (vout and gndout) must be star-routed to their corresponding I/O buffers with less than 0.1  $\Omega$  of parasitic resistance.

External decoupling capacitors must be connected to ensure performance. A 100 nF capacitor in parallel with a 1  $\mu$ F ceramic capacitor (X7R) is needed between the pins, vin5v and vssana. A 470 nF ceramic capacitor (X7R) is needed between the pins, vout and gndout. The ESR value must be kept within the boundary defined in Table 4-1.

All the decoupling capacitors must be as close as possible to the package.

All the decoupling capacitors must connect to a large area low impedance ground plane through or short trace to minimize inductance.

### 9.3 Analog Signals Routing

All the analog signals must be routed to have less than 1  $\Omega$  parasitic resistance, including associated I/O cell for core blocks.

All the analog signals must be routed to have less than 1 pF parasitic capacitance, not including associated I/O cell for core blocks.

The signal routed to the pin, aifb, is the regulated voltage feedback or FB signal. All the digital or the clock signals must be routed with 1  $\mu$ m spacing away from the FB signal. In case of crossing the digital or the clock signals, a shield must be added, connected to the analog ground line, between the noisy net and the FB signal.

The output pin, aovref, provides a reference voltage. All the digital or the clock signals must be routed with 1  $\mu$ m spacing away from the signal connected to aovref, V<sub>REF</sub> signal. In case of crossing the digital or the clock signals, a shield must be added, connected to the analog ground line, between the noisy net and the V<sub>REF</sub> signal.

In case of any of this condition is not met, contact the design group to investigate any potential performance impact.

### 9.4 Routing Constraints

The following table lists the routing constratints.

#### Table 9-1. Routing Constraints

| Pin Name         | Signal Type | Related<br>Power<br>Supply | Max DC<br>Current<br>Flowing (mA) | Max Allowed<br>Routing Resistance<br>(Ω) | Max Allowed<br>Capacitance <b>to</b><br>Ground (pF) | Other<br>constraints                                                                                                                                  |

|------------------|-------------|----------------------------|-----------------------------------|------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| vin5v            | Supply      | —                          | 200                               | 0.1                                      | —                                                   | Star routed to power supply input                                                                                                                     |

| vssana           | Ground      | -                          | 1                                 | 0.1                                      | -                                                   | Star routed to power supply input                                                                                                                     |

| i18bgcal<2:0>    | Digital     | vout                       | —                                 | —                                        | _                                                   | -                                                                                                                                                     |

| i50bypass        | Digital     | vin5v                      | —                                 | —                                        | —                                                   | —                                                                                                                                                     |

| i18testen        | Digital     | vout                       | —                                 | —                                        | _                                                   | _                                                                                                                                                     |

| i18testmode<1:0> | Digital     | vout                       | _                                 | —                                        | —                                                   | _                                                                                                                                                     |

| vout             | Supply      | —                          | 200                               | 0.1                                      | _                                                   | Star routed to power supply input                                                                                                                     |

| gndout           | Ground      | -                          | 1                                 | 0.1                                      | -                                                   | Star routed to power supply input                                                                                                                     |

| aifb             | Analog      |                            | 0.01                              | 10                                       | 0.1                                                 | No crossing with<br>other signal,<br>shielding to<br>vssana must be<br>inserted in that<br>case.<br>1 um minimum<br>spacing to other<br>signal trace. |

| aovref           | Analog      | _                          | _                                 |                                          | 1                                                   | No crossing with<br>other signal,<br>shielding to<br>vssana must be<br>inserted in that<br>case.<br>1 um minimum<br>spacing to other<br>signal trace. |

| o18por           | Digital     | vout                       | _                                 | _                                        | _                                                   | _                                                                                                                                                     |

| o18pfd           | Digital     | vout                       | -                                 | _                                        | _                                                   | _                                                                                                                                                     |

| aotestout        | Analog      | _                          | _                                 | _                                        | _                                                   | _                                                                                                                                                     |

# 10. Revision History

| Revision | Date    | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 09/2023 | Added a new ${\sf I}_{\sf load\_start\_up}$ parameter in the Electrical Specification table. See Table 4-1.                                                                                                                                                                                                                                                                 |

| A        | 07/2020 | <ul> <li>The following is a summary of changes in revision A of this document.</li> <li>The template was updated.</li> <li>The document number was updated from 41068 to DS60001639.</li> <li>Bandgap table correction</li> <li>The "testability" paragraph was replaced with "testability requirements". For more information, see 7. Testability Requirements.</li> </ul> |

## **Microchip Information**

### The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.

### Legal Notice

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure

that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at www.microchip.com/en-us/support/design-help/ client-support-services.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2023, Microchip Technology Incorporated and its subsidiaries. All Rights Reserved.

ISBN: 978-1-6683-3181-1

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

| MERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|--------------------------|-----------------------|-------------------------|-----------------------|

| orporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| andler, AZ 85224-6199    | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| l: 480-792-7200          | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| ax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| chnical Support:         | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| ww.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| eb Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| ww.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| lanta                    | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| uluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| l: 678-957-9614          | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| nx: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| ustin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| l: 512-257-3370          | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| oston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| estborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| el: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| ax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| hicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| asca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| l: 630-285-0071          | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| ax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| ddison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| el: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| ax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| etroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| ovi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| l: 248-848-4000          | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| ouston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| l: 281-894-5983          | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| dianapolis               | China - Xiamen        |                         | Tel: 31-416-690399    |

| oblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| l: 317-773-8323          | China - Zhuhai        |                         | Norway - Trondheim    |

| ax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| l: 317-536-2380          |                       |                         | Poland - Warsaw       |

| os Angeles               |                       |                         | Tel: 48-22-3325737    |

| ssion Viejo, CA          |                       |                         | Romania - Bucharest   |

| : 949-462-9523           |                       |                         | Tel: 40-21-407-87-50  |

| ix: 949-462-9608         |                       |                         | Spain - Madrid        |

| l: 951-273-7800          |                       |                         | Tel: 34-91-708-08-90  |

| aleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| l: 919-844-7510          |                       |                         | Sweden - Gothenberg   |

| ew York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| l: 631-435-6000          |                       |                         | Sweden - Stockholm    |

| an Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| el: 408-735-9110         |                       |                         | UK - Wokingham        |

| el: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| anada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

| l: 905-695-1980          |                       |                         |                       |