# RFMD 🔊

**RF2637**

#### **RECEIVE AGC AMPLIFIER**

#### **RoHS Compliant & Pb-Free Product**

#### **Typical Applications**

- 3V Basestation Systems

- General Purpose Linear IF Amplifier

- Commercial and Consumer Systems

- Portable Battery-Powered Equipment

#### **Product Description**

The RF2637 is a complete AGC amplifier designed for the receive section of 3V cellular and PCS applications basestations. It is designed to amplify IF signals while providing more than 90dB of gain control range. Noise Figure, IP<sub>3</sub>, and other specifications are designed for basestations. The IC is manufactured on an advanced high frequency SiGe process, and is packaged in a standard miniature 8-lead plastic MSOP package.

#### **Optimum Technology Matching® Applied**

| -          |            |              |

|------------|------------|--------------|

| 🔲 Si BJT   | GaAs HBT   | GaAs MESFET  |

| Si Bi-CMOS | 🗹 SiGe HBT | Si CMOS      |

| InGaP/HBT  | GaN HEMT   | SiGe Bi-CMOS |

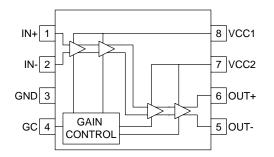

#### **Functional Block Diagram**

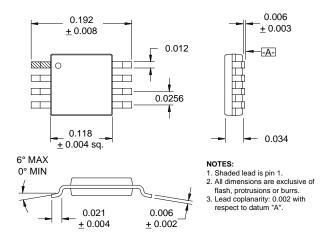

Package Style: MSOP-8

#### **Features**

- Supports Basestation Applications

- -55dB to +51dB Gain Control Range @ 85MHz

- Single 3V Power Supply

- -2dBm Input IP<sub>3</sub>

- 12MHz to 385MHz Operation

#### Ordering Information RF2637 Receive AGC Amplifier

RF2637 PCBA Fully Assembled Evaluation Board

RF Micro Devices, Inc.

Tel (336) 664 1233

7628 Thorndike Road

Fax (336) 664 0454

Greensboro, NC 27409, USA

http://www.rfmd.com

#### **Absolute Maximum Ratings**

| Parameter                     | Value        | Unit            |

|-------------------------------|--------------|-----------------|

| Supply Voltage                | -0.5 to +5.0 | V <sub>DC</sub> |

| Control Voltage               | -0.5 to +5.0 | V <sub>DC</sub> |

| Input RF Power                | +10          | dBm             |

| Operating Ambient Temperature | -40 to +85   | °C              |

| Storage Temperature           | -40 to +150  | °C              |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. RoHS marking based on EUDirective 2002/95/EC (at time of this printing). However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                    | Specification |            | Unit | Condition       |                                                                                                   |  |

|------------------------------|---------------|------------|------|-----------------|---------------------------------------------------------------------------------------------------|--|

| Farameter                    | Min. Typ.     |            | Max. |                 | Condition                                                                                         |  |

|                              |               |            |      |                 | T=25°C, 85MHz, V <sub>CC</sub> =3.0V, Z <sub>S</sub> =500Ω,                                       |  |

|                              |               |            |      |                 | $Z_L$ =500Ω, 500Ω External Input Terminating                                                      |  |

| Overall                      |               |            |      |                 | Resistor, $500\Omega$ External Output Terminating                                                 |  |

|                              |               |            |      |                 | Resistor (Effective $Z_S = 333 \Omega$ , Effective $Z_I = 250 \Omega$ ) (See Application Example) |  |

| Frequency Range              |               | 12 to 385  |      | MHz             | Z <sub>2</sub> =23032) (See Application Example)                                                  |  |

| Maximum Gain                 | +40           | +51        | +65  | dB              | V <sub>GC</sub> =2.5V, 85MHz                                                                      |  |

| Minimum Gain                 | -65           | -55        | -40  | dB              | V <sub>GC</sub> =0.1V, 85MHz                                                                      |  |

| Maximum Gain                 | +35           | +45        | +55  | dB              | V <sub>GC</sub> =2.5V, 385MHz                                                                     |  |

| Minimum Gain                 | -68           | -58        | -48  | dB              | V <sub>GC</sub> =0.1V, 385MHz                                                                     |  |

| Gain Slope                   | 00            | 57         | -0   | dB/V            | Note 1                                                                                            |  |

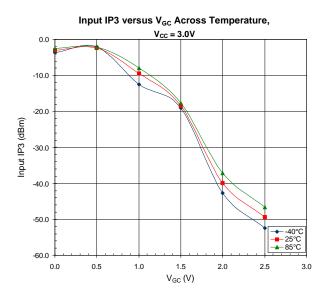

| Gain Control Voltage Range   |               | 0 to 2.5   |      | V <sub>DC</sub> | Source impedance of 4.7 k $\Omega$                                                                |  |

| Gain Control Input Impedance |               | 30         |      | kΩ              |                                                                                                   |  |

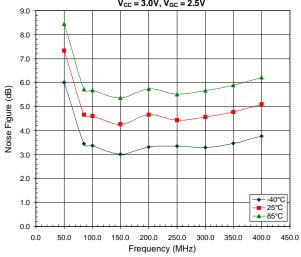

| Noise Figure                 |               | 5          | 7.2  | dB              | At maximum gain and 85MHz                                                                         |  |

| Input IP <sub>3</sub>        | -46           | -40        |      | dBm             | At +40 dB gain, referenced to $500 \Omega$                                                        |  |

| -                            |               | -2         |      | dBm             | At minimum gain, referenced to $500\Omega$                                                        |  |

| Stability (Max VSWR)         | 10:1          |            |      |                 | Spurious<-70dBm                                                                                   |  |

| IF Input                     |               |            |      |                 |                                                                                                   |  |

| Input Impedance              |               | 1          |      | kΩ              | CDMA, differential                                                                                |  |

| Power Supply                 |               |            |      |                 |                                                                                                   |  |

| Voltage                      |               | 2.7 to 3.4 |      | V               |                                                                                                   |  |

| Current Consumption          | 6             | 10         | 15   | mA              | Minimum gain, $V_{CC}$ =3.0V                                                                      |  |

|                              | 7             | 11.5       | 15   | mA              | Maximum gain, $V_{CC}$ =3.0V                                                                      |  |

| Thermal                      |               |            |      |                 |                                                                                                   |  |

| Thermal Resistance           |               | 150        |      | °C/W            | Theta J-Ref 85°C                                                                                  |  |

| Maximum Junction Temperature |               | 90         |      | °C              | Ref 85°C                                                                                          |  |

Note 1: Measured between a gain control voltage of 1.0V to 1.5V.

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interface Schematic                               |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1   | IN+      | CDMA balanced input pin. This pin is internally DC-biased and should be DC-blocked if connected to a device with a DC level other than $V_{CC}$ present. A DC to connection to $V_{CC}$ is acceptable. For single-ended input operation, one pin is used as an input and the other CDMA input is AC-coupled to ground. The balanced input impedance is $1 k\Omega$ , while the single-ended input impedance is $500\Omega$ .                                                                                                     | BIAS<br>700 Ω<br>CDMA+ O<br>CDMA+<br>CDMA+        |

| 2   | IN-      | Same as pin 2, except complementary input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | See pin 1.                                        |

| 3   | GND      | Ground connection. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |

| 4   | GC       | Analog gain adjustment for all amplifiers. Valid control ranges are from 0V to 2.5V. Maximum gain is selected with 2.5V. Minimum gain is selected with 0V. These voltages are only valid for a 4.7k $\Omega$ DC source impedance.                                                                                                                                                                                                                                                                                                | 23.5 kΩ<br>23.5 kΩ<br>12.7 kΩ<br>12.7 kΩ<br>15 kΩ |

| 5   | OUT-     | Balanced output pin. This is an open-collector output, designed to operate into a 250 $\Omega$ balanced load. The load sets the operating impedance, but an external choke or matching inductor to V <sub>CC</sub> must also be supplied in order to correctly bias this output. This bias inductor is typically incorporated in the matching network between the output and next stage. Because this pin is biased to V <sub>CC</sub> , a DC-blocking capacitor must be used if the next stage's input has a DC path to ground. |                                                   |

| 6   | OUT+     | Same as pin 5, except complementary output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 5.                                        |

| 7   | VCC2     | Supply voltage pin. External bypassing is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                         |                                                   |

| 8   | VCC1     | Same as pin 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | See pin 7.                                        |

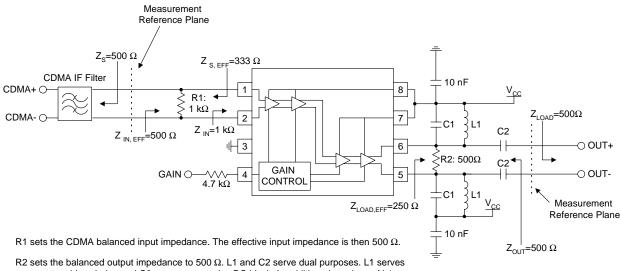

### **Application Schematic**

R2 sets the balanced output impedance to 500  $\Omega$ . L1 and C2 serve dual purposes. L1 serves as an output bias choke, and C2 serves as a series DC block. In addition, the values of L1 and C2 may be chosen to form an impedance matching network of the load impedance is not 500  $\Omega$ . Otherwise, the values of L1 and C1 are chosen to form a parallel-resonant tank circuit at the IF when the load impedance is 500  $\Omega$ .

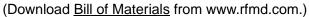

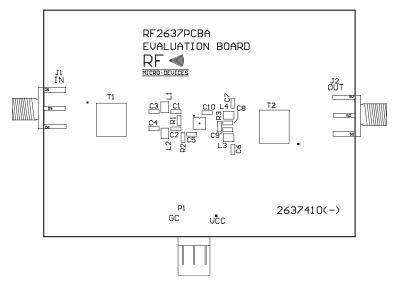

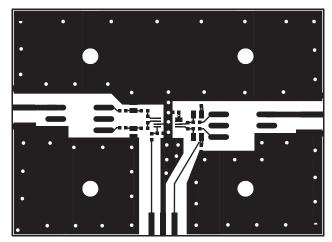

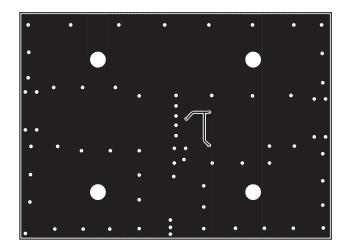

### **Evaluation Board Schematic**

### Evaluation Board Layout Board Size 2.750" x 2.000"

Board Thickness 0.031", Board Material FR-4

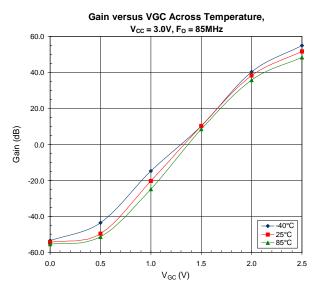

Noise Figure versus Frequency Across Temperature,  $V_{CC} = 3.0V, V_{GC} = 2.5V$