### 750 W, 50 V, HF to 500 MHz RF power LDMOS transistor

| Pin connection |                      |  |  |

|----------------|----------------------|--|--|

| Pin            | Connection           |  |  |

| 1              | Gate                 |  |  |

| 2              | Drain                |  |  |

| 3              | Source (bottom side) |  |  |

#### **Features**

| Order code                  | Frequency | V <sub>DD</sub> | P <sub>OUT</sub> | Gain  | Efficiency |

|-----------------------------|-----------|-----------------|------------------|-------|------------|

| RF5L05750CF2 <sup>(1)</sup> | 108 MHz   | 50 V            | 1500 W           | 20 dB | 78%        |

- Measured on 88-108 MHz wideband test board with two RF5L05750CF2 devices connected in push-pull.

- · High efficiency and linear gain operations

- · Integrated ESD protection

- Large positive and negative gate-source voltage range for improved class C operation

- · Excellent thermal stability, low HCI drift

- In compliance with the european directive 2002/95/EC

#### **Applications**

- 30-88 MHz/136-174 MHz ground communication

- 1.6-30 MHz HF transceiver

- Plasma generator

- · Particle accelerator

- · FM and VHF TV broadcast

#### **Description**

The RF5L05750CF2 is a 750 W, 50 V, high performance, unmatched LDMOS FET, designed for wideband commercial and industrial applications in the frequency range from HF to 500 MHz. It can be used for both CW and pulse application. It is featured for high power and high ruggedness, suitable for industrial, scientific and medical application, as well as FM radio, VHF TV and aerospace applications.

# Product status link RF5L05750CF2

| Product summary    |                   |  |  |  |

|--------------------|-------------------|--|--|--|

| Order code         | RF5L05750CF2      |  |  |  |

| Marking            | 5L05750           |  |  |  |

| Package            | C2                |  |  |  |

| Packing            | Tape and reel 13" |  |  |  |

| Base/bulk quantity | 100/100           |  |  |  |

## 1 Electrical ratings

Table 1. Absolute maximum ratings (T<sub>C</sub> = 25 °C)

| Symbol           | Parameter                    | Value      | Unit |

|------------------|------------------------------|------------|------|

| V <sub>DS</sub>  | Drain-source voltage         | 110        | V    |

| V <sub>GS</sub>  | Gate-source voltage          | -8 to 10   | V    |

| V <sub>DD</sub>  | Maximum operating voltage    | 55         | V    |

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 200        | °C   |

Table 2. Thermal data

| Symbol                           | Parameter                            | Value | Unit |  |

|----------------------------------|--------------------------------------|-------|------|--|

| R <sub>thJC</sub> <sup>(1)</sup> | Thermal resistance, junction-to-case | 0.08  | °C/W |  |

<sup>1.</sup>  $T_{\rm C}$  = 85 °C ,  $P_{\rm OUT}$  = 1500 W, pulsed CW output at 108 MHz, two RF5L05750CF2 devices connected in push-pull.

Table 3. ESD protection

| Symbol | Test methodology                                               | Class |

|--------|----------------------------------------------------------------|-------|

| HBM    | Human body model (according to ANSI/ESDA/JEDEC JS001-2017)     | 2     |

| CDM    | Charge device model (according to ANSI/ESDA/JEDEC JS-002-2014) | C3    |

DS13746 - Rev 2 page 2/12

#### 2 Electrical characteristics

Table 4. Static

| Symbol               | Parameter                        | Test conditions                                  | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------|--------------------------------------------------|------|------|------|------|

| V <sub>(BR)DSS</sub> | Drain-source breakdown voltage   | $V_{GS} = 0 \text{ V}, I_{DS} = 100 \mu\text{A}$ | 110  |      |      | V    |

| l                    | Zero gate voltage drain leakage  | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 50 V    |      |      | 1    |      |

| I <sub>DSS</sub>     | current                          | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 90 V    |      |      |      | μA   |

| I <sub>GSS</sub>     | Gate-source leakage current      | V <sub>GS</sub> = -8/10 V, V <sub>DS</sub> = 0 V |      |      | ±100 | nA   |

| V <sub>GS(th)</sub>  | Gate threshold voltage           | V <sub>DS</sub> = 50 V, I <sub>D</sub> = 600 μA  | 2.3  |      | 2.9  | V    |

| $V_{GS(Q)}$          | Gate quiescent voltage           | V <sub>DS</sub> = 50 V, I <sub>D</sub> = 230 mA  | 2    |      | 5    | V    |

| V <sub>DS(on)</sub>  | Static drain-source on-voltage   | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 6 A     |      |      | 1    | V    |

| I <sub>DS(on)</sub>  | Static drain-source on-current   | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 100 mV |      |      | 2.5  | Α    |

| R <sub>DS(on)</sub>  | Drain-source on-state resistance | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 100 mV |      |      | 1    | Ω    |

Table 5. Dynamic

| Symbol           | Parameter        | Test conditions                             | Min. | Тур. | Max. | Unit |

|------------------|------------------|---------------------------------------------|------|------|------|------|

| P <sub>OUT</sub> | Output power     | f = 108 MHz, pulsed CW,<br>3 dB compression | -    | 1500 |      | W    |

| G <sub>PS</sub>  | Power gain       |                                             | -    | 20   |      | dB   |

| $\eta_{D}$       | Drain efficiency |                                             | -    | 78   |      | %    |

| VSWR             | Load mismatch    | P <sub>OUT</sub> = 1500 W, all phases       | -    |      | 10:1 |      |

Note:

- 1.  $V_{DD}$  = 50 V,  $I_{DQ}$  = 200 mA, pulse width = 100  $\mu$ s, duty cycle = 10%.

- 2. Measured on 88-108 MHz wideband test board with two RF5L05750CF2 devices connected in push-pull.

DS13746 - Rev 2 page 3/12

## 3 Typical performances

GADG201220211228GT Power gain, GPS (dB) Drain efficiency, η<sub>D</sub> (%) P<sub>OUT</sub> (dbm)  $\textbf{G}_{\text{PS}}$  $\eta_D$  .....

Figure 1. Power gain and drain efficiency vs output power (f = 108 MHz)

Note:

- 1.  $V_{DD} = 50 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$ , pulse width = 100  $\mu$ s, duty cycle = 10%.

- 2. Measured on 88-108 MHz wideband test board with two RF5L05750CF2 devices connected in push-pull.

DS13746 - Rev 2 page 4/12

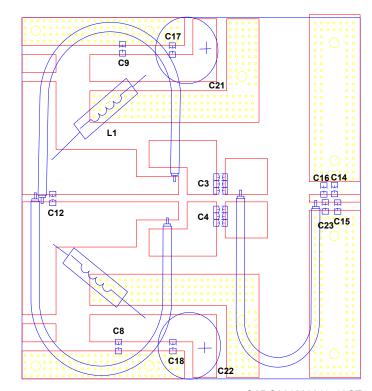

#### 4 Test circuits

C24 C13 R1

Figure 2. Test circuit layout (88-108 MHz frequency band)

GADG201220211410GT

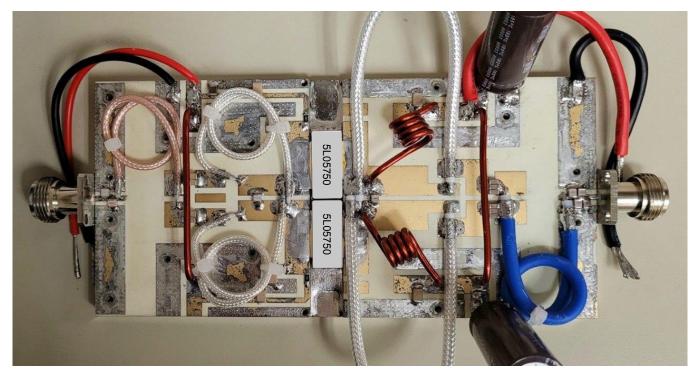

Figure 3. Test circuit photo

GADG201220211418GT

DS13746 - Rev 2 page 5/12

Table 6. Components list

| Component          | Value                           | Reference                   |

|--------------------|---------------------------------|-----------------------------|

| C1, C2             | 10 nF (2x)                      | C4532X7R3D103KT000N         |

| C3, C4             | 470 pF (3x)                     | ATC800B                     |

| C5                 | 27 pF                           | DLC70B                      |

| C6-C11             | 100 nF                          | C4532X7R3D103KT000N         |

| C12                | 20 pF                           | DLC70B                      |

| C13                | 68 pF                           | ATC800B                     |

| C23, C14, C55, C16 | 3.9 pF                          | DLC70B                      |

| C17, C18, C19, C20 | 10 μF                           | 100 V ceramic capacitor     |

| C21, C22           | 2200 μF                         | 63 V electrolitic capacitor |

| C24                | 10 pF                           | ATC800B                     |

| R1, R2             | 16 Ω                            | 0805 chip resistor          |

| R3, R4             | 470 Ω                           | 0805 chip resistor          |

| T1                 | 50 Ω 150 mm                     | SFF-50-1.5                  |

| T2, T3             | 25 Ω line length =150 mm 9:1    | SFF-25-1.5                  |

| T4, T5             | 12.5 Ω line length = 150 mm 9:1 | SFF-12.5-1.5                |

| T6                 | 50 Ω 150 mm                     | RG402-3                     |

| L1, L2             | 4tums Φ1 mm                     |                             |

| PCB                | 0.762 mm (0.030") thick, εr = 3 | 3.48, Rogers RO4350B        |

DS13746 - Rev 2 page 6/12

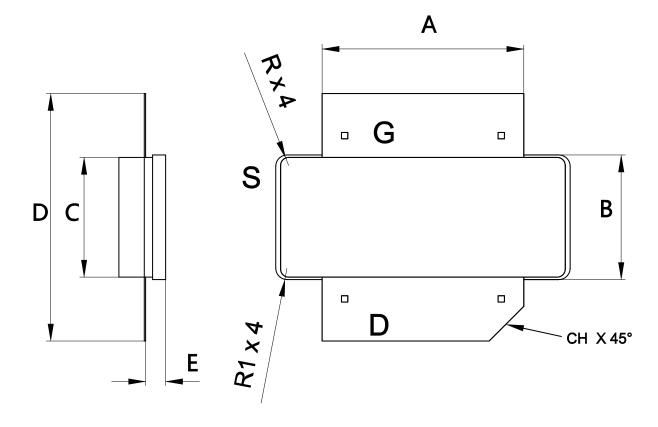

## 5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

#### **5.1** C2 package information

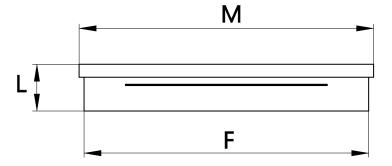

Figure 4. C2 package outline

DM00666714\_2

DS13746 - Rev 2 page 7/12

Table 7. C2 package mechanical data

| Symbol | Millimeters |        |        |  |  |

|--------|-------------|--------|--------|--|--|

| Symbol | Min.        | Тур.   | Max.   |  |  |

| Α      | 15.713      | 15.840 | 15.967 |  |  |

| В      | 9.653       | 9.780  | 9.907  |  |  |

| С      | 9.273       | 9.400  | 9.527  |  |  |

| D      | 19.303      | 19.430 | 19.557 |  |  |

| E      | 1.443       | 1.570  | 1.697  |  |  |

| F      | 22.223      | 22.350 | 22.477 |  |  |

| L      | 3.543       | 3.670  | 3.797  |  |  |

| M      | 22.993      | 23.120 | 23.247 |  |  |

| СН     |             | 2.720  |        |  |  |

| R      |             | 0.630  |        |  |  |

| R1     |             | 0.880  |        |  |  |

DS13746 - Rev 2 page 8/12

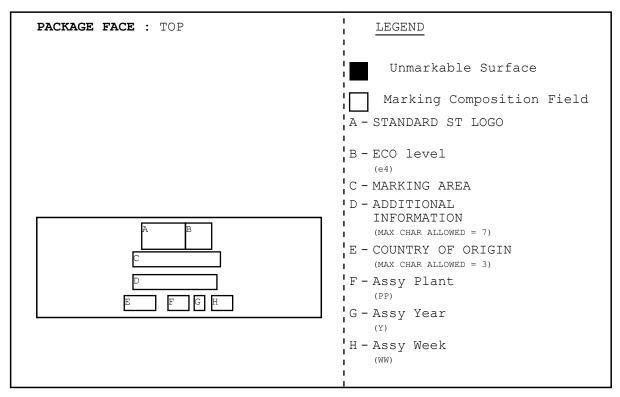

#### 5.2 Marking information

Figure 5. Marking composition

GADG040220211644GT

DS13746 - Rev 2 page 9/12

## **Revision history**

**Table 8. Document revision history**

| Date        | Version | Changes                                                                                       |

|-------------|---------|-----------------------------------------------------------------------------------------------|

| 24-May-2021 | 1       | First release.                                                                                |

|             | 2       | Updated Features and Description on cover page.                                               |

| 22-Dec-2021 |         | Updated Table 1. Absolute maximum ratings (T <sub>C</sub> = 25 °C) and Table 2. Thermal data. |

| 22-Dec-2021 |         | Updated Section 2 Electrical characteristics.                                                 |

|             |         | Added Section 3 Typical performances and Section 4 Test circuits.                             |

DS13746 - Rev 2 page 10/12

#### **Contents**

| 1   | Elec   | trical data            | 2  |

|-----|--------|------------------------|----|

| 2   | Elec   | trical characteristics | 3  |

| 3   | Турі   | cal performances       | 4  |

| 4   | Test   | circuits               | 5  |

| 5   | Pacl   | kage information       | 7  |

|     | 5.1    | C2 package information | 7  |

|     | 5.2    | Marking information    | 9  |

| Rev | /ision | history                | 10 |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13746 - Rev 2 page 12/12