## Operational Amplifier

### DESCRIPTION

The RH108A is a precision operational amplifier particularly well-suited for high source impedance applications requiring low offset and bias currents and low power-consumption.

The wafer lots are processed to Analog Devices' in-house Class S flow to yield circuits usable in stringent-military applications.

For complete electrical specifications, performance curves and applications information, see the LM108A/LM108 data sheet.

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltage                       | ±20V          |

|--------------------------------------|---------------|

| Differential Input Current (Note 1)  |               |

| Input Voltage (Note 2)               | ±15V          |

| Output Short-Circuit Duration        | Indefinite    |

| Operating Temperature Range          | 55°C to 125°C |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | )300°C        |

|                                      |               |

All registered trademarks and trademarks are the property of their respective owners.

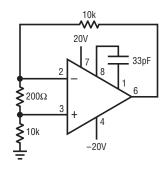

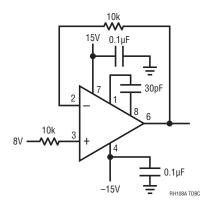

### **BURN-IN CIRCUIT**

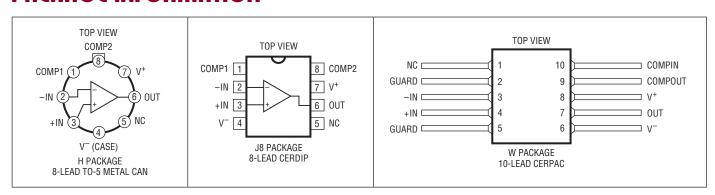

### PACKAGE INFORMATION

Rev. E

# **TABLE 1: ELECTRICAL CHARACTERISTICS** (Preirradiation, Note 4) Device is characterized at the TID levels below. Device is production tested at 100kRad(si).

| SYMBOL                             | PARAMETER                           | CONDITIONS                                             | NOTES | MIN   | A = 25°<br>TYP | C<br>Max | SUB-<br>GROUP | –55°C<br>Min | ≤ T <sub>A</sub> ≤ TYP | 125°C<br>Max | SUB-<br>GROUP | UNITS |

|------------------------------------|-------------------------------------|--------------------------------------------------------|-------|-------|----------------|----------|---------------|--------------|------------------------|--------------|---------------|-------|

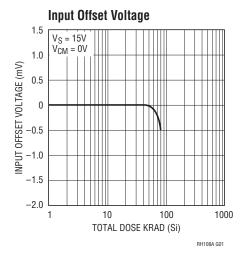

| V <sub>OS</sub>                    | Input Offset Voltage                |                                                        |       |       |                | 0.5      | 1             |              |                        | 1.0          | 2,3           | mV    |

| $\Delta V_{OS}$<br>$\Delta Temp$   | Average Tempco of Offset<br>Voltage |                                                        | 3     |       |                |          |               |              |                        | 5.0          |               | μV/°C |

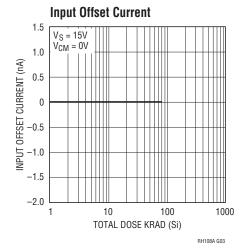

| I <sub>OS</sub>                    | Input Offset Current                |                                                        |       |       |                | 0.2      | 1             |              |                        | 0.4          | 2,3           | nA    |

| $\frac{\Delta I_{S}}{\Delta Temp}$ | Average Tempco of Offset<br>Current |                                                        | 3     |       |                |          |               |              |                        | 2.5          |               | pA/°C |

| I <sub>B</sub>                     | Input Bias Current                  |                                                        |       |       |                | 2.0      | 1             |              |                        | 3.0          | 2,3           | nA    |

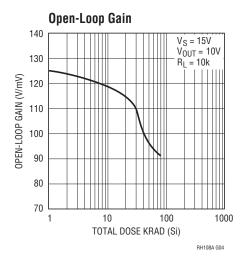

| A <sub>VOL</sub>                   | Large-Signal Voltage Gain           | $V_S = \pm 15V$ , $V_{OUT} = \pm 10V$<br>$R_L \ge 10k$ |       | 80    |                |          | 4             | 40           |                        |              | 5,6           | V/mV  |

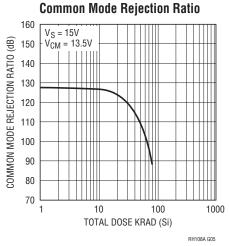

| CMRR                               | Common Mode Rejection Ratio         |                                                        |       | 96    |                |          | 1             | 96           |                        |              | 2,3           | dB    |

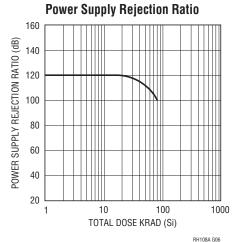

| PSRR                               | Power Supply Rejection Ratio        |                                                        |       | 96    |                |          | 1             | 96           |                        |              | 2,3           | dB    |

|                                    | Input Voltage Range                 | V <sub>S</sub> = ±15V                                  | 3     | ±13.5 |                |          |               | ±13.5        |                        |              |               | V     |

| V <sub>OUT</sub>                   | Output Voltage Swing                | $V_S = \pm 15V, R_L = 10k$                             |       | ±13   |                |          | 4             | ±13          |                        |              | 5,6           | V     |

| R <sub>IN</sub>                    | Input Resistance                    |                                                        | 3     | 30    |                |          |               |              |                        |              |               | MΩ    |

| I <sub>S</sub>                     | Supply Current                      | (Note 6)                                               |       |       |                | 0.6      | 1             |              |                        | 0.4          | 2             | mA    |

# **TABLE 1A: ELECTRICAL CHARACTERISTICS** (Preirradiation, Note 4) Device is characterized at the TID levels below. Device is production tested at 100kRad(si).

| SYMBOL           | PARAMETER                    | CONDITIONS                                          | NOTES | 10KRA<br>MIN | D (Si)<br>Max | 20KRA<br>Min | D (Si)<br>Max | 50KRA<br>Min | D (Si)<br>Max | 80KRA<br>Min | D (Si)<br>Max | UNITS |

|------------------|------------------------------|-----------------------------------------------------|-------|--------------|---------------|--------------|---------------|--------------|---------------|--------------|---------------|-------|

| $V_{0S}$         | Input Offset Voltage         |                                                     |       |              | 0.5           |              | 0.5           |              | 0.5           |              | 1.0           | mV    |

| I <sub>OS</sub>  | Input Offset Current         |                                                     |       |              | 0.3           |              | 0.3           |              | 0.3           |              | 0.3           | nA    |

| I <sub>B</sub>   | Input Bias Current           |                                                     |       |              | ±2.0          |              | ±2.0          |              | ±2.0          |              | ±4.0          | nA    |

| A <sub>VOL</sub> | Large-Signal Voltage Gain    | $V_S = \pm 15V, V_{OUT} = \pm 10V$<br>$R_L \ge 10k$ |       | 98           |               | 98           |               | 90           |               | 86           |               | dB    |

| CMRR             | Common Mode Rejection Ratio  |                                                     |       | 96           |               | 96           |               | 84           |               | 70           |               | dB    |

| PSRR             | Power Supply Rejection Ratio |                                                     | 4     | 96           |               | 96           |               | 84           |               | 70           |               | dB    |

|                  | Input Voltage Range          |                                                     | 3     | ±13.5        |               | ±13.5        |               | ±13.5        |               | ±13.5        |               | V     |

| V <sub>OUT</sub> | Output Voltage Swing         |                                                     |       | ±13          |               | ±13          |               | ±13          |               | ±13          |               | V     |

| R <sub>IN</sub>  | Input Resistance             |                                                     | 3     | 30           |               | 30           |               | 30           |               | 30           |               | MΩ    |

| I <sub>S</sub>   | Supply Current               |                                                     |       |              | 0.6           |              | 0.6           |              | 0.6           |              | 0.6           | mA    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: For supply voltages less than ±15V, the maximum input voltage isequal to the supply voltage.

Note 3: Guaranteed by design, characterization or correlation to othertested parameters.

Note 4:  $\pm 5V \le V_S \le \pm 20V$  preirradiation,  $\pm 5V \le V_S \le \pm 15V$  postirradiation, unless otherwise noted.

**Note 5:**  $V_S = \pm 15V$ ,  $V_{CM} = 0V$ ,  $T_A = 25$ °C unless otherwise noted.

Note 6:  $25^{\circ}C \le T_A \le 125^{\circ}C$ .

### TABLE 2: ELECTRICAL TEST REQUIREMENTS

| MIL-PRF-38535 TEST REQUIREMENTS         | SUBGROUP          |

|-----------------------------------------|-------------------|

| Final Electrical Test Requirements      | 1*, 2, 3, 4, 5, 6 |

| Group A Test Requirements               | 1, 2, 3, 4, 5, 6  |

| Group C End Point Electrical Parameters | 1                 |

| Group D End Point Electrical Parameters | 1                 |

| Group E End Point Electrical Parameters | 1                 |

<sup>\*</sup>PDA applies to subgroup 1. See PDA Test Notes.

#### **PDA Test Notes**

The PDA is specified as 5% based on failures from group A, subgroup 1, tests after cooldown as the final electrical test in accordance with method 5004 of MIL-STD-883 Class B. The verified failures (including Delta parameters) of group A, subgroup 1, after burn-in divided by the total number of devices submitted for burn-in in that lot shall be used to determine the percent for the lot.

Analog Devices reserves the right to test to tighter limits than those given.

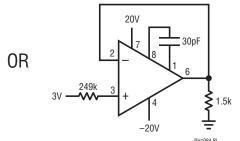

### TOTAL DOSE BIAS CIRCUIT

## **REVISION HISTORY** (Revision history begins at Rev C)

| REV | DATE  | DESCRIPTION                                                                                        | PAGE NUMBER |

|-----|-------|----------------------------------------------------------------------------------------------------|-------------|

| С   | 11/10 | Note 4 revised and added to Power Supply Rejection Ratio.                                          | 2           |

| D   | 7/23  | Updated art title in the Electrical Characteristics section and updated the document to ADI format | 1–4         |

| Е   | 7/24  | Updated Table 2: Electrical Test Requirements                                                      | 3           |

### TYPICAL PERFORMANCE CHARACTERISTICS