# **Datasheet**

RM126x LoRaWAN™ Module

Part Numbers: RM126x (RM1261 and RM1262)

Version 1.3

Americas: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852-2762-4823

## **REVISION HISTORY**

| Version | Date         | Notes                                                                                          | Contributor(s)                              | Approver              |

|---------|--------------|------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------|

| 0.1     | 17 May 2023  | Preliminary Release                                                                            | Raj Khatri<br>Dave Drogowski                | Senthooran<br>Ragavan |

| 0.2     | 29 Sept 2023 | Replaced "MCU" with SoC" where applicable. Replaced "microcontroller" to SoC" in Figure 4      | Raj Khatri<br>Dave Drogowski                | Senthooran<br>Ragavan |

| 0.3     | 20 Oct 2023  | Updated Sleep currents in Table 8 of section 3.3.4 LoRa Power Consumption.                     | Greg Leach<br>Dave Drogowski                | Senthooran<br>Ragavan |

| 0.4     | 23 Oct 2023  | Updated orientation for MOSI/MISO signals and pad for BUSY signal in Block Diagram and Pin-out | Raj Khatri<br>Dave Drogowski                | Senthooran<br>Ragavan |

| 1.0     | 24 Oct 2023  | Initial Release                                                                                | Various                                     | Senthooran<br>Ragavan |

| 1.1     | 31 Oct 2023  | Added Note 6 for EFR32 Soc GPIO (PB01) control of RF switch (ANT_SW) pin.                      | Raj Khatri<br>Greg Leach,<br>Dave Drogowski | Senthooran<br>Ragavan |

| 1.2     | 27 Mar 2024  | Change Laird Connectivity to Ezurio                                                            | Raj Khatri<br>Dave Drogowski                | Senthooran<br>Ragavan |

| 1.3     | 10 Apr 2024  | Removed ANT-916-OC-LG-RPS antenna                                                              | Dave Drogowski                              | Senthooran<br>Ragavan |

## **CONTENTS**

| 1 | Over  | riew and Key Features                                           | 5    |

|---|-------|-----------------------------------------------------------------|------|

|   | 1.1   | Features and Benefits                                           | 5    |

|   | 1.2   | Application Areas                                               | 5    |

| 2 | Spec  | ifications                                                      | 6    |

| 3 | Hard  | ware Specifications                                             | ç    |

|   | 3.1   | Block Diagram and Pin-out                                       | ç    |

|   | 3.2   | Pin Definitions                                                 |      |

|   | 3.3   | Electrical Specifications                                       | .14  |

|   | 3.3.1 | Absolute Maximum Ratings                                        |      |

|   | 3.3.2 | Recommended Operating Parameters                                |      |

|   | 3.3.3 | BOOT pin (for AT firmware)                                      |      |

|   | 3.3.4 |                                                                 |      |

|   | 3.4   | RF Specifications                                               | .18  |

|   | 3.4.1 | LoRa / FSK RF Transmit Power                                    | .19  |

|   | 3.4.2 | External antenna                                                | .19  |

|   | 3.4.3 | 32MHz TCXO LoRa SX126x radio clock                              | . 19 |

|   | 3.4.4 | LoRa / FSK RF Receive Sensitivity vs Data Rate                  | .19  |

| 4 | EFR3  | 32 SoC Peripherals                                              | .20  |

|   | 4.1   | Power Management (includes brown-out and power on reset)        | 21   |

|   | 4.2   | Clocks                                                          | .21  |

|   | 4.2.1 | 76.8MHz HFRCO EFR32 SoC high frequency RC oscillator clock      | .21  |

|   | 4.2.2 | 32.768kHz LFXO EFR32 SoC low frequency crystal oscillator clock | .21  |

|   | 4.3   | General Purpose I/O, ADC and PWM/FREQ                           | .22  |

|   | 4.3.1 | GPIO                                                            | .22  |

|   | 4.3.2 | Timer / Counter and PWM                                         | .22  |

|   | 4.4   | Communications and other Digital peripherals                    | .23  |

|   | 4.4.1 | EUART Interface                                                 | .23  |

|   | 4.4.2 | SPI Bus (alternative USART0)                                    | .23  |

|   | 4.4.3 |                                                                 |      |

|   | 4.4.4 | Pulse Density Modulation (PDM) interface                        | .25  |

|   | 4.5   | Analog                                                          |      |

|   | 4.5.1 | Incremental Analog to Digital Convertor (IADC)                  |      |

|   | 4.5.2 | Temperature Sense                                               | .25  |

|   | 4.6   | nRESET Pin                                                      | .26  |

|   | 4.7   | Two-pin Serial-Wire Debug (SWD) Programming/Debug Interface     |      |

| 5 | -     | ammability                                                      |      |

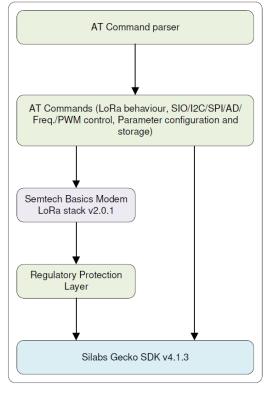

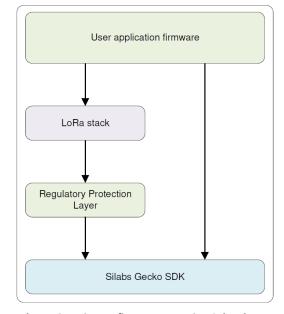

|   | 5.1   | AT Application firmware                                         |      |

|   | 5.2   | Native C Development                                            |      |

|   | 5.3   | Mandatory FW Requirements Related to Hardware                   |      |

|   | 5.4   | Certified Max RF TX power and Frequency Bands per Country       |      |

|   | 5.5   | Other Mandatory Radio Settings (Sx126x)                         |      |

| _ | 5.6   | EFR32 Low Frequency crystal oscillator (LXFO) settings          |      |

| 6 |       | ware Integration Suggestions                                    |      |

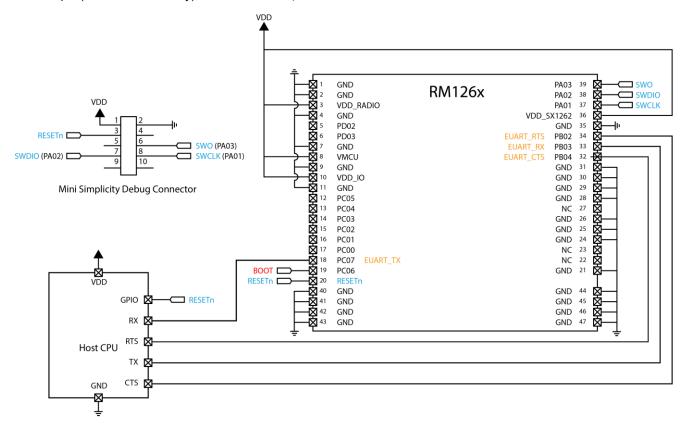

|   | 6.1   | Reference Diagrams                                              |      |

|   | 6.1.1 | RM126x with EUART Host                                          |      |

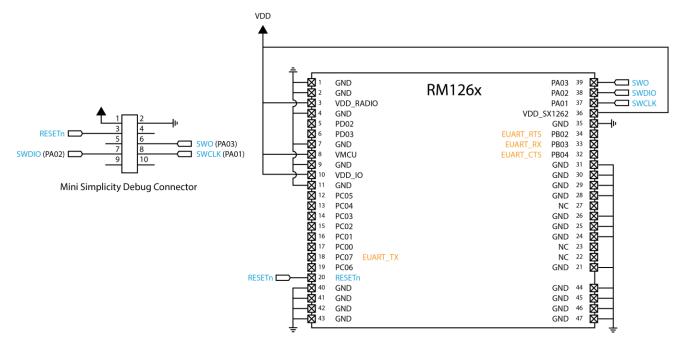

|   | 6.1.2 | RM126x standalone host-less                                     | 35   |

## RM126x LoRaWAN Module Datasheet

Americas: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852-2762-4823

| 6.2   | Circuit                                               | 35 |

|-------|-------------------------------------------------------|----|

| 6.3   | PCB Layout on Host PCB – General                      | 36 |

| 6.    | .3.1 External Antenna Proximity to Metal or Plastic   | 37 |

| 6.4   | LoRa External Antenna Integration with RM126x         | 38 |

| 7 M   | Mechanical Details                                    | 39 |

| 7.1   | RM126x Mechanical Details                             | 39 |

| 7.2   | Host PCB Land Pattern for RM126x                      | 40 |

| 8 A   | pplication Note for Surface Mount Modules             | 41 |

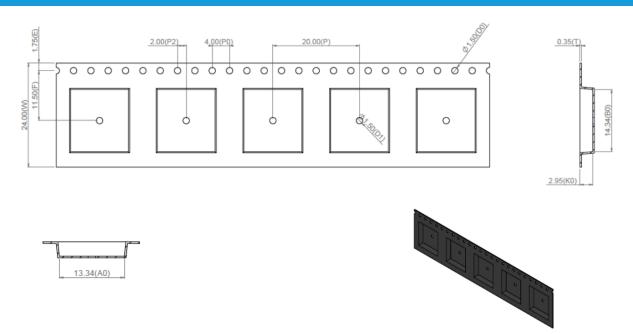

| 8.1   | Introduction                                          | 41 |

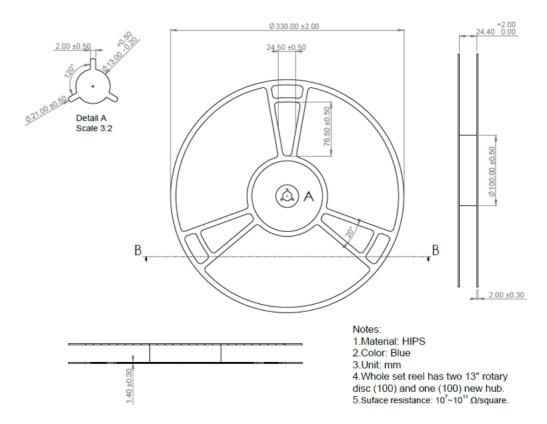

| 8.2   | Shipping                                              | 41 |

| 9 C   | Carton Contents and Packaging Process                 | 43 |

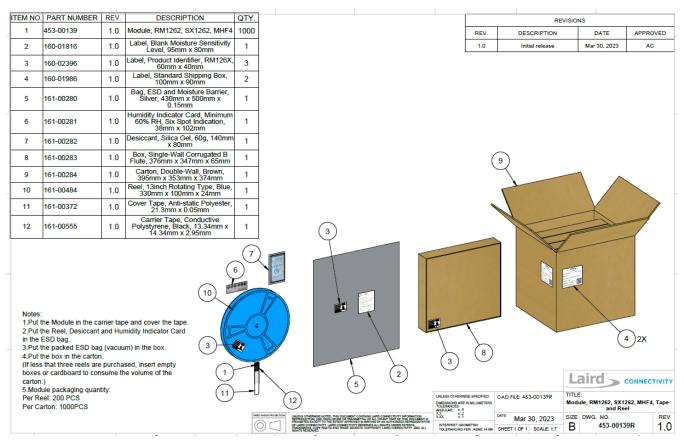

| 9.1   | Carton Contents and Packaging Process                 | 43 |

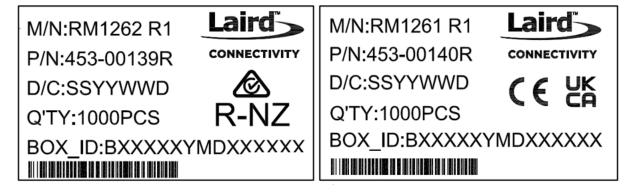

| 9.2   | Labelling                                             | 43 |

| 10 S  | oldering Recommendations                              | 44 |

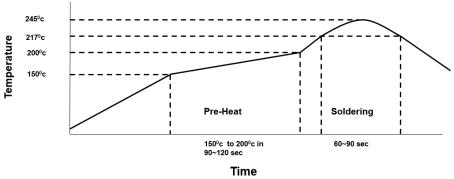

| 10.1  | Reflow for lead Free Solder Paste                     | 44 |

| 10.2  | Recommended Reflow Profile for lead Free Solder Paste | 44 |

| 11 M  | fiscellaneous                                         | 45 |

| 11.1  | Cleaning                                              | 45 |

| 11.2  | Pework                                                | 45 |

| 11.3  | Handling and Storage                                  | 45 |

| 1     | 1.3.1 Handling                                        | 45 |

| 1     | 1.3.2 Moisture Sensitivity Level (MSL)                | 45 |

| 1     | 1.3.3 Storage                                         | 45 |

| 1     | 1.3.4 Repeated Reflow Soldering                       | 45 |

| 12 R  | Reliability Test                                      | 46 |

| 12.1  | Climatic and Dynamic                                  | 46 |

| 12.2  | Reliability MTBF Prediction                           | 47 |

| 13 R  | Regulatory                                            | 47 |

| 14 O  | Ordering Information                                  | 48 |

| 15 Lo | oRaWAN Alliance END Node Qualification                | 48 |

| 15.1  | Overview                                              | 48 |

| 16 A  | dditional Informationdditional Information            | 49 |

## 1 OVERVIEW AND KEY FEATURES

This Datasheet describes both the RM1261 and RM1262. The differences are outlined in the radio specifications.

The Ezurio RM126x series of modules (RM1261 and RM1262), is based on **Silicon Labs EFR32 series SoC** and the **Semtech SX1261 / SX1262 radio.** They provide a low power, long range solution for you to easily develop your LoRaWAN™ application. The RM126x supports LoRaWAN classes A, B and C for secure, scalable, and bi-directional communication and leverages the advantages of Silicon Labs hardware, software, and tools. The Ezurio RM126x module also includes a **LoRa Point to Point (LoRa P2P)** capability which enables you to create your own private ultra-long range radio network between two RM126x modules.

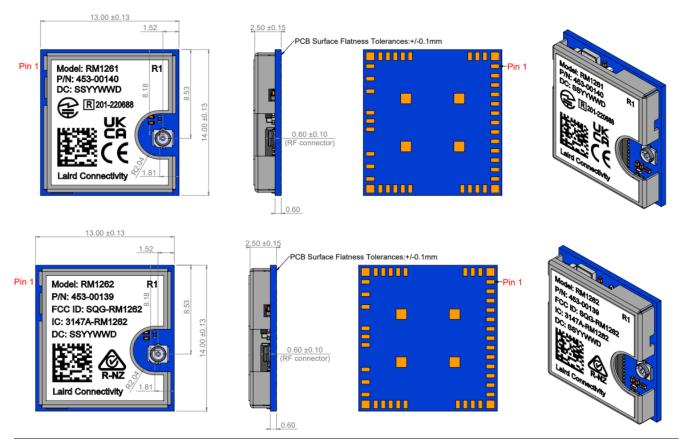

The RM126x series modules are small form factor PCB modules with a built in MHF4 connector, TCXO and a DC-DC converter.

Note:

This information in this document is subject to change. For full documentation, technical drawings, software downloads and more visit the RM126x page at: www.ezurio.com/rm126x-series

### 1.1 Features and Benefits

- Designed to operate in both hosted and hostless modes:

- Hosted Mode: When connected to an external MCU, the RM126x can be simply and easily programmed with our AT command set.

- Hostless Mode: Utilizing the powerful Cortex-M33 core which includes 512kB flash and 32K of RAM. Full support is offered by Silabs' Simplicity Studio for development purposes with a range of sample applications we offer to simplify your development.

- Designed for IoT Devices: Small 14mm x 13mm PCB module for smaller end device design.

- Based on the EFR32 series SoC: First LoRaWAN module based on Silicon Labs SoC, following Silicon Labs tools for development.

- Powerful Core Cortex-M33: 512 kB Flash, 32 kB RAM

- Many interfaces: GPIO, I2C, UART, SPI, Analog, Freq, PWM

- Ultra-low power consumption: Years of use on a single battery

- Broad regulatory region support:

- RM1261 Europe, UK, Taiwan, Japan, India

- RM1262 USA, Canada, Australia, New Zealand

- LoRa P2P Communication: create your own proprietary radio.

- Certifications: FCC, ISED, EU, UKCA, NCC, AS/NZS, MIC, IN

- Lora Alliance certified

- Fully featured development kits: Everything needed to start your LoRaWAN device development.

- Fast time-to-market

### 1.2 Application Areas

- Public or private networks

- Irrigation/Agriculture

- Parking

- Lighting

- Asset tracking

- Tank monitoring

- Smart Home smoke alarms, heating,

- Access control security

- Industrial automation factory

- Any long range, battery powered sensor application

Americas: +1-800-492-2320

Hong Kong: +852-2762-4823

Europe: +44-1628-858-940

## 2 SPECIFICATIONS

Table 1: Specifications

| Categories                          | Feature                                                | Implementation                                                                                                                                                                               |  |  |  |  |

|-------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LoRaWAN<br>Wireless                 | Specification                                          | LoRaWAN 1.04 (End Device)<br>LoRa MAC Class A, B and C                                                                                                                                       |  |  |  |  |

| Specification                       | LoRaWAN Regional Parameters specification              | LoRaWAN RP002-1.0.3 LoRaWAN Regional Parameters                                                                                                                                              |  |  |  |  |

|                                     | RF connector                                           | MHF4                                                                                                                                                                                         |  |  |  |  |

|                                     | Frequency                                              | 863-870MHz                                                                                                                                                                                   |  |  |  |  |

|                                     |                                                        | 902-928MHz                                                                                                                                                                                   |  |  |  |  |

|                                     | Maximum Transmit Power                                 | Upto 22dBm RM1262 (see Note1                                                                                                                                                                 |  |  |  |  |

|                                     | Setting (conducted)                                    | Upto 14dBm/15dBm RM1261 (see Note1                                                                                                                                                           |  |  |  |  |

|                                     | Minimum Transmit Power Setting (conducted)             | -9.0dBm RM1262<br>-17dBm RM1261                                                                                                                                                              |  |  |  |  |

|                                     | Receive Sensitivity                                    | -125.6dBm (SF7, LoRa 125kHz, 903.0MHz) -139.2dBm (SF12, LoRa 125kHz, 863.1MHz) -122.7dBm (SF7, LoRa 250kHz, 869.9MHz) -130.8dBm (SF12, LoRa 500kHz, 923.3MHz) -109 dBm (FSK 50kbps, TBD MHz) |  |  |  |  |

|                                     | Modulation, Bandwidth, data rates (as per RP002-1.0.3) | LoRa – Chirp Spread Spectrum and FSK 50kps<br>LoRa 125kHz,<br>LoRa 250kHz,<br>LoRa 500kHz,<br>FSK 50kbps                                                                                     |  |  |  |  |

|                                     | TCXO High Accuracy                                     | 32MHz ±1ppm (at 25°C) Stable Frequency over temperature and duration of the LoRa, FSK packet (longest packet is 2793.5ms)                                                                    |  |  |  |  |

|                                     | Link Budget (RM1262)                                   | et (RM1262) 183.2dB @ LoRa 125kHz, SF12, 22dBm TX power                                                                                                                                      |  |  |  |  |

|                                     | Link Budget (RM1261)                                   | 153.2dB @ LoRa 125kHz, SF12, 14dBm TX power                                                                                                                                                  |  |  |  |  |

|                                     | Range                                                  | Up to 15 km in free space                                                                                                                                                                    |  |  |  |  |

| oRa Point to<br>Point (LoRa<br>P2P) | Specification                                          | Supports Unicast or Broadcast with nodes up to 64 devices per netw                                                                                                                           |  |  |  |  |

| lost Interface                      | Total                                                  | 16 GPIOs: SWD (3 pins), EUART (4pins), Boot pin (1 pin), GPIO, I20<br>UART, SPI, Analog, Freq, PWM (8 pins)                                                                                  |  |  |  |  |

| Peripherals                         | UART                                                   | TX, RX, CTS, RTS DCD, RI, DTR, DSR, CTS, RTS (Note1) Default 115200, n, 8, 1 From 9,600 to 1,000,000 bps                                                                                     |  |  |  |  |

|                                     | GPIO                                                   | Up to 8 With configurable I/O direction, pull-up/pull-down Default Silabs "Disabled input" at application start-up (AT FW)                                                                   |  |  |  |  |

| Categories                | Feature                                             | Implementation                                                                                                                      |  |  |  |

|---------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                           | ADC                                                 | One 12-bit channel (including ADC reference) 12-bit resolution                                                                      |  |  |  |

|                           |                                                     | 1.21V internal reference or external reference VDD                                                                                  |  |  |  |

|                           | PWM or FREQ output                                  | PWM output on up to three GPIO output pins (in AT firmware):                                                                        |  |  |  |

|                           |                                                     | PWM output duty cycle 0%-100%                                                                                                       |  |  |  |

|                           |                                                     | PWM output frequency 10kHz                                                                                                          |  |  |  |

|                           |                                                     | FREQ output on up to one GPIO output pins (in AT firmware):                                                                         |  |  |  |

|                           |                                                     | FREQ output frequency 0 MHz-1 MHz (50% duty cycle)                                                                                  |  |  |  |

|                           | I2C                                                 | Upto 2xI2C interface (100 kbps, 400kbps, 1Mbps)                                                                                     |  |  |  |

|                           | SPI                                                 | Upto 2xSPI Master interface (1Mbps)                                                                                                 |  |  |  |

|                           | BOOT pin (for AT firmware)                          | BOOT pin High (default, pull-up 44KOhms): start application BOOT pin Low (externally): enter Bootloader                             |  |  |  |

|                           | SWD interface                                       | 1 x 3 pins Programming firmware (preferred)                                                                                         |  |  |  |

| Software                  | Programming or upgrade (via<br>SWD 2-pin interface) | Hosted: AT Command set Hostless: C development using Silicon Labs Simplicity Studio                                                 |  |  |  |

| Supply                    | Operating Voltage (Internally                       | RM1261: 2.0V-3.6V 14dBm                                                                                                             |  |  |  |

| Voltage                   | regulated DCDC or LDO)                              | RM1262: 3.0V-3.6V 22dBm (22dBm – 2dB)                                                                                               |  |  |  |

|                           |                                                     | 2.7V 20dBm                                                                                                                          |  |  |  |

|                           |                                                     | 2.4V 19dBm (22dBm – 3dB)                                                                                                            |  |  |  |

|                           |                                                     | 2.0V 16dBm (22dBm – 6dB)                                                                                                            |  |  |  |

| LoRa Power<br>Consumption | Peak TX current                                     | RM1262 LoRa TX 915MHz: 107mA 22dBm<br>RM1262 LoRa TX 915MHz: 50.7mA 14dBm<br>RM1261 LoRa TX 915MHz: 25.0mA 14dBm                    |  |  |  |

|                           | Peak RX current                                     | RM1262 LoRa Receive: 8.1mA (LoRa); 7.6mA (FSK) RM1261 LoRa Receive: 8.1mA (LoRa); 7.6mA (FSK)                                       |  |  |  |

|                           | Sleep current                                       | RM1262/ RM1261 Sleep: 2.6uA (EM2, Full RAM retention, RTC(LXFO)) RM1262/ RM1261 Sleep: 2.2uA (EM3, Full RAM retention, RTC(ULFRCO)) |  |  |  |

|                           |                                                     | RM1262/ RM1261 Sleep: 2.1uA (EM2, Full RAM retention, RTC(LFXO), no SoC Radio RAM retention, BURTC enabled)                         |  |  |  |

| Antenna<br>Options        | LoRa (External)                                     | Dipole antenna with up to 2.0 dBi (868MHz).                                                                                         |  |  |  |

| Options                   |                                                     | Dipole antenna with up to 2.2 dBi (915MHz).  Some with MHF4 (IPEX) connector or RP-SMA connector                                    |  |  |  |

| Physical                  | Dimensions                                          | 14 mm x 13 mm x 2 mm                                                                                                                |  |  |  |

| 1 Hysical                 | Weight                                              | 0.9 grams                                                                                                                           |  |  |  |

| Environmental             | Operating                                           | -40°C to +85°C                                                                                                                      |  |  |  |

| Livioninoniai             | Storage                                             | -40°C to +85°C                                                                                                                      |  |  |  |

| Miscellaneous             | Lead Free                                           | Lead-free and RoHS compliant                                                                                                        |  |  |  |

| Misocialicous             | Warranty                                            | 1-Year Warranty                                                                                                                     |  |  |  |

|                           | vvarianty                                           | 1-1 Cai vvailailly                                                                                                                  |  |  |  |

## RM126x LoRaWAN Module Datasheet

**Americas**: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852-2762-4823

| Categories           | Feature          | Implementation                                                                                       |

|----------------------|------------------|------------------------------------------------------------------------------------------------------|

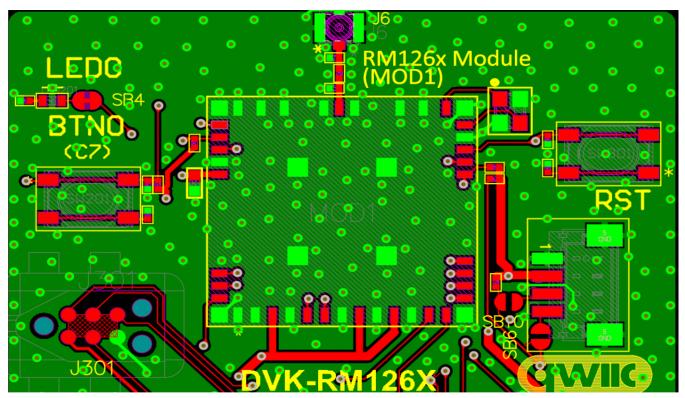

| Development<br>Tools | Development Kit  | Development Kits:<br>DVK-RM1261 (453-00140-K1), DVK-RM1262 (453-00139-K1) and<br>Free Software Tools |

| Approvals            | LoRa Alliance    | LoRaWAN Alliance End Node Certified                                                                  |

|                      | Radio Regulatory | RM1262: FCC, ISED, AS/NZS<br>RM1261: EU, UKCA, NCC(Taiwan), MIC(Japan), IN(India)                    |

**Note 1**: It is mandatory to use the correct RF registers to set RF TX power based on country radio regulatory requirements. For details, see Mandatory FW Requirements Related to Hardware.

Americas: +1-800-492-2320

Hong Kong: +852-2762-4823

Europe: +44-1628-858-940

## **3 HARDWARE SPECIFICATIONS**

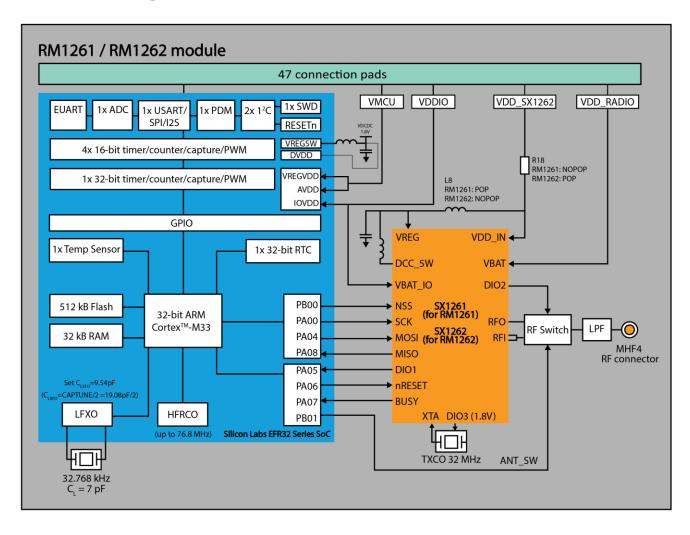

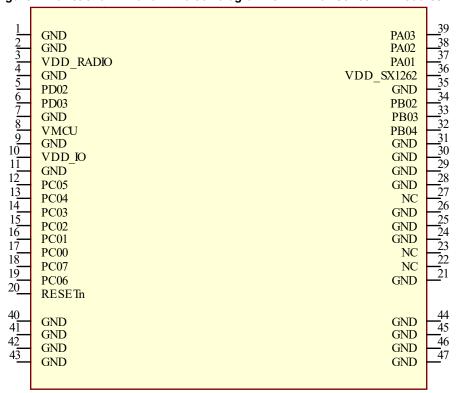

## 3.1 Block Diagram and Pin-out

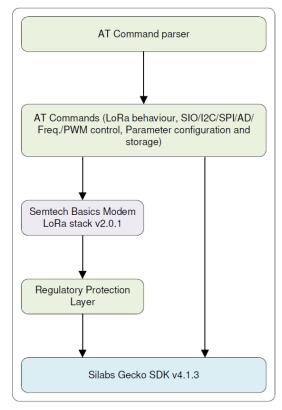

When using AT firmware

When NOT using AT firmware - Native C development

Figure 1: Functional HW and FW block diagram for RM126x series AT modules

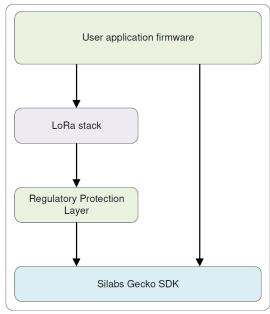

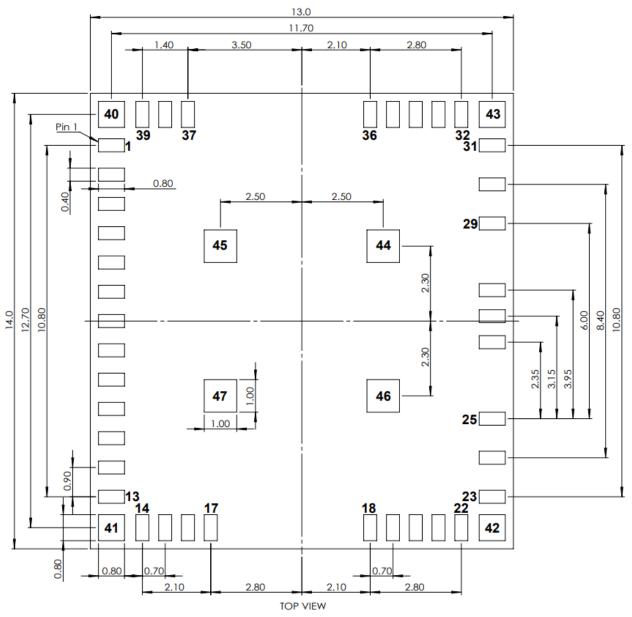

Figure 2: RM1261 and RM1262 module pin-out (top view)

## 3.2 Pin Definitions

Table 2: Pin definitions

| Table | Table 2: Pin definitions |                                                      |                                                             |                       |                    |                                                                                                                   |  |  |  |

|-------|--------------------------|------------------------------------------------------|-------------------------------------------------------------|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin#  | Pin name and Port        | Pin Name when using AT Firmware (NOTE1 for IO state) | Pin Name<br>When using Custom FW /<br>Native C development) | EFR32<br>SoC<br>pin # | EFR32 SoC pin name | Comment                                                                                                           |  |  |  |

| 1     | GND                      | -                                                    | -                                                           | -                     | -                  | -                                                                                                                 |  |  |  |

| 2     | GND                      | -                                                    | -                                                           | -                     | -                  | -                                                                                                                 |  |  |  |

| 3     | VDD_RADIO                | -                                                    | -                                                           | -                     | -                  | MUST connect to same<br>external supply as<br>VMCU, VDD_IO,<br>VDD_SX1262.                                        |  |  |  |

| 4     | GND                      | -                                                    | -                                                           | -                     | -                  | -                                                                                                                 |  |  |  |

| 5     | PD02                     | SIO07/I2C1/AN/<br>FREQ/PWM/SPI_CIPO                  | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 38                    | PD02               | MIKROE_SPI_MISO on DVK-RM126x                                                                                     |  |  |  |

| 6     | PD03                     | SIO06/I2C1/AN/<br>FREQ/PWM/SPI_COPI                  | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 37                    | PD03               | MIKROE_SPI_MOSI on DVK-RM126x                                                                                     |  |  |  |

| 7     | GND                      | -                                                    | -                                                           | -                     |                    | -                                                                                                                 |  |  |  |

| 8     | VMCU                     | -                                                    | -                                                           | 32<br>35              | VREGVDD,<br>AVDD   | MUST connect to same external supply as VDD_RADIO, VDD_IO, VDD_SX1262.                                            |  |  |  |

| 9     | GND                      | -                                                    | -                                                           | -                     | -                  | -                                                                                                                 |  |  |  |

| 10    | VDD_IO                   | -                                                    | -                                                           | 36                    | IOVDD              | MUST connect to same external supply as VDD_RADIO, VMCU, VDD_SX1262.                                              |  |  |  |

| 11    | GND                      | -                                                    | -                                                           | -                     | -                  | -                                                                                                                 |  |  |  |

| 12    | PC05                     | SIO05 /I2C1/AN/<br>FREQ/PWM                          | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 6                     | PC05/              | LED0 on DVK-RM126x<br>or MIKROE_INT on DVK-<br>RM126x                                                             |  |  |  |

| 13    | PC04                     | SIO04/I2C1/AN/<br>FREQ/PWM                           | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 5                     | PC04               | MIKROE_PWM on DVK-<br>RM126x                                                                                      |  |  |  |

| 14    | PC03                     | SIO03 /I2C1/AN/<br>FREQ/PWM                          | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 4                     | PC03               | MIKROE_RST on DVK-<br>RM126x                                                                                      |  |  |  |

| 15    | PC02                     | SIO02/I2C1/AN/<br>FREQ/PWM                           | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 3                     | PC02               | MIKROE_ANALOG on<br>DVK-RM126x                                                                                    |  |  |  |

| 16    | PC01                     | SIO01/I2C1/AN/<br>FREQ/PWM                           | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0                     | 2                     | PC01               | MIKROE_SPI_CS on<br>DVK-RM126x                                                                                    |  |  |  |

| 17    | PC00                     | SIO00/I2C1/AN/<br>FREQ/PWM/SPI_CLK                   | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 1                     | PC00               | MIKROE_SPI_SCK on DVK-RM126x                                                                                      |  |  |  |

| 18    | PC07                     | EUART_TX                                             | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0.PDM                 | 8                     | PC07               | Output, Set high in FW                                                                                            |  |  |  |

| 19    | PC06                     | воот                                                 | I2C0/I2C1/AN/<br>FREQ/PWM/EUART0/USART0/PDM                 | 7                     | PC06               | Input, default pull high<br>(not enter BOOT mode).<br>BOOT or BUTTON0 on<br>DVK-RM126x. 1Mohm<br>pull on DVK-126X |  |  |  |

| 20    | RESETn                   | RESETn                                               | RESETn                                                      | 11                    | RESETn             | System Reset (Active low). 1.8V IO voltage only. Internally pulled-up to 1.8V.                                    |  |  |  |

|      |                      | Pin Name when using              | Pin Name                                            | EFR32        |                    |                                                                                                                                                                                           |

|------|----------------------|----------------------------------|-----------------------------------------------------|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Pin name<br>and Port | AT Firmware (NOTE1 for IO state) | When using Custom FW / Native C development)        | SoC<br>pin # | EFR32 SoC pin name | Comment                                                                                                                                                                                   |

| 21   | GND                  | -                                | <u>-</u>                                            | _            | -                  | -                                                                                                                                                                                         |

| 22   | NC                   | -                                | -                                                   | -            | -                  | DO NOT CONNECT                                                                                                                                                                            |

| 23   | NC                   | -                                | -                                                   | -            | -                  | DO NOT CONNECT                                                                                                                                                                            |

| 24   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 25   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 26   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 27   | NC                   | -                                | -                                                   | -            | -                  | DO NOT CONNECT<br>Reserved for future. RF<br>pad active on future RF<br>pad variant.                                                                                                      |

| 28   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 29   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 30   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 31   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 32   | PB04                 | EUART_CTS                        | I2C0/AN/FREQ/PWM/<br>EUART0/USART0/USART1/PDM       | 15           | PB04               | Input, pull-down in AT<br>FW                                                                                                                                                              |

| 33   | PB03                 | EUART_RX                         | I2C0/AN/FREQ/PWM/<br>EUART0/USART0/USART1/PDM       | 17           | PB03               | Input, pullup in AT FW                                                                                                                                                                    |

| 34   | PB02                 | EUART_RTS                        | I2C0/AN/FREQ/PWM/<br>EUART0/USART0/USART1/PDM       | 18           | PB02               | Output Set low in AT FW                                                                                                                                                                   |

| 35   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 36   | VDD_SX1262           | -                                | -                                                   | -            | -                  | VDD_SX1262: RM1262:<br>Lora Radio only. 3.3V<br>minimum to achieve<br>22dBm.<br>VDD_SX1262: NC on<br>RM1261.<br>MUST connect to same<br>external supply as<br>VDD_RADIO, VMCU,<br>VDD_IO. |

| 37   | PA01                 | SWCLK                            | I2C0/AN/FREQ/PWM/<br>EUART0/USART0/USART1/SWCLK/PDM | 22           | PA01               | -                                                                                                                                                                                         |

| 38   | PA02                 | SWDIO                            | I2C0/AN/FREQ/PWM/<br>EUART0/USART1/SWDIO/PDM        | 23           | PA02               | -                                                                                                                                                                                         |

| 39   | PA03                 | SWO                              | I2C0/AN/FREQ/PWM/<br>EUART0/USART0/USART1/SWO/PDM   | 24           | PA03               | -                                                                                                                                                                                         |

| 40   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 41   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 42   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 43   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 44   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 45   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 46   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

| 47   | GND                  | -                                | -                                                   | -            | -                  | -                                                                                                                                                                                         |

|      |                      |                                  |                                                     |              |                    |                                                                                                                                                                                           |

Americas: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852-2762-4823

**Note 1:** Apart from EUART, BOOT, when using AT firmware, most of the SIO GPIO pins are input and EFR32BG22 pin configuration "DISABLED" by default. "DISABLED" disables the pin, reducing the power consumption to a minimum. When the input drivers are disabled, the pin can be used as connection for an analog module.

Avoid floating inputs, which can also cause current consumption in low power mode (e.g. Sleep) to drift with time.

When using AT firmware, BOOT pin is default high (internally).

When using AT firmware, EUART, has below IO direction and state:

- EUART TX, PC07 is an output, set high (in AT firmware).

- EUART RTS, PB02 is an output, set low (in AT firmware).

- EUART RX, PB03 is an input, set with internal pull-up (in AT firmware).

- EUART\_CTS, PB04 is an input, set with internal pull-down (in AT firmware).

For Native C development, to learn which GPIO ports provide access to every peripheral, consult Analog Peripheral Connectivity and Digital Peripheral Connectivity in the EFR32BG22 datasheet.

- Note 2: All pins (SIO, AN, EUART, SWD) I/O voltage tracks VDD.

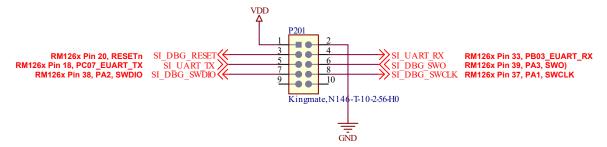

- Note 3: 2-pin Serial Wire Debug (SWD) Programming/Debug Interface, pin38 (PA02, SWDIO) and pin37 (PA01, SWDCLK) used for upgrading firmware with Silabs Simplicity Studio SWD programmer via the Mini Simplicity connector. Using this 2-pin Serial Wire SWD Programming/Debug Interface requires on customers host PCB a header connector, refer to Two-pin Serial-Wire Debug (SWD) Programming/Debug Interface for details of connector and wiring.

- Note 4: Pull the RESETn pin (pin 20) low for minimum 100 ns to reset the module. RESETn pin has a pull-up internally (to an internal 1.8V). RESETn pin should not exceed 1.8V.

- Note 5: When I2C interface is selected, pull-up resistors on I2C SDA and I2C SCL MUST be connected externally as per I2C standard.

- Note 6: EFR32 Soc GPIO (PB01) control of RF switch (ANT\_SW).

| Mode (SX1261 or SX1262 radio) | EFR32 series SoC GPIO PB01 state driving RF switch (ANT_SW) pin.   |  |  |  |

|-------------------------------|--------------------------------------------------------------------|--|--|--|

|                               | PB01 is configured as Push Pull output.                            |  |  |  |

|                               | PB01 initialised to output low to put RF switch in disabled state. |  |  |  |

| RF transmit                   | Output High                                                        |  |  |  |

| RF receive                    | Output High                                                        |  |  |  |

| Standby                       | Output High                                                        |  |  |  |

| Sleep                         | Output Low                                                         |  |  |  |

|                               |                                                                    |  |  |  |

## 3.3 Electrical Specifications

#### 3.3.1 Absolute Maximum Ratings

Absolute maximum ratings for supply voltage and voltages on digital and analogue pins of the module are listed below. Exceeding these values causes permanent damage (Table 3).

Table 3: Maximum Current Ratings

| Parameter                                 | Minimum | Maximum      | Unit   |

|-------------------------------------------|---------|--------------|--------|

| Voltage at VDD_RADIO                      | -0.5    | 3.9          | V      |

| Voltage at VDD_SX1262                     | -0.5    | 3.9 (Note 1) | V      |

| Voltage at VDD_VMCU                       | -0.3    | 3.8          |        |

| Voltage at VDD_IO                         | -0.3    | 3.8          | V      |

| Voltage ramp rate on any supply pin       |         | 1.0          | V / us |

| Voltage at GND pin                        |         | 0            | V      |

| DC voltage on any GPIO pin                | -0.3    | VDD_IO+0.3   | V      |

| DC voltage in RESETn pin                  | -0.3    | 3.8(Note 2)  | V      |

| Total current into VDD_VMCU               |         | 200          | mA     |

| Current per I/O pin (sink or source)      |         | 50           | mA     |

| Current for all I/O pins (sink or source) |         | 200          | mA     |

| RF Input level                            |         | 10           | dBm    |

| Storage temperature                       | -40     | +85          | °C     |

| Moisture Sensitivity Level (MSL)          |         | MSL4         |        |

| ESD (as per EN301-489)                    |         |              |        |

| Conductive coupling                       |         | 4            | kV     |

| Air coupling                              |         | 8            | kV     |

Note 1: VDD\_SX1262 pin is only for RM1262. VDD\_SX1262 pin on RM1261 is no connect or can be connected (as it is not used in the RM1261 module).

Note 2: RESETn pin has a pull-up internally (to an internal 1.8V). For minimum leakage, RESETn should not exceed 1.8V.

#### 3.3.2 Recommended Operating Parameters

Table 4: Power Supply Operating Parameters

| Parameter                                                                                              | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Voltage at supply pins VDD_RADIO, VDD_VMCU, VDD_IO, VDD_SX1262 (Note 1).                               | 2.0 | 3.3 | 3.7 | V    |

| (With DCDC in EFR32 in regulation with EFR32 Iload=5mA limit, (Note 2).                                |     |     |     |      |

| Voltage at supply pins VDD_RADIO, VDD_VMCU, VDD_IO, VDD_SX1262(NOTE1). (With DCDC in EFR32 in bypass). | 2.0 | 3.3 | 3.7 | V    |

| VCC Maximum ripple or noise (Note 3)                                                                   |     |     | TBD | mV   |

| Operating Temperature Range                                                                            | -40 | -   | +85 | °C   |

| RF input power                                                                                         |     |     | 0   | dBm  |

| Parameter                               | Min | Тур                                       | Max | Unit |

|-----------------------------------------|-----|-------------------------------------------|-----|------|

| Maximum allowed RF TX power per country |     | As per radio certifications (Section 5.4) |     | dBm  |

Note 1: VDD\_SX1262 pin is only for RM1262: To achieve RM1262 full RF TX power of 22dBm, requires minimum 3.3V on pin VDD SX1262. Other VDD pins MUST be at same voltage as that on VDD SX1262 pin.

VDD\_SX1262 pin on RM1261: is no connect on the RM1261 or can be connected (as it is not used in the RM1261 module). Other VDD pins MUST be at same voltage.

**Note 2:** EFR32 DCDC in regulation (in AT Firmware) and with EFR32 Iload=5mA limit. If Iload more than 5mA, the supply voltage minimum needs to be 2.2V.

Note 3: The maximum VDD ripple or noise (at any frequency) that does not disturb the radio.

Table 5: Signal Levels for GPIO (SIO) Interface and RESETn

| Parameter                                                    | Minimum  | Typical | Maximum | Unit |

|--------------------------------------------------------------|----------|---------|---------|------|

| Input high voltage (any GPIO), V <sub>IH</sub>               | 0.7*VDD  | -       | VDD     | V    |

| Input high voltage (RESETn), V <sub>IH</sub> (Note1)         | 0.7*1.8V | -       | 1.8     | V    |

| Input low voltage (any GPIO), V <sub>IL</sub>                | -        | -       | 0.3VDD  | V    |

| Input low voltage (RESETn), V <sub>IL</sub> (Note1)          | -        | -       | 1.8     | V    |

| Hysteresis of input voltage (any GPIO), V <sub>HYS</sub>     | 0.05*VDD | -       | -       |      |

| Hysteresis of input voltage (RESETn), V <sub>HYS</sub>       | 0.05*1.8 | -       | -       |      |

| Output high voltage, V <sub>OH</sub>                         |          | -       |         |      |

| source 20mA, VDD=3.0V                                        | 0.8*VDD  |         | -       | V    |

| source 8mA, VDD=2.0V                                         | 0.6*VDD  |         | -       | V    |

| Output low voltage, VoL                                      |          |         |         |      |

| source 20mA, VDD=3.0V                                        | -        | -       | 0.2*VDD | V    |

| source 8mA, VDD=2.0V                                         | -        | -       | 0.4*VDD | V    |

| GPIO rise time, T <sub>GPIO_RISE</sub>                       |          |         |         |      |

| VDD=3.0V, C <sub>LOAD</sub> =50pF, SLEWRATE=4, 10% to 90%    | -        | 8.4     | -       | ns   |

| VDD=2.0V, C <sub>LOAD</sub> =50pF, SLEWRATE=4, 10% to 90%    | -        | 13      | -       | ns   |

| GPIO fall time, TGPIO_FALL                                   |          |         |         |      |

| VDD=3.0V, C <sub>LOAD</sub> =50pF, SLEWRATE=4, 90% to 10%    | -        | 7.1     | -       | ns   |

| VDD=2.0V, C <sub>LOAD</sub> =50pF, SLEWRATE=4, 90% to 10%    | -        | 11.9    | -       | ns   |

| Pull up/ down resistance, V <sub>PULL</sub>                  |          |         |         |      |

| (Any GPIO pin. Pull-up to IOVDD: MODEn = DISABLE             | 35       | 44      | 55      | kΩ   |

| DOUT=1. Pull-down to VSS: MODEn = WIREDORPULLDOWN DOUT = 0). |          |         |         |      |

| Pull up/ down resistance, V <sub>PULL</sub>                  |          |         |         |      |

| (RESETn pin. Pull-up to 1.8V) (Note 2)                       | 35       | 44      | 55      | kΩ   |

|                                                              | 33       | 77      | 33      |      |

| Maximum filtered gltch width, V <sub>GF</sub>                |          | 27      |         | ns   |

| (MODE = INPUT, DOUT = 1)                                     | -        | 21      | -       |      |

| RESETn low time to ensure pin reset, TRESET                  | 100      | -       | -       | ns   |

Note 1: GPIO input thresholds are proportional to VDD pin. RESETn input threshold proportional to internal 1.8V.

Note 2: GPIO pull-ups connect to VDD supply, pull-downs connect to VSS. RESETn pull-ups connect to internal 1.8V.

Table 6: SIO pin alternative function AIN (ADC) specification

| Tuble of old pill alternative function Airt (ABO) openiousion |         |         |         |      |  |  |  |  |  |

|---------------------------------------------------------------|---------|---------|---------|------|--|--|--|--|--|

| Parameter                                                     | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| Main analog supply, V <sub>IN_MAX</sub> (Note 1)                                         | 2                  |                        | VDD              | V    |

|------------------------------------------------------------------------------------------|--------------------|------------------------|------------------|------|

| Full-Scale Voltage, V <sub>FS</sub>                                                      | -                  | V <sub>REF</sub> /Gain | -                | -    |

| Input Measurement Range                                                                  |                    |                        |                  |      |

| Differential Mode - Plus and Minus inputs                                                | -V <sub>FS</sub> - | -                      | +V <sub>FS</sub> | V    |

| Single Ended Mode - One input tied to ground                                             | 0                  | -                      | $V_{FS}$         |      |

| Input Sampling Capacitance, Cs                                                           |                    |                        |                  |      |

| Analog Gain =1x                                                                          | -                  | 1.8                    | -                | pF   |

| Analog Gain =2x                                                                          | -                  | 3.6                    | -                | pF   |

| Analog Gain =4x                                                                          | -                  | 7.2                    | -                | pF   |

| Analog Gain =0.5x                                                                        | -                  | 0.9                    | -                | pF   |

| ADC clock frequency, fclk                                                                | -                  | -                      | 10               | MHz  |

| Current from supply continuous operation, I <sub>ADC_CONT</sub>                          |                    |                        |                  |      |

| Normal Mode, 1 Msps, OSR=2, fCLK =10 MHz                                                 | -                  | 290                    | 385              | uA   |

| Current in Standby mode. ADC is not functional but can wake up in 1us, I <sub>STBY</sub> |                    |                        |                  |      |

| Normal Mode                                                                              | -                  | 16                     | -                | uA   |

| ADC Startup Time, T <sub>startup</sub>                                                   |                    |                        |                  |      |

| From power down state                                                                    | -                  | 5                      | -                | us   |

| From Standby state                                                                       | -                  | 1                      | -                | us   |

| ADC Resolution                                                                           | -                  | 12                     | -                | bits |

| External reference voltage range, V <sub>EVREF</sub>                                     | 2                  | -                      | VDD              | V    |

| Internal reference voltage range, VIREF                                                  | -                  | 1.21                   | -                | V    |

## 3.3.3 BOOT pin (for AT firmware)

For RM126x loaded with AT firmware, the BOOT pin is used to determine when execution of the bootloader is required. Upon reset, execution of the bootloader begins. The state of the BOOT pin is read immediately upon start-up of the bootloader. If LOW, execution of the bootloader continues, facilitating firmware update via the EUART. If the BOOT pin is HIGH, the bootloader will stop execution and pass control to the main application firmware.

Table 7: BOOT pin

| Signal Name | Pin# | I/O | Comments                                                  |

|-------------|------|-----|-----------------------------------------------------------|

| PC06/BOOT   | 19   | 1   | Input with active low logic.                              |

|             |      |     | Operating mode selected by BOOT pin status (at power up): |

|             |      |     | If externally held Low (0V), enters BOOT mode;            |

|             |      |     | If High (VDD), enter application (default).               |

### 3.3.4 LoRa Power Consumption

VDD 3.3V with both DCDC on (in SX126x and EFR32) and 25°C, see Table 8).

Table 8: Power consumption

| Parameter                             | Min | Typical |      |      |     | Max   | Unit |  |     |

|---------------------------------------|-----|---------|------|------|-----|-------|------|--|-----|

|                                       |     | 928     | 915  | 902  | 870 | 868   | 863  |  | MHz |

| RM1262:                               |     |         |      |      |     |       |      |  |     |

| RM1262 RF TX power at setting @22dBm  |     | 20.7    | 21.1 | 21.4 |     | Note2 |      |  | dBm |

| RM1262 Peak current at setting @22dBm |     | 106     | 109  | 111  |     | Note2 |      |  | mA  |

| RM1262 RF TX power at setting @14dBm  |     |         |      |      |     | Note2 |      |  | dBm |

| RM1262 Peak current at setting @14dBm |     |         |      |      |     | Note2 |      |  | mA  |

| Parameter                                | Min | Typical |      |      |      | Max  | Unit |  |     |

|------------------------------------------|-----|---------|------|------|------|------|------|--|-----|

|                                          |     | 928     | 915  | 902  | 870  | 868  | 863  |  | MHz |

| RM1261:                                  |     |         |      |      |      |      |      |  |     |

| RM1261 RF TX power at setting @15dBm     |     |         |      |      |      |      |      |  | dBm |

| RM1261 Peak current at setting @15dBm    |     |         |      |      |      |      |      |  | mA  |

| RM1261 RF TX power at setting @14dBm     |     | 13.7    | 13.8 | 13.9 | 13.9 | 14.0 | 14.0 |  | dBm |

| RM1261 Peak current at setting @14dBm    |     | 28.3    | 28.8 | 29.0 | 29.4 | 29.5 | 29.5 |  | mA  |

| RM1261 RF TX power at setting @13dBm     |     |         |      |      |      |      |      |  | dBm |

| RM1261 Peak current at setting @13dBm    |     |         |      |      |      |      |      |  | mA  |

| RM1261 RF TX power at setting @12dBm     |     |         |      |      |      |      |      |  | dBm |

| RM1261 Peak TX current at setting @12dBm |     |         |      |      |      |      |      |  | mA  |

| RM1261 AND RM1262:                                                                                                                 | Min | Typical | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| Peak current, RF RX Mode                                                                                                           |     |         |     |      |

| RX boosted, FSK, includes, EFR32 (peripherals disabled) current.                                                                   |     | 7.6     |     | mA   |

| RX boosted, LoRa, includes, EFR32 (peripherals disabled) current.                                                                  |     | 8.1     |     | mA   |

| Sleep (Note 2)                                                                                                                     |     |         |     |      |

| RM1262/ RM1261 Sleep: 2.6uA (EM2, Full RAM retention, RTC(LXFO))                                                                   |     | 2.6     |     | uA   |

| RM1262/ RM1261 Sleep: 2.2uA (EM3, Full RAM retention, RTC(ULFRCO))                                                                 |     | 2.2     |     | uA   |

| RM1262/ RM1261 Sleep: 2.1uA (EM2, Full RAM retention, RTC(LFXO), no SoC Radio RAM retention, BURTC enabled) - used in AT firmware. |     | 2.1     |     | uA   |

- Note 1: Peak currents measured with RM126x radio test firmware, EUART open. Receive "RX Boosted" refers to SX126x radio which can operate in RX boosted gain setup or in RX power saving gain setup. In RX power saving gain, the radio will consume less power at small cost in RX sensitivity. In RX Boosted gain, the radio will consume more power to improve the RX sensitivity (this is preferred and default).

- **Note2:** RM1262 HW RF tuned and capable of operating in both 902-928MHz, 863-870MHz, but RM1262 not certified for the 863-870MHz band and certified for 902-928MHz band countries (USA, Canada, Australia, New Zealand).

RM1261 HW RF tuned and capable of operating in both 902-928MHz, 863-870MHz, but RM1261 is certified for both 902-928MHz (Taiwan, Japan) and 863-870MHz band (India, CE, UKCA) countries.

- Note 3: Sleep mode current assumes SX126x in SLEEP mode with warm start, config retained.

- **Note 4:** For asynchronous interface like the EUART (asynchronous as the other end can communicate at any time), the EUART (on RM126x) must kept resulting in the base current consumption.

For synchronous interface like the I2C or SPI (when RM126x side is the master), the interface can be closed and opened only when needed resulting in current saving (no base current consumption penalty). There's a similar argument for ADC (open ADC when needed).

## 3.4 RF Specifications

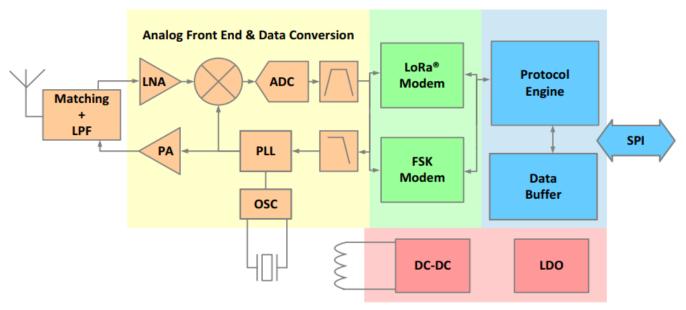

Figure 3: SX126X Block Diagram (from SX1261/SX1262 Datasheet)

The RM126x (RM1261 / RM1262) module uses SX1261 /SX1262 LoRa transceivers capable of low power operation in the case of RM126x operated in 863-870 and 902-928MHz frequency bands. The radio comprises four main blocks:-

- RF front end: RF transmit and receive chains (including channel filters) interface to digital blocks. The last stage of transmit chain is different between SX1261 and SX1262. The (RM1261) SX1261 transceiver capable of outputting 14/15dBm maximum RF TX output power under DCDC convertor or LDO supply. The (RM1262) SX1262 transceiver capable of RF TX power of 22dBm under external supply (3.3V minimum to get 22dBm). The rest of the SX1262 powered by DCDC or LDO.

- Digital Modem: A range of modulations are available but the RM126x is designed and certified for:

- LoRa 125kHz

- LoRa 250kHz

- LoRa 500kHz

- FSK 50kbps

- LR-FHSS (Long Range FHSS) Transmit mode not currently certified for the RM126x

as per the LoRaWAN RP002-1.0.3 LoRaWAN Regional Parameters specification and per countries radio regulatory certified.

- Digital Interface and Control: this comprises all payload data and protocol processing as well as access to configuration of the radio via the SPI interface.

- Power Distribution: two forms of voltage regulation, DC-DC or linear regulator LDO, are available depending upon the design priorities of the application.

## 3.4.1 LoRa / FSK RF Transmit Power

Table 9: LoRa / FSK RF Transmit Power

| Part   | Maximum RF TX power<br>conducted at MHF4 RF<br>connector<br>Typical | Conditions<br>All VDD pins           | Comment                                                    |

|--------|---------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------|

| RM1261 | 14/15dBm                                                            | 2V to 3.6V                           | RF Transmit programmable 14dBm down to -17dBm in 1dB step. |

| RM1262 | 22dBm                                                               | 3.3V to 3.6V. (3.3V min. for 22dBm). | RF Transmit programmable 22dBm down                        |

|        | 22dBm – 2dB                                                         | 2.7V                                 | to -9dBm in 1dB step.                                      |

|        | 22dBm – 3dB                                                         | 2.4V                                 | _                                                          |

|        | 22dBm – 6dB                                                         | 2.0V                                 |                                                            |

The actual maximum RF TX power achieved per country radio regulatory certification are shown in Mandatory FW Requirements Related to Hardware.

• **SX126x Errata:** In AT firmware, all errata workarounds are implemented as per the **SX1261/SX1262 Datasheet**. For example, "Better Resistance of the SX1262 TX to Antenna Mismatch," if not patched, would result in 5dB to 6dB lower RF TX power due to antenna mismatch.

#### 3.4.2 External antenna

The RM1261 supports a range of external antennas with up to peak antenna gain of 2.0dBi (863-879MHz). The RM1262 supports range of external antennas with up to peak antenna gain of 2.2dBi (902-928MHz). For more information, see 6.4 LoRa External Antenna Integration with RM126x.

#### 3.4.3 32MHz TCXO LoRa SX126x radio clock

The LoRaWAN radio (SX1261 / SX1261) uses very accurate 32MHz TCXO (±1ppm at 25°C) which additionally reduces the frequency drift within a LoRa packet (longest LoRa packet is 2793.5ms) due to the temperature rise due to the RF power amplifier.

#### 3.4.4 LoRa / FSK RF Receive Sensitivity vs Data Rate

Table 10 tabulates typical LoRaWAN RF receive sensitivity as a function of the LoRa data rate. The data rate is determined by the combination of bandwidth and spreading factor of the incoming LoRa signal. The data rates in the table are the LoRaWAN data rates used by the gateway when transmitting to the end device.

Table 10: Receive sensitivity vs LoRa or FSK data rate

|         | DR | Bit Rate [Bits/s] | BW [kHz] | SF | Conducted Rx Sensitivity [dBm] |

|---------|----|-------------------|----------|----|--------------------------------|

| RM126x1 | 8  | 980               | 500      | 12 | -130.8                         |

|         | 13 | 21900             | 500      | 7  | TBD                            |

|         | 0  | 250               | 125      | 12 | -139.2                         |

|         | 5  | 5470              | 125      | 7  | -125.6                         |

|         | 6  | 11000             | 250      | 7  | -122.7                         |

|         | 7  | 50000             | FSK      | -  | -109.0                         |

#### Note the following:

- DR = LoRaWAN data rate

- Bit rate is the effective over the air bit rate

- BW is the bandwidth of the incoming LoRa transmission

- SF is the Spreading Factor of the incoming LoRa transmission

## 4 EFR32 SoC PERIPHERALS

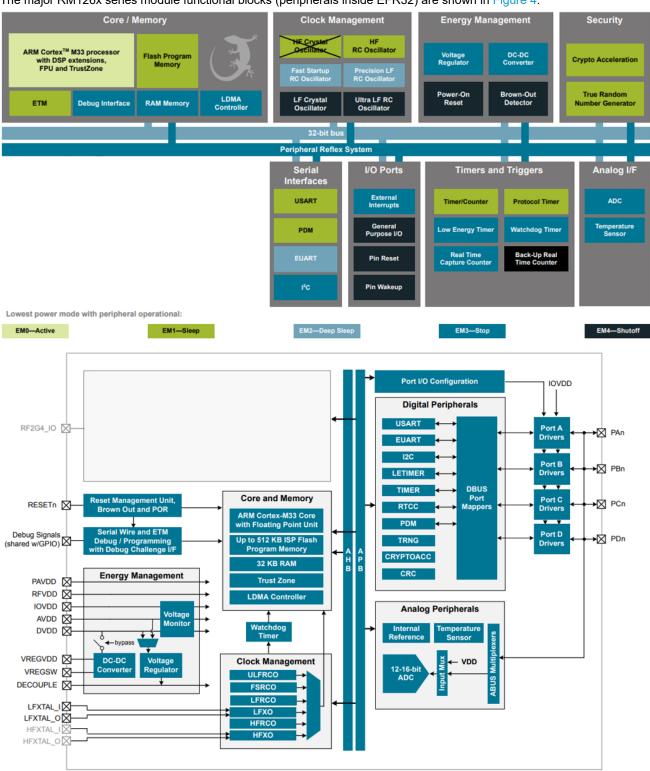

The major RM126x series module functional blocks (peripherals inside EFR32) are shown in Figure 4.

Figure 4: EFR32BG22 SoC peripherals and block diagram (from EFR32 datasheet)

The available SoC peripherals include:

- ADC: 12-bit@1 Msps, 16-bit@76.9 ksps

- TBD x GPIO with output state retention and asynchronous interrupts

- 4 x 16-bit Timers/Counters with 3 compare/capture/PWM

- 1 x 32-bit Timers/Counters with 3 compare/capture/PWM

- 24-bit Low Energy Timer for waveform generation

- 32-bit Real Time Counter

- 2 x USART (UART/SPI/SmartCards(ISO7816)/IrDA/I2S)

- 1 x EUART (UART/IrDA)

- 2 x I2C peripheral interface with SMBus support

- Digital microphone interface (PDM)

- Die temperature sensor with ±1.5°C accuracy after single-point calibration

- 12 Channel Peripheral Reflex System

For details on their electrical performance, consult the relevant portions of Section 4 in the EFR32BG22 datasheet.

To learn which GPIO ports provide access to every peripheral, consult Analog Peripheral Connectivity and Digital Peripheral Connectivity in the EFR32BG22 datasheet.

## 4.1 Power Management (includes brown-out and power on reset)

#### Flexible Energy Management System:

- Five energy modules from EM0 to EM4 provide flexibility between higher performance and low power System Sleep /Deep Sleep modes

- Power DCDC or DCDC bypass control

- Voltage monitoring and brow out detection (Brownout Reset)

- Automatic voltage scaling for additional energy savings

- State retention

- Open/Close peripherals (UART, SPI, I2C, SIO's/GPIO's and ADC). Peripherals consume current when open; each

peripheral can be individually closed to save power consumption.

- Pin wake-up system from deep sleep

- Ultra efficient Power-on Reset (POR) and Brown-Out Detector (BOD).

- 2V to 3.65V supply range.

#### 4.2 Clocks

#### 4.2.1 76.8MHz HFRCO EFR32 SoC high frequency RC oscillator clock

The EFR32 SoC integrated high speed RC oscillator (HFRCO) is used for the RM126x module. The HFRCO employs fast startup at minimal energy consumption combined with wide frequency range from 1MHz to 76.8MHz.

#### 4.2.2 32.768kHz LFXO EFR32 SoC low frequency crystal oscillator clock

The EFR32 SoC uses a high accuracy LXFO (+/-20 ppm at 25°C) 7pF load capacitor 32.768 kHz crystal (tuning fork) oscillator circuit. It provides an accurate protocol timing and helps with radio power consumption in the system sleep mode. The EFR32 LXFO block provides the load capacitance (EFR32 CAPTUNE) for the 32.768 kHz crystal (which is 7pF load capacitance tuning fork) to create the oscillator circuit. The RM126x optimised value (to account for PCB parasitics) for CAPTUNE is 19.08pF, which is equal to 32.668kHz crystal seeing 9.54pF (C<sub>LXFO</sub>=CAPTUNE/2).

The EFR32 SoC LFRCO 32.768kHz RC oscillator is not used by the RM126x module as it has lower accuracy of ±500 ppm.

Americas: +1-800-492-2320

Europe: +44-1628-858-940

Hong Kong: +852-2762-4823

## 4.3 General Purpose I/O, ADC and PWM/FREQ

#### 4.3.1 GPIO

All SIO pins are configurable and can be accessed individually. Each has the following user configured features:

- Input/output direction (or tristate [reset state])

- More advanced configurations including open-drain and glitch-filtering can be configured for each individual GPIO pin

- All of the pins on ports A and port B are EM2 capable. These pins may be used by Low-Energy peripherals in EM2/3 and may also be used as EM2/3 pin wake-ups. Pins on ports C and D are latched/retained in their current state when entering EM2 until EM2 exit upon which internal peripherals could once again drive those pads.

- A few GPIOs also have EM4 wake functionality/EM4 IO retention (output enable, output value, pull enable, pull direction)

| GPIO |                        | Alternative Function |                  |

|------|------------------------|----------------------|------------------|

| PC00 | GPIO.EM4WU6            | GPIO.THMSW_EN        |                  |

| PC05 | GPIO.EM4WU7            |                      |                  |

| PC07 | GPIO.EM4WU8            |                      |                  |

| PB03 | GPIO.EM4WU4            |                      |                  |

| PA01 | GPIO.SWCLK             |                      |                  |

| PA02 | GPIO.SWDIO             |                      |                  |

| PA03 | GPIO.SWV (this is SWO) | GPIO.TDO             | GPIO.TRACEDA-TA0 |

| PD02 | GPIO.EM4WU9            |                      |                  |

- Output drive strength (8mA)

- Internal pull-up and pull-down resistors (44kOhms typical) or no pull-up/down

- All GPIO pins are selectable as interrupts in EM0 and EM1

- All PA and PB GPIO pins are also selectable as interrupts down to EM2 and EM3

- All EM4 wake-up pins are also available as interrupts in EM0/1/2/3

## 4.3.2 Timer / Counter and PWM

The TIMER (Timer/Counter) is not configurable with AT.

The TIMER (Timer/Counter) keeps track of timing and counts events, generates output waveforms, and triggers timed actions in other peripherals.

The core of each TIMER is a 16-bit or 32-bit counter with up to 3 compare/capture channels. Each channel is configurable in one of three modes:

- Capture mode: The counter state is stored in a buffer at a selected input event.

- Compare mode: The channel output reflects the comparison of the counter to a programmed threshold value.

- PWM mode: The TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers. In addition, some timers offer dead-time insertion for motor control applications.

Refer to the EFR32BG22 datasheet to determine the capabilities (capture/compare channel count, width, and DTI) of each timer instance.

Refer to the EFR32BG22 datasheet also for Low Energy Timer (LETIMER), Real Time Clock with Capture (RTCC), Back-up Real Time Counter (BURTC), Watchdog Timer (WDOG).

## 4.4 Communications and other Digital peripherals

#### 4.4.1 EUART Interface

The Enhanced Universal Asynchronous Receiver/Transmitter supports full duplex asynchronous UART communication with hardware flow control, RS-485 and IrDA support. In EM0 and EM1 the EUART provides a high-speed, buffered communication interface.

Two-way hardware flow control is implemented by EUART\_RTS and EUART\_CTS. EUART\_RTS is an output and EUART\_CTS is an input. Both are active low.

These signals operate according to normal industry convention. EUART\_RX, EUART\_TX, EUART\_CTS, EUART\_RTS are all CMOS logic levels that track VDD. For example, when RX and TX are idle they sit at a high logic level (VDD). Conversely for handshaking pins CTS, RTS at 0 V is treated as an assertion.

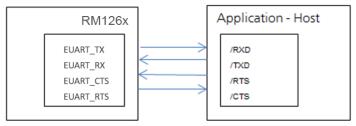

The module communicates with the customer application using the following signals (Figure 5):