December 2004

### **RMPA2265**

# Dual Band WCDMA Power Amplifier Module 1850 to 1910 MHz and 1920 to 1980 MHz

### **General Description**

The RMPA2265 power amplifier module (PAM) is designed for WCDMA applications in both the 1850–1910 and 1920–1980 MHz bands. The 2 stage PAM is internally matched to  $50\Omega$  to minimize the use of external components and features a low-power mode to reduce standby current and DC power consumption during peak phone usage. High power-added efficiency and excellent linearity are achieved using Fairchild's InGaP/GaAs Heterojunction Bipolar Transistor (HBT) process.

#### **Features**

- Single positive-supply operation and low power and shutdown modes

- 42% WCDMA efficiency at +28 dBm average output power 1920–1980 MHz

- 39% WCDMA efficiency at 27.5 dBm average output power 1850–1910 MHz

- Meets UMTS/WCDMA performance requirements in both UMTS bands

- Compact, low-profile package—(3.0 x 3.0 x 1.0 mm nominal)

- Internally matched to  $50\Omega$  and DC blocked RF input/ output

### **Device (3 x 3 x 1mm)**

### **Functional Block Diagram**

### (Top View) **PA MODULE MMIC** Vcc1 Vcc2 Output Input **RF OUT RF IN** 7 2 Match Match Vmode **GND** 3 6 DC Bias Control **GND** Vref 5 (paddle ground on package bottom)

## Absolute Ratings<sup>1</sup>

| Symbol                              | Parameter             | Ratings     | Units |

|-------------------------------------|-----------------------|-------------|-------|

| V <sub>CC1</sub> , V <sub>CC2</sub> | Supply Voltages       | 5.0         | V     |

| V <sub>REF</sub>                    | Reference Voltage     | 2.6 to 3.5  | V     |

| V <sub>MODE</sub>                   | Power Control Voltage | 3.5         | V     |

| P <sub>IN</sub>                     | RF Input Power        | +10         | dBm   |

| T <sub>STG</sub>                    | Storage Temperature   | -55 to +150 | °C    |

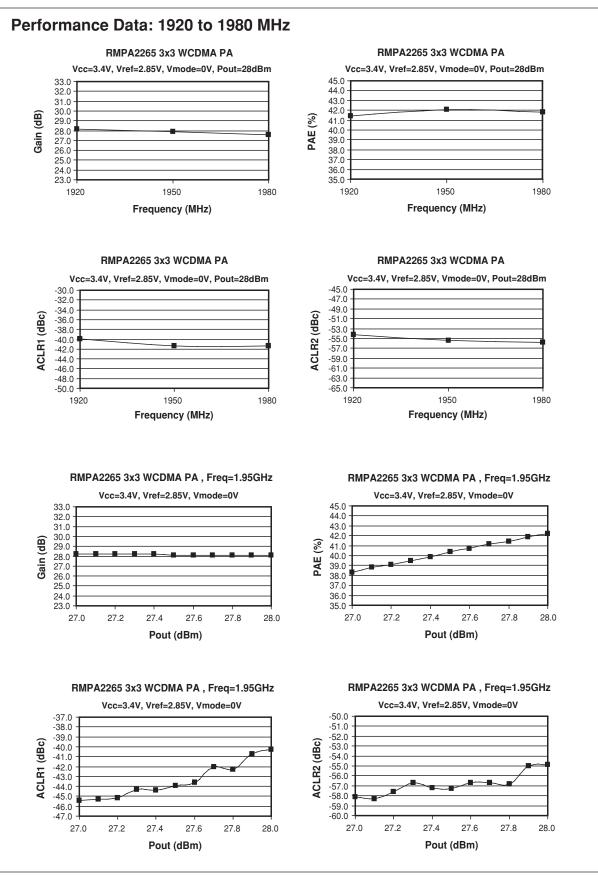

## Electrical Characteristics (1920 to 1980 MHz)<sup>1</sup>

| Symbol     | Parameter                                     | Comments                      | Min  | Тур   | Max  | Units  |

|------------|-----------------------------------------------|-------------------------------|------|-------|------|--------|

| f          | Operating Frequency                           |                               | 1920 |       | 1980 | MHz    |

| WCDMA Op   | peration                                      |                               |      |       |      | '      |

| Gp         | Power Gain                                    | Po = +28dBm, Vmode = 0V       | 26   | 28    |      | dB     |

|            |                                               | Po = +16dBm, Vmode ≥ 2.0V     |      | 26    |      | dB     |

| Po         | Linear Output Power                           | Vmode = 0V                    | 28   |       |      | dBm    |

|            |                                               | Vmode ≥ 2.0V                  | 16   |       |      | dBm    |

| PAEd       | PAEd (digital) @ +28dBm                       | Vmode = 0V                    |      | 42    |      | %      |

|            | PAEd (digital) @ +16dBm                       | Vmode ≥ 2.0V                  |      | 9     |      | %      |

|            | PAEd (digital) @ +16dBm                       | Vmode ≥ 2.0V, Vcc = 1.4V      |      | 25    |      | %      |

| Itot       | High Power Total Current                      | Po = +28dBm, Vmode = 0V       |      | 440   |      | mA     |

|            | Low Power Total Current                       | Po = +16dBm, Vmode = 2.0V     |      | 120   |      | mA     |

|            | Adjacent Channel Leakage<br>Ratio             |                               |      |       |      |        |

| ACLR1      | ±5.00MHz Offset<br>1920–1980 MHz              | Po = +28dBm, Vmode = 0V       |      | -40   |      | dBc    |

|            |                                               | Po = +16dBm, Vmode ≥ 2.0V     |      | -42   |      | dBc    |

| ACLR2      | ±10.00MHz Offset<br>1920–1980 MHz             | Po = +28dBm, Vmode = 0V       |      | -54   |      | dBc    |

|            |                                               | Po = +16dBm, Vmode ≥ 2.0V     |      | -66   |      | dBc    |

| General Ch | aracteristics                                 | -                             | _    |       |      |        |

| VSWR       | Input Impedance                               |                               |      | 2.0:1 |      |        |

| NF         | Noise Figure                                  |                               |      | 4     |      | dB     |

| Rx No      | Receive Band Noise Power                      | Po ≤ +28dBm, 2110 to 2170 MHz |      | -139  |      | dBm/Hz |

| 2fo - 5fo  | Harmonic Suppression                          | Po ≤ +28dBm                   |      |       | -50  | dBc    |

| S          | Spurious Outputs <sup>2, 3</sup>              | Load VSWR ≤ 5.0:1             |      |       | -60  | dBc    |

|            | Ruggedness with Load<br>Mismatch <sup>3</sup> | No permanent damage           |      |       | 10:1 |        |

| Tc         | Case Operating Temperature                    |                               | -30  |       | 85   | °C     |

| DC Charact | eristics                                      | •                             | •    | •     |      | •      |

| Iccq       | Quiescent Current                             | Vmode ≥ 2.0V                  |      | 50    |      | mA     |

| Iref       | Reference Current                             | Po ≤ +28dBm                   |      | 5     |      | mA     |

| lcc(off)   | Shutdown Leakage Current                      | No applied RF signal          |      | 1     | 5    | μA     |

- **Notes:**1: All parameters met at  $T_C = +25^{\circ}C$ ,  $V_{CC} = +3.4V$ ,  $V_{REF} = 2.85V$  and load VSWR  $\leq$  1.2:1, unless otherwise noted.

2: All phase angles

3: Guaranteed by design

Note:

1: No permanent damage with only one parameter set at extreme limit. Other parameters set to typical values.

| Symbol    | Parameter                                     | Comments                        | Min  | Тур   | Max  | Units  |

|-----------|-----------------------------------------------|---------------------------------|------|-------|------|--------|

| f         | Operating Frequency                           |                                 | 1850 |       | 1910 | MHz    |

| VCDMA Op  | eration                                       |                                 |      |       |      |        |

| Gp        | Power Gain                                    | Po = +27.5dBm, Vmode = 0V       | 26   | 28    |      | dB     |

|           |                                               | Po = +16dBm, Vmode ≥ 2.0V       |      | 26    |      | dB     |

| Po        | Linear Output Power                           | Vmode = 0V                      | 27.5 |       |      | dBm    |

|           |                                               | Vmode ≥ 2.0V                    | 16   |       |      | dBm    |

| PAEd      | PAEd (digital) @ +27.5dBm                     | Vmode = 0V                      |      | 39    |      | %      |

|           | PAEd (digital) @ +16dBm                       | Vmode ≥ 2.0V                    |      | 9     |      | %      |

|           | PAEd (digital) @ +16dBm                       | Vmode ≥ 2.0V, Vcc = 1.4V        |      | 25    |      | %      |

| Itot      | High Power Total Current                      | Po = +27.5dBm, Vmode = 0V       |      | 420   |      | mA     |

|           | Low Power Total Current                       | Po = +16dBm, Vmode = 2.0V       |      | 120   |      | mA     |

|           | Adjacent Channel Leakage<br>Ratio             |                                 |      |       |      |        |

| ACLR1     | ±5.00MHz Offset                               | Po = +27.5dBm, Vmode = 0V       |      | -40   |      | dBc    |

|           | 1850–1910 MHz                                 | Po = +16dBm, Vmode ≥ 2.0V       |      | -42   |      | dBc    |

| ACLR2     | ±10.00MHz Offset                              | Po = +27.5dBm, Vmode = 0V       |      | -54   |      | dBc    |

|           | 1850–1910 MHz                                 | Po = +16dBm, Vmode ≥ 2.0V       |      | -66   |      | dBc    |

| eneral Ch | aracteristics                                 |                                 | •    | •     |      | •      |

| VSWR      | Input Impedance                               |                                 |      | 2.0:1 |      |        |

| NF        | Noise Figure                                  |                                 |      | 4     |      | dB     |

| Rx No     | Receive Band Noise Power                      | Po ≤ +27.5dBm, 2110 to 2170 MHz |      | -139  |      | dBm/Hz |

| 2fo – 5fo | Harmonic Suppression                          | Po ≤ +27.5dBm                   |      |       | -50  | dBc    |

| S         | Spurious Outputs <sup>2, 3</sup>              | Load VSWR ≤ 5.0:1               |      |       | -60  | dBc    |

|           | Ruggedness with Load<br>Mismatch <sup>3</sup> | No permanent damage             |      |       | 10:1 |        |

| Тс        | Case Operating Temperature                    |                                 | -30  |       | 85   | °C     |

| C Charact | eristics                                      |                                 | •    |       |      |        |

| Iccq      | Quiescent Current                             | Vmode ≥ 2.0V                    |      | 50    |      | mA     |

| Iref      | Reference Current                             | Po ≤ +27.5dBm                   |      | 5     |      | mA     |

|           |                                               |                                 |      |       |      |        |

**Notes:**1: All parameters met at  $T_C = +25^{\circ}C$ ,  $V_{CC} = +3.4V$ ,  $V_{REF} = 2.85V$  and load VSWR  $\leq$  1.2:1, unless otherwise noted.

2: All phase angles

3: Guaranteed by design

Shutdown Leakage Current No applied RF signal

Icc(off)

μΑ

## **Recommended Operating Conditions**

| Symbol                              | Parameter                       | Min  | Тур  | Max   | Units |

|-------------------------------------|---------------------------------|------|------|-------|-------|

| f                                   | Operating Frequency             | 1850 |      | 1980  | MHz   |

| V <sub>CC1</sub> , V <sub>CC2</sub> | Supply Voltage                  | 3.0  | 3.4  | 4.2   | V     |

| $V_{REF}$                           | Reference Voltage               |      |      |       |       |

|                                     | Operating                       | 2.7  | 2.85 | 3.1   | V     |

|                                     | Shutdown                        | 0    |      | 0.5   | V     |

| $V_{MODE}$                          | Bias Control Voltage            |      |      |       |       |

|                                     | Low-Power                       | 1.8  | 2.0  | 3.0   | V     |

|                                     | High-Power                      | 0    |      | 0.5   | V     |

| P <sub>OUT</sub>                    | Linear Output Power (low-power) |      |      | +16   | dBm   |

|                                     | 1920-1980 MHz (high power)      |      |      | +28   | dBm   |

|                                     | 1850-1910 MHz (high power)      |      |      | +27.5 | dBm   |

| T <sub>C</sub>                      | Case Operating Temperature      | -30  |      | +85   | °C    |

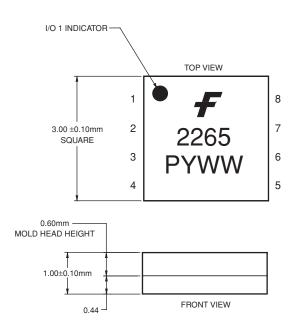

### **Package Outline**

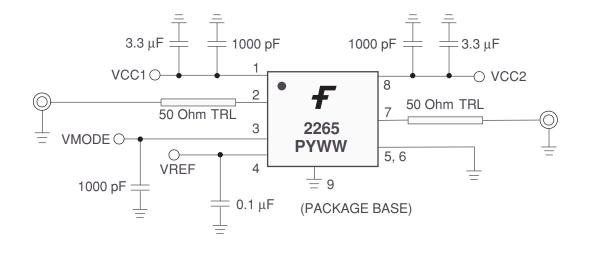

### **Signal Description**

| Pin # | Signal Name | Description                    |                 |  |

|-------|-------------|--------------------------------|-----------------|--|

| 1     | VCC1        | Supply Voltage to Input Stage  |                 |  |

| 2     | RF In       | RF Input Signal                | RF Input Signal |  |

| 3     | VMODE       | High Power/Low Power Switch    |                 |  |

| 4     | VREF        | Reference Voltage              |                 |  |

| 5     | GND         | Ground                         |                 |  |

| 6     | GND         | Ground                         |                 |  |

| 7     | RF Out      | RF Output Signal               |                 |  |

| 8     | VCC2        | Supply Voltage to Output Stage |                 |  |

| 9     | GND         | Ground                         |                 |  |

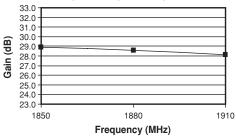

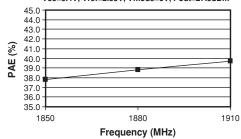

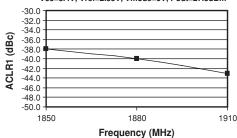

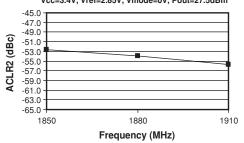

### Performance Data: 1850 to 1910 MHz

### RMPA2265 3x3 WCDMA PA at US-PCS Freq Vcc=3.4V, Vref=2.85V, Vmode=0V, Pout=27.5dBm

## RMPA2265 3x3 WCDMA PA at US-PCS Freq Vcc=3.4V, Vref=2.85V, Vmode=0V, Pout=27.5dBm

## RMPA2265 3x3 WCDMA PA at US-PCS Freq Vcc=3.4V, Vref=2.85V, Vmode=0V, Pout=27.5dBm

### **Efficiency Improvement Applications**

In addition to high-power/low-power bias modes, the efficiency of the PA module can be significantly increased at backed-off RF power levels by dynamically varying the supply voltage (Vcc) applied to the amplifier. Since mobile handsets and power amplifiers frequently operate at 10–20 dB back-off, or more, from maximum rated linear power, battery life is highly dependent on the DC power consumed at antenna power levels in the range of 0 to +16dBm. The reduced demand on transmitted RF power allows the PA supply voltage to be reduced for improved efficiency, while still meeting linearity requirements for WCDMA modulation with excellent margin. High-efficiency DC-DC converters are now available to implement switched-voltage operation.

With the PA module in low-power mode (Vmode = 2.0V) at +16dBm output power and supply voltages reduced from 3.4V nominal down to 1.2V, power-added efficiency is more than doubled from 9 percent to 25 percent (Vcc = 1.2V) while maintaining a typical ACLR1 of -40dBc and ACLR2 of less than -54 dBc. Operation at even lower levels of Vcc supply voltage are possible with a further restriction on the maximum RF output power.

RMPA2265 Rev. E

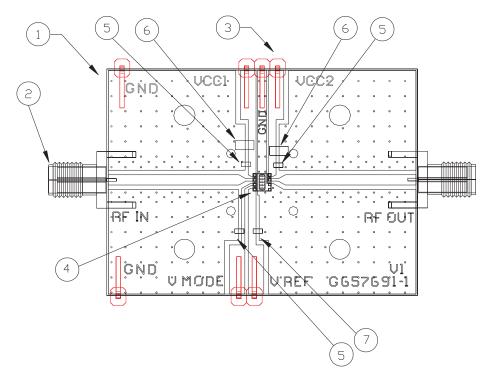

### **Evaluation Board Layout**

### **Materials List**

| Qty | Item No. | Part Number     | Description             | Vendor       |

|-----|----------|-----------------|-------------------------|--------------|

| 1   | 1        | G657691-1 V1    | PC Board                | Fairchild    |

| 2   | 2        | #142-0701-841   | SMA Connector           | Johnson      |

| 7   | 3        | #2340-5211TN    | Terminals               | ЗМ           |

| Ref | 4        |                 | Assembly, RMPA2265      | Fairchild    |

| 3   | 5        | GRM39X7R102K50V | 1000pF Capacitor (0603) | Murata       |

| 3   | 5 (Alt)  | ECJ-1VB1H102K   | 1000pF Capacitor (0603) | Panasonic    |

| 2   | 6        | C3216X5R1A335M  | 3.3µF Capacitor (1206)  | TDK          |

| 1   | 7        | GRM39Y5V104Z16V | 0.1µF Capacitor (0603)  | Murata       |

| 1   | 7 (Alt)  | ECJ-1VB1C104K   | 0.1µF Capacitor (0603)  | Panasonic    |

| A/R | 8        | SN63            | Solder Paste            | Indium Corp. |

| A/R | 9        | SN96            | Solder Paste            | Indium Corp. |

### DC Turn On Sequence:

1. VCC1 = VCC2 = 3.4V (typical)

2. VREF = 2.85V (typical)

3. High-Power: VMODE = 0V (Pout > 16dBm) Low-Power: VMODE = 2.0V (Pout < 16dBm)

### **Evaluation Board Schematic**

### **Applications Information**

### CAUTION: THIS IS AN ESD SENSITIVE DEVICE.

#### **Precautions to Avoid Permanent Device Damage:**

- Cleanliness: Observe proper handling procedures to ensure clean devices and PCBs. Devices should remain in their original packaging until component placement to ensure no contamination or damage to RF, DC and ground contact areas.

- Device Cleaning: Standard board cleaning techniques should not present device problems provided that the boards are properly dried to remove solvents or water residues.

- Static Sensitivity: Follow ESD precautions to protect against ESD damage:

- A properly grounded static-dissipative surface on which to place devices.

- Static-dissipative floor or mat.

- A properly grounded conductive wrist strap for each person to wear while handling devices.

- General Handling: Handle the package on the top with a vacuum collet or along the edges with a sharp pair of bent tweezers. Avoiding damaging the RF, DC, and ground contacts on the package bottom. Do not apply excessive pressure to the top of the lid.

- Device Storage: Devices are supplied in heat-sealed, moisture-barrier bags. In this condition, devices are protected and require no special storage conditions.

Once the sealed bag has been opened, devices should be stored in a dry nitrogen environment.

#### Device Usage:

Fairchild recommends the following procedures prior to assembly.

- Dry-bake devices at 125°C for 24 hours minimum. Note: The shipping trays cannot withstand 125°C baking temperature.

- Assemble the dry-baked devices within 7 days of removal from the oven.

- During the 7-day period, the devices must be stored in an environment of less than 60% relative humidity and a maximum temperature of 30°C

- If the 7-day period or the environmental conditions have been exceeded, then the dry-bake procedure must be repeated.

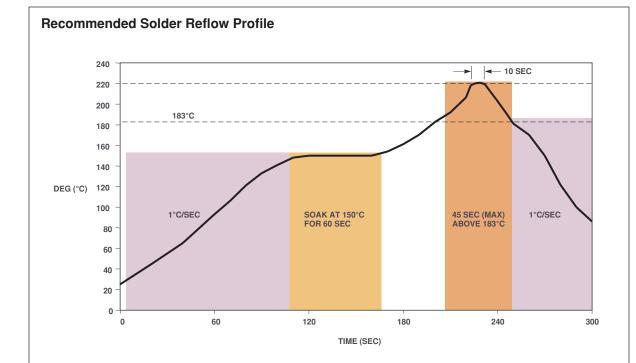

#### **Solder Materials & Temperature Profile:**

Reflow soldering is the preferred method of SMT attachment. Hand soldering is not recommended.

#### **Reflow Profile**

- Ramp-up: During this stage the solvents are evaporated from the solder paste. Care should be taken to prevent rapid oxidation (or paste slump) and solder bursts caused by violent solvent out-gassing. A typical heating rate is 1-2°C/sec.

- Pre-heat/soak: The soak temperature stage serves two purposes; the flux is activated and the board and devices achieve a uniform temperature. The recommended soak condition is: 120–150 seconds at 150°C.

- Reflow Zone: If the temperature is too high, then devices may be damaged by mechanical stress due to thermal mismatch or there may be problems due to excessive solder oxidation. Excessive time at temperature can enhance the formation of inter-metallic compounds at the lead/board interface and may lead to early mechanical failure of the joint. Reflow must occur prior to the flux being completely driven off. The duration of peak reflow temperature should not exceed 10 seconds. Maximum soldering temperatures should be in the range 215–220°C, with a maximum limit of 225°C.

- Cooling Zone: Steep thermal gradients may give rise to excessive thermal shock. However, rapid cooling promotes a finer grain structure and a more crackresistant solder joint. The illustration below indicates the recommended soldering profile.

#### **Solder Joint Characteristics:**

Proper operation of this device depends on a reliable void-free attachment of the heat sink to the PWB. The solder joint should be 95% void-free and be a consistent thickness.

#### **Rework Considerations:**

Rework of a device attached to a board is limited to reflow of the solder with a heat gun. The device should not be subjected to more than 225°C and reflow solder in the molten state for more than 5 seconds. No more than 2 rework operations should be performed.

### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

| $ACEx^{TM}$                       | FAST®                          | IntelliMAX™       | POPTM               | SPM™                   |

|-----------------------------------|--------------------------------|-------------------|---------------------|------------------------|

| ActiveArray™                      | FASTr™                         | ISOPLANAR™        | Power247™           | Stealth™               |

| Bottomless™                       | FPS™                           | LittleFET™        | PowerEdge™          | SuperFET™              |

| CoolFET™                          | FRFET™                         | MICROCOUPLER™     | PowerSaver™         | SuperSOT™-3            |

| CROSSVOLT™                        | GlobalOptoisolator™            | MicroFET™         | PowerTrench®        | SuperSOT™-6            |

| DOME™                             | GTO™ .                         | MicroPak™         | QFET®               | SuperSOT™-8            |

| EcoSPARK™                         | HiSeC™                         | MICROWIRE™        | QS™                 | SyncFET™               |

| E <sup>2</sup> CMOS <sup>TM</sup> | I <sup>2</sup> C <sup>TM</sup> | MSX <sup>TM</sup> | QT Optoelectronics™ | TinyLogic <sup>®</sup> |

| EnSigna™                          | i-Lo™                          | MSXPro™           | Quiet Series™       | TINYOPTO™              |

| FACT™                             | ImpliedDisconnect™             | $OCX^{TM}$        | RapidConfigure™     | TruTranslation™        |

| FACT Quiet Series <sup>™</sup>    |                                | OCXPro™           | RapidConnect™       | UHC™                   |

| Across the boar                   | d. Around the world.™          | OPTOLOGIC®        | μSerDes™            | UltraFET <sup>®</sup>  |

| The Power Franchise®              |                                | OPTOPLANAR™       | SILENT SWITCHER®    | UniFET™                |

| Programmable Active Droop™        |                                | PACMAN™           | SMART START™        | VCX <sup>TM</sup>      |

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

Rev. I15