# RP56LD/RP336LD and RP56D/RP336D Modem Data Pumps

Designer's Guide (Preliminary)

Order No. 1155 Rev. 2, June 24, 1998

### **NOTICE**

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

K56flex is a trademark of Rockwell International and Lucent Technologies.

ii 1155

# **Table of Contents**

| 1. | INTR           | RODUCTION                                            | 1-1  |  |  |  |  |

|----|----------------|------------------------------------------------------|------|--|--|--|--|

|    | 1.1            | SUMMARY                                              | 1-1  |  |  |  |  |

|    | 1.2            | FEATURES                                             | 1-3  |  |  |  |  |

|    | 1.3            | TECHNICAL DESCRIPTION                                | 1-4  |  |  |  |  |

| 2. | HAR            | RDWARE INTERFACE                                     | 2-1  |  |  |  |  |

|    | 2.1            | HARDWARE INTERFACE SIGNAL DESCRIPTION                | 2-1  |  |  |  |  |

|    | 2.2            | LINE TRANSFORMER REQUIREMENTS FOR K56flex, V.34/V.32 | 2-20 |  |  |  |  |

| 3. | SOF            | TWARE INTERFACE                                      |      |  |  |  |  |

|    | 3.1            | INTERFACE MEMORY                                     |      |  |  |  |  |

|    |                | 3.1.1 Interface Memory Map                           |      |  |  |  |  |

|    |                | 3.1.2 Interface Memory Signal Definitions            |      |  |  |  |  |

| 4. | DSP            | PRAM ACCESS                                          | 4-1  |  |  |  |  |

|    | 4.1            | INTERFACE MEMORY ACCESS TO DSP RAM                   | 4-1  |  |  |  |  |

|    |                | 4.1.1 RAM Access Methods                             | 4-1  |  |  |  |  |

|    |                | 4.1.2 RAM Parameters                                 |      |  |  |  |  |

|    | 4.2            | HOST DSP READ AND WRITE PROCEDURES                   | 4-5  |  |  |  |  |

|    | 4.3            | RAM READ AND WRITE EXAMPLES4                         |      |  |  |  |  |

|    | 4.4            | 4.4 DSP RAM DATA SCALING                             |      |  |  |  |  |

| 5. | HDLC OPERATION |                                                      |      |  |  |  |  |

|    | 5.1            | .1 HDLC FRAMES                                       |      |  |  |  |  |

|    | 5.2            | 2 HDLC AND FIFO DATA BUFFERS                         |      |  |  |  |  |

|    |                | 5.2.1 Transmit and Receive FIFO Data Buffers         | 5-2  |  |  |  |  |

|    |                | 5.2.2 RX FIFO and HDLC Operation                     |      |  |  |  |  |

|    | 5.3            | OPERATION                                            | 5-4  |  |  |  |  |

|    |                | 5.3.1 Transmitter and Receiver Setup                 |      |  |  |  |  |

|    |                | 5.3.2 Transmitter HDLC Operation                     |      |  |  |  |  |

|    | 5.4            | 5.3.3 Receiver HDLC Operation  EXAMPLE APPLICATION   |      |  |  |  |  |

|    | 5.4            | 5.4.1 Transmitter Example (Tx FIFO Disabled)         |      |  |  |  |  |

|    |                | 5.4.2 Transmitter Example (Tx FIFO Enabled)          |      |  |  |  |  |

|    |                | 5.4.3 Receiver Example                               |      |  |  |  |  |

| 6. | HOS            | ST FUNCTIONS                                         | 6-1  |  |  |  |  |

|    | 6.1            | INTERRUPT REQUEST HANDLING                           | 6-1  |  |  |  |  |

|    | 6.2            | AUTO DIAL PROCEDURE                                  |      |  |  |  |  |

|    | 6.3            | AUTO MODE DETECTION                                  |      |  |  |  |  |

|    | 6.4            | MODEM SELF-TEST INFORMATION                          | 6-6  |  |  |  |  |

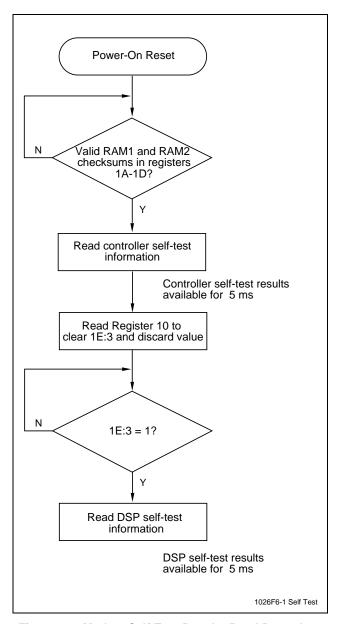

|    |                | 6.4.1 Controller Self-Test                           |      |  |  |  |  |

|    |                | 6.4.2 DSP Self-Test                                  |      |  |  |  |  |

|    | 6.5            | EQM AVERAGING                                        | 6-8  |  |  |  |  |

|     | 6.6     | RETRAIN AND AUTOMATIC RATE CHANGE                 | 6-9  |

|-----|---------|---------------------------------------------------|------|

|     |         | 6.6.1 Retrain Without a Rate Change               | 6-9  |

|     |         | 6.6.2 Retrain With a Rate Change                  |      |

|     | 6.7     | HANDSHAKE TIME-OUT TIMERS                         | 6-9  |

|     | 6.8     | CLEARDOWN                                         | 6-10 |

|     |         | 6.8.1 V.90 Cleardown                              | 6-10 |

|     |         | 6.8.2 K56flex Cleardown                           |      |

|     |         | 6.8.3 V.34 Cleardown                              |      |

| _   |         | 6.8.4 V.32 bis Cleardown                          |      |

| 7.  | DESI    | IGN CONSIDERATIONS                                |      |

|     | 7.1     | PC BOARD LAYOUT GUIDELINES                        |      |

|     | 7.2     | ELECTROMAGNETIC INTERFERENCE (EMI) CONSIDERATIONS |      |

|     | 7.3     | CRYSTAL SPECIFICATIONS                            | 7-5  |

|     | 7.4     | INTERFACE CIRCUITS                                | 7-7  |

|     | 7.5     | PACKAGE DIMENSIONS                                | 7-9  |

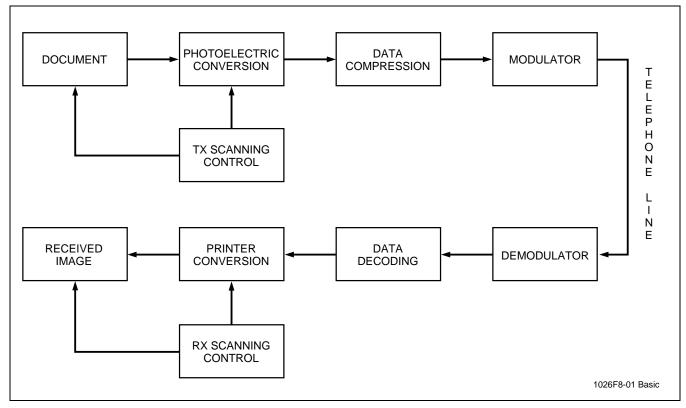

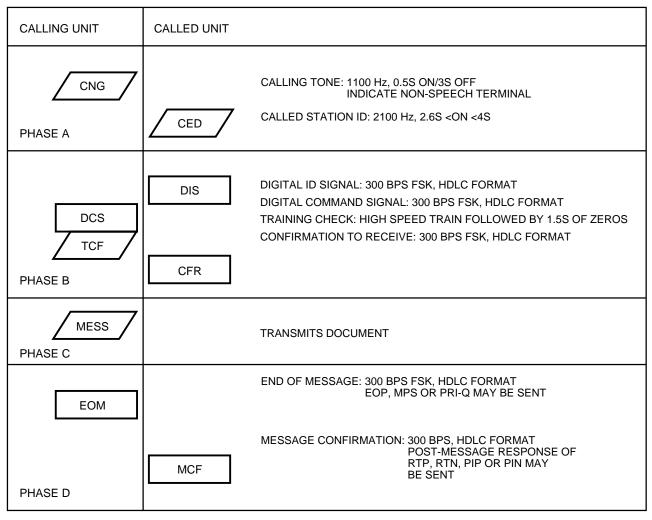

| 8.  | T.30    | IMPLEMENTATION                                    | 8-1  |

|     | 8.1     | GENERAL                                           | 8-1  |

|     |         | 8.1.1 Phase A                                     | 8-1  |

|     |         | 8.1.2 Phase B                                     | 8-1  |

|     |         | 8.1.3 Phase C                                     |      |

|     |         | 8.1.4 Phase D                                     |      |

|     |         | 8.1.5 Phase E                                     |      |

|     | 8.2     | ERROR CORRECTION MODE                             |      |

|     |         | 8.2.1 General                                     |      |

|     | 0.0     | 8.2.2 ECM Frame Structure                         |      |

| _   | 8.3     | SIGNAL RECOGNITION ALGORITHM                      |      |

| 9.  | V.8 C   | DPERATION CONSIDERATIONS                          |      |

|     | 9.1     | V.8 ORIGINATING MODEM OPERATING PROCEDURE         |      |

|     |         | 9.1.1 Originating Without CI Option (Default)     |      |

|     | 0.0     | 9.1.2 Originating With CI Option                  |      |

|     | 9.2     |                                                   |      |

|     | 9.3     | V.8 AND AUTOMODE                                  |      |

|     | 9.4     | HANDSHAKE MONITORING                              |      |

| 40  | \/ Ob : | 9.4.1 V.8 Octet Monitoring                        |      |

| 10. |         | is                                                |      |

|     | 10.1    | V.8bis TRANSMITTER                                |      |

|     |         | V.8bis RECEIVER                                   |      |

| 11. | ADPO    | CM VOICE COMPRESSION AND DECOMPRESSION            |      |

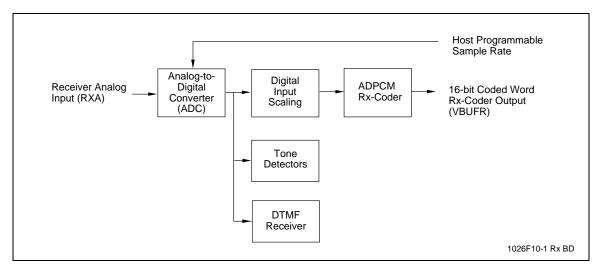

|     | 11.1    | ADPCM RECEIVER (RX-CODER)                         |      |

|     |         | 11.1.1 Mode Selection                             |      |

|     | 44.0    | 11.1.2 Operation                                  |      |

|     | 11.2    | ADPCM TRANSMITTER (TX-DECODER)                    |      |

|     |         | 11.2.1 Mode Selection                             |      |

|     |         | 11.2.2 Operation                                  | 11-1 |

|     | 11.3                                                | VOICE   | AGC                                                                       | 11-5 |  |  |  |

|-----|-----------------------------------------------------|---------|---------------------------------------------------------------------------|------|--|--|--|

|     | 11.3.1 Voice AGC Parameters                         |         |                                                                           |      |  |  |  |

| 12. | VOIC                                                | E MODE  | CONFIGURATIONS                                                            | 12-1 |  |  |  |

|     | 12.1 VOICE PATHS                                    |         |                                                                           |      |  |  |  |

|     |                                                     | 12.1.1  | L8771 Voice Operation Differences from L8570 Devices                      | 12-1 |  |  |  |

|     |                                                     | 12.1.2  | Volume and Microphone Level Control                                       |      |  |  |  |

|     |                                                     | 12.1.3  | Voice Loopback (Sidetone Feature)                                         |      |  |  |  |

|     |                                                     | 12.1.4  | Voice Record, Playback, and Tone Detector Control Register (Address 43Eh) |      |  |  |  |

|     |                                                     | 12.1.5  | Voice Mode Sample Rate Select Control Bit (Address 690h)                  | 12-5 |  |  |  |

|     |                                                     | 12.1.6  | DTMF Generation/Detection Sample Rate Control Bit (Address 691h)          |      |  |  |  |

|     |                                                     | 12.1.7  | Voice Mode Interface Control Bits (Address 692h)                          | 12-6 |  |  |  |

|     |                                                     | 12.1.8  | A-Law/μ-Law Select Control Bit (Address 39Bh)                             | 12-6 |  |  |  |

|     |                                                     | 12.1.9  | Voice Mode Setup Example                                                  | 12-6 |  |  |  |

|     |                                                     | 12.1.10 | Voice Idle Mode                                                           | 12-6 |  |  |  |

|     |                                                     | 12.1.11 | Voice AGC                                                                 | 12-6 |  |  |  |

|     | 12.2                                                | SPEAK   | ERPHONE CONFIGURATION                                                     | 12-7 |  |  |  |

|     |                                                     | 12.2.1  | Speakerphone Interface Memory Registers                                   | 12-7 |  |  |  |

|     |                                                     | 12.2.2  | DTMF and Dual Tone Modes                                                  |      |  |  |  |

|     |                                                     | 12.2.3  | Speakerphone Mode Setup Example                                           | 12-8 |  |  |  |

|     |                                                     | 12.2.4  | "Room Monitor" Mode                                                       | 12-8 |  |  |  |

|     |                                                     | 12.2.5  | Speakerphone Conversation Record                                          | 12-8 |  |  |  |

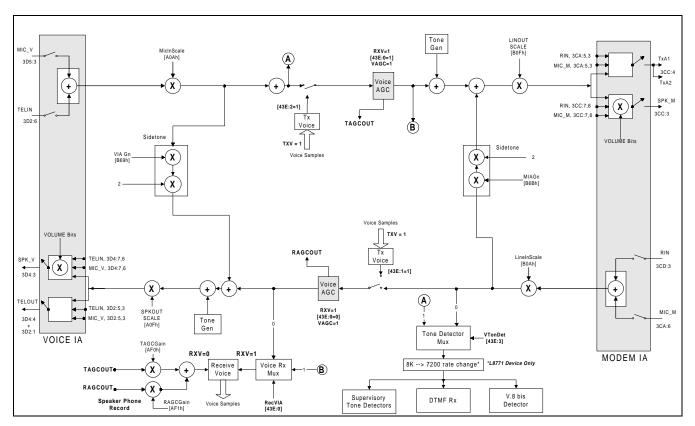

|     | 12.3                                                | Voice M | Node, Tone Detection and Tone Generation Paths                            | 12-9 |  |  |  |

| 13. | SIMULTANEOUS AUDIO/VOICE AND DATA (AUDIOSPAN)       |         |                                                                           |      |  |  |  |

|     | 13.1                                                | ML144/  | V.61 (V.32bis) AUDIOSPAN CONTROL                                          | 13-1 |  |  |  |

|     |                                                     | 13.1.1  | AudioSpan Control Registers                                               | 13-1 |  |  |  |

|     |                                                     | 13.1.2  | ML144 Mode Selection                                                      | 13-2 |  |  |  |

|     |                                                     | 13.1.3  | Detecting Remote Off-Hook Status                                          | 13-2 |  |  |  |

|     |                                                     | 13.1.4  | Generating Ring and Ringback                                              | 13-2 |  |  |  |

|     |                                                     | 13.1.5  | ML144/V.61 AudioSpan Rate Sequence                                        | 13-3 |  |  |  |

|     |                                                     | 13.1.6  | Selecting Voice+Data Rates                                                | 13-4 |  |  |  |

|     |                                                     | 13.1.7  | Maximum Voice+Data Rate                                                   | 13-4 |  |  |  |

|     |                                                     | 13.1.8  | Data-only or Voice+Data Detection                                         | 13-4 |  |  |  |

|     |                                                     | 13.1.9  | Speaker Attenuation/Gain Control                                          |      |  |  |  |

|     |                                                     |         | Microphone Gain Control                                                   |      |  |  |  |

|     |                                                     |         | TELIN/TELOUT Gain Control                                                 |      |  |  |  |

|     |                                                     |         | Handset Echo Canceller                                                    |      |  |  |  |

|     | 13.2                                                | HOST I  | NTERFACE SELECTION AND SETUP                                              |      |  |  |  |

|     |                                                     | 13.2.1  | Typical Operation and Selection of User Interface                         | 13-7 |  |  |  |

| 14. | K56F                                                | LEX SET | TUP AND CODE CHANGES                                                      | 14-1 |  |  |  |

|     | 14.1                                                | K56flex | SETUP                                                                     | 14-1 |  |  |  |

|     |                                                     | 14.1.1  | Client Modem (Analog Modem) Configuration Procedure                       | 14-1 |  |  |  |

|     |                                                     | 14.1.2  | Server Modem (Digital Modem) Configuration Procedure                      | 14-1 |  |  |  |

|     |                                                     | 14.1.3  | K56flex Bit Definitions                                                   | 14-3 |  |  |  |

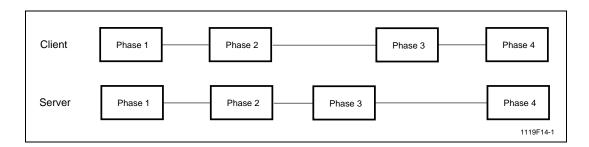

|     |                                                     | 14.1.4  | K56flex Handshake                                                         |      |  |  |  |

|     |                                                     | 14.1.5  | Detecting K56flex                                                         | 14-4 |  |  |  |

|     |                                                     | 14.1.6  | EQM Readings                                                              | 14-5 |  |  |  |

|     |                                                     | 14.1.7  | Automatic Data Rate Selection                                             | 14-5 |  |  |  |

|     | 14.2                                                | RETRA   | INS AND RENEGOTIATIONS                                                    | 14-7 |  |  |  |

|     | 14.3 ROBBED BIT SIGNALING AND DIGITAL PAD DETECTION |         |                                                                           |      |  |  |  |

| 15. | 15. V.90 PROGRAMMING INFORMATION |                                                                                                    |          |  |

|-----|----------------------------------|----------------------------------------------------------------------------------------------------|----------|--|

|     | 15.1                             | V.90 CONTROL BITS                                                                                  | 15-2     |  |

|     |                                  | 15.1.1 6A3h:0-7 - V.90 Host Control                                                                | 15-2     |  |

|     |                                  | 15.1.2 6A2h:0-7 - Desired V.90 Receive Speed                                                       | 15-3     |  |

|     |                                  | 15.1.3 6C1h, 6C2h, 6C3h - Server DPCM Transmit Data Rate Mask                                      |          |  |

|     |                                  | 15.1.4 382h, 383h - Client APCM Transmit Data Rate Mask and Server DPCM Receive Data Rate          | Mask15-6 |  |

|     |                                  | 15.1.5 604h - APCM and DPCM Maximum Receive Data Rate                                              | 15-7     |  |

|     |                                  | 15.1.6 6B3h - DPCM TX Level Control                                                                | 15-8     |  |

|     |                                  | 15.1.7 680h:5 - Rate Renegotiation with Silence for V.90 (Fast Retrain)                            | 15-8     |  |

|     |                                  | 15.1.8 6EAh:0-5 - RBS Pattern                                                                      | 15-8     |  |

|     |                                  | 15.1.9 39Bh:7 - A-law / u-Law Selection                                                            | 15-8     |  |

|     |                                  | 15.1.10 6C9h - Digital Loss Estimate                                                               | 15-8     |  |

|     | 15.2                             | V.90 DATA RATE SELECTION                                                                           | 15-9     |  |

|     |                                  | 15.2.1 General Procedure                                                                           | 15-9     |  |

|     |                                  | 15.2.2 Data Rate Vs EQM Sum                                                                        | 15-10    |  |

|     |                                  | 15.2.3 EQM Readings                                                                                | 15-10    |  |

|     |                                  | 15.2.4 Forcing a V.34 Fallback From V.90                                                           | 15-10    |  |

| 16. | RAM                              | DOWNLOAD AND V.90/K56FLEX BIMODAL SETUP                                                            | 16-1     |  |

|     | 16.1                             | RAM DOWNLOAD MODULES                                                                               | 16-1     |  |

|     |                                  | 16.1.1 Server V.90 RAM Code                                                                        | 16-1     |  |

|     |                                  | 16.1.2 Client V.90 RAM Code                                                                        | 16-1     |  |

|     |                                  | 16.1.3 Client K56flex RAM Code                                                                     | 16-3     |  |

|     | 16.2                             | RAM MODULE DOWNLOAD PROCEDURE                                                                      | 16-4     |  |

|     |                                  | 16.2.1 Downloading can be initiated by the Host or the Datapump                                    | 16-4     |  |

|     | 16.3                             | DOWNLOAD FILE FORMAT                                                                               | 16-5     |  |

|     |                                  | 16.3.1 RAM File Header Information                                                                 | 16-5     |  |

|     | 16.4                             | RAM DOWNLOAD PROCEDURES                                                                            | 16-7     |  |

|     | 16.5                             | TYPICAL HANDSHAKE SCENERIOS                                                                        | 16-10    |  |

|     |                                  | 16.5.1 Setup for Answering Server: V.90, K56flex, K56plus, V.34, VFC, V.32bis                      | 16-10    |  |

|     |                                  | 16.5.2 Setup for Originating Server: V.90, K56flex, K56plus, V.34, VFC, V.32bis                    | 16-10    |  |

|     |                                  | 16.5.3 Setup for Originating Client: V.90, K56flex, V.34, V.32bis, with V.90 Priority over K56flex | 16-11    |  |

|     |                                  | 16.5.4 Setup for Originating Client: K56flex, V.90, V.34, V.32bis, with K56flex Priority over V.90 | 16-11    |  |

|     |                                  | 16.5.5 Setup for Answering Client: V.90, K56flex, V.34, V.32bis, with V.90 Priority over K56flex   | 16-12    |  |

|     |                                  | 16.5.6 Setup for Answering Client: K56flex, V.90, V.34, V.32bis, with K56flex Priority over V.90   | 16-13    |  |

|     | 16.6                             | INITIAL HANDSHAKE DECISION PROCESS                                                                 | 16-14    |  |

|     |                                  | 16.6.1 Bi-Modal Server: Answer Mode                                                                | 16-14    |  |

|     |                                  | 16.6.2 Bi-Modal Server: Originate Mode                                                             | 16-14    |  |

|     |                                  | 16.6.3 Bi-Modal Client: Originate Mode                                                             | 16-14    |  |

|     |                                  | 16.6.4 Bi-Modal Client: Answer Mode                                                                | 16-14    |  |

| 17. | V.34                             | FAX OPERATIONS                                                                                     | 17-1     |  |

|     | 17.1                             | V.34 FAX OPERATION SPECIFICATIONS                                                                  | 17-1     |  |

|     | 17.2                             | START-UP SCENARIOS                                                                                 | 17-5     |  |

|     |                                  | Automatic start scenarios:                                                                         | 17-5     |  |

|     |                                  | Manual start scenarios:                                                                            | 17-5     |  |

|     |                                  | 17.2.1 Automatic Start Scenerios                                                                   | 17-5     |  |

|     |                                  | 17.2.2 Manual Start Scenerios                                                                      | 17-6     |  |

vi

| 17.3 | TURNAROUND POLLING AND SCENARIOS |                                       |       |  |  |

|------|----------------------------------|---------------------------------------|-------|--|--|

|      |                                  | Changing from Transmit to Receive Fax |       |  |  |

|      | 17.3.2                           | Changing from Receive to Transmit Fax | 17-7  |  |  |

| 17.4 | SUMMA                            | ARY OF SIGNAL DETECTORS AT EACH PHASE | 17-8  |  |  |

|      | 17.4.1                           | Call Terminal                         | 17-8  |  |  |

|      | 17.4.2                           | Answer Terminal                       | 17-8  |  |  |

| 17.5 | OPERATION AND CONNECTION         |                                       |       |  |  |

|      | 17.5.1                           | Configuration and Operation Setup     | 17-9  |  |  |

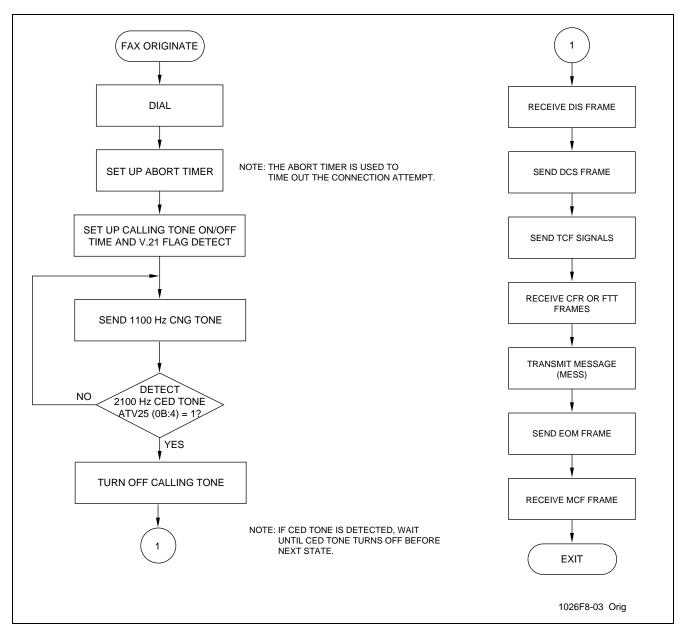

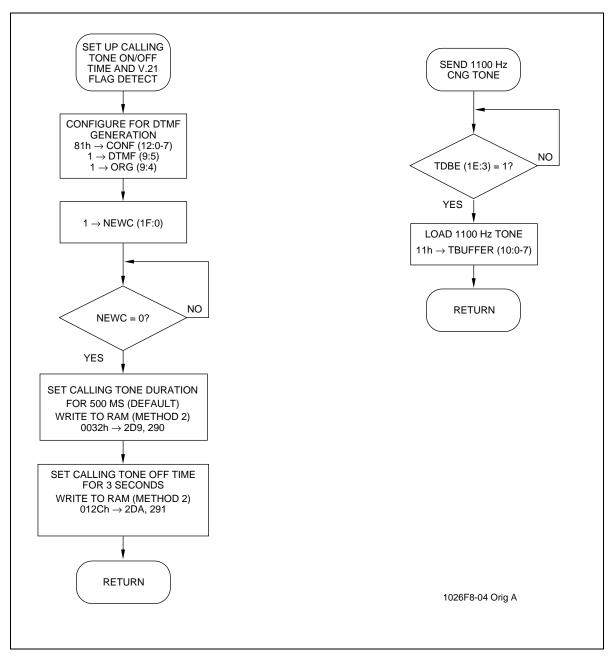

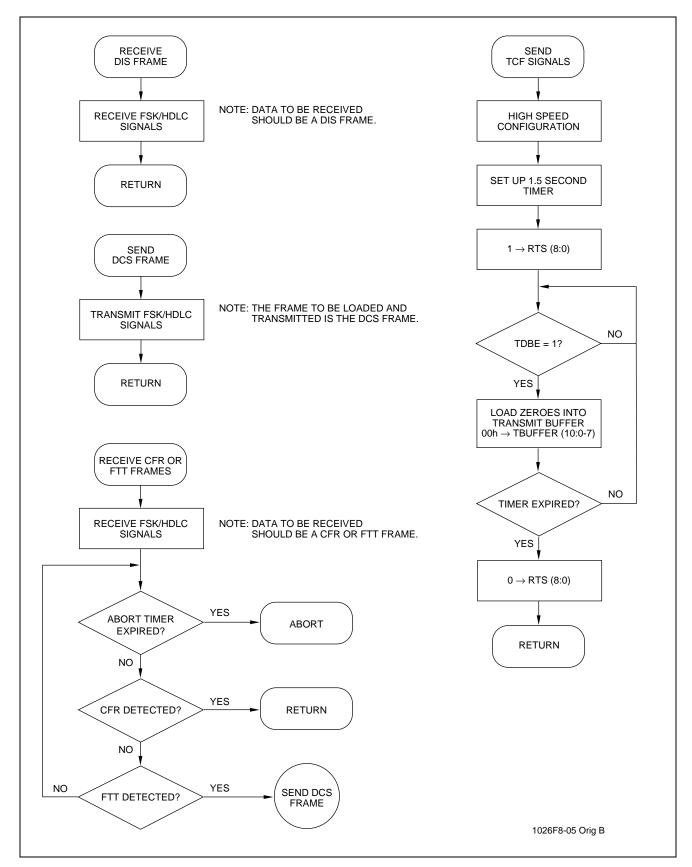

|      | 17.5.2                           | Originating Modem Operating Procedure | 17-11 |  |  |

|      | 17.5.3                           | Answering Modem Operating Procedure   |       |  |  |

|      |                                  | Operation during Turnaround Polling   |       |  |  |

|      | 17.5.5                           | Operation during Initial Polling      | 17-17 |  |  |

| 17.6 | HANDS                            | SHAKE MONITORING                      | 17-18 |  |  |

|      | 17.6.1                           | Octet Monitoring                      | 17-18 |  |  |

|      | 17.6.2                           | V.34 Fax Handshake Phase Monitoring   | 17-18 |  |  |

|      | 1763                             | Control Channel Retrain               | 17-20 |  |  |

# **List of Figures**

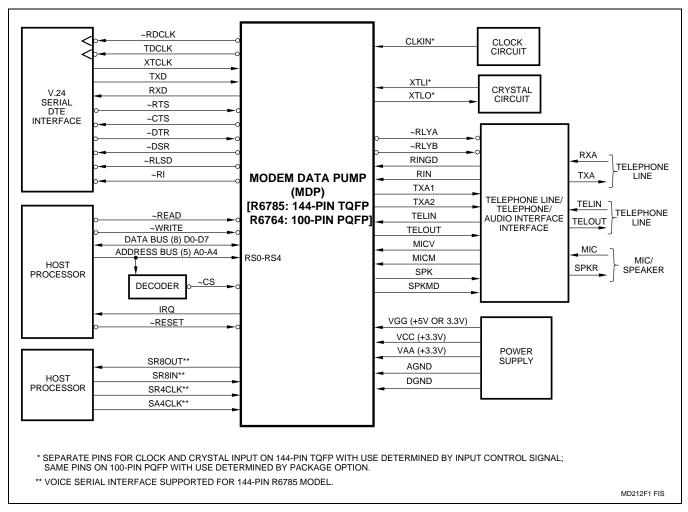

| Figure 2-1. MDP Functional Interface Signals                     | 2-2  |

|------------------------------------------------------------------|------|

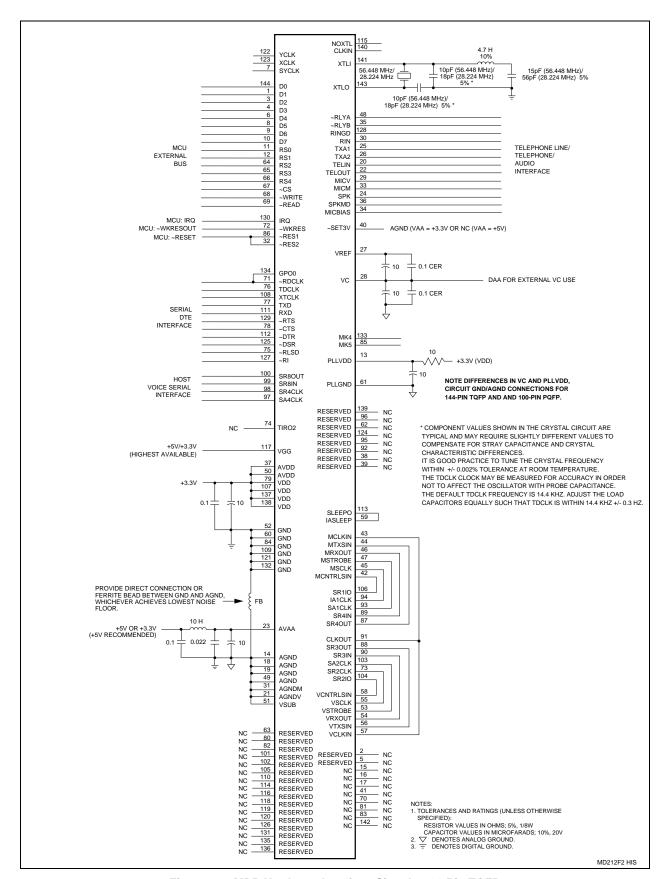

| Figure 2-2. MDP Hardware Interface Signals-144-Pin TQFP          | 2-3  |

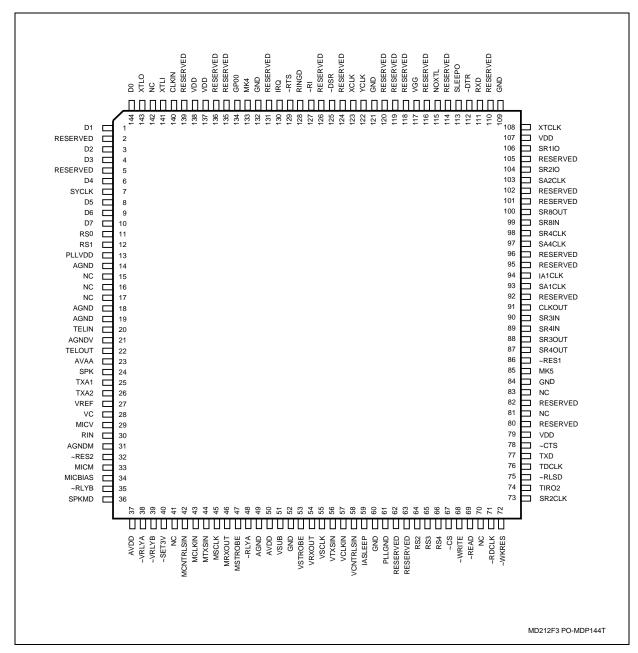

| Figure 2-3. MDP Pin Signals - 144-Pin TQFP                       | 2-4  |

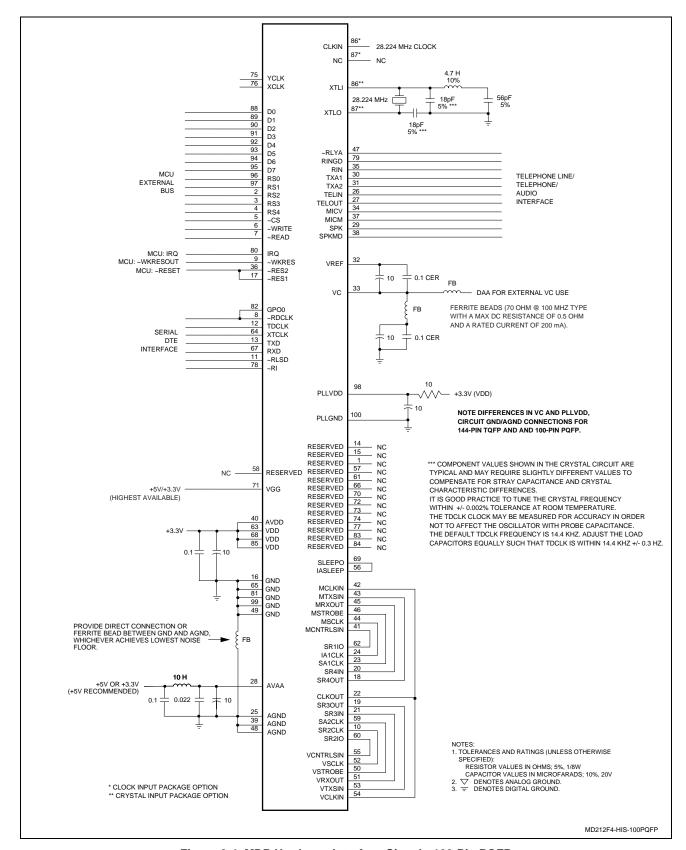

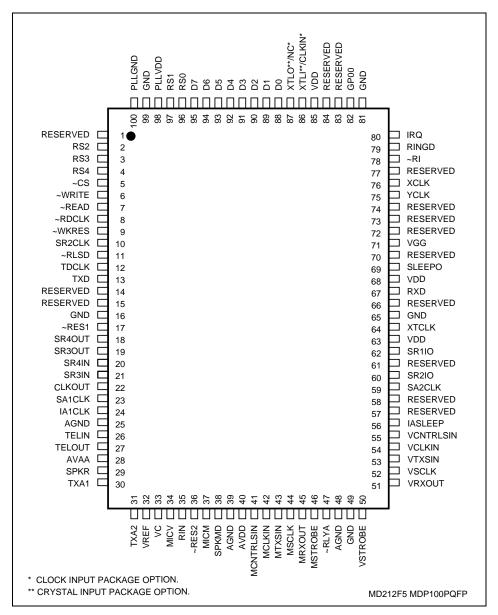

| Figure 2-4. MDP Hardware Interface Signals-100-Pin PQFP          | 2-7  |

| Figure 2-5. MDP Pin Signals - 100-Pin PQFP                       | 2-8  |

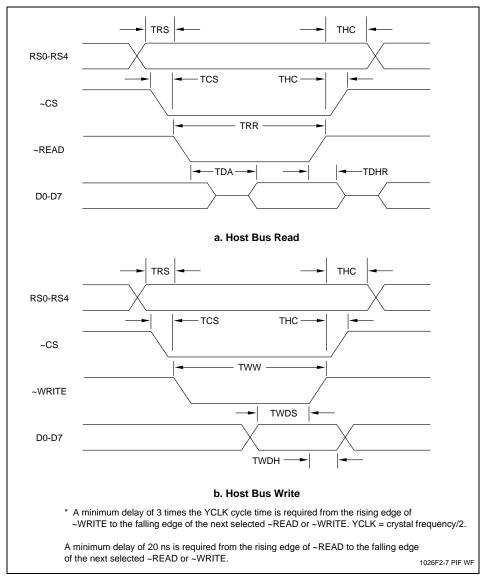

| Figure 2-6. Host Bus Interface Waveforms                         | 2-18 |

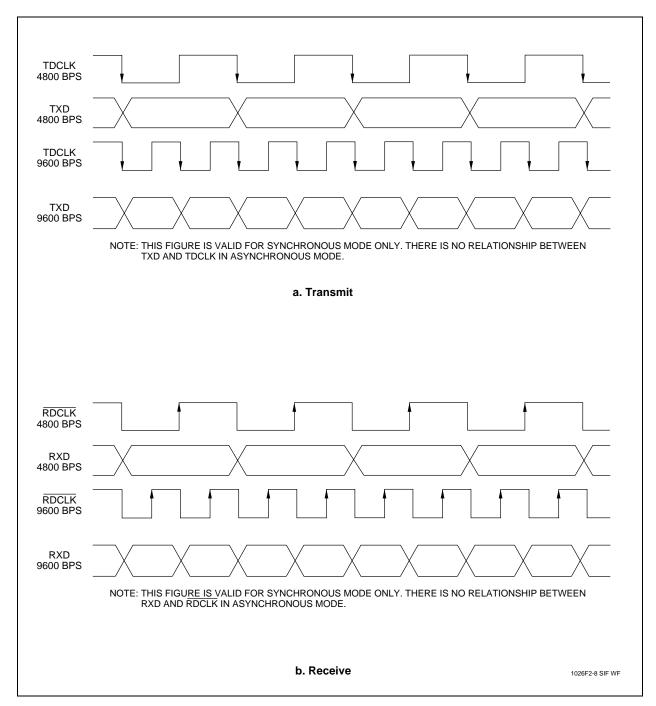

| Figure 2-7. DTE Serial Interface Waveforms                       | 2-19 |

| Figure 3-1. MDP Interface Memory Map                             | 3-2  |

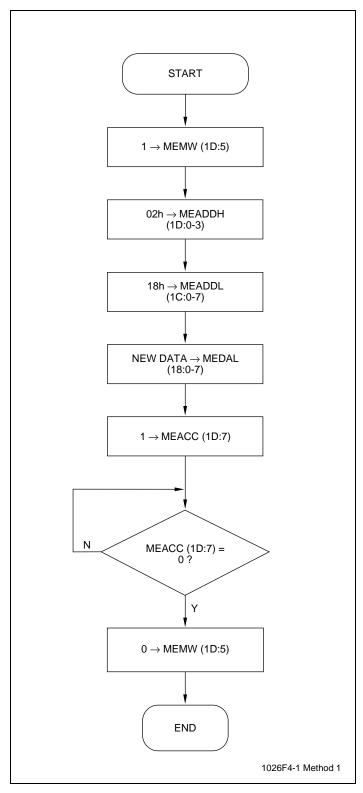

| Figure 4-1. Method 1 Example - Changing DTMF Tone Duration (LSB) | 4-6  |

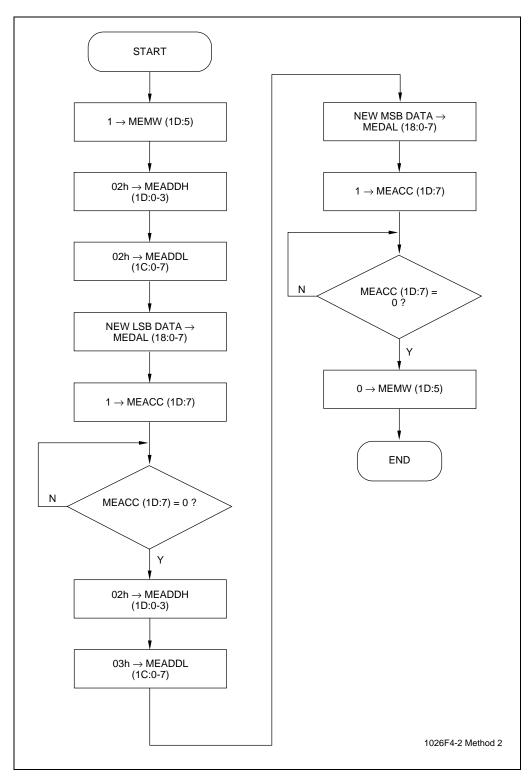

| Figure 4-2. Method 2 Example - Changing RTS-CTS Delay            | 4-7  |

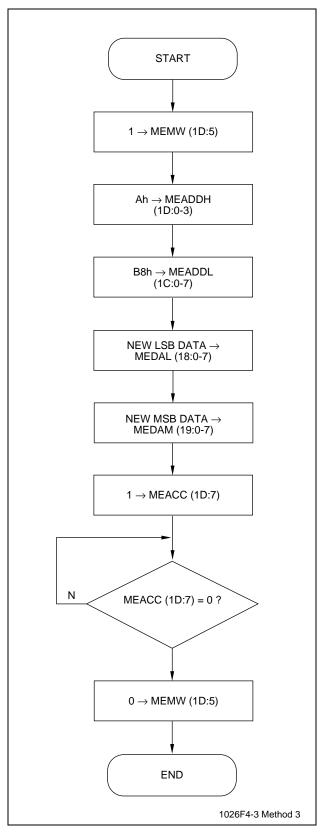

| Figure 4-3. Method 3 Example - Changing TONEA THRESHU            | 4-8  |

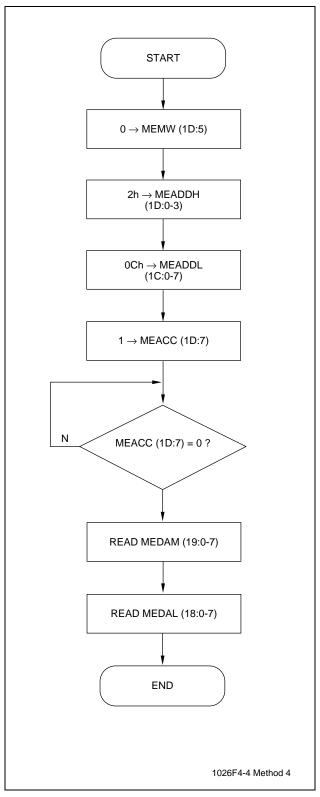

| Figure 4-4. Method 4 Example - Reading EQM                       | 4-9  |

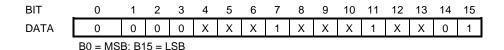

| Figure 4-5. NEWS Masking Registers                               | 4-16 |

| Figure 4-6. Tone Detectors                                       | 4-19 |

| Figure 4-7. Biquad Filter and Level Detector                     | 4-21 |

| Figure 4-8. Relationship of EQM to Eye Pattern                   | 4-24 |

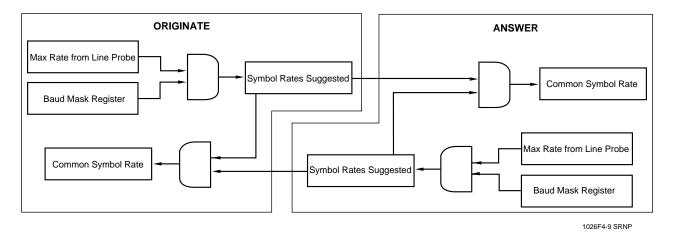

| Figure 4-9. V.34 Symbol Rate Negotiation Process                 | 4-27 |

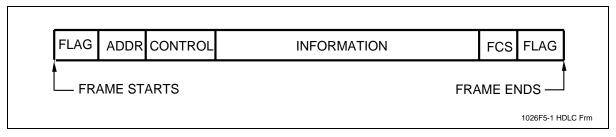

| Figure 5-1. HDLC Frame                                           | 5-2  |

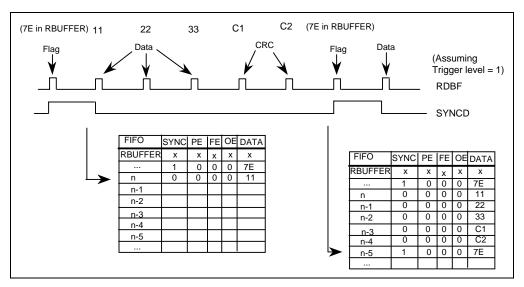

| Figure 5-2. Normal HDLC Receive Operation                        | 5-3  |

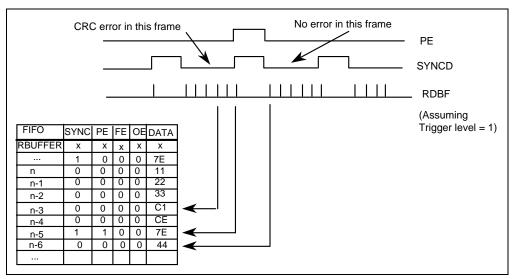

| Figure 5-3. HDLC Receive Operation when a CRC Error Occurs       | 5-3  |

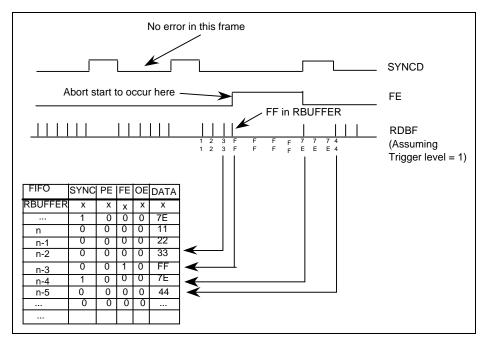

| Figure 5-4. HDLC Receiver Operation with an Abort Condition      | 5-4  |

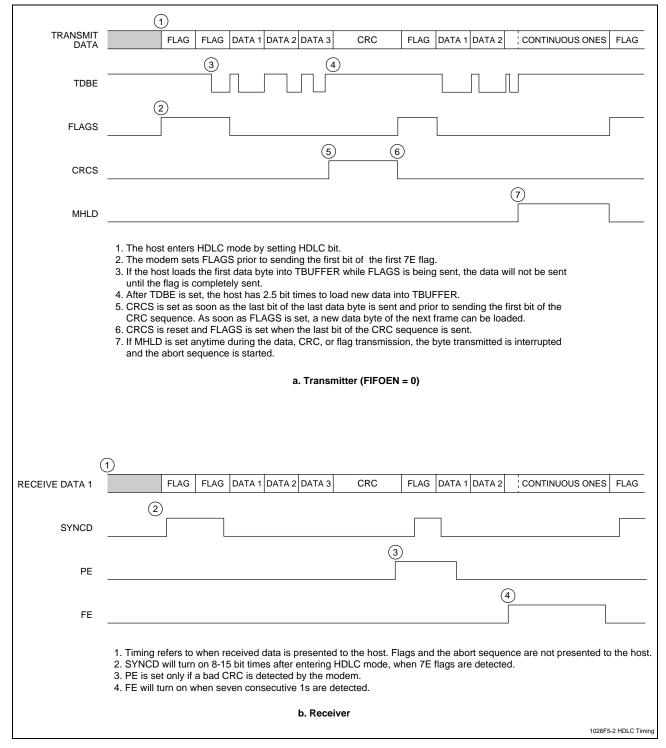

| Figure 5-5. HDLC Signal Timing                                   | 5-8  |

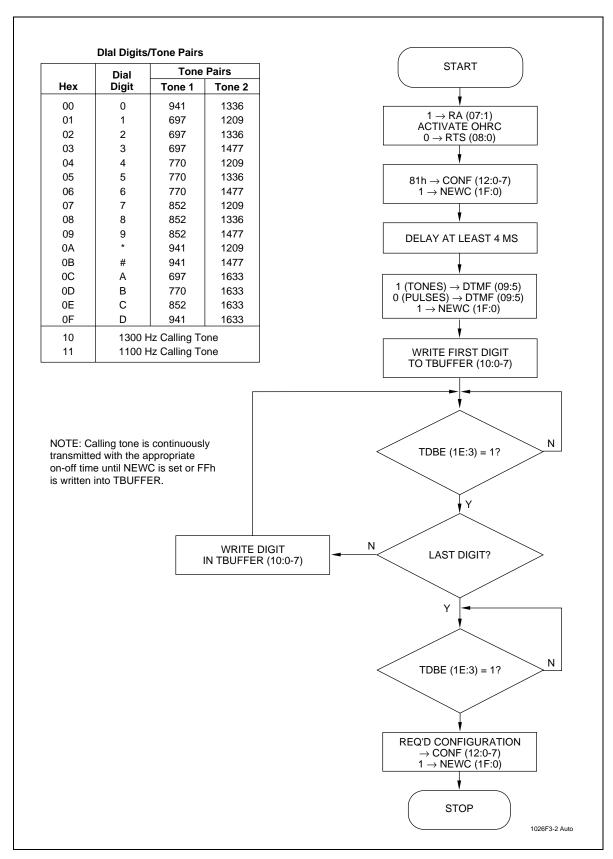

| Figure 6-1. Auto Dial Sequence and Dial Digits                   | 6-3  |

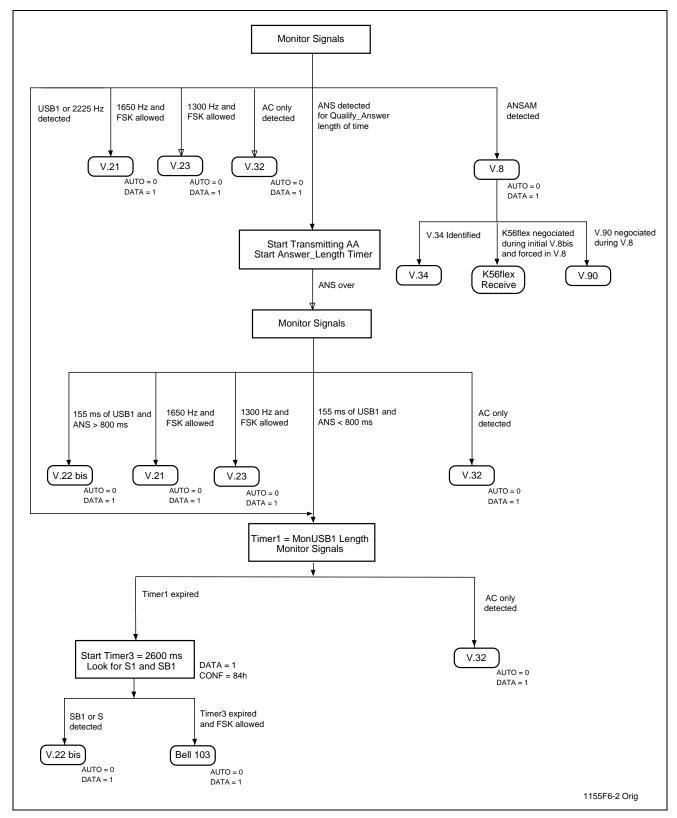

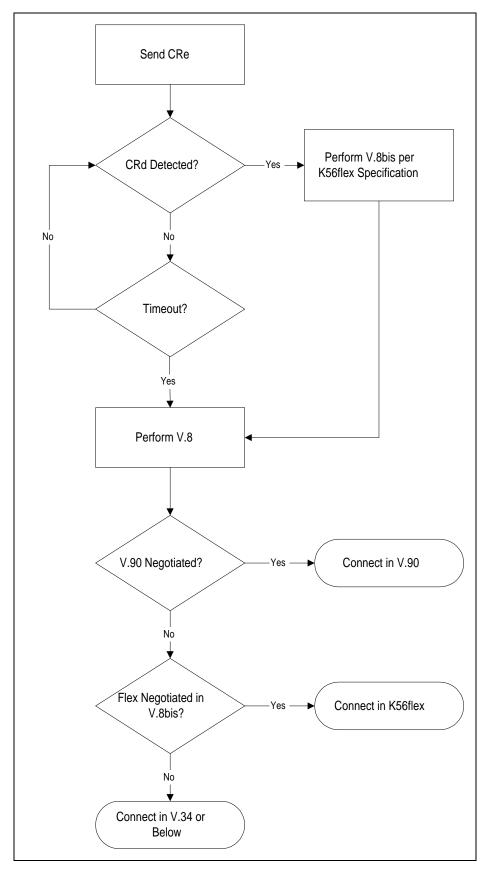

| Figure 6-2. Host Flowchart - Originating Automode                | 6-4  |

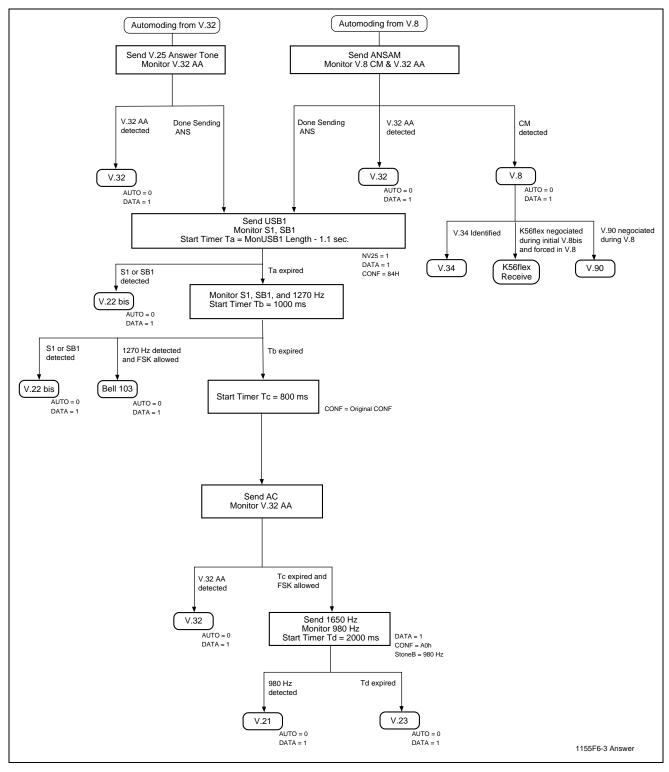

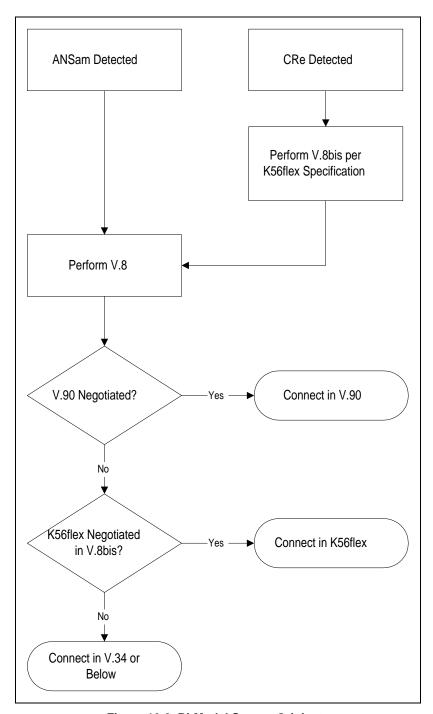

| Figure 6-3. Host Flowchart - Answering Automode                  | 6-5  |

| Figure 6-4. Modem Self-Test Results Read Procedure               | 6-7  |

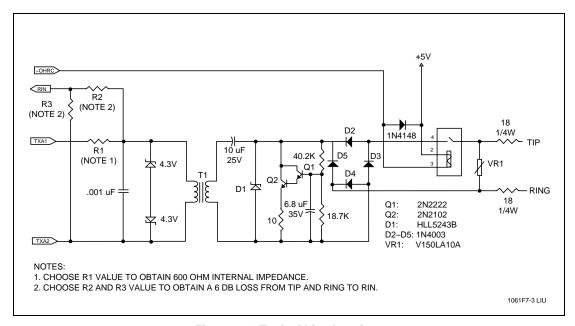

| Figure 7-1. Typical Line Interface                               | 7-7  |

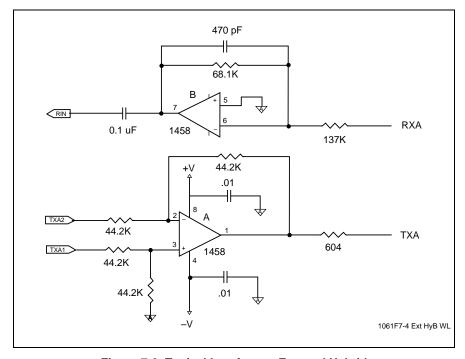

| Figure 7-2. Typical Interface to External Hybrid                 | 7-7  |

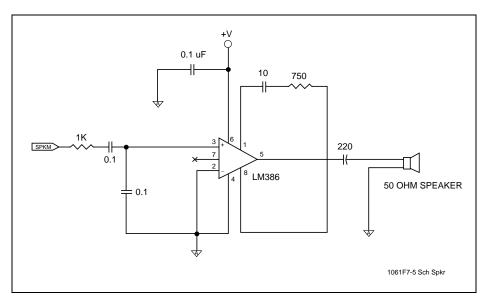

| Figure 7-3. Typical External Speaker Circuit                     | 7-8  |

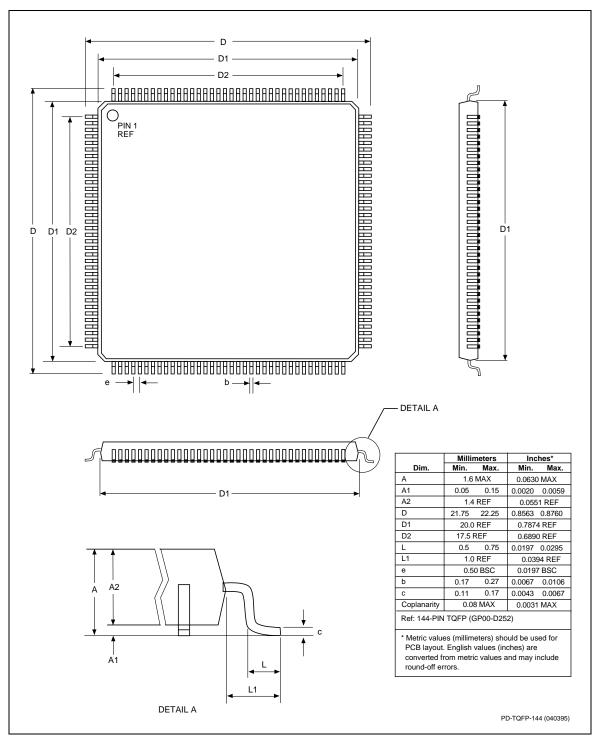

| Figure 7-4. Package Dimensions - 144-Pin TQFP                    | 7-9  |

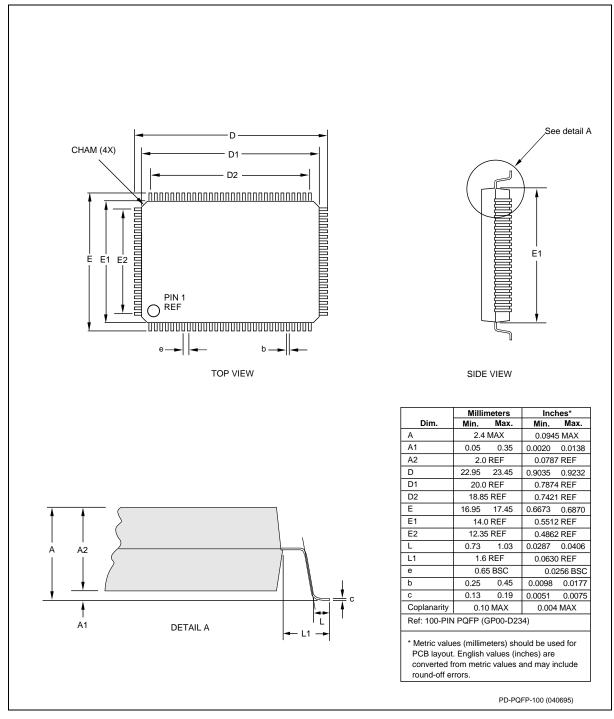

| Figure 7-5. Package Dimensions - 100-Pin PQFP                    | 7-10 |

| Figure 8-1. Basic Block Diagram of G3 Facsimile                  | 8-3  |

| Figure 8-2. G3 Facsimile Procedure                               | 8-4  |

| Figure 8-3. Originating a Fax Call - General                     | 8-5  |

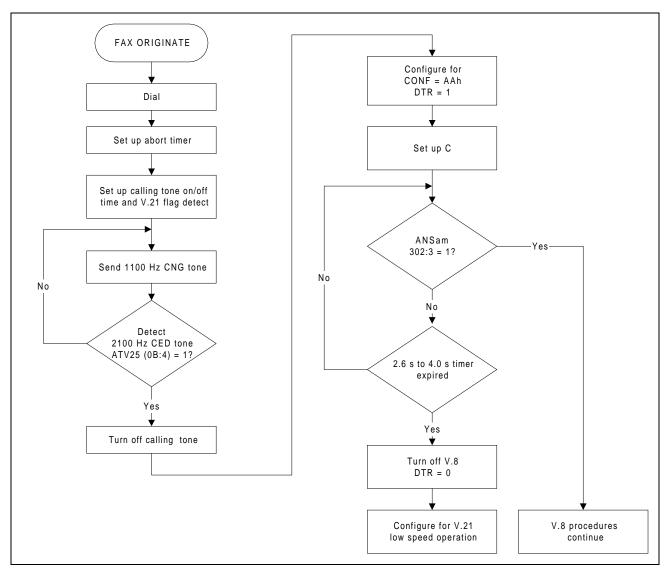

| Figure 8-4. Originating a Fax Call - Phase A                     | 8-6  |

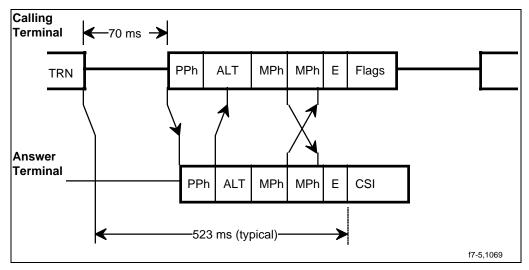

| Figure 8-5. Originating a Fax Call - Phase B                     | 8-7  |

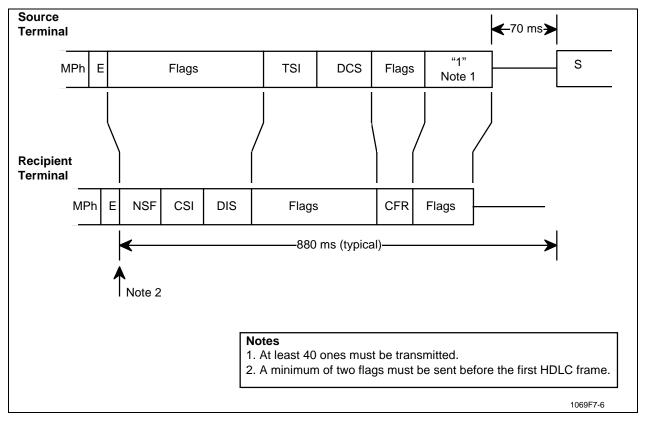

| Figure 8-6. Originating a Fax Call - Phase C                     | 8-8  |

| Figure 8-7. Originating a Fax Call - Phase D                     | 8-9  |

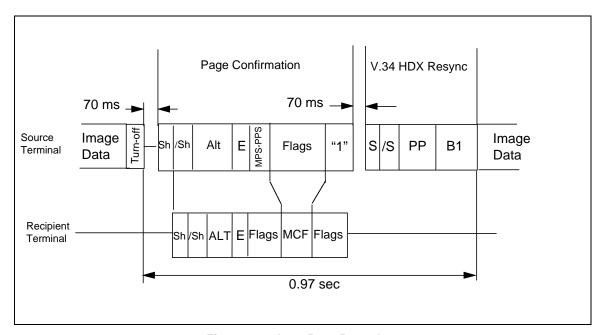

| Figure 8-8. Answering a Fax Call - General                       | 8-10 |

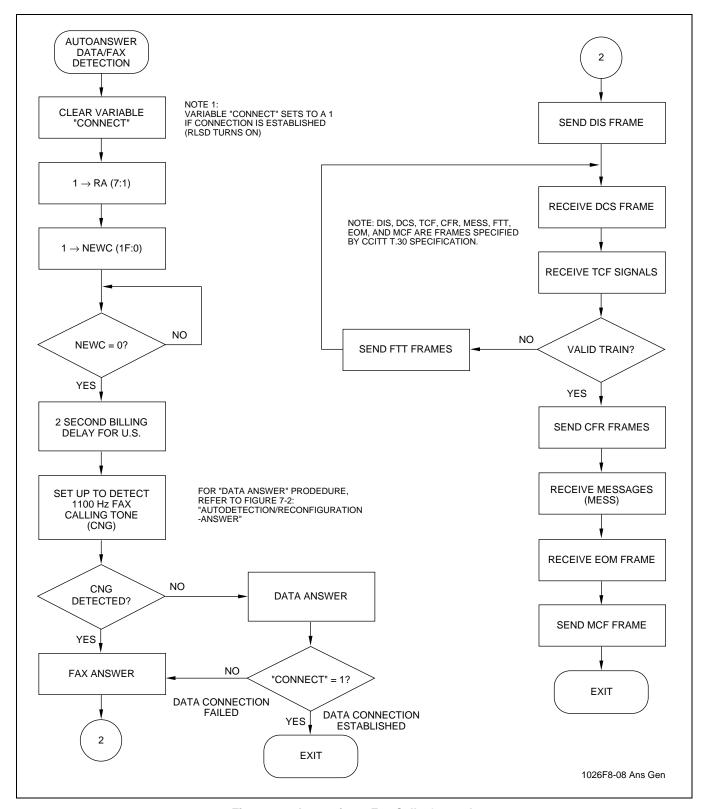

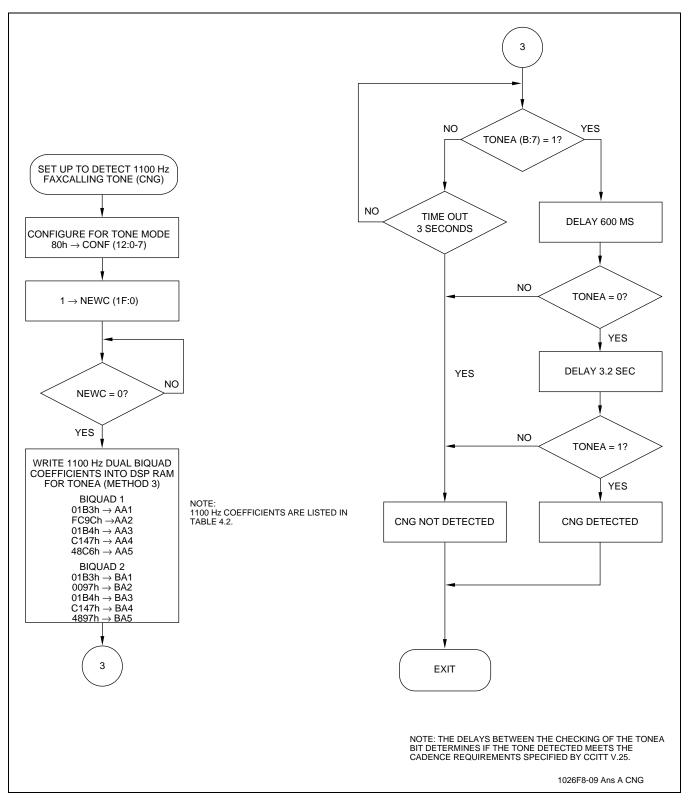

| Figure 8-9. Answering a Fax Call - Phase A (CNG)                 | 8-11 |

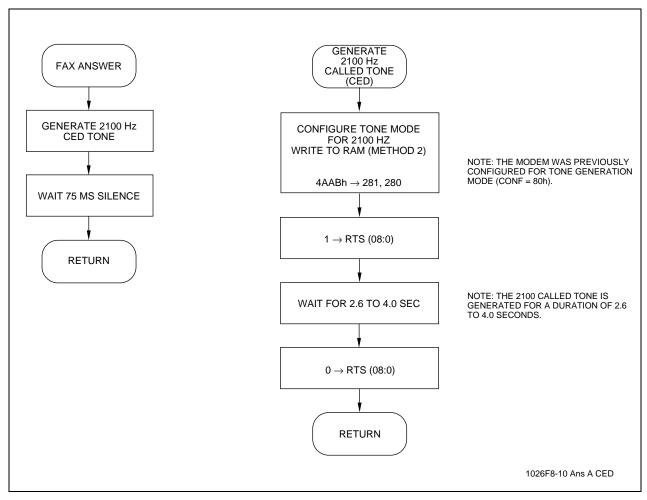

| Figure 8-10. Answering a Fax Call - Phase A (CED)                |      |

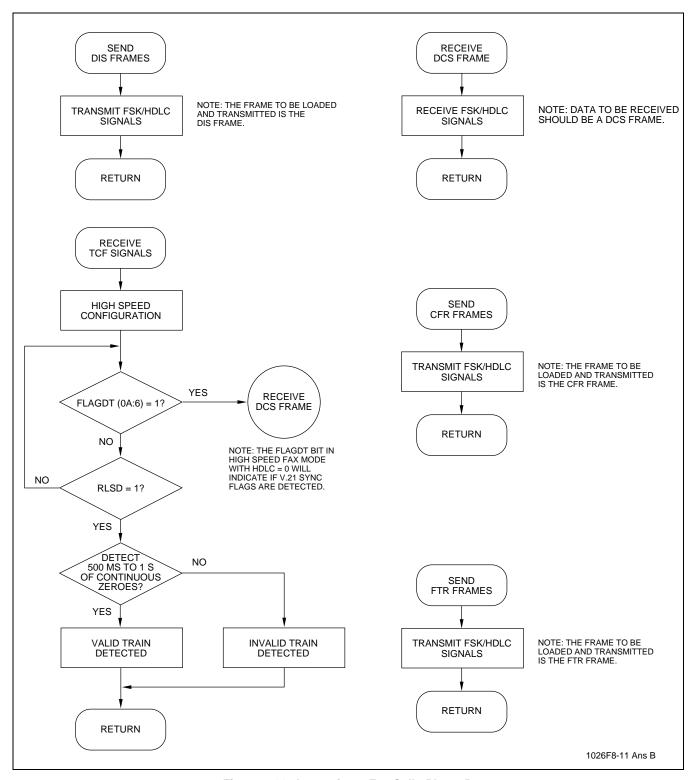

| Figure 8-11. Answering a Fax Call - Phase B                      | 8-13 |

|                                                                  |      |

1155

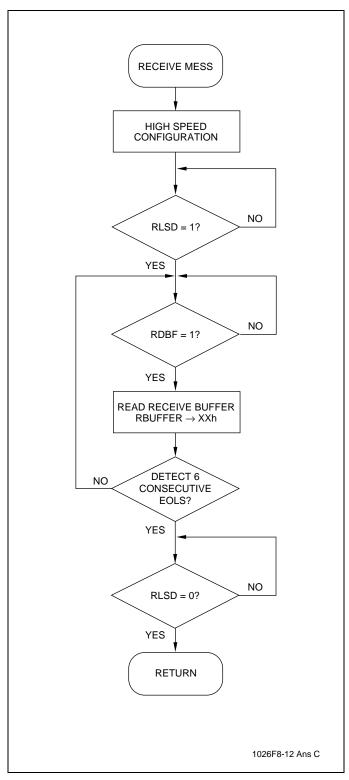

| Figure 8-12. Answering a Fax Call - Phase C                       | 8-14  |

|-------------------------------------------------------------------|-------|

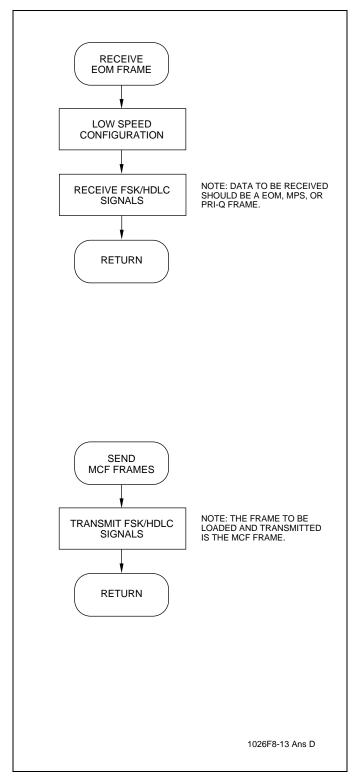

| Figure 8-13. Answering a Fax Call - Phase D                       | 8-15  |

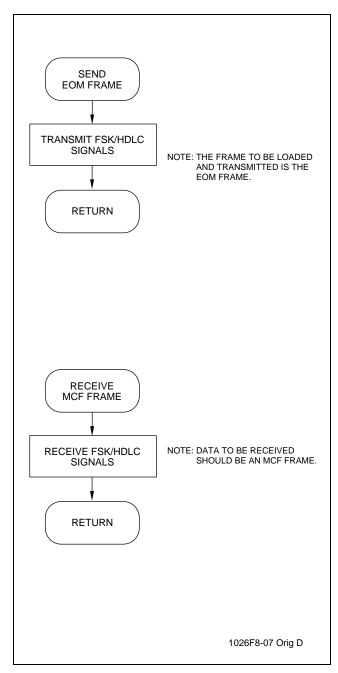

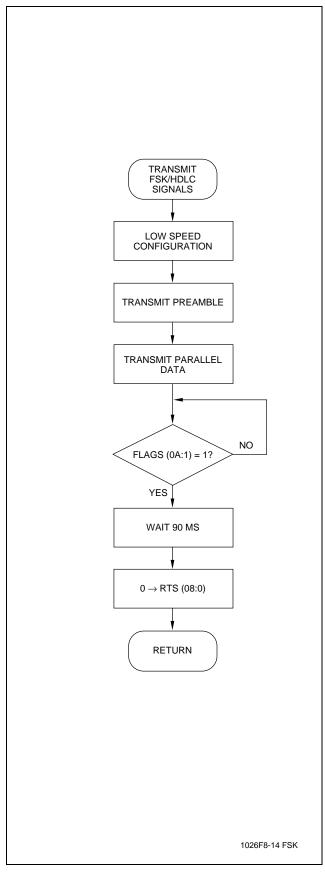

| Figure 8-14. Transmitting FSK/HDLC Signals                        | 8-16  |

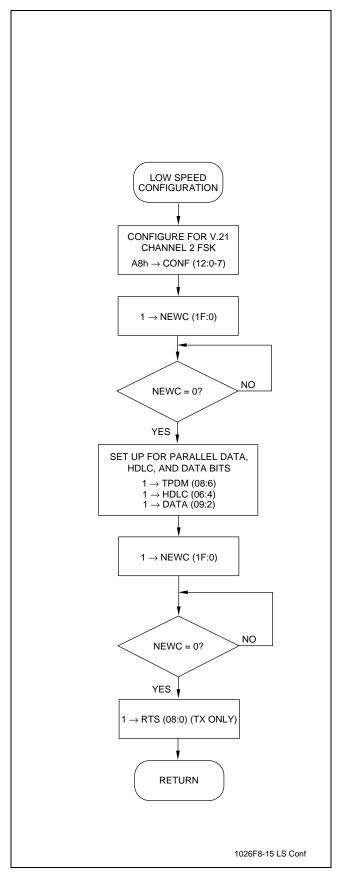

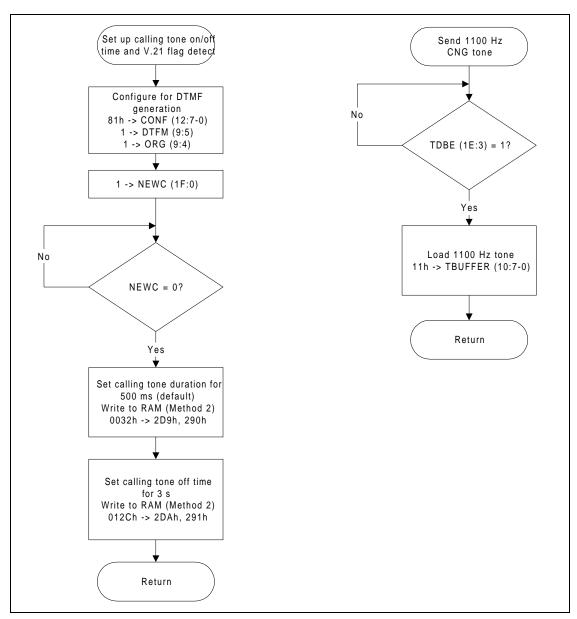

| Figure 8-15. Low Speed Configuration Routine                      | 8-17  |

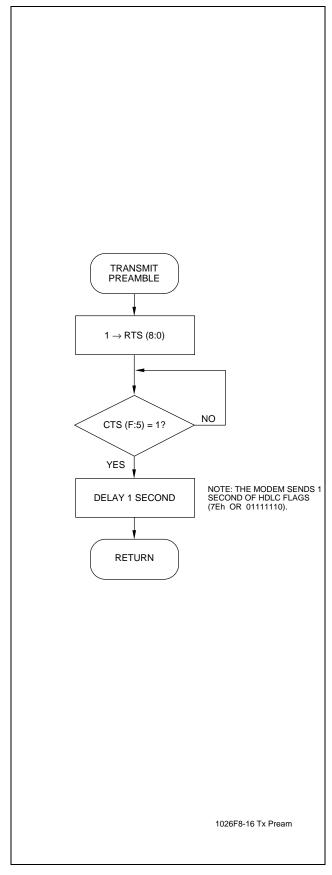

| Figure 8-16. Transmit Preamble Routine                            | 8-18  |

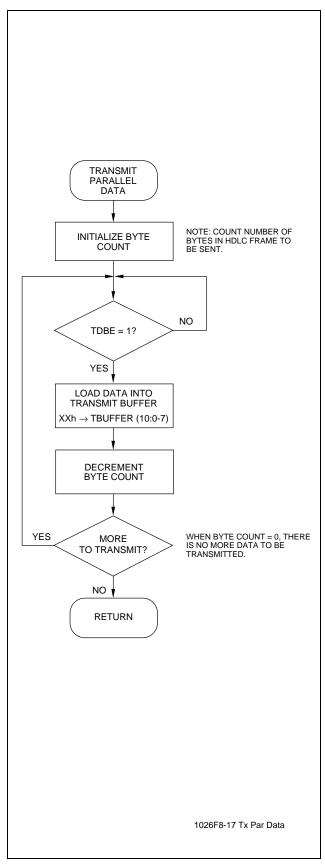

| Figure 8-17. Transmit Parallel Data Routine                       | 8-19  |

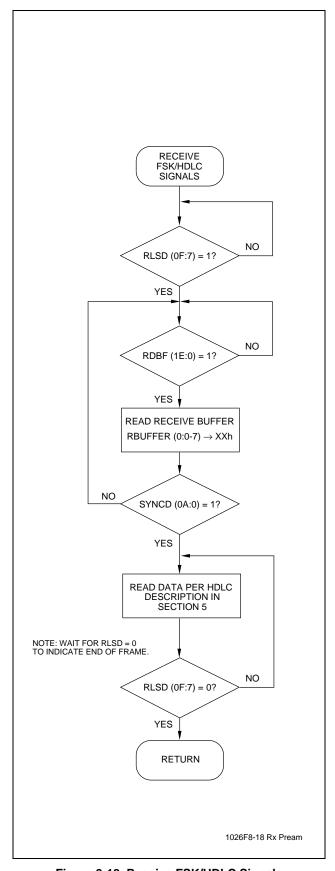

| Figure 8-18. Receive FSK/HDLC Signals                             | 8-20  |

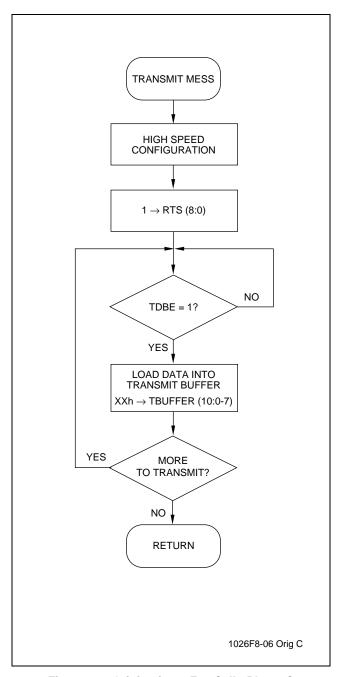

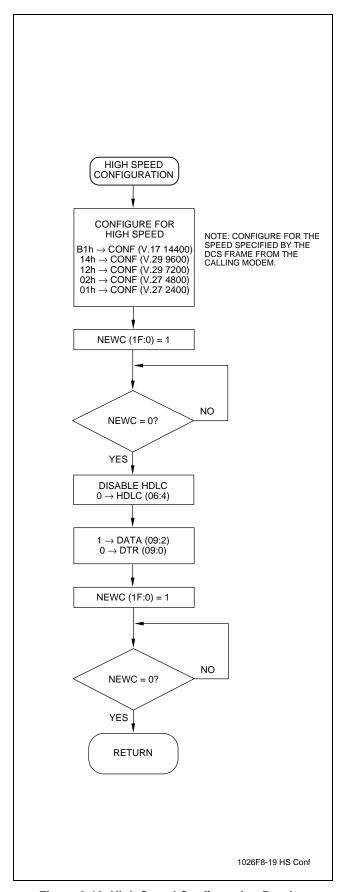

| Figure 8-19. High Speed Configuration Routine                     | 8-21  |

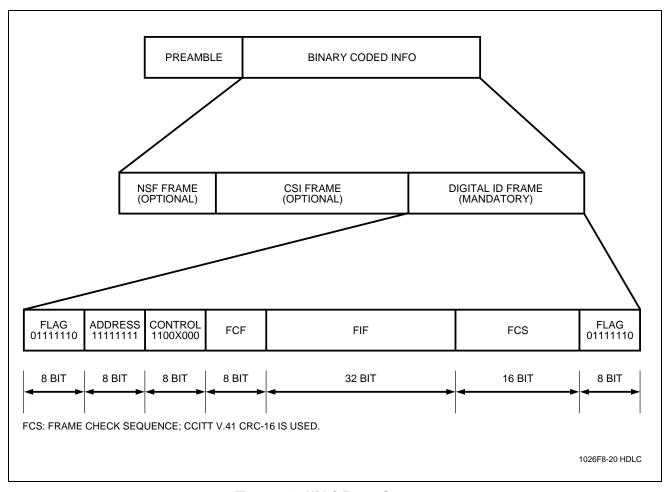

| Figure 8-20. HDLC Frame Structure                                 | 8-23  |

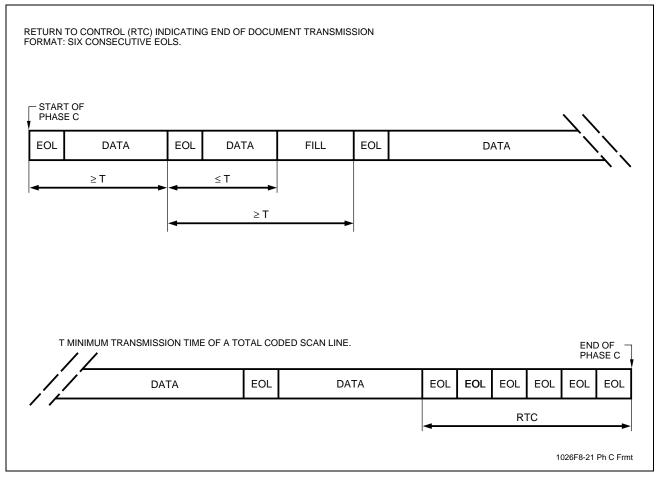

| Figure 8-21. Phase C Format                                       | 8-24  |

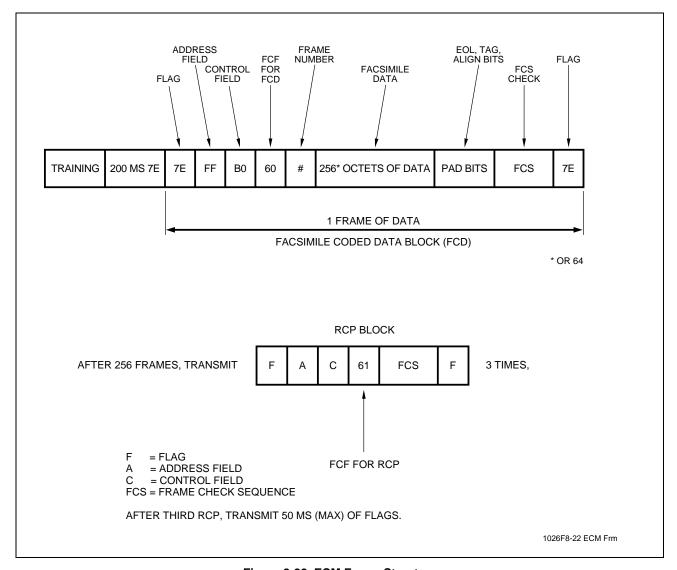

| Figure 8-22. ECM Frame Structure                                  | 8-25  |

| Figure 8-23. ECM Message Protocol Example                         | 8-26  |

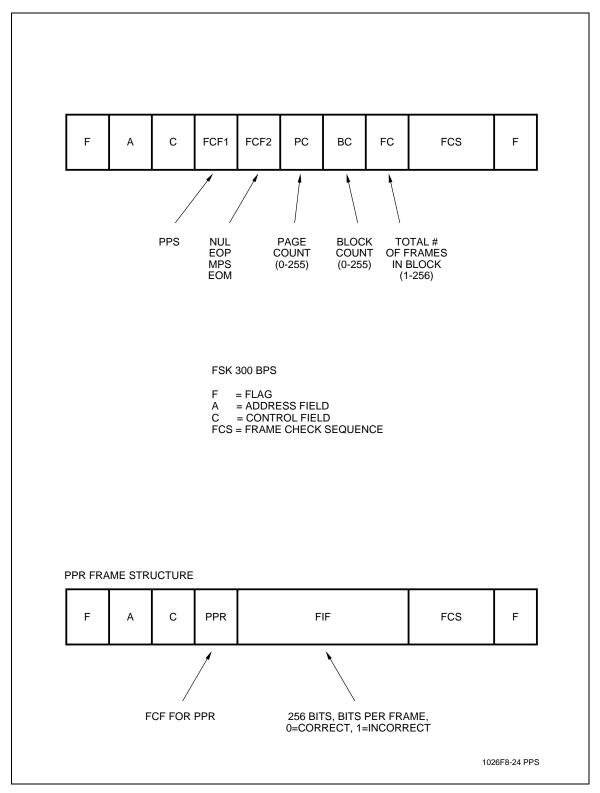

| Figure 8-24. PPS and PPR Frame Structure                          | 8-27  |

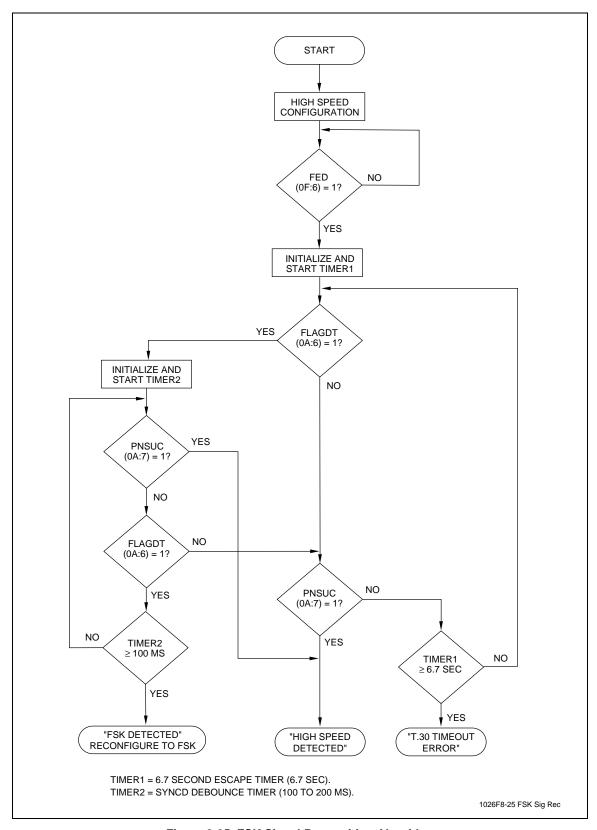

| Figure 8-25. FSK Signal Recognition Algorithm                     | 8-28  |

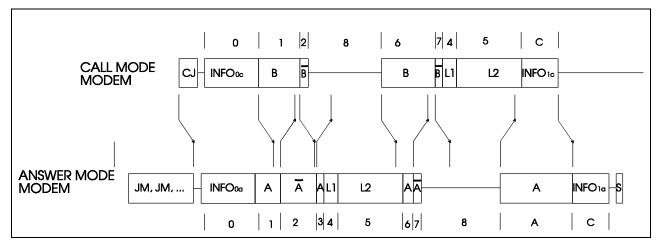

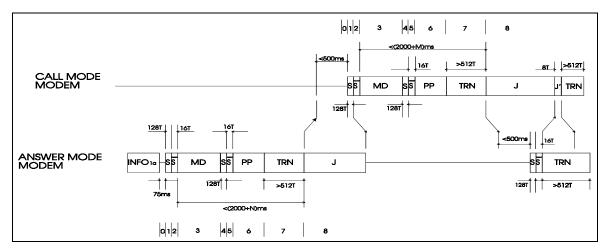

| Figure 9-1. Phase 2 Receiver States                               | 9-6   |

| Figure 9-2. Phase 2 Transmitter States                            | 9-6   |

| Figure 9-3. Phase 3 States                                        | 9-7   |

| Figure 9-4. Phase 4 States                                        | 9-7   |

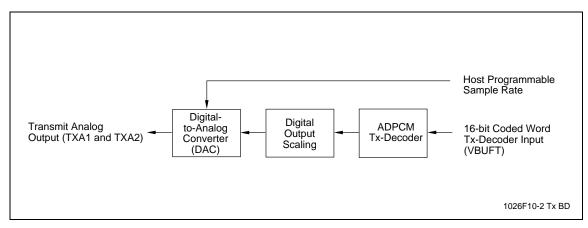

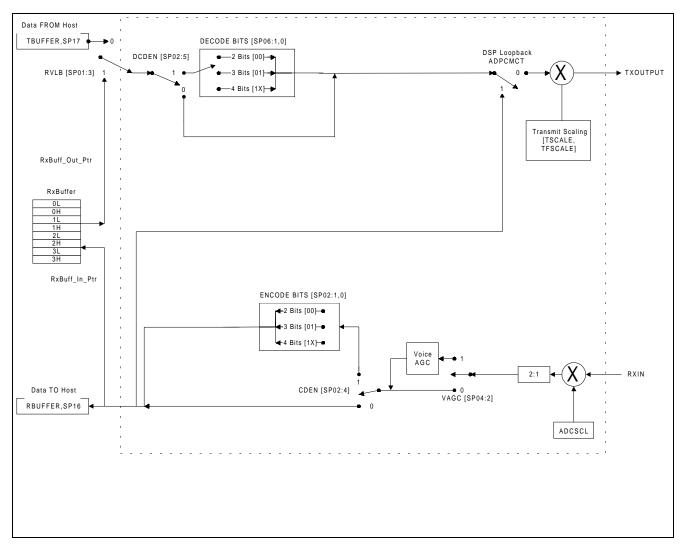

| Figure 11-1. ADPCM Rx-Coder                                       | 11-2  |

| Figure 11-2. ADPCM Tx-Decoder                                     | 11-2  |

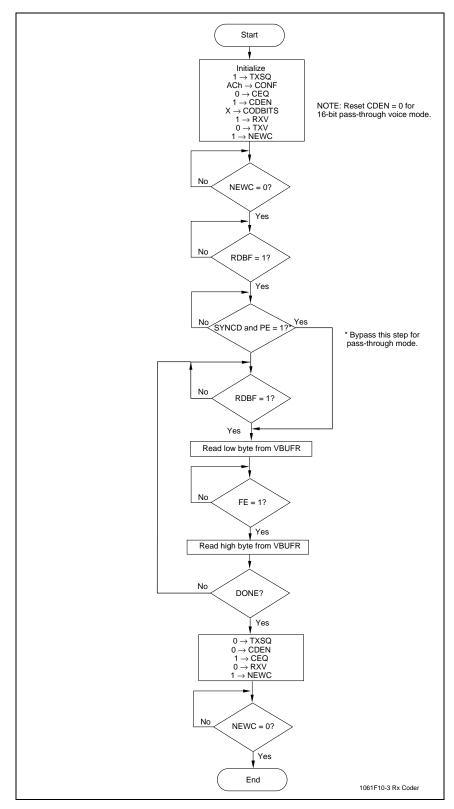

| Figure 11-3. Rx-Coder Operation                                   | 11-3  |

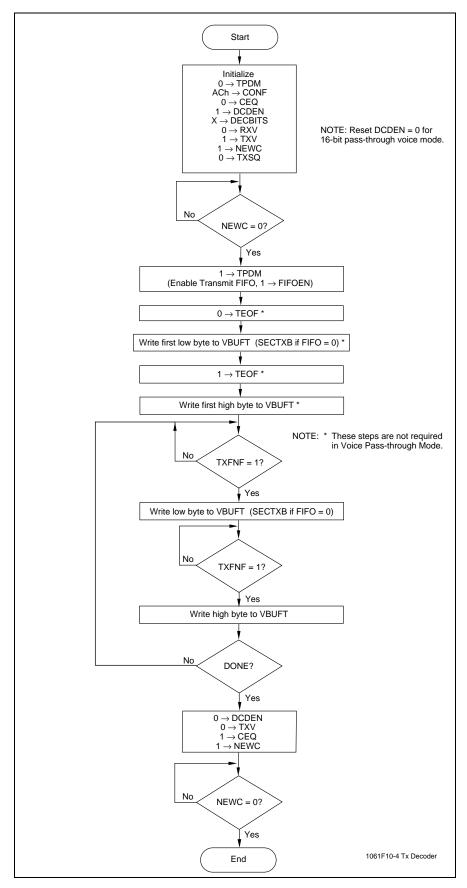

| Figure 11-4. Tx-Decoder Operation                                 | 11-4  |

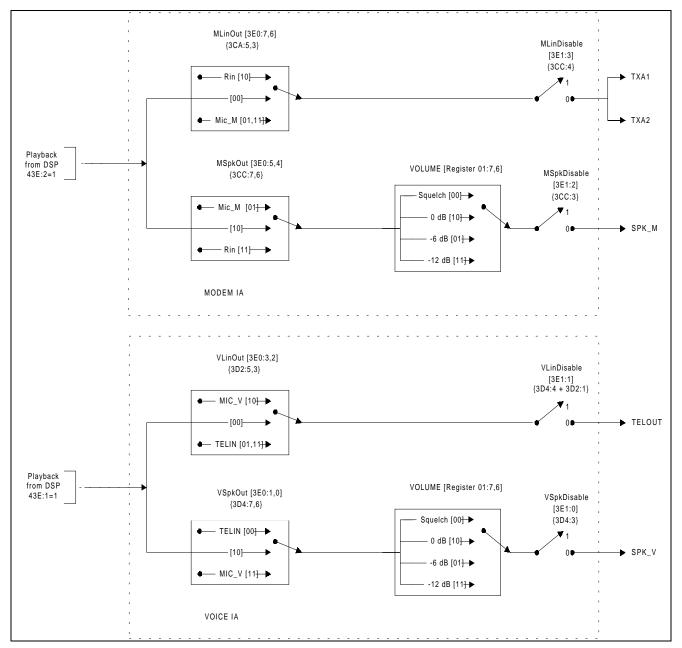

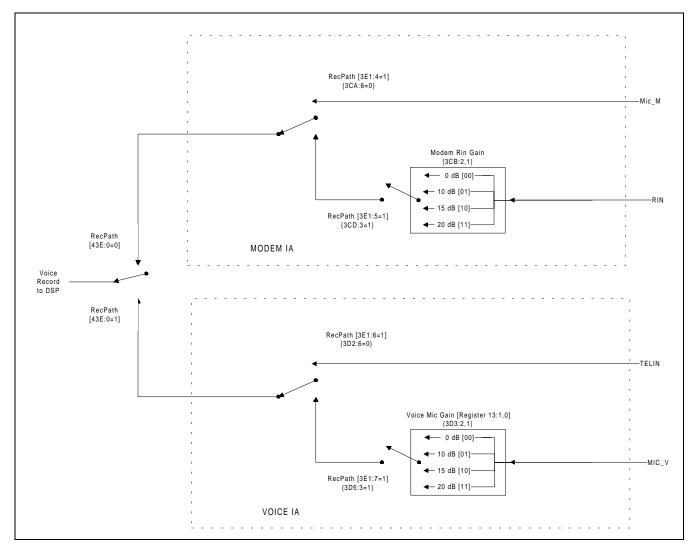

| Figure 12-1. Voice Flow Block Diagram                             | 12-2  |

| Figure 12-2. Transmit Voice Paths                                 | 12-3  |

| Figure 12-3. Receiver Voice Paths                                 | 12-4  |

| Figure 12-4. Voice Mode, Tone Detection and Tone Generation Paths | 12-9  |

| Figure 16-1. Bi-Modal Server: Answer                              | 16-15 |

| Figure 16-2. Bi-Modal Server: Originate                           | 16-16 |

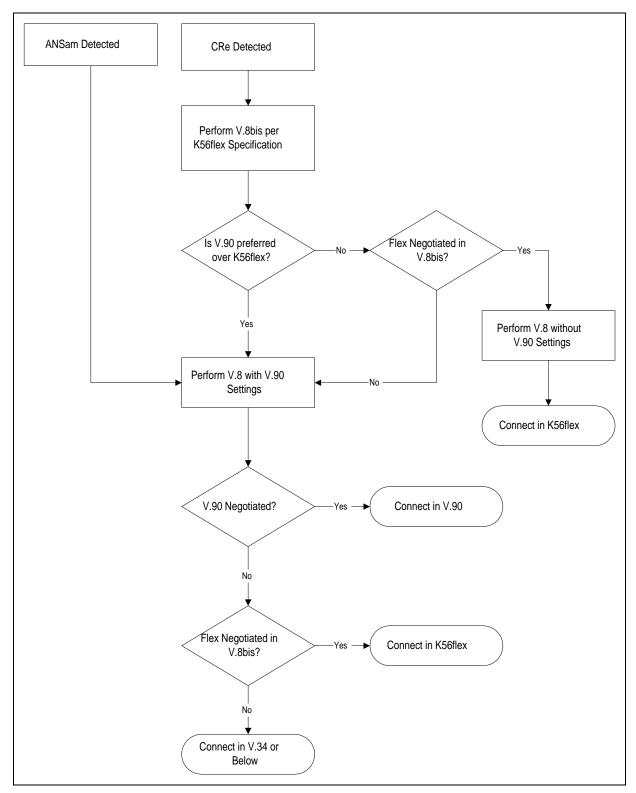

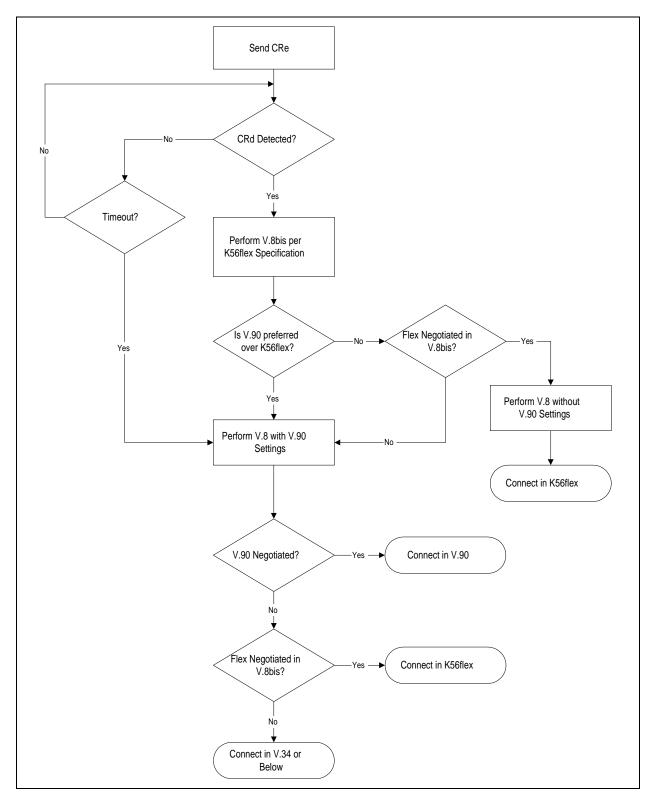

| Figure 16-3. Bi-Modal Client: Originate                           | 16-17 |

| Figure 16-4. Bi-Modal Client: Answer                              | 16-18 |

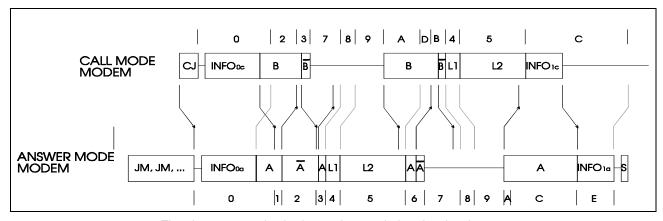

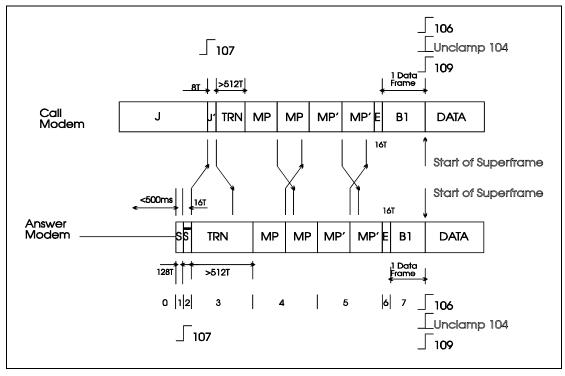

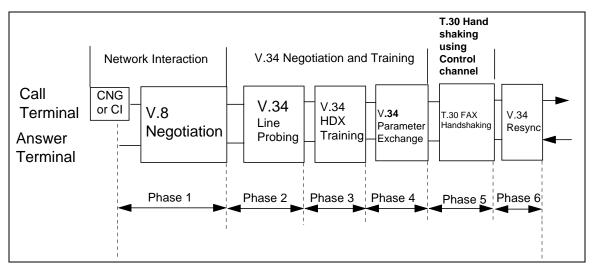

| Figure 17-1. V.34 Fax Starting Sequence                           |       |

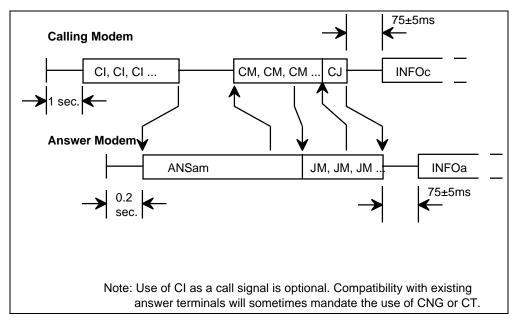

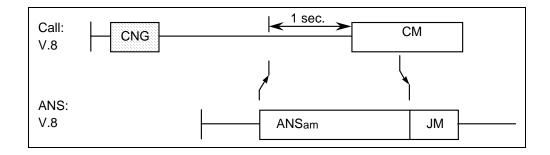

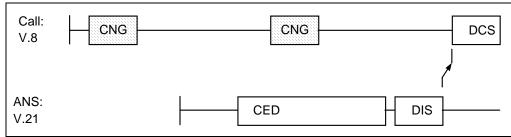

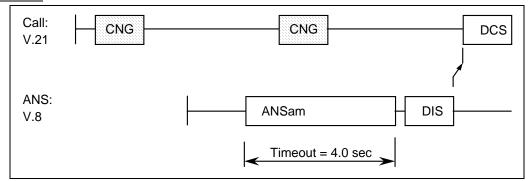

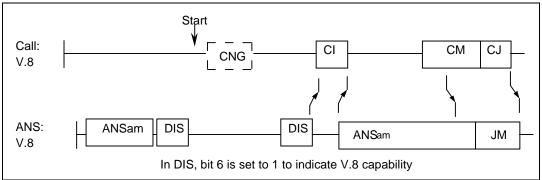

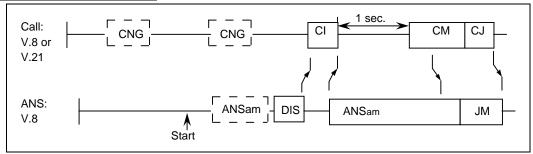

| Figure 17-2. V.8 Procedures - Phase 1 Exchange                    | 17-2  |

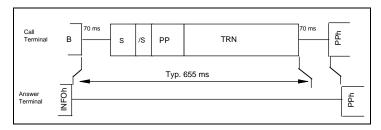

| Figure 17-3. V.34 Line Probing (Phase 2)                          |       |

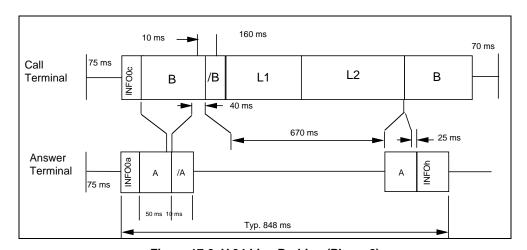

| Figure 17-4. V34 HDX Training Procedure (Phase 3)                 | 17-3  |

| Figure 17-5. V34 Parameter Exchange                               | 17-3  |

| Figure 17-6. T.30 Fax Handshaking (Phase 5)                       |       |

| Figure 17-7. Inter-Page Procedure                                 | 17-4  |

| Figure 17-8. Automatic to Automatic Origination and Operation     |       |

| Figure 17-9. Configuration Procedures                             |       |

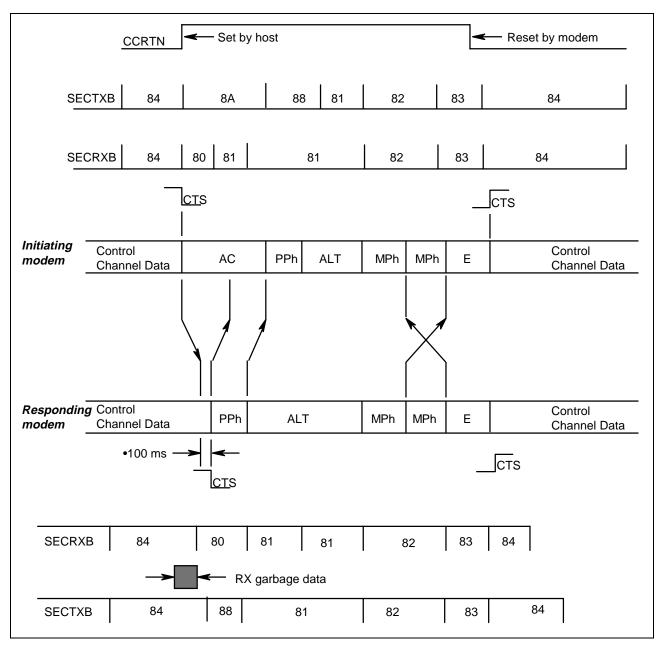

| Figure 17-10. Control Channel Retrain Timing                      | 17-21 |

# **List of Tables**

| Table 1-1. Modem Models and Functions                                        | 1-2  |

|------------------------------------------------------------------------------|------|

| Table 1-2. Configurations, Signaling Rates, and Data Rates                   | 1-5  |

| Table 1-3. RTS-CTS Response Times                                            | 1-6  |

| Table 2-1. MDP Pin Signals - 144-Pin TQFP                                    | 2-5  |

| Table 2-2. MDP Pin Signals - 100-Pin PQFP                                    | 2-9  |

| Table 2-3. MDP Signal Definitions                                            | 2-11 |

| Table 2-4. Digital Electrical Characteristics                                | 2-16 |

| Table 2-5. Analog Electrical Characteristics                                 | 2-16 |

| Table 2-6. Current and Power Requirements                                    | 2-17 |

| Table 2-7. Absolute Maximum Ratings                                          | 2-17 |

| Table 2-8. Host Bus Interface Timing                                         | 2-18 |

| Table 3-1. MDP Interface Memory Bit Definitions                              | 3-3  |

| Table 3-2. ABCODE Error Code Definitions                                     | 3-26 |

| Table 4-1. MDP Interface Memory RAM Addresses                                | 4-2  |

| Table 4-2. R and E Rate Sequences - V.32 to V.32 (V32BS = 0)                 | 4-13 |

| Table 4-3. R and E Rate Sequences - V.32 bis to V.32 bis (V32BS = 1)         | 4-13 |

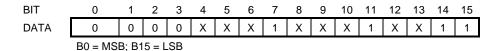

| Table 4-4. TONEA, TONEB, and TONEC DSP RAM Addresses (Hex)                   | 4-19 |

| Table 4-5. TONEA, TONEB, and TONEC Default Values (Hex)                      | 4-19 |

| Table 4-6. Example Tone Detector Filter Coefficients                         | 4-21 |

| Table 4-7. V.34 Rate Sequence Mask Bit Assignments                           | 4-33 |

| Table 4-8. V.34 Remote Modem Data Rate Capability Bit Assignments            | 4-34 |

| Table 6-1. Interrupt Request Bits                                            | 6-2  |

| Table 6-2. Auto Dial Default Values                                          | 6-2  |

| Table 7-1. Modem Pin Noise Characteristics                                   |      |

| Table 7-2. Crystal Specifications - 28.224 MHz                               | 7-5  |

| Table 7-3. Crystal Specifications - 56.448 MHz                               | 7-6  |

| Table 9-1. V.8 Host Control Bits                                             | 9-2  |

| Table 9-2. V.8 Status Bits                                                   | 9-2  |

| Table 9-3. Modulation Modes                                                  | 9-3  |

| Table 9-4. Automode Parameters                                               | 9-3  |

| Table 9-5. Receiver Handshake Phase and States                               | 9-4  |

| Table 9-6. Transmitter Handshake Phase and States                            | 9-5  |

| Table 10-1. V.8 bis Codewords                                                | 10-1 |

| Table 11-1. ADPCM Voice Mode Selection                                       | 11-2 |

| Table 11-2. Voice AGC Parameters                                             | 11-5 |

| Table 12-1. DTMF Routing                                                     | 12-7 |

| Table 12-2. Dual Tone Frequency Parameters                                   | 12-7 |

| Table 14-1. K56flex Data Rate Versus Configuration and Data Rate Mask Values | 14-2 |

| Table 14-2. K56flex Data Rate Versus Speed Bit Values                        | 14-2 |

| Table 14-3. ARA Values                                                       | 14-7 |

| Table 15-1. MDP DSP (SPX) Devices Supporting V.90                            |      |

| Table 15-2. Client APCM and Server DPCM Rates                                | 15-4 |

|                                                                              |      |

| Table 15-3. Server DPCM Transmit Data Rate Mask                                        | 15-5  |

|----------------------------------------------------------------------------------------|-------|

| Table 15-4. Client APCM Transmit Data Rate Mask and Server DPCM Receive Data Rate Mask | 15-6  |

| Table 15-5. APCM and DPCM Maximum Receive Data Rate                                    | 15-7  |

| Table 15-6. V.90 Data Rates vs. EQM Sum                                                | 15-10 |

| Table 17-1. V.8 Host Control Registers                                                 | 17-16 |

| Table 17-2. V.8 Status Registers                                                       | 17-16 |

| Table 17-3. Modulation Modes                                                           | 17-16 |

| Table 17-4. Call Functions Allowed                                                     | 17-17 |

| Table 17-5. Receiver Handshake Phase and States                                        | 17-18 |

| Table 17-6. Transmitter Handshake Phase and States                                     | 17-18 |

| Table 17-7. Status Codes                                                               | 17-19 |

1155 xi

This page is intentionally blank.

xii 1155

#### 1. INTRODUCTION

#### 1.1 SUMMARY

The Rockwell RP56LD/RP336LD and RP56D/RP336D Modem Data Pump (MDP) families support high speed data, high speed fax, AudioSpan, voice coding/decoding, full-duplex speakerphone (optional), and AudioSpan (optional) functions depending upon model (Table 1-1). The RP56D/RP336D, with low voltage operation and small footprint support desktop applications. The RP56LD/RP336LD, with low voltage operation and low power consumption support portable applications. Downloadable architecture allows upgrading of MDP code from the host/DTE. The RP56LD/RP56D supports ITU-T V.90, K56flex™, and V.34 data modem operation. The RP336LD/RP336D supports V.34 data modem operation. Other than power consumption, models of the RP56LD/RP336LD are identical to like models of the RP56D/RP336D. Other than not supporting V.90, RP336LD/RP336D are identical to corresponding RP56LD/RP56D models.

V.90/K56flex MDPs can receive data at speeds up to 56 kbps from a digitally connected V.90- or K56flex-compatible central site modem. These MDPs take advantage of the PSTN which is primarily digital except for the client modem to central office local loop and are ideal for applications such as remote access to an Internet service provider (ISP), on-line service, or corporate site. The MDP can send upstream data at speeds up to V.34 rates.

In V.34 data mode, the MDP can operate in 2-wire, full-duplex, synchronous/asynchronous modes at rates up to 33600 bps. Using V.34 techniques to optimize modem configuration for line conditions, the MDP can connect at the highest data rate that the channel can support from 33600 bps to 2400 bps with auto-fallback to V.32 bis.

Internal HDLC support eliminates the need for an external serial input/output (SIO) device in the DTE for products incorporating error correction and T.30 protocols.

Voice mode includes an Adaptive Differential Pulse Code Modulation (ADPCM) voice coder and decoder (codec). The codec compresses and decompresses voice signals for efficient digital storage of voice messages. The codec operates at 28.8k, 21.6k, or 14.4k bps (4-bit, 3-bit, or 2-bit quantization, respectively) with a 7.2 kHz or 8.0 kHz sample rate.

A voice pass-through mode allows the host to transmit and receive uncompressed voice samples in 16-bit linear form at 7.2 kHz, 8.0 kHz, or 11.025 kHz sample rate, or in 8-bit A-Law/ $\mu$ -Law PCM form at 8.0 kHz sample rate.

SP models support position-independent full-duplex speakerphone (FDSP) operation using a dual internal integrated analog circuit to interface with the telephone line and the audio input/out (i.e., a headset, handset, or a microphone with external speaker).

144-pin TQFP models also support a 4-line voice serial interface used to transfer 16-bit linear or 8-bit A-Law/μ-Law PCM FDSP voice samples with acoustic echo cancellation to and from the host. This interface can be used by the host to support concurrent voice and data modem applications such as host-based DSVD.

AudioSpan (analog simultaneous audio/voice and data) operation supports at a data rate of 4.8 kbps.

The MDP operates over the public switched telephone network (PSTN) through the appropriate line termination.

1155

**Table 1-1. Modem Models and Functions**

| Modem/Part Number <sup>1</sup> |          | Package and Package Options |                        |                                | Supported Functions <sup>2</sup> |                                                      |      |                           |

|--------------------------------|----------|-----------------------------|------------------------|--------------------------------|----------------------------------|------------------------------------------------------|------|---------------------------|

| Model Number                   | Part No. | Package                     | Crystal/Clock<br>Input | Analog<br>Interface<br>Voltage | V.90/K56flex<br>Data             | V.34 Data,<br>V.34 Fax,<br>Voice/Audio,<br>AudioSpan | FDSP | Voice Serial<br>Interface |

| RP56LD/SP                      | R6764-21 | 100-Pin PQFP                | Clock                  | +3.3V                          | Y                                | Y                                                    | Y    | -                         |

| RP56LD                         | R6764-23 | 100-Pin PQFP                | Clock                  | +3.3V                          | Υ                                | Υ                                                    | -    | _                         |

| RP336LD/SP                     | R6764-26 | 100-Pin PQFP                | Clock                  | +3.3V                          | _                                | Υ                                                    | Υ    | -                         |

| RP336LD                        | R6764-27 | 100-Pin PQFP                | Clock                  | +3.3V                          | _                                | Υ                                                    | _    | -                         |

| RP56LD/SP                      | R6785-21 | 144-Pin TQFP                | Clock/Crystal          | +3.3V/+5V                      | Υ                                | Υ                                                    | Υ    | Υ                         |

| RP56LD                         | R6785-23 | 144-Pin TQFP                | Clock/Crystal          | +3.3V/+5V                      | Υ                                | Υ                                                    | -    | Υ                         |

| RP336LD/SP                     | R6785-26 | 144-Pin TQFP                | Clock/Crystal          | +3.3V/+5V                      | -                                | Υ                                                    | Υ    | Υ                         |

| RP336LD                        | R6785-27 | 144-Pin TQFP                | Clock/Crystal          | +3.3V/+5V                      | _                                | Υ                                                    | _    | Υ                         |

### Notes:

1. Model/part number options:

L Low power

D Downloadable

SP Speakerphone.

2. Supported functions (Y = Supported; – = Not supported):

FDSP Full-duplex speakerphone

Voice/Audio Voice and audio

AudioSpan Analog simultaneous voice and data.

1-2

### 1.2 FEATURES

- Downloadable MDP code from the host/DTE

- 2-wire full-duplex

- ITU-T V.90 and K56flex (RP56 models), V.34 (33.6 kbps), V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21

- Bell 212 and 103

- 2-wire half-duplex

- ITU-T V.34 fax, V.17, V.33, V.29, V.27 ter, and V.21 channel 2

- Bell 208

- Short train option in V.17 and V.27 ter

- Serial synchronous and asynchronous data

- Parallel synchronous and asynchronous data

- Parallel synchronous SDLC/HDLC support

- In-band secondary channel (V.34 and V.32 bis)

- Automatic mode selection (AMS)

- Automatic rate adaption (ARA)

- Digital near-end and far-end echo cancellation

- Bulk delay for satellite transmission

- Auto-dial and auto-answer

- ADPCM voice mode (7.2 kHz or 8.0 kHz)

- Voice pass-through mode (7.2 kHz, 8.0 kHz, or 11.025 kHz)

- Full-duplex speakerphone (SP models)

- Acoustic and line echo cancellation

- Programmable microphone AGC

- Microphone volume selection and muting

- Speaker volume control and muting; room monitor

- Voice serial data interface (144-pin TQFP)

- 16-bit linear or 8-bit A-Law/μ-Law PCM voice samples

- FDSP support with acoustic echo cancellation

- AudioSpan

- ITU-T V.61 modulation (4.8 kbps data plus audio)

- Handset, headset, or half-duplex speakerphone

- TTL and CMOS compatible DTE interface

- ITU-T V.24 (EIA/TIA-232-E) (data/control)

- Microprocessor bus (data/configuration/control)

- Dynamic range: -9 dBm to -43 dBm

- Adjustable speaker output to monitor received signal

- DMA support interrupt lines

- Transmit and receive (16+128)-byte FIFO data buffers for burst data transfer

- NRZI encoding/decoding

- 511 pattern generation/detection

- V.8 and V.8 bis signaling

- V.13 signaling

- Diagnostic capability

- V.54 inter-DCE signaling

- V.54 local analog and remote digital loopback

- +3.3V operation with +5V tolerant inputs

- +5V or +3.3V analog signal interface

- Low profile, small footprint package meets PCMCIA Type II envelope requirements for PC Cards

- 100-pin PQFP or 144-pin TQFP

1155

### 1.3 TECHNICAL DESCRIPTION

#### **Configurations and Rates**

The selectable MDP configurations, signaling rates, and data rates are listed in Table 1-2.

#### **Automatic Mode Selection**

When automatic mode selection (AMS) is enabled, the MDP configures itself to the highest compatible data rate supported by the remote modem (AUTO bit). Automode operation is supported in V.90, K56flex, V.34, V.32 bis, V.32 V.22 bis, V.22, V.21, V.23, Bell 212A, and Bell 103 modes.

NOTE: Bit names refer to data, control, and/or status bits in the MDP interface memory (see Table 3-1).

#### **Automatic Rate Adaption (ARA)**

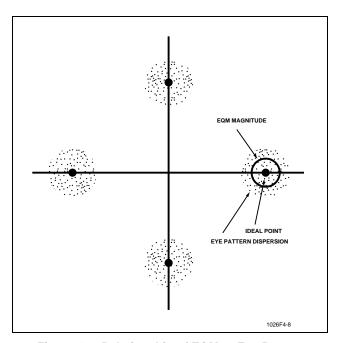

In K56flex, V.34, and V.32 bis modes, automatic rate adaption (ARA) can be enabled to select the highest data rate possible based on the measured eye quality monitor (EQM) (EARC bit). This selection occurs during handshake/retrain and rate renegotiation.

#### **Tone Generation**

The MDP can generate single or dual voice-band tones from 0 Hz to 3600 Hz with a resolution of 0.15 Hz and an accuracy of  $\pm$  0.01%. Tones over 3000 Hz are attenuated. DTMF tone generation allows the MDP to operate as a programmable DTMF dialer.

#### **Data Encoding**

The data encoding conforms to ITU-T recommendations V.90, V.34, V.32 bis, V.32, V.17, V.33, V.29, V.27 ter, V.22 bis, V.22, V.23, or V.21, and is compatible with Bell 208, 212A, or 103, depending on the configuration.

#### **RTS - CTS Response Time**

The response times of CTS relative to a corresponding transition of RTS are listed Table 1-3.

#### **Transmit Level**

The transmitter output level is selectable from -4 dBm to -19 dBm (VAA =  $\pm 3.3$ V) or 0 dBm to -15 dBm (VAA =  $\pm 5$ V) in 1 dB steps and is accurate to  $\pm 0.5$  dB when used with an external hybrid. The output level can also be fine tuned by changing a gain constant in MDP DSP RAM. The maximum V.34/V.32 bis/V.32 transmit level for acceptable receive performance should not exceed -9 dBm.

**Note:** In V.34 mode, the transmit level may be automatically changed during the handshake. This automatic adjustment of the transmit level may be disabled via a parameter in DSP RAM.

#### **Transmitter Timing**

Transmitter timing is selectable between internal (±0.01%), external, or slave.

#### Scrambler/Descrambler

A self-synchronizing scrambler/descrambler is used in accordance with the selected configuration.

#### **Answer Tone**

When the NV25 bit is a zero, the MDP generates a 2100 Hz answer tone at the beginning of the answer handshake for 5.0 seconds (V.8) or 3.6 seconds (V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21). The answer tone has 180° phase reversals every 0.45 second to disable network echo cancellers (V.8, V.32 bis, V.32).

1-4 1155

Table 1-2. Configurations, Signaling Rates, and Data Rates

| Configuration                       | Modulation | Carrier Frequency<br>(Hz) ±0.01% | Data Rate (bps)<br>±0.01%      | Symbol Rate<br>(Symbols/Sec.) | Bits/Symbol<br>- Data | Bits/Symbol<br>- TCM | Constellation<br>Points |

|-------------------------------------|------------|----------------------------------|--------------------------------|-------------------------------|-----------------------|----------------------|-------------------------|

| V.90/K56flex PCM                    | PCM        | -                                | 56000R/V.34ratesT <sup>4</sup> | 8000                          | Dynamic               | -                    | -                       |

| V.34 33600 TCM                      | TCM        | Note 2                           | 33600                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 31200 TCM                      | ТСМ        | Note 2                           | 31200                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 28800 TCM                      | TCM        | Note 2                           | 28800                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 26400 TCM                      | ТСМ        | Note 2                           | 26400                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 24000 TCM                      | TCM        | Note 2                           | 24000                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 21600 TCM                      | TCM        | Note 2                           | 21600                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 19200 TCM                      | TCM        | Note 2                           | 19200                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 16800 TCM                      | TCM        | Note 2                           | 16800                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 14400 TCM                      | TCM        | Note 2                           | 14400                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 12000 TCM                      | TCM        | Note 2                           | 12000                          | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 9600 TCM                       | TCM        | Note 2                           | 9600                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 7200 TCM                       | TCM        | Note 2                           | 7200                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 4800 TCM                       | TCM        | Note 2                           | 4800                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.34 2400 TCM                       | TCM        | Note 2                           | 2400                           | Note 2                        | Note 2                | Note 2               | Note 2                  |

| V.32 bis 14400 TCM                  | TCM        | 1800                             | 14400                          | 2400                          | 6                     | 1                    | 128                     |

| V.32 bis 12000 TCM                  | TCM        | 1800                             | 12000                          | 2400                          | 5                     | 1                    | 64                      |

| V.32 bis 9600 TCM                   | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.32 bis 7200 TCM                   | TCM        | 1800                             | 7200                           | 2400                          | 3                     | 1                    | 16                      |

| V.32 bis 4800                       | QAM        | 1800                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.32 9600 TCM                       | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.32 9600                           | QAM        | 1800                             | 9600                           | 2400                          | 4                     | 0                    | 16                      |

| V.32 4800                           | QAM        | 1800                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.22 bis 2400                       | QAM        | 1200/2400                        | 2400                           | 600                           | 4                     | 0                    | 16                      |

| V.22 bis 1200                       | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| V.22 1200                           | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| V.22 600                            | DPSK       | 1200/2400                        | 600                            | 600                           | 1                     | 0                    | 4                       |

| V.23 1200/75                        | FSK        | 1700/420                         | 1200/75                        | 1200                          | 1                     | 0                    | _                       |

| V.21                                | FSK        | 1080/1750                        | 0–300                          | 300                           | 1                     | 0                    | _                       |

| Bell 208 4800                       | DPSK       | 1800                             | 4800                           | 1600                          | 3                     | 0                    | 8                       |

| Bell 212A                           | DPSK       | 1200/2400                        | 1200                           | 600                           | 2                     | 0                    | 4                       |

| Bell 103                            | FSK        | 1170/2125                        | 0–300                          | 300                           | 1                     | 0                    | _                       |

| V.23 1200/75                        | FSK        | 1700/420                         | 1200/75                        | 1200                          | 1                     | 0                    | _                       |

| V.21                                | FSK        | 1080/1750                        | 0-300                          | 300                           | 1                     | 0                    | _                       |

|                                     | TCM        | 1800                             | 14400                          | 2400                          | 6                     | 1                    | 128                     |

| V.17 14400 TCM/V.33 <sup>3</sup>    |            |                                  |                                |                               | _                     |                      |                         |

| V.17 12000 TCM/V.33 <sup>3</sup>    | TCM        | 1800                             | 12000                          | 2400                          | 5                     | 1                    | 64                      |

| V.17 9600 TCM <sup>3</sup>          | TCM        | 1800                             | 9600                           | 2400                          | 4                     | 1                    | 32                      |

| V.17 7200 TCM <sup>3</sup>          | TCM        | 1800                             | 7200                           | 2400                          | 3                     | 1                    | 16                      |

| V.29 9600 <sup>3</sup>              | QAM        | 1700                             | 9600                           | 2400                          | 4                     | 0                    | 16                      |

| V.29 7200 <sup>3</sup>              | QAM        | 1700                             | 7200                           | 2400                          | 3                     | 0                    | 8                       |

| V.29 4800 <sup>3</sup>              | QAM        | 1700                             | 4800                           | 2400                          | 2                     | 0                    | 4                       |

| V.27 4800 <sup>3</sup>              | DPSK       | 1800                             | 4800                           | 1600                          | 3                     | 0                    | 8                       |

| V.27 4000<br>V.27 2400 <sup>3</sup> | DPSK       | 1800                             | 2400                           | 1200                          | 2                     | 0                    | 4                       |

| V.21 Channel 2 <sup>3</sup>         | FSK        | 1750                             | 300                            | 300                           | 1                     | 0                    | _                       |

| Tone Transmit                       | _          | _                                |                                | _                             | _                     | _                    | _                       |

## Notes:

1. Modulation legend: TCM: Trellis-Coded Modulation QAM: Quadrature Amplitude Modulation FSK: Frequency Shift Keying DPSK: Differential Phase Shift Keying

2. Adaptive; established during handshake:

| Symbol Rate (Baud) | V.34 Low Carrier Frequency (Hz) | V.34 High Carrier Frequency (Hz) |

|--------------------|---------------------------------|----------------------------------|

| 2400               | 1600                            | 1800                             |

| 2800               | 1680                            | 1867                             |

| 3000               | 1800                            | 2000                             |

| 3200               | 1829                            | 1920                             |

| 3429               | 1959                            | 1959                             |

3. Models with fax support only.

4. Maximum data rate.

1155

Table 1-3. RTS-CTS Response Times

|                                     | RTS-CTS          | Response <sup>1</sup> |                                |

|-------------------------------------|------------------|-----------------------|--------------------------------|

| Configuration                       | Constant Carrier | Controlled Carrier    | Turn-Off Sequence <sup>3</sup> |

| V.90, K56flex, V.34, V.32 bis, V.32 | ± 2 ms           | N/A                   | N/A                            |

| V.33/V.17 Long                      | N/A              | 1393 ms <sup>2</sup>  | 15 ms <sup>4</sup>             |

| V.33/V.17 Short                     | N/A              | 142 ms <sup>2</sup>   | 15 ms <sup>4</sup>             |

| V.29                                | N/A              | 253 ms <sup>2</sup>   | 12 ms                          |

| V.27 4800 Long                      | N/A              | 708 ms <sup>2</sup>   | 7 ms <sup>4</sup>              |

| V.27 4800 Short                     | N/A              | 50 ms <sup>2</sup>    | 7 ms <sup>4</sup>              |

| V.27 2400 Long                      | N/A              | 943 ms <sup>2</sup>   | 10 ms <sup>4</sup>             |

| V.27 2400 Short                     | N/A              | 67 ms <sup>2</sup>    | 10 ms <sup>4</sup>             |

| V.22 bis, V.22, Bell 212A           | ± 2 ms           | 270 ms                | N/A                            |

| V.21                                | 500 ms           | 500 ms                | N/A                            |

| V.23, Bell 103                      | 210 ms           | 210 ms                | N/A                            |

#### Notes:

- 1. Times listed are CTS turn-on. The CTS OFF-to-ON response time is host programmable in DSP RAM. (Full-duplex modes only.)

- 2. Add echo protector tone duration plus 20 ms when echo protector tone is used during turn-on.

- 3. Turn-off sequence consists of transmission of remaining data and scrambled ones for controlled carrier operation. CTS turn-off is less than 2 ms for all configurations.

- 4. Plus 20 ms of no transmitted energy.

- 5. N/A = not applicable.

#### Receive Level

The MDP satisfies performance requirements for received line signal levels from –9 dBm to –43 dBm measured at the Receiver Analog (RXA) (TIP and RING) input (-15 dBm at RIN).

Note: A 6 dB pad is required between TIP and RING and the RIN input.

#### **Receiver Timing**

The timing recovery circuit can track a frequency error in the associated transmit timing source of  $\pm 0.035\%$  (V.22 bis) or  $\pm 0.01\%$  (other configurations).

#### **Carrier Recovery**

The carrier recovery circuit can track a ±7 Hz frequency offset in the received carrier.

#### Clamping

Received Data (RXD) is clamped to a constant mark whenever the Received Line Signal Detector (~RLSD) is off. ~RLSD can be clamped off (RLSDE bit).

#### **Echo Canceller**

A data echo canceller with near-end and far-end echo cancellation is included for 2-wire full-duplex V.34/V.32 bis/V.32 operation. The combined echo span of near and far cancellers can be up to 40 ms. The proportion allotted to each end is automatically determined by the MDP. The delay between near-end and far-end echoes can be up to 1.2 seconds.

V.90 and K56flex echo cancellation is also provided.

#### **ADPCM Voice Mode**

The Adaptive Differential Pulse Code Modulation (ADPCM) voice coder and decoder (codec) compresses and decompresses voice signals for efficient digital storage of voice messages. The codec operates at 28.8k, 21.6k, or 14.4k bps (4-bit, 3-bit, or 2-bit quantization, respectively) with a 7.2 kHz or 8.0 kHz sample rate.

**Transmit Voice.** 16-bit compressed transmit voice can be sent to the MDP ADPCM codec for decompression then to the digital-to-analog converter (DAC) by the host.

1-6

**Receive Voice.** 16-bit received voice samples from the MDP analog-to-digital converter (ADC) can be sent to the ADPCM codec for compression, and then be read by the host.

#### Voice Pass-Through Mode

Voice pass-through mode allows the host to transmit and receive uncompressed voice samples in 16-bit linear form at 7.2 kHz, 8.0 kHz, or 11.025 kHz sample rate, or in 8-bit A-Law/μ-Law PCM form at 8.0 kHz sample rate.

Transmit Voice. Transmit voice samples can be sent to the MDP DAC from the host.

Receive Voice. Received voice samples from the MDP ADC can be read by the host.

#### Voice/Audio Paths

The MDP incorporates a dual integrated analog interface. The voice/audio transmit and receive signals can be routed through several paths. The voice/audio paths are available in the speakerphone mode configuration and are selected through DSP RAM.

The voice/audio input can be taken from one of four different sources: telephone line input (RIN), handset (TELIN), microphone (MICM or MICV).

The speaker output (SPK) can originate from one of five different sources: RIN, TELIN, MICM or MICV or from the MDP's internal voice playback mode.

The voice/audio output may be routed to the telephone line output (TXA1 and TXA2) or handset (TELOUT).

The voice paths can be switched to allow an audio input to be routed to the telephone line output through a variable gain for applications such as music-on-hold.

The "room monitor" mode allows the MDP to receive audio from its surroundings and concurrently transmit the audio to a remote site.

#### Voice Serial Interface (144-Pin TQFP)

A 4-pin serial interface supports the transfer of 16-bit linear or 8-bit A-Law/µ-Law PCM voice samples in full-duplex speakerphone form with acoustic echo cancellation to and from the host. These signals can be used in concurrent voice and data applications such as host-controlled DSVD by the host. Signals supported are Serial Data Output (S8OUT), Serial Data In (SR8IN), Serial Shift Clock (SR4CLK), and Sample Shift Clock (SA4CLK).

Analog voice on the MICV input pin is converted to 16-bit linear or 8-bit A-Law/µ-Law PCM digital voice samples and output on the SR8OUT pin to the host. Digital voice in 16-bit linear or 8-bit A-Law/µ-Law PCM form is received from the host on the SR8IN pin, converted to analog form and routed to the SPK output pin. SA4CLK provides the bit clock used to shift data bits in on the SR8IN pin and out on the SR8OUT pin. SR8CLK provides the frame clock used to synchronize words shifted in on the SR8IN pin and shifted out on the SR8OUT pin.

#### AudioSpan Mode

AudioSpan provides full-duplex analog simultaneous audio/voice and data over a single telephone line at a data rate with audio of 4800 bps using V.61 modulation. AudioSpan can send any type of audio waveform, including music. Data can be sent with or without error correction. The audio/voice interface can be in the form of a headset, handset, or a microphone and speaker (half-duplex speakerphone). Handset echo cancellation is provided.

### **Data Formats**

## Serial Synchronous Data

Data rate: 300-33600 (RP336) or 300-56000 (RP56) bps ±0.01%.

Selectable clock: Internal, external, or slave.

#### **Serial Asynchronous Data**

Data rate: 300-33600 (RP336) or 300-56000 (RP56) bps ±0.01%.

0-300 bps (V.21 and Bell 103);

1200/75 bps (V.23).

Bits per character: 7, 8, 9, 10, or 11.

1155

#### **Parallel Synchronous Data**

Normal sync: 8-bit data for transmit and receive

Data rate: 300-33600 (RP336) or 300-56000 (RP56) bps ±0.01%.

SDLC/HDLC support:

Transmitter: Flag generation, 0 bit stuffing, CRC-16 or CRC-32 generation.

Receiver: Flag detection, 0 bit deletion, CRC-16 or CRC-32 checking.

#### **Parallel Asynchronous Data**

Data rate: 300-33600 (RP336) or 300-56000 (RP56) bps +1% (or 2.3%), -2.5%;

1200, 300, or 75 bps (FSK).

Data bits per character: 5, 6, 7, or 8.

Parity generation/checking: Odd, even, or 9th data bit.

#### Async/Sync and Sync/Async Conversion

An asynchronous-to-synchronous converter is provided in the transmitter and a synchronous-to-asynchronous converter is provided in the receiver. The converters operate in both serial and parallel modes. The asynchronous character format is 1 start bit, 5 to 8 data bits, an optional parity bit, and 1 or 2 stop bits. Valid character size, including all bits, is 7, 8, 9, 10, or 11 bits per character. Two ranges of signaling rates are provided:

- Basic range: +1% to −2.5%

- Extended overspeed range: +2.3% to -2.5%

When the transmitter's converter is operating at the basic signaling rate, no more than one stop bit will be deleted per 8 consecutive characters. When operating at the extended rate, no more than one stop bit will be deleted per 4 consecutive characters. Break handling is performed as described in V.14.

Asynchronous characters are accepted on the TXD serial input and are issued on the RXD serial output.

#### V.54 Inter-DCE Signaling

The MDP supports V.54 inter-DCE signaling procedures in synchronous and asynchronous configurations. Transmission and detection of the preparatory, acknowledgment, and termination phases as defined in V.54 are provided. Three control bits in the transmitter allow the host to send the appropriate bit patterns (V54T, V54A, and V54P bits). Three control bits in the receiver are used to enable one of three bit pattern detectors (V54TE, V54AE, and V54PE bits). A status bit indicates when the selected pattern detector has found the corresponding bit pattern (V54DT bit).

#### V.13 Remote RTS Signaling

The MDP supports V.13 remote RTS signaling. Transmission and detection of signaling bit patterns in response to a change of state in the RTS bit or the ~RTS input signal are provided. The RRTSE bit enables V.13 signaling. The RTSDE bit enables detection of V.13 patterns. The RTSDT status bit indicates the state of the remote RTS signal. This feature may be used to clamp/unclamp the local ~RLSD and RXD signals in response to a change in the remote RTS signal in order to simulate controlled carrier operation in a constant carrier environment. The MDP automatically clamps and unclamps ~RLSD.

#### **Dialing and Answering**

The host can dial and answer using supported DTMF dialing and tone detection functions. The major parameters are host programmable.

1-8

#### **Supervisory Tone Detection**

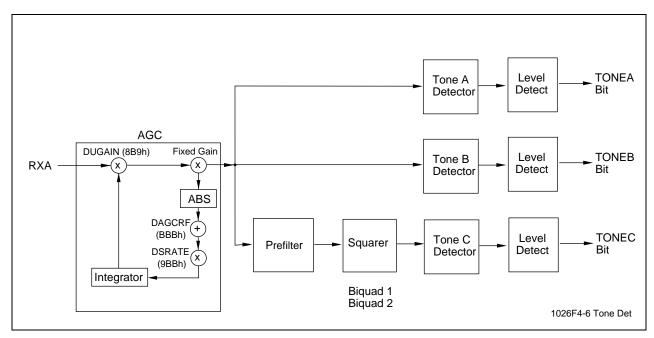

Three parallel tone detectors (A, B, and C) are provided for supervisory tone detection. The signal path to these detectors is separate from the main received signal path.

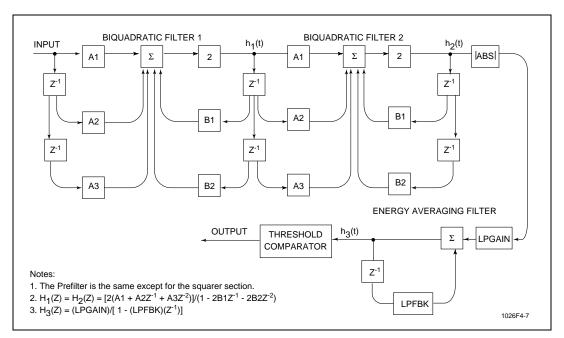

Each tone detector consists of two cascaded second order IIR biquad filters. The coefficients are host programmable. Each fourth order filter is followed by a level detector which has host programmable turn-on and turn-off thresholds allowing hysteresis. Tone detector C is preceded by a prefilter and squarer. This circuit is useful for detecting a tone with frequency equal to the difference between two tones that may be simultaneously present on the line. The squarer may be disabled by the SQDIS bit causing tone detector C to be an eighth order filter. The tone detectors are disabled in data mode.

The tone detection sample rate is 9600 Hz in V.8 and is 7200 Hz in other modes. The default call progress filter coefficients are based on a 7200 Hz sampling rate and apply to non-V.34 modes only. The maximum detection bandwidth is equal to one-half the sample rate. The tone detection sample rate can 7200 Hz or 8000 Hz in voice mode (CONF ACh). The default bandwidths and thresholds of the tone detectors are:

| Tone Detector | Bandwidth    | Turn-On Threshold | Turn-Off Threshold |

|---------------|--------------|-------------------|--------------------|

| Α             | 245 – 650 Hz | –25 dBm           | −31 dBm            |

| В             | 360 – 440 Hz | –25 dBm           | −31 dBm            |

| C Prefilter   | 0 – 500 Hz   | N/A               | N/A                |

| С             | 50 – 110 Hz  | *                 | *                  |

<sup>\*</sup> Tone Detector C will detect a difference tone within its bandwidth when the two tones present are in the range –1 dBm to –26 dBm.

#### 511 Pattern Generation/Detection

In synchronous mode, a 511 pattern can be generated and detected (control bit S511). Use of this bit pattern during self-test eliminates the need for external test equipment.

#### **In-Band Secondary Channel**

A full-duplex in-band secondary channel is provided in V.34 (all speeds) and V.32 bis/V.32 (7200 bps and above) modes. Control bit SECEN enables and disables the secondary channel operation. The secondary channel operates in parallel data mode with independent transmit and receive interrupts and data buffers. The main channel may operate in parallel or serial mode.

In V.34 modes, the secondary channel rate is 200 bps.

In V.32 bis/V.32 modes, the secondary channel rate is 150 bps. This rate is also host programmable in V.32 bis/V.32 modes.

#### **Transmit and Receive FIFO Data Buffers**

Two (16+128)-byte first-in first-out (FIFO) data buffers allow the DTE/host to rapidly output up to 144 bytes of transmit data and input up to 144 bytes of accumulated received data. The receiver FIFO is always enabled. The transmitter FIFO is enabled by the FIFOEN control bit. TXHF and RXHF bits operate off the lower 16 bits and indicate the corresponding FIFO buffer half full (8 or more bytes loaded) status. TXFNF and RXFNE bits indicate the TXFIFO buffer not full and RXFIFO buffer not empty status, respectively. An interrupt mask register allows an interrupt request to be generated whenever the TXFNF, RXFNE, RXHF, or TXHF status bit changes state. The 128-byte FIFO extensions are enabled by default and can be disabled by clearing a bit in RAM. (See Section 4, Function 74.)

#### **DMA Support Interrupt Request Lines**

DMA support is available in synchronous, asynchronous, and HDLC parallel data modes. Control bit DMAE enables and disables DMA support. When DMA support is enabled, the MDP ~RI and ~DSR lines are assigned to Transmitter Request (TXRQ) and Receiver Request (RXRQ) hardware output interrupt request lines, respectively. The TXRQ and RXRQ signals follow the assertion of the TDBE and RDBF interrupt bits thus allowing the DTE/host to respond immediately to the interrupt request without masking out status bits to determine the interrupt source.

#### **NRZI Encoding/Decoding**

NRZI data encoding/decoding may be selected in synchronous and HDLC modes instead of the default NRZ (control bit NRZIEN). In NRZ encoding, a 1 is represented by a high level and a 0 is represented by a low level. In NRZI encoding, a 1 is represented by no change in level and a 0 is represented by a change in level.

1155

#### **ITU-T CRC-32 Support**

ITU-T CRC-32 generation/checking may be selected instead of the default ITU-T CRC-16 in HDLC mode using DSP RAM access.

#### **Caller ID Demodulation**

Caller ID information can be demodulated in V.23 1200 receive configuration and presented to the host/DTE in serial (RXD) and parallel (RBUFFER) form.

**Relay Control.** Direct control of the off-hook and talk/data relays is provided. Internal relay drivers allow direct connection to the off-hook (RLYA) and talk/data (RLYB) relays. The talk/data relay output can optionally be used for pulse dial.

#### **Speaker Interface**

An analog speaker output (SPK) is provided with on/off and volume control logic incorporated in the MDP. An external amplifier is recommended if driving non-amplified speakers.

A digital speaker output (SPKMD) is provided which reflects the received analog input signal digitized to TTL high or low level by an internal comparator to create a PC Card (PCMCIA)-compatible signal. See the VOLUME bits description in Section 3.

1-10 1155

## 2. HARDWARE INTERFACE

#### 2.1 HARDWARE INTERFACE SIGNAL DESCRIPTION

A functional interconnect diagram showing the typical MDP connection in a system is illustrated in Figure 2-1. Any point that is active low is represented by a small circle at the signal point.

Edge triggered inputs are denoted by a small triangle (e.g., TDCLK). An active low signal is indicated by a tilde preceding the signal name (e.g., ~RESET).