# Supply Voltage Supervisor with Watchdog and Manual Reset

### 1 FEATURES

- Operating Voltage Range:1.0V to 5.5V

- Low Power Consumption:40µA (Max)

- Precision Supply-Voltage Monitor: 2.63V, 2.93V, 3.08V, 4.00V

- Debounced TTL/CMOS Compatible Manual-Reset Input

- Guaranteed RESET Valid at V<sub>CC</sub>=1.0V

- 160ms Reset Pulse Width

- Independent Watchdog Timer (1.6sec TYP)

Timeout

- Voltage Monitor for Power-Fail or Low-Battery Warning

- Operating Temperature Range: -40°C to +125°C

- Available in Green Package: SOIC-8(SOP8)

### 2 APPLICATIONS

- Computers

- SOC DSP or Micro Controllers

- Embedded Systems

- Industrial Equipment

- Intelligent Instruments

- Critical µP Power Monitoring

- Wireless Communications Systems

# 3 DESCRIPTIONS

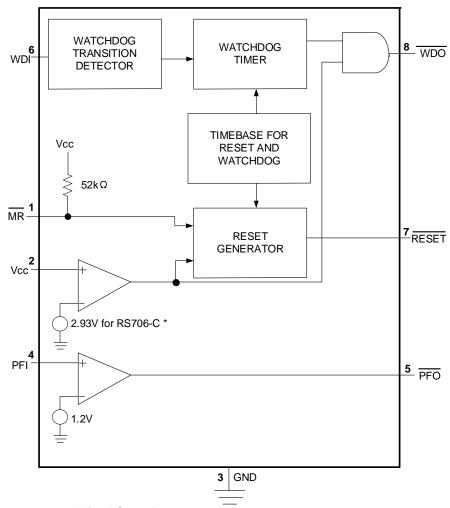

The RS706 microprocessor ( $\mu P$ ) supervisory circuits reduce the complexity and number of components required to monitor power-supply and battery function in  $\mu P$  systems. This device significantly improves system reliability and accuracy compared to separate ICs or discrete components.

The RS706 provide four functions:

- 1) A reset output during power-up, power-down, and brownout conditions. The reset output remains operational with  $V_{\rm CC}$  as low as 1.0V.

- 2) An independent watchdog output that goes low if the watchdog input has not been toggled within 1.6 seconds (TYP).

- 3) A 1.2V threshold detector for power-fail warning, low-battery detection, or for monitoring a power supply.

- 4) An active-low manual-reset input.

The RS706 is available in Green SOIC-8 (SOP8) package. It operates over an ambient temperature range of -40°C to +125°C.

### **Device Information (1)**

| PART<br>NUMBER | PACKAGE      | BODY SIZE (NOM) |

|----------------|--------------|-----------------|

| RS706          | SOIC-8(SOP8) | 4.90mm x 3.90mm |

For all available packages, see the orderable addendum at the end of the data sheet.

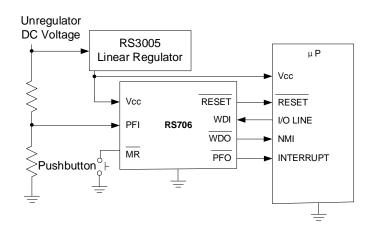

# 4 TYPICAL APPLICATION

# **Table of Contents**

| 1 FEATURES                                                   | 1  |

|--------------------------------------------------------------|----|

| 2 APPLICATIONS                                               | 1  |

| 3 DESCRIPTION                                                | 1  |

| 4 TYPICAL APPLICATION                                        | 1  |

| 5 Revision History                                           | 3  |

| 6 PACKAGE/ORDERING INFORMATION (1)                           | 4  |

| 7 PIN CONFIGURATIONS                                         | 5  |

| 8 Specifications                                             | 6  |

| 8.1 Absolute Maximum Ratings (1)                             | 6  |

| 8.2 ESD Ratings                                              | 6  |

| 8.3 Thermal Information:                                     | 6  |

| 8.4 ELECTRICAL CHARACTERISTICS                               | 7  |

| 8.5 Typical Operating Characteristics                        | 8  |

| 9 Function Block Diagram                                     | 11 |

| 10 Detailed Description                                      | 12 |

| 10.1 Reset Output                                            | 12 |

| 10.2 Watchdog Timer                                          | 12 |

| 10.3 Manual Reset                                            | 12 |

| 10.4 Power-Fail Comparator                                   | 12 |

| 11 Applications Information                                  | 13 |

| 11.1 Ensuring a Valid RESET Output Down to Vcc=0V            | 13 |

| 11.2 Monitoring Voltages Other Than the Unregulated DC Input | 13 |

| 11.3 Interfacing to μPs with Bidirectional Reset Pins        | 13 |

| 12 PACKAGE OUTLINE DIMENSIONS                                | 15 |

| 13 TAPE AND REEL INFORMATION                                 | 16 |

# **5 Revision History**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| Version | Change Date | Change Item                                                                                                                                                                                         |

|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.1     | 2020/12/13  | Initial version completed                                                                                                                                                                           |

| A.2     | 2022/02/22  | 1.Added the maximum value of t <sub>MD</sub> on Page 6@RevA.1<br>2.Modify ELECTRICAL CHARACTERISTICS                                                                                                |

| A.3     | 2022/06/27  | Update Operating Temperature Range: -40°C to +125°C     Update Typical Operating Characteristics     Update Reset Pulse Width typical value     Update V <sub>CC</sub> to RESET delay typical value |

# 6 PACKAGE/ORDERING INFORMATION (1)

| PRODUCT  | ORDERING TEMPERATURE PACKAGE NUMBER RANGE LEAD |               | PACKAGE<br>MARKING (2/3) | PACKAGE OPTION |                    |

|----------|------------------------------------------------|---------------|--------------------------|----------------|--------------------|

|          | RS706-2.63YK                                   | -40°C ~+125°C | SOIC-8(SOP8)             | RS706B         | Tape and Reel,4000 |

| D.C.70.0 | RS706-2.93YK                                   | -40°C ~+125°C | SOIC-8(SOP8)             | RS706C         | Tape and Reel,4000 |

| RS706    | RS706-3.08YK                                   | -40°C ~+125°C | SOIC-8(SOP8)             | RS706D         | Tape and Reel,4000 |

|          | RS706-4.00YK                                   | -40°C ~+125°C | SOIC-8(SOP8)             | RS706E         | Tape and Reel,4000 |

### NOTE:

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) There may be additional marking, which relates to the lot trace code information(data code and vendor code), the logo or the environmental category on the device.

- (3) B, C, D, E, represents different Reset Thresholds.

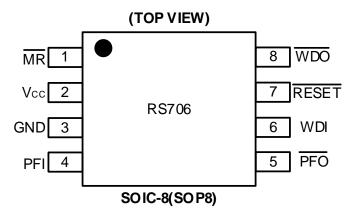

# **7 PIN CONFIGURATIONS**

# **PIN DESCRIPTION**

| PIN          | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOIC-8(SOP8) | NAIVIE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1            | MR     | Manual-Reset Input triggers a reset pulse when pulled below 0.8V. This active-low input has an internal pull-up resistance. It can be driven from a TTL or CMOS logic line as well as shorted to ground with a switch.                                                                                                                                                                                                                      |

| 2            | Vcc    | Power Supply Voltage that is monitored.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3            | GND    | Ground, reference for all signals.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4            | PFI    | Power-Fail Volta Monitor Input. When PFI is less than 1.2V, $\overline{PFO}$ goes low. Connect PFI to GND or V <sub>CC</sub> if not used.                                                                                                                                                                                                                                                                                                   |

| 5            | PFO    | Power-Fail Output goes low and sinks current when PFI is less than 1.2V; Otherwise PFO stays high.                                                                                                                                                                                                                                                                                                                                          |

| 6            | WDI    | Watchdog Input. If WDI remains high or low 1.6sec, the internal watchdog timer runs out and WDO goes low. Floating WDI or connecting WDI to a high-impedance three-state buffer disables the watchdog feature. The internal watchdog timer clears whenever reset is asserted, WDI is three-stated, or WDI sees a rising or falling edge.                                                                                                    |

| 7            | RESET  | Active-Low Reset Output pulses low for 160ms when triggered, and stays low whenever VCC is below the reset threshold. It remains low for 160ms after $V_{CC}$ rises above the reset threshold or $\overline{MR}$ goes from low to high. A watchdog timeout will not trigger $\overline{RESET}$ unless $\overline{WDO}$ is connected to $\overline{MR}$ .                                                                                    |

| 8            | WDO    | Watchdog Output pulls low when the internal watchdog timer finishes, its 1.6sec count and does not go high again until the watchdog is cleared. $\overline{WD0}$ also goes low during low-line conditions. Whenever $V_{CC}$ is below the reset threshold, $\overline{WD0}$ stays low; $\overline{WD0}$ does not have a minimum pulse width. As soon as $V_{CC}$ rises above the reset threshold, $\overline{WD0}$ goes high with no delay. |

# 8 Specifications

# 8.1 Absolute Maximum Ratings (1)

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                  |                                                                                                |                   | MIN  | MAX     | UNIT |

|------------------|------------------------------------------------------------------------------------------------|-------------------|------|---------|------|

| Vcc              | Supply voltage range                                                                           |                   | -0.5 | 6.0     | V    |

| Vı               | Input voltage range (2)                                                                        |                   | -0.5 | 6.0     | V    |

| Vo               | Vo Voltage range applied to any output in the high-impedance or power-off state <sup>(2)</sup> |                   | -0.5 | 6.0     | V    |

| Vo               | Voltage range applied to any output in the high or low s                                       | state (2)(3)      | -0.5 | Vcc+0.5 | V    |

| lıĸ              | Input clamp current                                                                            | V <sub>I</sub> <0 |      | -20     | mA   |

| Іок              | Output clamp current                                                                           | Vo<0              |      | -20     | mA   |

| lo               | Continuous output current                                                                      |                   |      | ±20     | mA   |

|                  | Continuous current through Vcc or GND                                                          |                   |      | ±20     | mA   |

| ТJ               | Junction temperature (4)                                                                       |                   | -65  | 150     | °C   |

| T <sub>stg</sub> | Storage temperature                                                                            |                   | -65  | 150     | °C   |

| TA               | Operating temperature                                                                          |                   | -40  | 125     | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) The input and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.

- (3) The value of V<sub>CC</sub> is provided in the Recommended Operating Conditions table.

- (4) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

# 8.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                                |                         |                                                                   | VALUE | UNIT |

|--------------------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub>             | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±6000 | V    |

| V(ESD) Electrostatic discharge |                         | Machine model (MM)                                                | ±300  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# 8.3 Thermal Information:

|                     |                                              | RS706        |      |

|---------------------|----------------------------------------------|--------------|------|

|                     | THERMAL METRIC (1)                           | 8PINS        | UNIT |

|                     |                                              | SOIC-8(SOP8) |      |

| RөJA                | Junction-to-ambient thermal resistance       | 124.7        | °C/W |

| ReJC(top)           | Junction-to-case(top) thermal resistance     | 66.9         | °C/W |

| Rејв                | Junction-to-board thermal resistance         | 67.9         | °C/W |

| $\Psi_{	extsf{JT}}$ | Junction-to-top characterization parameter   | 19.2         | °C/W |

| $\Psi_{JB}$         | Junction-to-board characterization parameter | 67.2         | °C/W |

| ReJC(bot)           | Junction-to-case(bottom) thermal resistance  | N/A          | °C/W |

<sup>(1)</sup> Thermal resistance varies with operating conditions.

6 / 17 www.run-ic.com

# 8.4 ELECTRICAL CHARACTERISTICS

$(V_{CC} = 1.67 \text{V to } 5.5 \text{V for RS706-} 1.63; V_{CC} = 2.7 \text{V to } 5.5 \text{V for RS706-} 2.63; V_{CC} = 3 \text{V to } 5.5 \text{V for RS706-} 2.93; V_{CC} = 3.16 \text{V to } 5.5 \text{V for RS706-} 3.08; V_{CC} = 4.1 \text{V to } 5.5 \text{V for RS706-} 4.00; V_{CC} = 4.51 \text{V to } 5.5 \text{V for RS706-} 4.40; V_{CC} = 4.77 \text{V to } 5.5 \text{V for RS706-} 4.65; T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted, typical at } 25 ^{\circ}\text{C}.)$

| PARAMETER                              | SYMBOL          | TEST CONDITIONS                                         | MIN                 | TYP  | MAX      | UNIT |  |

|----------------------------------------|-----------------|---------------------------------------------------------|---------------------|------|----------|------|--|

| Operating Voltage Range                | Vcc             |                                                         | 1.0                 |      | 5.5      | V    |  |

| Supply Current                         | ISUPPLY         |                                                         |                     | 20   | 40       | μA   |  |

|                                        |                 | RS706-2.63                                              | 2.56                | 2.63 | 2.7      | .,   |  |

| Decet Three bald                       |                 | RS706-2.93                                              | 2.86                | 2.93 | 3.0      |      |  |

| Reset Threshold                        | $V_{RT}$        | RS706-3.08                                              | 3.0                 | 3.08 | 3.16     | V    |  |

|                                        |                 | RS706-4.00                                              | 3.9                 | 4.0  | 4.1      |      |  |

|                                        |                 | RS706-2.63                                              |                     | 12   |          |      |  |

| Reset Threshold                        |                 | RS706-2.93                                              |                     | 14   |          | >/   |  |

| Hysteresis                             |                 | RS706-3.08                                              |                     | 15   |          | mV   |  |

|                                        |                 | RS706-4.00                                              |                     | 20   |          |      |  |

| Reset Pulse Width                      | t <sub>RS</sub> |                                                         | 100                 | 160  | 350      | ms   |  |

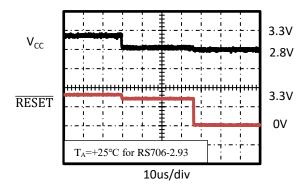

| V <sub>CC</sub> to RESET delay         | t <sub>RD</sub> | Vcc=3.3V, RS706-2.93                                    |                     | 20   |          | μs   |  |

| Watchdog Timeout Period                | t <sub>WD</sub> |                                                         | 1.0                 | 1.6  | 2.9      | s    |  |

| WDI Pulse Width                        | t <sub>WP</sub> | V <sub>IL</sub> =0.4V, V <sub>IH</sub> =V <sub>CC</sub> | 16                  |      |          | ns   |  |

| <del></del>                            | High            | Isource = 500uA                                         | 0.7xVcc             |      |          | V    |  |

| RESET Output voltage                   | Low             | I <sub>SINK</sub> = 1.2mA                               |                     |      | 0.4      |      |  |

|                                        | High            | Vcc=5.0V                                                | 4.0                 |      |          | .,   |  |

| \\/\D\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | Low             | V <sub>CC</sub> =5.0V                                   |                     |      | 0.8      |      |  |

| WDI Input Threshold                    | High            | V <sub>RST(MAX)</sub> < V <sub>CC</sub> < 3.6V          | 0.8xVcc             |      |          | V    |  |

|                                        | Low             | $V_{RST(MAX)} < V_{CC} < 3.6V$                          |                     |      | 0.6      |      |  |

| MDI In a d Occurrent                   |                 | WDI = V <sub>CC</sub>                                   |                     | 0.1  | 1        |      |  |

| WDI Input Current                      |                 | WDI = 0V                                                | -1                  | -0.1 |          | μA   |  |

| IMDO Outsut Valtaria                   | High            | I <sub>SOURCE</sub> = 800uA                             | 0.7xVcc             |      |          | V    |  |

| WDO Output Voltage                     | Low             | I <sub>SINK</sub> = 1.2mA                               |                     |      | 0.4      | V    |  |

| MR Pull-Up Resistor                    |                 |                                                         | 20                  | 52   | 120      | kΩ   |  |

| MR Pulse Width                         | t <sub>MR</sub> |                                                         | 150                 |      |          | ns   |  |

|                                        | High            | V <sub>CC</sub> =5.0V                                   | 4.0                 |      |          |      |  |

| MD lancet Through and                  | Low             | Vcc=5.0V                                                |                     |      | 0.6      | .,   |  |

| MR Input Threshold                     | High            | $V_{RST(MAX)} < V_{CC} < 3.6V$                          | 0.8xV <sub>CC</sub> |      |          | V    |  |

|                                        | Low             | V <sub>RST(MAX)</sub> < V <sub>CC</sub> < 3.6V          |                     |      | 0.15xVcc |      |  |

| MR to Reset Out Delay                  | t <sub>MD</sub> |                                                         |                     | 23   | 200      | ns   |  |

| PFI Input Threshold                    |                 | V <sub>CC</sub> = 5.0V                                  | 1.14                | 1.20 | 1.26     | V    |  |

| PFI Input Current                      |                 |                                                         | -10                 | 0.01 | 10       | nA   |  |

| DEO Outmut Valtaria                    | High            | Isource = 800uA                                         | 0.7xVcc             |      |          | 17   |  |

| PFO Output Voltage                     | Low             | I <sub>SINK</sub> = 1.2mA                               |                     |      | 0.4      | V    |  |

# 8.5 Typical Operating Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

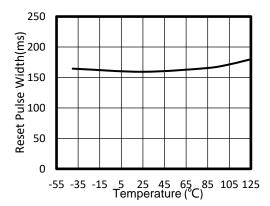

Figure 1. Reset Pulse Width vs Temperature

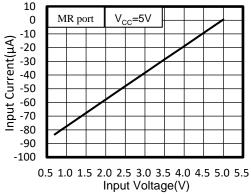

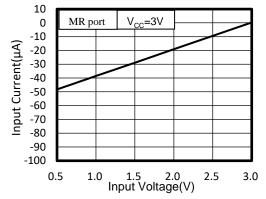

Figure 3. Input Voltage vs Input Current

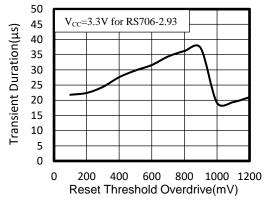

Figure 5. Transient Duration vs Reset

Threshold Overdrive

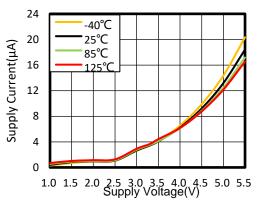

Figure 2. Supply Voltage vs Supply Current

Figure 4. Input Voltage vs Input Current

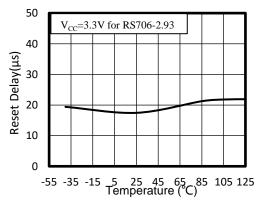

Figure 6. Reset Delay vs Temperature

# **Typical Operating Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

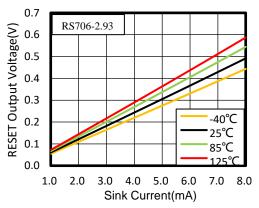

Figure 7. RESET Output Voltage vs Sink Current

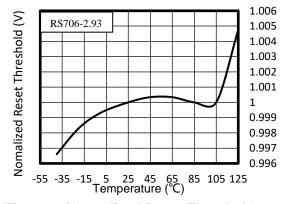

Figure 9. Normalized Reset Threshold vs Temperature

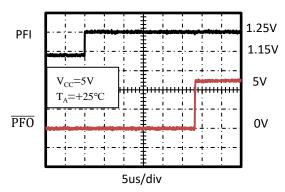

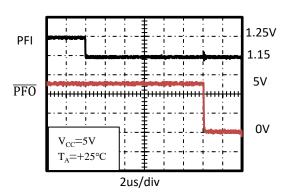

Figure 11. Power-Fail Comparator Deassertion Response Time

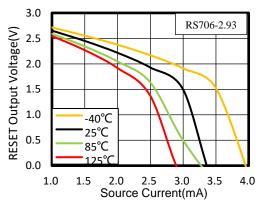

Figure 8. RESET Output Voltage vs Source Current

Figure 10. RESET Output Voltage vs Supply Voltage

Figure 12. Power-Fail Comparator Assertion Response Time

9 / 17 www.run-ic.com

**Typical Operating Characteristics**NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

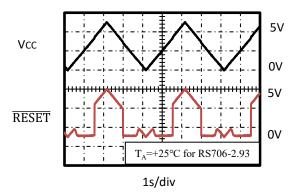

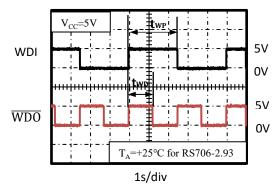

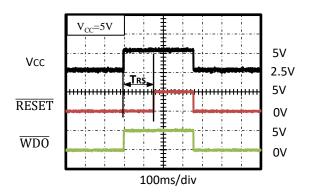

Figure 13. Watchdog Timing

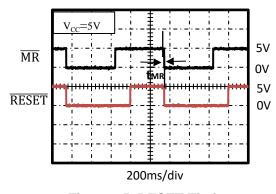

Figure 15. RESET Timing

Figure 14. RESET and WDO Timing

Figure 16. RESET Response Time

# 9 Function Block Diagram

- 2.63V for RS706-B

- \* 2.93V for RS706-C

- 3.08V for RS706-D

- 4.00V for RS706-E

# 10 Detailed Description

### **10.1 Reset Output**

A microprocessor's ( $\mu$ P's) reset input starts the  $\mu$ P in a known state. Whenever the  $\mu$ P is in an unknown state, it should be held in reset. The RS706 assert reset during power-up and prevent code execution errors during power-down or brownout conditions.

On power-up, once  $V_{CC}$  reaches 1.0V,  $\overline{RESET}$  is a guaranteed logic low of 0.4V or less. As  $V_{CC}$  rises,  $\overline{RESET}$  stays low. When  $V_{CC}$  rises above the reset threshold, an internal timer release  $\overline{RESET}$  after about 160ms.  $\overline{RESET}$  pulses low whenever  $V_{CC}$  dips below the reset threshold. If brownout occurs in the middle of a previously initiated reset pulse, the pulse continues for at least another 100ms. On power-down, once  $V_{CC}$  falls below the reset threshold,  $\overline{RESET}$  stays low and is guaranteed to be 0.4V or less until  $V_{CC}$  drops below 1.0V.

# 10.2 Watchdog Timer

The RS706 watchdog circuit monitors the  $\mu P$ 's activity. If the  $\mu P$  does not toggle the watchdog input (WDI) within 1.6 sec (Minimum is 1.0 sec) and WDI is not three stated,  $\overline{WDO}$  goes low. As long as  $\overline{RESET}$  is asserted or the WDI input is three stated, the watchdog timer stays cleared and will not count. As soon as reset is released and WDI is driven high or low, the timer starts counting. Pulses as short as 50ns can be detected.

Typically,  $\overline{WDO}$  is not connected to the non-maskable interrupt input (NMI) of a  $\mu P$ . When  $V_{CC}$  drops below the reset threshold,  $\overline{WDO}$  goes low whether or not the watchdog timer has timed out yet. Normally this would trigger an NMI interrupt, but  $\overline{RESET}$  goes low simultaneously, and thus overrides the NMI interrupt.

If WDI is left unconnected,  $\overline{\text{WDO}}$  can be used as a low-line output. Since floating WDI disable the internal timer,  $\overline{\text{WDO}}$  goes low only when Vcc falls below the reset threshold, thus functioning as a low-line output.

### 10.3 Manual Reset

The manual-reset input  $(\overline{MR})$  allows reset to be triggered by a push-button switch.  $\overline{MR}$  is TTL/CMOS logic compatible, so it can be driven by an external logic line.  $\overline{MR}$  can be used to force a watchdog timeout to generate a reset pulse in the RS706. Simply connect  $\overline{WDO}$  to  $\overline{MR}$ .

### **10.4 Power-Fail Comparator**

The power-fail comparator can be used for various purposes because its output and non-inverting input are not internally connected. The inverting input is internally connected to a 1.2V reference.

To build an early-warning circuit for power failure, connect the PFI pin to a voltage divider. Choose the voltage divider ratio so that the voltage at PFI falls below 1.2V just before the 5V regulator drops out. Use  $\overline{PFO}$  to interrupt the  $\mu P$  so it can prepare for an orderly power-down.

# 11 Applications Information

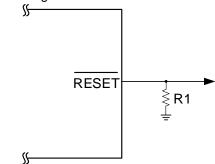

# 11.1 Ensuring a Valid RESET Output Down to Vcc=0V

When  $V_{CC}$  falls down below 1V, the RS706  $\overline{RESET}$  output no longer sinks current, it becomes an open circuit. High-impedance CMOS logic inputs can drift to undetermined voltages if left un-driven. If a pull-down resistor is added to the  $\overline{RESET}$  pin, as shown in Figure 17, any stray charge or leakage currents will be drained to ground, holding  $\overline{RESET}$  low. Resistor value (R1) is not critical. It should be about  $100 \mathrm{K}\Omega$ , large enough not to load  $\overline{RESET}$  and small enough to pull  $\overline{RESET}$  to ground.

Figure 17. RESET Valid to Ground Circuit

# 11.2 Monitoring Voltages Other Than the Unregulated DC Input

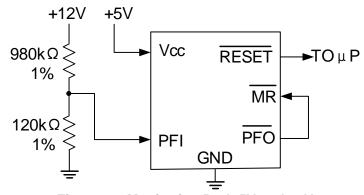

Monitor voltages other than the unregulated DC by connecting a voltage-divider to PFI and adjusting the ratio appropriately. If required, add hysteresis by connecting a resistor (with a value approximately 10 times the sum of the two resistors in the potential divider network) between PFI and  $\overline{PFO}$ . A capacitor between PFI and GND reduces the power - fail circuit's sensitivity to high-frequency noise on the line being monitored.  $\overline{RESET}$  can be asserted on other voltages in addition to the 5V V<sub>CC</sub> line. Connect  $\overline{PFO}$  to  $\overline{MR}$  to initiate a  $\overline{RESET}$  pulse when PFI drops below 1.2V. Figure 18 shows the RS706 configured to assert  $\overline{RESET}$  when the 5V supply falls below the reset threshold, or when the 12V supply falls below approximately 11V.

Figure 18. Monitoring Both 5V and 12V

### 11.3 Interfacing to µPs with Bidirectional Reset Pins

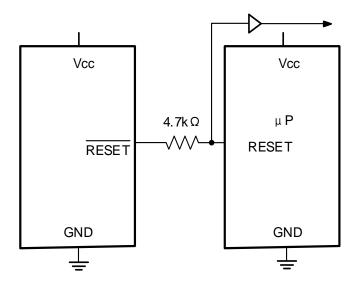

$\mu$ Ps with bidirectional reset pins, can contend with the RS706  $\overline{RESET}$  output. If, for example, the  $\overline{RESET}$  output is driven high and the  $\mu$ P wants to pull it low, indeterminate logic levels may result. To correct this, connect a 4.7K $\Omega$  resistor between the  $\overline{RESET}$  output and the  $\mu$ P reset I/O, as in Figure 19. Buffer the  $\overline{RESET}$  output to other system components.

Figure 19. Buffered  $\overline{\text{RESET}}$  to other system components

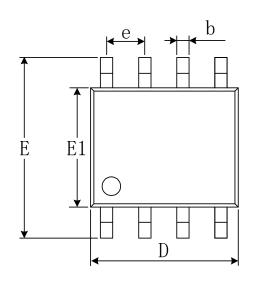

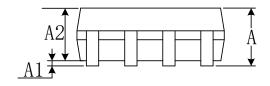

# 12 PACKAGE OUTLINE DIMENSIONS SOIC-8(SOP8)

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |

|--------|------------|----------------|----------------------|-------|--|--|

| Symbol | Min        | Max            | Min                  | Max   |  |  |

| Α      | 1.350      | 1.750          | 0.053                | 0.069 |  |  |

| A1     | 0.100      | 0.250          | 0.004                | 0.010 |  |  |

| A2     | 1.350      | 1.550          | 0.053                | 0.061 |  |  |

| b      | 0.330      | 0.510          | 0.013                | 0.020 |  |  |

| С      | 0.170      | 0.250          | 0.007                | 0.010 |  |  |

| D      | 4.800      | 5.000          | 0.189                | 0.197 |  |  |

| е      | 1.270      | (BSC)          | 0.050                | (BSC) |  |  |

| E      | 5.800      | 6.200          | 0.228                | 0.244 |  |  |

| E1     | 3.800      | 4.000          | 0.150                | 0.157 |  |  |

| L      | 0.400      | 1.270          | 0.016                | 0.050 |  |  |

| θ      | 0°         | 8°             | 0°                   | 8°    |  |  |

### NOTE:

- A. All linear dimension is in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

D. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

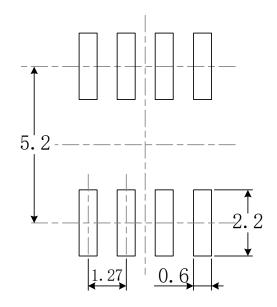

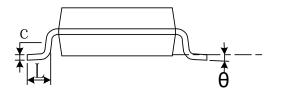

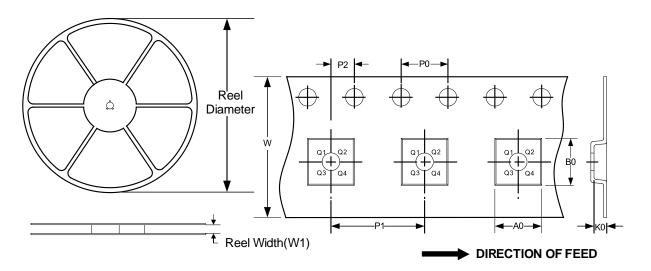

# 13 TAPE AND REEL INFORMATION

# **REEL DIMENSIONS**

# **TAPE DIMENSION**

NOTE: The picture is only for reference. Please make the object as the standard.

# **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel<br>Width<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|-----------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOIC-8(SOP8) | 13"              | 12.4                  | 6.4        | 5.4        | 2.1        | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

NOTE:

- 1. All dimensions are nominal.

- 2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

# IMPORTANT NOTICE AND DISCLAIMER

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.