## Sink Only USB Type-C PD Controller

### 1 General Description

The RT1719A is a USB Type-C controller that complies with the latest USB Type-C and PD standards. It performs USB Type-C detection, including attach and cable orientation. The RT1719A integrates the physical layer of the USB BMC power delivery protocol to allow up to 100W of power. The BMC PD block supports the full Type-C specification.

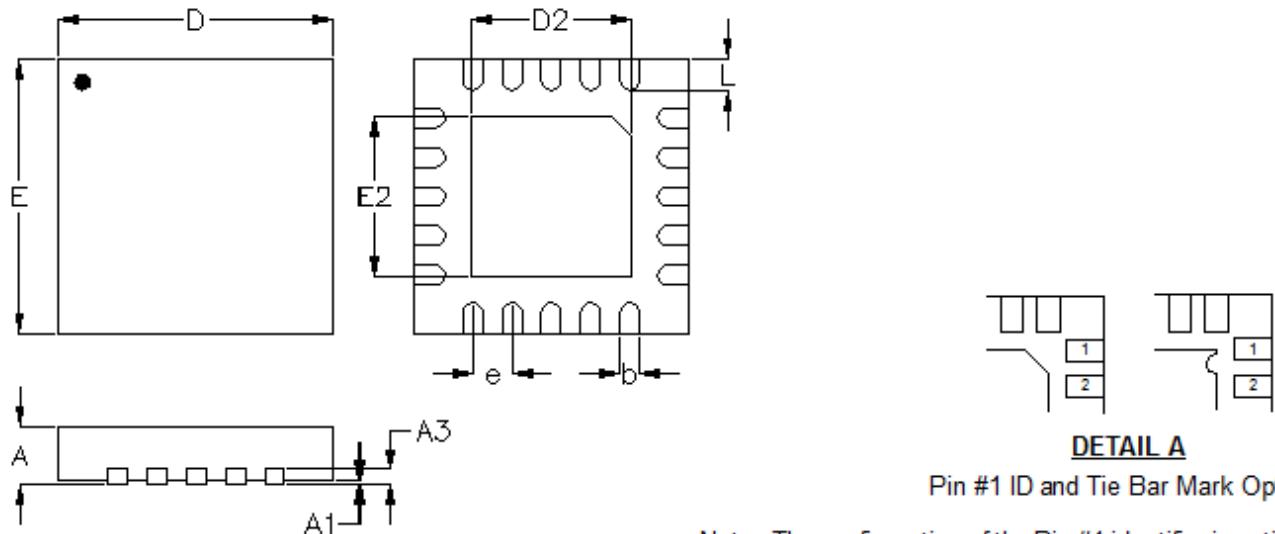

The RT1719A is available in a WQFN-20L 3.5x3.5 package. The recommended junction temperature range is  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$ , and the ambient temperature range is  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

### 2 Ordering Information

RT1719A□-□

## Packing

A: Standard

Package Type<sup>(1)</sup>

N: WQFN-20L 3.5x3.5 (W-Type)

## Note 1.

Richtek products are Richtek Green Policy compliant and marked with <sup>(1)</sup> indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

### 3 Features

- PD 3.2 Compatible

- Attach/Detach Detection as Device

- Current Capability Definition

- Data Role Support

- Dead Battery Support

- Simple I<sup>2</sup>C Interface with AP or EC

- BIST Mode Supported

### 4 Applications

- Cameras

- Printers

- Toys

- Drones

- Handheld Devices

- Sink Devices

### 5 Marking Information

02H: Product Code

YMDAN: Date Code

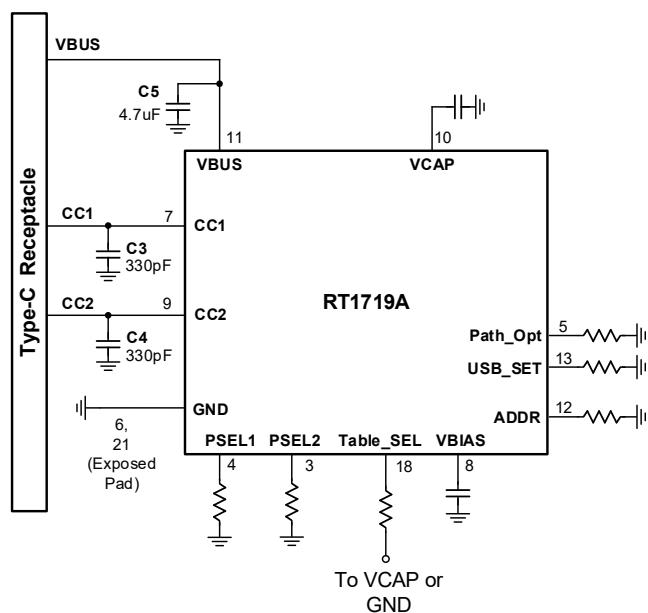

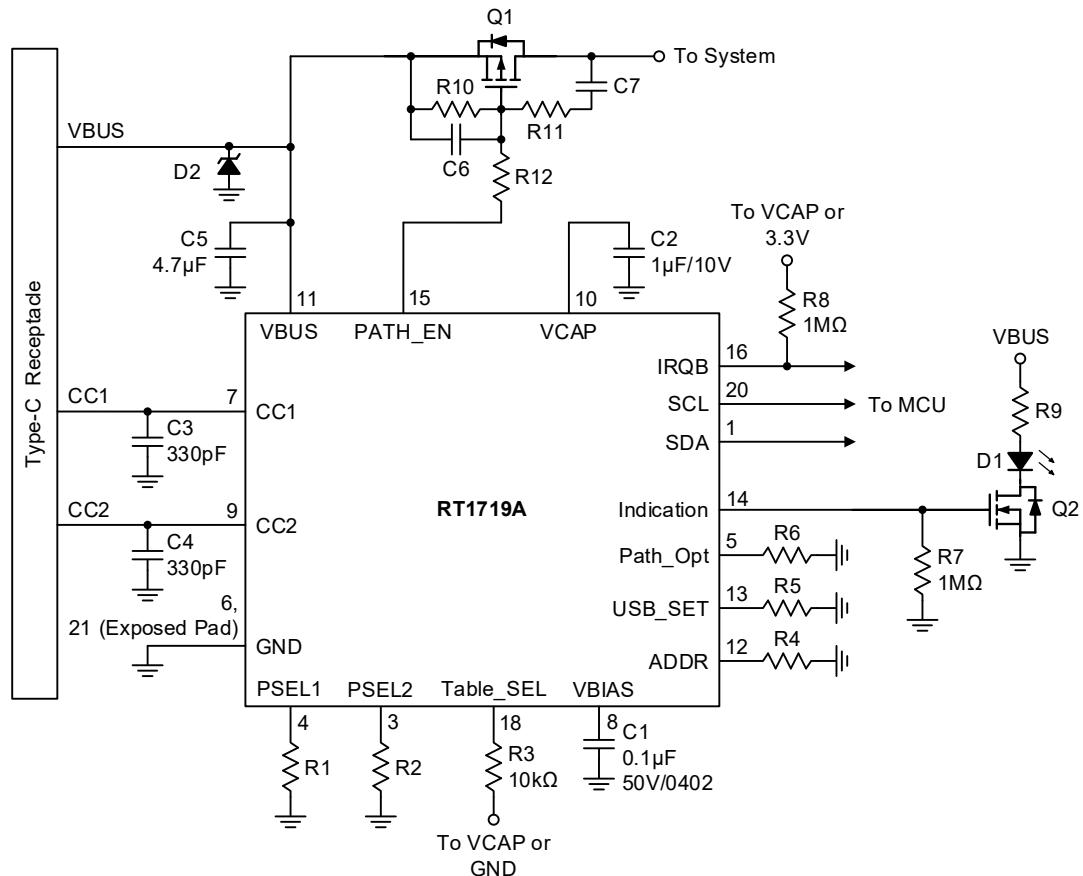

### 6 Simplified Application Circuit

## Table of Contents

|    |                                                  |    |       |                                              |           |

|----|--------------------------------------------------|----|-------|----------------------------------------------|-----------|

| 1  | General Description.....                         | 1  | 15.7  | USB Setting .....                            | 13        |

| 2  | Ordering Information .....                       | 1  | 15.8  | Table Selection.....                         | 13        |

| 3  | Features.....                                    | 1  | 15.9  | PSEL.....                                    | 14        |

| 4  | Applications .....                               | 1  | 15.10 | Path Option.....                             | 19        |

| 5  | Marking Information.....                         | 1  | 15.11 | HV Bound and LV Bound .....                  | 19        |

| 6  | Simplified Application Circuit .....             | 1  | 15.12 | PD Suspend Information.....                  | 20        |

| 7  | Pin Configuration.....                           | 3  | 16    | <b>Application Information .....</b>         | <b>21</b> |

| 8  | Functional Pin Description.....                  | 3  | 16.1  | CC Status .....                              | 21        |

| 9  | Functional Block Diagram.....                    | 4  | 16.2  | DR Swap.....                                 | 21        |

| 10 | Absolute Maximum Ratings .....                   | 5  | 16.3  | Reading Source Capability .....              | 22        |

| 11 | Recommended Operating Conditions.....            | 5  | 16.4  | Request Source PDO .....                     | 23        |

| 12 | Electrical Characteristics .....                 | 6  | 16.5  | Editing Sink Capability Extend .....         | 26        |

| 13 | Typical Application Circuit .....                | 9  | 16.6  | Thermal Considerations.....                  | 27        |

| 14 | Timing Diagram .....                             | 10 | 17    | <b>Functional Register Description .....</b> | <b>28</b> |

|    | 14.1 Power-On Sequence .....                     | 10 | 17.1  | Register Map.....                            | 28        |

| 15 | Operation.....                                   | 11 | 18    | <b>Outline Dimension.....</b>                | <b>49</b> |

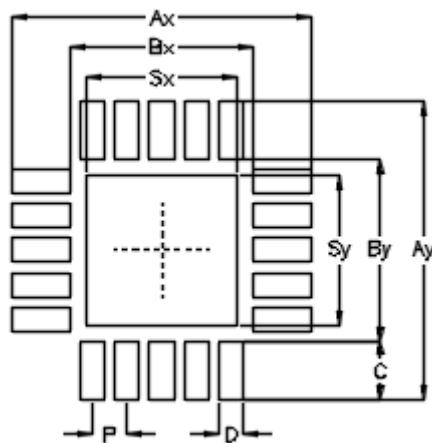

|    | 15.1 USB_PD .....                                | 11 | 19    | <b>Footprint Information .....</b>           | <b>50</b> |

|    | 15.2 Type-C Detection.....                       | 11 | 20    | <b>Packing Information .....</b>             | <b>51</b> |

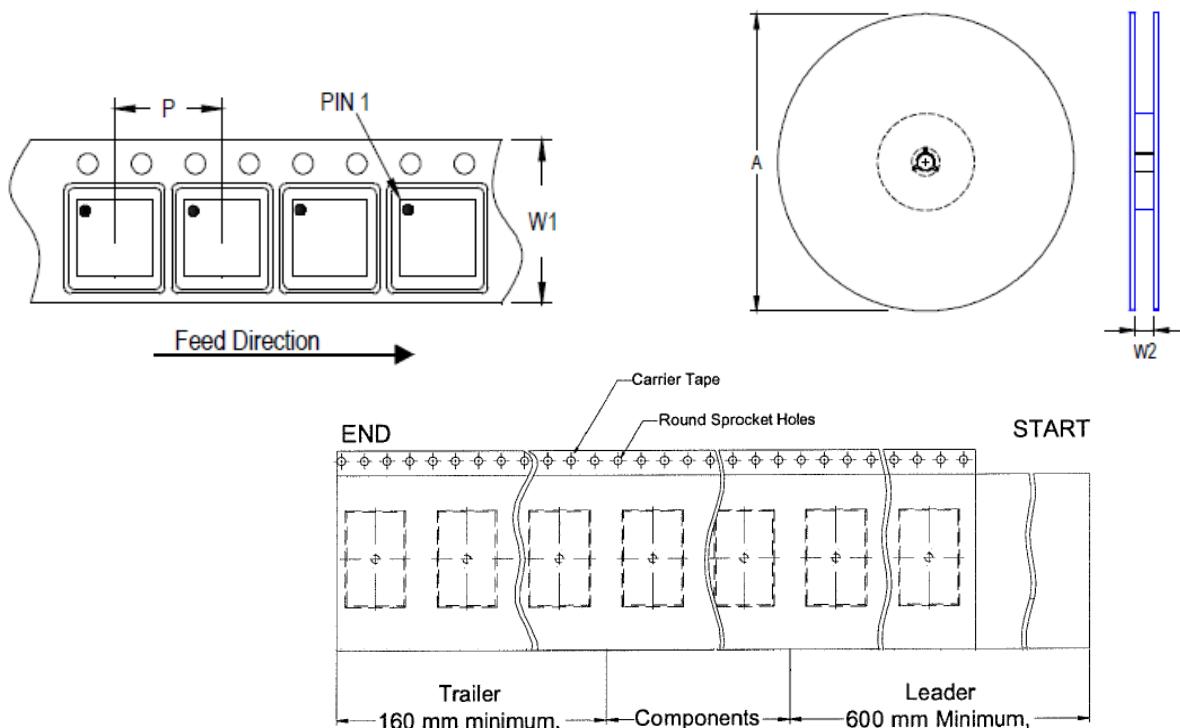

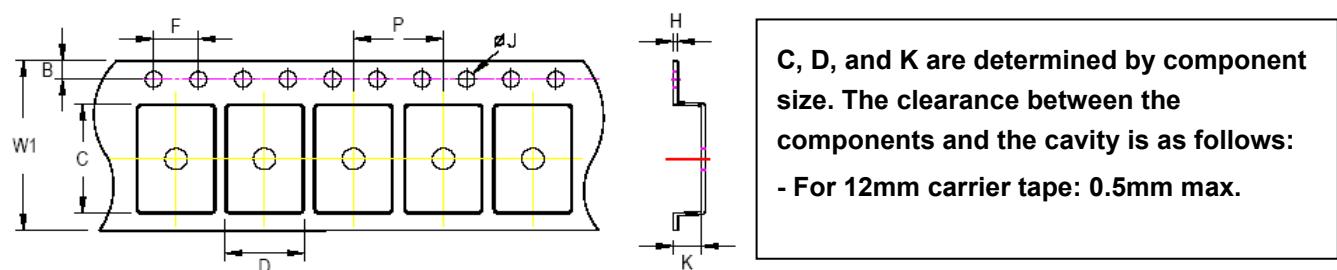

|    | 15.3 Dead Battery Mode .....                     | 11 | 20.1  | Tape and Reel Data .....                     | 51        |

|    | 15.4 I <sup>2</sup> C Interface .....            | 11 | 20.2  | Tape and Reel Packing .....                  | 52        |

|    | 15.5 Read and Write Function.....                | 12 | 20.3  | Packing Material Anti-ESD Property .....     | 53        |

|    | 15.6 I <sup>2</sup> C Waveform Information ..... | 12 | 21    | <b>Datasheet Revision History .....</b>      | <b>54</b> |

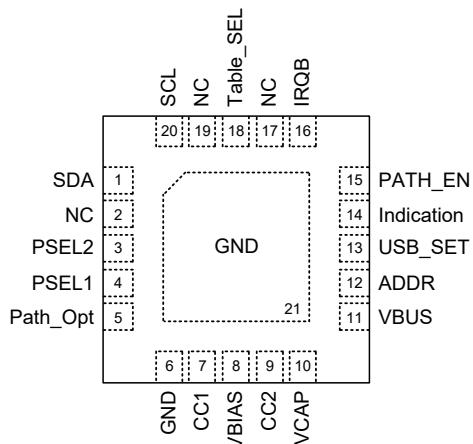

## 7 Pin Configuration

(TOP VIEW)

WQFN-20L 3.5x3.5

## 8 Functional Pin Description

| Pin No.                | Pin Name   | Pin Function                                                                                                                                                      |

|------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | SDA        | $\text{I}^2\text{C}$ serial data signal to be connected to the $\text{I}^2\text{C}$ master. Connect $1\text{k}\Omega$ to GND if $\text{I}^2\text{C}$ is not used. |

| 2, 17, 19              | NC         | No internal connection.                                                                                                                                           |

| 3                      | PSEL2      | Power selection 2 for power data object. Use the $\pm 1\%$ resistor for setting.                                                                                  |

| 4                      | PSEL1      | Power selection 1 for power data object. Use the $\pm 1\%$ resistor for setting.                                                                                  |

| 5                      | Path_Opt   | Power path option. Use the $\pm 1\%$ resistor for setting.                                                                                                        |

| 6, 21<br>(Exposed Pad) | GND        | Ground pin. The exposed pad must be connected to GND and be well soldered to a large copper PCB for maximum power dissipation.                                    |

| 7                      | CC1        | Type-C connector configuration channel (CC) pins. Initially used to determine when an attach has occurred and what the orientation detected.                      |

| 8                      | VBIAS      | Put a $0.1\mu\text{F}$ (0402/50V) capacitor. This pin cannot drive external load.                                                                                 |

| 9                      | CC2        | Type-C connector configuration channel (CC) pins. Initially used to determine when an attach has occurred and what the orientation detected.                      |

| 10                     | VCAP       | Put a $1\mu\text{F}$ capacitor. This pin cannot drive external load.                                                                                              |

| 11                     | VBUS       | VBUS input pin for attach/detach detection and supply input.                                                                                                      |

| 12                     | ADDR       | Address selection node when used with multiple Type-C ports. Use the $\pm 1\%$ resistor for setting.                                                              |

| 13                     | USB_SET    | USB ability setting node. Use the $\pm 1\%$ resistor for setting.                                                                                                 |

| 14                     | Indication | The power data object does not match the indication pin.                                                                                                          |

| 15                     | PATH_EN    | Open-drain gate driver, which may be used to drive a PMOS.                                                                                                        |

| 16                     | IRQB       | Interrupt output, active-low open-drain, to prompt the processor to read the registers. Connect $1\text{k}\Omega$ to GND if IRQB is not used.                     |

| Pin No. | Pin Name  | Pin Function                                                                                                          |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------|

| 18      | Table_SEL | Power data object table selection                                                                                     |

| 20      | SCL       | $I^2C$ serial clock signal to be connected to the $I^2C$ master.<br>Connect 1k $\Omega$ to GND if $I^2C$ is not used. |

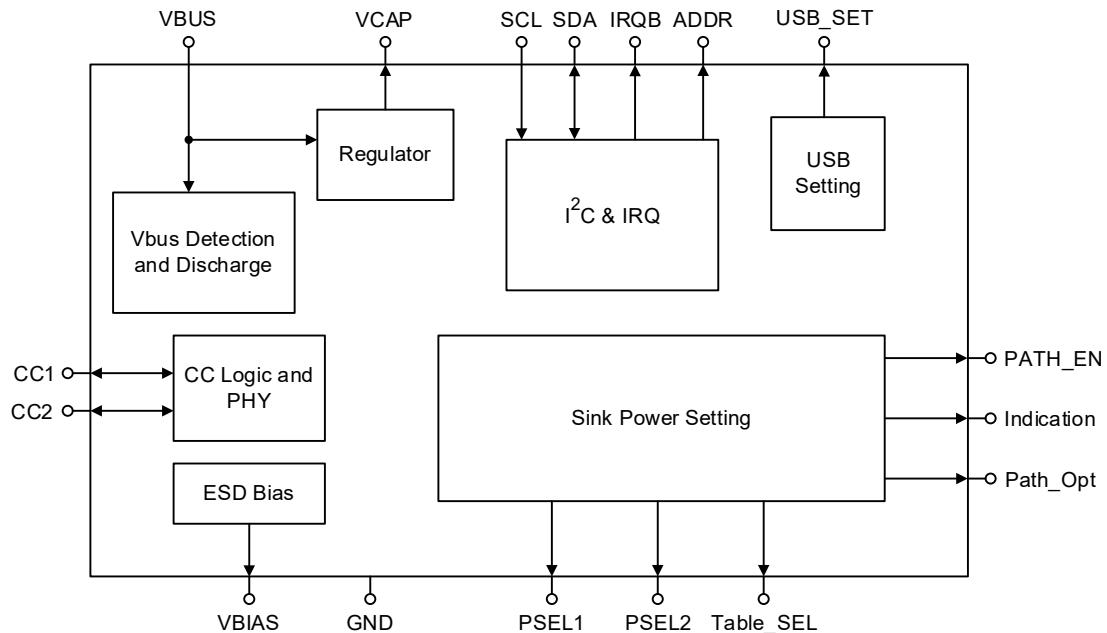

## 9 Functional Block Diagram

## 10 Absolute Maximum Ratings

### (Note 2)

- VBUS ----- -0.3V to 28V

- CC1, CC2, PATH\_EN, VBIAS ----- -0.3V to 24V

- VCAP, Indication, Path\_Opt, USB\_SET, ADDR ----- -0.3V to 6V

- SDA, SCL, IRQB, PSEL1, PSEL2, Table\_SEL ----- -0.3V to 6V

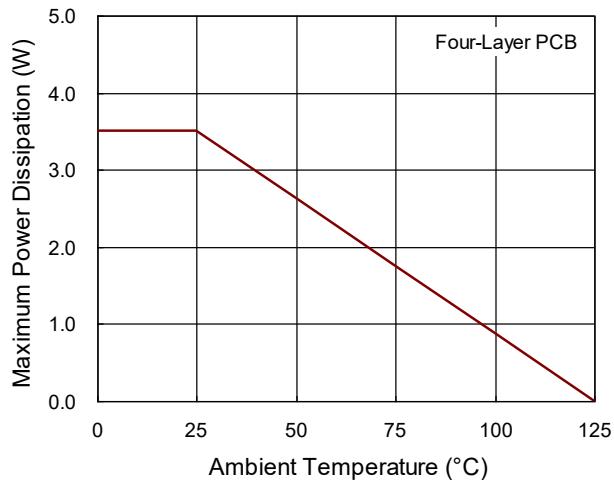

- Power Dissipation, PD @ TA = 25°C

WQFN-20L 3.5x3.5 ----- 3.5W

### • Package Thermal Resistance (Note 3)

- WQFN-20L 3.5x3.5, θJA ----- 28.5°C/W

- WQFN-20L 3.5x3.5, θJC ----- 7.2°C/W

- Lead Temperature (Soldering, 10 sec.) ----- 260°C

- Junction Temperature ----- 150°C

- Storage Temperature Range ----- -65°C to 150°C

### • ESD Susceptibility (Note 4)

#### HBM (Human Body Model)

- VBUS, CC1, CC2 ----- ±4kV

- Other Pins ----- ±2kV

- VBUS, CC1, CC2 (IEC 61000-4-2 Contact Discharge) ----- ±8kV

- VBUS, CC1, CC2 (IEC 61000-4-2 Air Discharge) ----- ±15kV

- VBUS, CC1, CC2 (IEC 61000-4-5 Surge) ----- ±28V

**Note 2.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings at TA = 25°C only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Note 3.** θJA is simulated under natural convection (still air) at TA = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard. θJC is simulated at the bottom of the package.

**Note 4.** Devices are ESD sensitive. Handling precautions are recommended.

## 11 Recommended Operating Conditions

### (Note 5)

- VBS Input Voltage ----- 3V to 22V

- Ambient Temperature Range ----- -40°C to 85°C

- Junction Temperature Range ----- -40°C to 125°C

**Note 5.** The device is not guaranteed to function outside its operating conditions.

## 12 Electrical Characteristics

( $T_A = 25^\circ\text{C}$ , unless otherwise specified.)

| Parameter                                                                                                               | Symbol                     | Test Conditions                                                                                                                                      | Min  | Typ   | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| <b>Common Normative Signaling Requirements</b>                                                                          |                            |                                                                                                                                                      |      |       |      |      |

| Bit Rate                                                                                                                | fBitRate                   | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 270  | 300   | 330  | kbps |

| <b>Common Normative Signaling Requirements for Transmitter</b>                                                          |                            |                                                                                                                                                      |      |       |      |      |

| Maximum Difference between the Bit-Rate during the Part of the Packet Following the Preamble and the Reference Bit-Rate | pBitRate                   | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | --   | --    | 0.25 | %    |

| Time from the End of Last Bit of a Frame until the Start of the First Bit of the Next Preamble                          | t <sub>InterFrameGap</sub> | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 25   | --    | --   | μs   |

| Time before the Start of the First Bit of the Preamble when the Transmitter Shall Start Driving the Line                | t <sub>StartDrive</sub>    | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | -1   | --    | 1    | μs   |

| <b>BMC Common Normative Requirements</b>                                                                                |                            |                                                                                                                                                      |      |       |      |      |

| Time to Cease Driving the Line after the End of the Last Bit of the Frame                                               | t <sub>EndDriveBMC</sub>   | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | --   | --    | 23   | μs   |

| Fall Time                                                                                                               | t <sub>Fall</sub>          | V <sub>BUS</sub> = 3V to 22V<br>10% and 90% amplitude points, minimum is under an unloaded condition.                                                | 300  | --    | --   | ns   |

| Time to Cease Driving the Line after the Final High-to-Low Transition                                                   | t <sub>HoldLowBMC</sub>    | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 1    | --    | --   | μs   |

| Rise Time                                                                                                               | t <sub>Rise</sub>          | V <sub>BUS</sub> = 3V to 22V<br>10% and 90% amplitude points, minimum is under an unloaded condition.                                                | 300  | --    | --   | ns   |

| Voltage Swing                                                                                                           | V <sub>Swing</sub>         | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 1.05 | 1.125 | 1.2  | V    |

| Transmitter Output Impedance                                                                                            | Z <sub>Driver</sub>        | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 33   | --    | 75   | Ω    |

| Receiver Input Impedance                                                                                                | Z <sub>BmcRx</sub>         | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 1    | --    | --   | MΩ   |

| <b>Power Consumption</b>                                                                                                |                            |                                                                                                                                                      |      |       |      |      |

| Idle Mode                                                                                                               | I <sub>Idle_Sink</sub>     | V <sub>BUS</sub> = 3V to 22V. No events                                                                                                              | --   | 130   | 180  | μA   |

| BIST Mode                                                                                                               | I <sub>BIST</sub>          | Sink current consumption in cable attached and CC send BIST<br>V <sub>BUS</sub> = 3V to 22V.<br>I <sup>2</sup> C and IRQB pull high voltage is 3.3V. | --   | 5.5   | 6.5  | mA   |

| <b>Type-C Port Control</b>                                                                                              |                            |                                                                                                                                                      |      |       |      |      |

| UFP Rd                                                                                                                  | Rd                         | V <sub>BUS</sub> = 3V to 22V                                                                                                                         | 4.59 | 5.10  | 5.61 | kΩ   |

| Parameter                                                   | Symbol                               | Test Conditions                       | Min                | Typ   | Max                | Unit    |

|-------------------------------------------------------------|--------------------------------------|---------------------------------------|--------------------|-------|--------------------|---------|

| UFP Pull-Down Voltage in Dead Battery under DFP 80 $\mu$ A  | V <sub>DB_80<math>\mu</math>A</sub>  |                                       | 0.25               | --    | 1.5                | V       |

| UFP Pull-Down Voltage in Dead Battery under DFP 180 $\mu$ A | V <sub>DB_180<math>\mu</math>A</sub> |                                       | 0.45               | --    | 1.5                | V       |

| UFP Pull-Down Voltage in Dead Battery under DFP 330 $\mu$ A | V <sub>DB_330<math>\mu</math>A</sub> |                                       | 0.85               | --    | 2.45               | V       |

| <b>VBUS Port Control</b>                                    |                                      |                                       |                    |       |                    |         |

| VBUS High Voltage Bound for 20V                             | V <sub>HV20</sub>                    |                                       | 21.85              | 23    | 24                 | V       |

| VBUS Low Voltage Bound for 20V                              | V <sub>LV20</sub>                    |                                       | 15.975             | 16.9  | 17.75              | V       |

| VBUS High Voltage Bound for 15V                             | V <sub>HV15</sub>                    |                                       | 16.15              | 17    | 17.85              | V       |

| VBUS Low Voltage Bound for 15V                              | V <sub>LV15</sub>                    |                                       | 11.7               | 12.35 | 13                 | V       |

| VBUS High Voltage Bound for 12V                             | V <sub>HV12</sub>                    |                                       | 13.3               | 14    | 14.7               | V       |

| VBUS Low Voltage Bound for 12V                              | V <sub>LV12</sub>                    |                                       | 9.135              | 9.6   | 10.18              | V       |

| VBUS High Voltage Bound for 9V                              | V <sub>HV09</sub>                    |                                       | 9.975              | 10.5  | 11.02 <sub>5</sub> | V       |

| VBUS Low Voltage Bound for 9V                               | V <sub>LV09</sub>                    |                                       | 6.57               | 6.93  | 7.36               | V       |

| VBUS High Voltage Bound for 5V                              | V <sub>HV05</sub>                    |                                       | 5.7                | 6     | 6.3                | V       |

| VBUS_PRESENT Voltage Rising Threshold                       | V <sub>BUS_PRESENT_rising</sub>      | V <sub>BUS</sub> rising               | 3.7                | 3.85  | 4                  | V       |

| VBUS_PRESENT Voltage Falling Threshold                      | V <sub>BUS_PRESENT_Falling</sub>     | V <sub>BUS</sub> falling              | 3.4                | 3.5   | 3.6                | V       |

| <b>IRQB Low-Level Output Voltage</b>                        |                                      |                                       |                    |       |                    |         |

| IRQB Low-Level Output Voltage                               | V <sub>IRQB_OL</sub>                 | I <sub>IRQB_OL</sub> = 4mA            | --                 | --    | 0.4                | V       |

| <b>VCAP</b>                                                 |                                      |                                       |                    |       |                    |         |

| Voltage at VCAP                                             | V <sub>CAP2</sub>                    | V <sub>BUS</sub> $\geq$ 5V, no load.  | 4.3                | --    | 5                  | V       |

| <b>Indication</b>                                           |                                      |                                       |                    |       |                    |         |

| Output Voltage High-Level                                   | V <sub>OH</sub>                      | With 1M $\Omega$ resistance load      | VCAP <sub>-1</sub> | --    | VCAP               | V       |

| Output Voltage Low-Level                                    | V <sub>OL</sub>                      | I <sub>OL</sub> = 4mA                 | --                 | --    | 0.4                | V       |

| <b>Table_SEL</b>                                            |                                      |                                       |                    |       |                    |         |

| Input Voltage High-Level                                    | V <sub>IH</sub>                      |                                       | VCAP x 0.75        | --    | --                 | V       |

| Input Voltage Low-Level                                     | V <sub>IL</sub>                      |                                       | --                 | --    | VCAP x 0.25        | V       |

| Input Leakage Current                                       | I <sub>IN_Leakage</sub>              |                                       | -1                 | --    | 1                  | $\mu$ A |

| <b>PATH_EN</b>                                              |                                      |                                       |                    |       |                    |         |

| PATH_EN Low-Level Output Voltage                            | V <sub>PATH_EN_OL</sub>              | I <sub>PATH_EN_OL</sub> = 800 $\mu$ A | --                 | --    | 0.4                | V       |

| Parameter                                                         | Symbol              | Test Conditions                                                                             | Min  | Typ | Max  | Unit |

|-------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|------|-----|------|------|

| <b>I<sup>2</sup>C Electrical Characteristics</b>                  |                     |                                                                                             |      |     |      |      |

| I <sup>2</sup> C Bus Pulled Voltage                               | V <sub>I2C_Hi</sub> |                                                                                             | 1.8  | --  | 3.6  | V    |

| Low-Level Input Voltage                                           | V <sub>IL</sub>     | V <sub>BUS</sub> = 3V to 22V                                                                | --   | --  | 0.4  | V    |

| High-Level Input Voltage                                          | V <sub>IH</sub>     | V <sub>BUS</sub> = 3V to 22V                                                                | 1.26 | --  | --   | V    |

| Low-Level Output Voltage                                          | V <sub>OL</sub>     | V <sub>BUS</sub> = 3V to 22V, open-drain                                                    | --   | --  | 0.4  | V    |

| Input Current Each IO Pin                                         | I <sub>I</sub>      | V <sub>BUS</sub> = 3V to 22V<br>0.1V <sub>DD</sub> < V <sub>I</sub> < 0.9V <sub>DDMAX</sub> | -10  | --  | 10   | µA   |

| SCL Clock Frequency                                               | f <sub>SCL</sub>    | V <sub>BUS</sub> = 3V to 22V                                                                | 100  | --  | 2000 | kHz  |

| Pulse Width of Spikes that Must Be Suppressed by the Input Filter | t <sub>SP</sub>     | V <sub>BUS</sub> = 3V to 22V                                                                | --   | --  | 50   | ns   |

| Data Hold Time                                                    | t <sub>HD:DAT</sub> | V <sub>BUS</sub> = 3V to 22V                                                                | 30   | --  | --   | ns   |

| Data Set-Up Time                                                  | t <sub>SU:DAT</sub> | V <sub>BUS</sub> = 3V to 22V                                                                | 50   | --  | --   | ns   |

### 13 Typical Application Circuit

#### Note:

1. R1, R2, R4, R5 and R6 values depend on system design. Use the  $\pm 1\%$  resistor for setting.

2. R9 value depends on the D1 when VBUS = 5V.

3. R10, R11, R12, C6 and C7 values depend on the soft-start requirements for the power path.

4. TDS2221PW is recommended for D2.

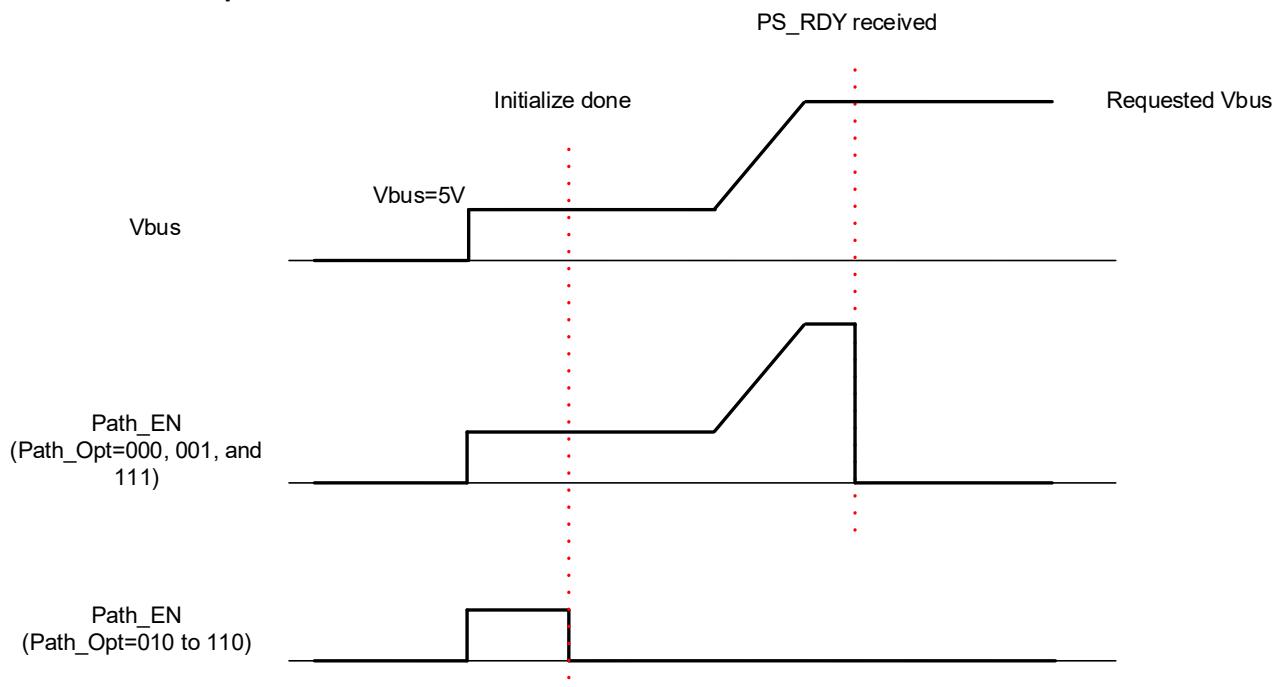

## 14 Timing Diagram

### 14.1 Power-On Sequence

## 15 Operation

### 15.1 USB\_PD

The Power Delivery (PD) function of the RT1719A complies with the USB Power Delivery Specification 3.2.

### 15.2 Type-C Detection

The RT1719A implements multiple comparators which can be used by software to determine the state of the CC1 and CC2 pins. This status information provides the host processor with all the information required to determine attach and detach status of the cable.

The RT1719A includes three threshold comparators matching the USB Type-C specification for the three charge current levels that can be detected by a Type-C device.

### 15.3 Dead Battery Mode

When VBUS is off, the RT1719A applies Rd on both CC1 and CC2 and follows all Sink rules. When it is connected to a Source, DRP or Sourcing Device, the system will receive the default VBUS. The circuitry presenting Rd must ensure the voltage on CC is pulled within the same range as the voltage clamp implementation of Rd, allowing a Source to recognize the Sink and provide VBUS.

### 15.4 I<sup>2</sup>C Interface

The RT1719A can be configured to four slave addresses by setting the resistance between ADDR (pin 12) and GND.

| I <sup>2</sup> C Address (7bit) | Resistance between ADDR and GND (unit: kΩ, ±1%) |

|---------------------------------|-------------------------------------------------|

| 0x40                            | 0                                               |

| 0x41                            | 309                                             |

| 0x42                            | 649                                             |

| 0x43                            | open                                            |

The I<sup>2</sup>C interface bus must connect a 1kΩ resistor to the power node and have an independent connection to the processor.

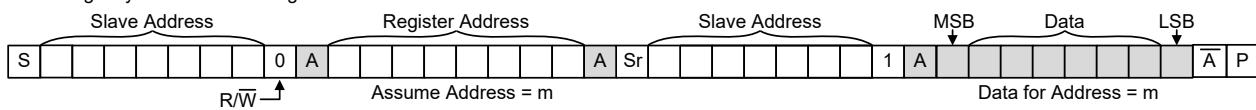

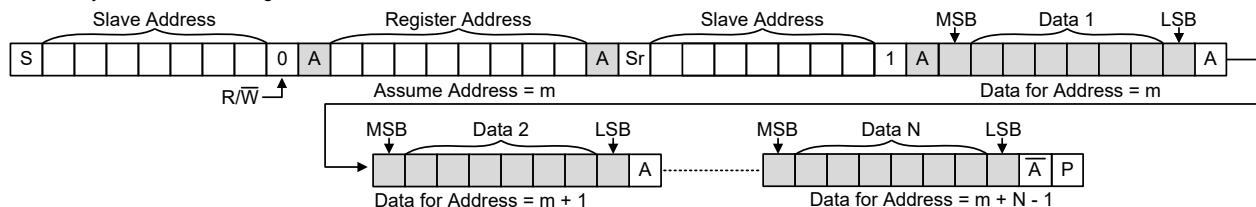

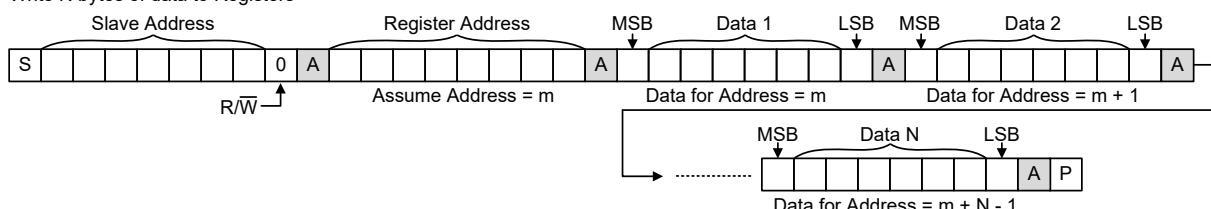

The I<sup>2</sup>C timing diagrams are listed below.

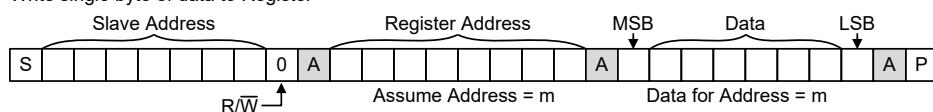

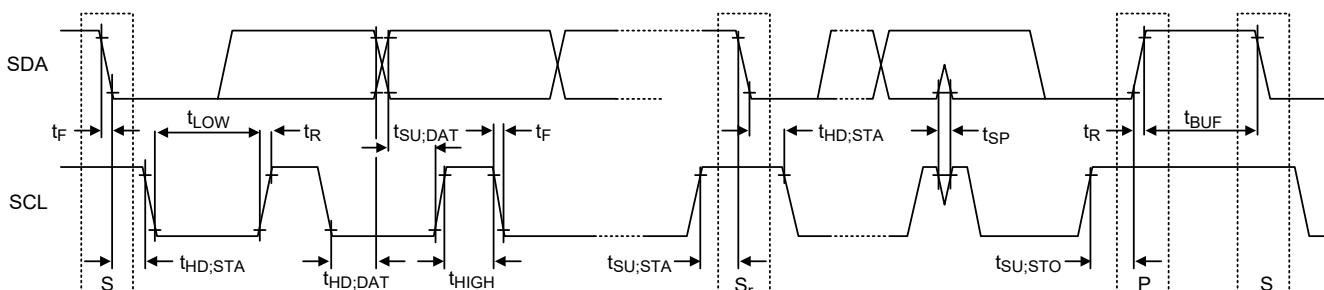

## 15.5 Read and Write Function

Read single byte of data from Register

Read N bytes of data from Registers

Write single byte of data to Register

Write N bytes of data to Registers

Driven by Master,  Driven by Slave,  P Stop,  S Start,  Sr Repeat Start

## 15.6 I<sup>2</sup>C Waveform Information

### 15.7 USB Setting

The USB ability of RT1719A can be set by USB\_SET (pin 13).

| USB Setting                               | Resistance between USB_SET and GND (unit: $k\Omega$ , $\pm 1\%$ ) | 0x3E[1:0] | Behavior                                                                                                                                                                                    |

|-------------------------------------------|-------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Ability, Data Role Swap               | Open                                                              | 11        | Respond "DR_Swap" by sending "Accept," and 0x35[7] will be 1 if "DR_Swap" is received.<br>USB Communications Capable in "Sink_Capabilities" is 1.<br>MCU can send "DR_Swap" by 0x03[7] = 1. |

| USB Ability, No Data Role Swap (UFP Only) | 309                                                               | 01        | Respond "DR_Swap" by sending "Reject," and 0x35[6] will be 1 if "DR_Swap" is received.<br>USB Communications Capable in "Sink_Capabilities" is 1.                                           |

| No USB Ability                            | 0                                                                 | 00        | Respond "DR_Swap" by sending "Reject," and 0x35[6] will be 1 if "DR_Swap" is received.<br>USB Communications Capable in "Sink_Capabilities" is 0.                                           |

The RT1719A will respond DR Swap from port partner according to the setting of USB\_SET and report the result in the register 0x35[7:6].

| Address | Bit | Bit Name           | Default | Type | Description                                                                                                           |

|---------|-----|--------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------|

| 0x2F    | 7   | M_RX_DRSW_ACCEPT   | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                |

|         | 6   | M_RX_DRSW_REJECT   | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                |

| 0x35    | 7   | INT_RX_DRSW_ACCEPT | 0       | WC   | 0: No DR_Swap received or no Accept transmitted. Cleared.<br>(default)<br>1: DR_Swap received and Accept transmitted. |

|         | 6   | INT_RX_DRSW_REJECT | 0       | WC   | 0: No DR_Swap received or no Reject transmitted. Cleared.<br>(default)<br>1: DR_Swap received and Reject transmitted. |

### 15.8 Table Selection

The RT1719A supports 128 configurable Sink\_Capabilities. These are divided into two tables. Table 1 contains 64 Sink\_Capabilities, where the sink currents of each Sink PDO in the capability are the same. Table 0 contains the other 64 Sink\_Capabilities, where the sink powers of each Sink PDO in the capability are the same, except for those with sink current over 5A.

| Table Setting | Configure in Pin 18           | 0x3C[6] |

|---------------|-------------------------------|---------|

| Table 1       | 10k $\Omega$ to VCAP (pin 10) | 1       |

| Table 0       | 10k $\Omega$ to GND           | 0       |

## 15.9 PSEL

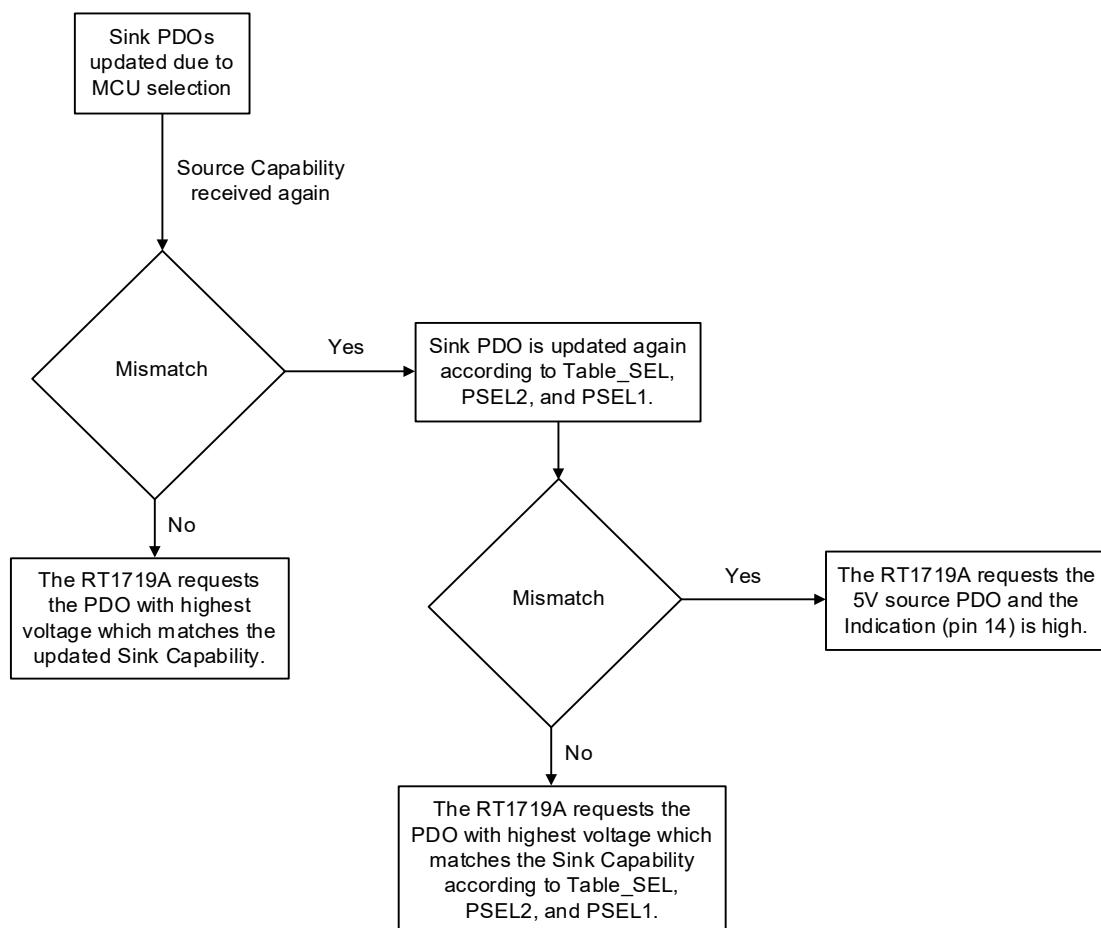

PSEL2 (pin 3) and PSEL1 (pin 4) can configure 64 settings. The sink capability can be configured according to Table\_SEL, PSEL2, and PSEL1.

| PSEL2 Setting | Resistance between PSEL2 and GND (unit: $k\Omega$ , $\pm 1\%$ ) | 0x3C[5:3] |

|---------------|-----------------------------------------------------------------|-----------|

| 111           | Open                                                            | 111       |

| 110           | 887                                                             | 110       |

| 101           | 649                                                             | 101       |

| 100           | 453                                                             | 100       |

| 011           | 324                                                             | 011       |

| 010           | 143                                                             | 010       |

| 001           | 56.2                                                            | 001       |

| 000           | 0                                                               | 000       |

| PSEL1 Setting | Resistance between PSEL1 and GND (unit: $k\Omega$ , $\pm 1\%$ ) | 0x3C[2:0] |

|---------------|-----------------------------------------------------------------|-----------|

| 111           | Open                                                            | 111       |

| 110           | 887                                                             | 110       |

| 101           | 649                                                             | 101       |

| 100           | 453                                                             | 100       |

| 011           | 324                                                             | 011       |

| 010           | 143                                                             | 010       |

| 001           | 56.2                                                            | 001       |

| 000           | 0                                                               | 000       |

The Min V value in the following 2 tables indicates the minimum VBUS voltage required for the sink system to operate. If VBUS is below the specified Min V, the sink system cannot function. Taking (Table\_SEL, PSEL2, PSEL1) = (1,101,011) as example, the PDO1 (5V/1000mA) will not be considered as a candidate to match with the Source PDO or Rp level.

Table 1

| Table_SEL<br>Setting | PSEL2<br>Setting | PSEL1<br>Setting | Min. V | Max. V | PDO1     |           | PDO2     |           | PDO3     |           | PDO4     |           | PDO5     |           |

|----------------------|------------------|------------------|--------|--------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|

|                      |                  |                  |        |        | V<br>(V) | I<br>(mA) |

| 1                    | 111              | 111              | 5      | 9      | 5        | 500       | 9        | 500       | NA       | NA        |          |           |          |           |

| 1                    | 111              | 110              | 5      | 9      | 5        | 1000      | 9        | 1000      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 101              | 5      | 9      | 5        | 1500      | 9        | 1500      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 100              | 5      | 9      | 5        | 2000      | 9        | 2000      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 011              | 5      | 9      | 5        | 2500      | 9        | 2500      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 010              | 5      | 9      | 5        | 3000      | 9        | 3000      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 001              | 5      | 9      | 5        | 3500      | 9        | 3500      | NA       | NA        |          |           |          |           |

| 1                    | 111              | 000              | 5      | 9      | 5        | 4000      | 9        | 4000      | NA       | NA        |          |           |          |           |

| 1                    | 110              | 111              | 5      | 9      | 5        | 4500      | 9        | 4500      | NA       | NA        |          |           |          |           |

| 1                    | 110              | 110              | 5      | 9      | 5        | 5000      | 9        | 5000      | NA       | NA        |          |           |          |           |

| 1                    | 110              | 101              | 5      | 12     | 5        | 500       | 9        | 500       | 12       | 500       | NA       | NA        |          |           |

| 1                    | 110              | 100              | 5      | 12     | 5        | 1000      | 9        | 1000      | 12       | 1000      | NA       | NA        |          |           |

| 1                    | 110              | 011              | 5      | 12     | 5        | 1500      | 9        | 1500      | 12       | 1500      | NA       | NA        |          |           |

| 1                    | 110              | 010              | 5      | 12     | 5        | 2000      | 9        | 2000      | 12       | 2000      | NA       | NA        |          |           |

| 1                    | 110              | 001              | 5      | 12     | 5        | 2500      | 9        | 2500      | 12       | 2500      | NA       | NA        |          |           |

| 1                    | 110              | 000              | 5      | 12     | 5        | 3000      | 9        | 3000      | 12       | 3000      | NA       | NA        |          |           |

| 1                    | 101              | 111              | 5      | 12     | 5        | 3500      | 9        | 3500      | 12       | 3500      | NA       | NA        |          |           |

| 1                    | 101              | 110              | 5      | 12     | 5        | 4000      | 9        | 4000      | 12       | 4000      | NA       | NA        |          |           |

| 1                    | 101              | 101              | 5      | 12     | 5        | 4500      | 9        | 4500      | 12       | 4500      | NA       | NA        |          |           |

| 1                    | 101              | 100              | 5      | 12     | 5        | 5000      | 9        | 5000      | 12       | 5000      | NA       | NA        |          |           |

| 1                    | 101              | 011              | 12     | 12     | 5        | 1000      | 12       | 1000      | NA       | NA        |          |           |          |           |

| 1                    | 101              | 010              | 12     | 12     | 5        | 1500      | 12       | 1500      | NA       | NA        |          |           |          |           |

| 1                    | 101              | 001              | 12     | 12     | 5        | 2000      | 12       | 2000      | NA       | NA        |          |           |          |           |

| 1                    | 101              | 000              | 12     | 12     | 5        | 2500      | 12       | 2500      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 111              | 12     | 12     | 5        | 3000      | 12       | 3000      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 110              | 12     | 12     | 5        | 3500      | 12       | 3500      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 101              | 12     | 12     | 5        | 4000      | 12       | 4000      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 100              | 12     | 12     | 5        | 4500      | 12       | 4500      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 011              | 12     | 12     | 5        | 5000      | 12       | 5000      | NA       | NA        |          |           |          |           |

| 1                    | 100              | 010              | 5      | 15     | 5        | 500       | 9        | 500       | 12       | 500       | 15       | 500       | NA       | NA        |

| 1                    | 100              | 001              | 5      | 15     | 5        | 1000      | 9        | 1000      | 12       | 1000      | 15       | 1000      | NA       | NA        |

| 1                    | 100              | 000              | 5      | 15     | 5        | 1500      | 9        | 1500      | 12       | 1500      | 15       | 1500      | NA       | NA        |

| Table_SEL<br>Setting | PSEL2<br>Setting | PSEL1<br>Setting | Min. V | Max. V | PDO1     |           | PDO2     |           | PDO3     |           | PDO4     |           | PDO5     |           |

|----------------------|------------------|------------------|--------|--------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|

|                      |                  |                  |        |        | V<br>(V) | I<br>(mA) |

| 1                    | 011              | 111              | 5      | 15     | 5        | 2000      | 9        | 2000      | 12       | 2000      | 15       | 2000      | NA       | NA        |

| 1                    | 011              | 110              | 5      | 15     | 5        | 2500      | 9        | 2500      | 12       | 2500      | 15       | 2500      | NA       | NA        |

| 1                    | 011              | 101              | 5      | 15     | 5        | 3000      | 9        | 3000      | 12       | 3000      | 15       | 3000      | NA       | NA        |

| 1                    | 011              | 100              | 5      | 15     | 5        | 3500      | 9        | 3500      | 12       | 3500      | 15       | 3500      | NA       | NA        |

| 1                    | 011              | 011              | 5      | 15     | 5        | 4000      | 9        | 4000      | 12       | 4000      | 15       | 4000      | NA       | NA        |

| 1                    | 011              | 010              | 5      | 15     | 5        | 4500      | 9        | 4500      | 12       | 4500      | 15       | 4500      | NA       | NA        |

| 1                    | 011              | 001              | 5      | 15     | 5        | 5000      | 9        | 5000      | 12       | 5000      | 15       | 5000      | NA       | NA        |

| 1                    | 011              | 000              | 15     | 15     | 5        | 1000      | 15       | 1000      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 111              | 15     | 15     | 5        | 1500      | 15       | 1500      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 110              | 15     | 15     | 5        | 2000      | 15       | 2000      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 101              | 15     | 15     | 5        | 2500      | 15       | 2500      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 100              | 15     | 15     | 5        | 3000      | 15       | 3000      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 011              | 15     | 15     | 5        | 3500      | 15       | 3500      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 010              | 15     | 15     | 5        | 4000      | 15       | 4000      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 001              | 15     | 15     | 5        | 4500      | 15       | 4500      | NA       | NA        |          |           |          |           |

| 1                    | 010              | 000              | 15     | 15     | 5        | 5000      | 15       | 5000      | NA       | NA        |          |           |          |           |

| 1                    | 001              | 111              | 5      | 20     | 5        | 1000      | 9        | 1000      | 12       | 1000      | 15       | 1000      | 20       | 1000      |

| 1                    | 001              | 110              | 5      | 20     | 5        | 2000      | 9        | 2000      | 12       | 2000      | 15       | 2000      | 20       | 2000      |

| 1                    | 001              | 101              | 5      | 20     | 5        | 2500      | 9        | 2500      | 12       | 2500      | 15       | 2500      | 20       | 2500      |

| 1                    | 001              | 100              | 5      | 20     | 5        | 3000      | 9        | 3000      | 12       | 3000      | 15       | 3000      | 20       | 3000      |

| 1                    | 001              | 011              | 5      | 20     | 5        | 3500      | 9        | 3500      | 12       | 3500      | 15       | 3500      | 20       | 3500      |

| 1                    | 001              | 010              | 5      | 20     | 5        | 4000      | 9        | 4000      | 12       | 4000      | 15       | 4000      | 20       | 4000      |

| 1                    | 001              | 001              | 5      | 20     | 5        | 4500      | 9        | 4500      | 12       | 4500      | 15       | 4500      | 20       | 4500      |

| 1                    | 001              | 000              | 5      | 20     | 5        | 5000      | 9        | 5000      | 12       | 5000      | 15       | 5000      | 20       | 5000      |

| 1                    | 000              | 111              | 20     | 20     | 5        | 1000      | 20       | 1000      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 110              | 20     | 20     | 5        | 2000      | 20       | 2000      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 101              | 20     | 20     | 5        | 2500      | 20       | 2500      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 100              | 20     | 20     | 5        | 3000      | 20       | 3000      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 011              | 20     | 20     | 5        | 3500      | 20       | 3500      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 010              | 20     | 20     | 5        | 4000      | 20       | 4000      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 001              | 20     | 20     | 5        | 4500      | 20       | 4500      | NA       | NA        |          |           |          |           |

| 1                    | 000              | 000              | 20     | 20     | 5        | 5000      | 20       | 5000      | NA       | NA        |          |           |          |           |

Table 0

| Table_SEL<br>Setting | PSEL2<br>Setting | PSEL1<br>Setting | Min. V | Max. V | PDO1     |           | PDO2     |           | PDO3     |           | PDO4     |           | PDO5     |           |

|----------------------|------------------|------------------|--------|--------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|

|                      |                  |                  |        |        | V<br>(V) | I<br>(mA) |

| 0                    | 111              | 111              | 5      | 5      | 5        | 500       | NA       | NA        |          |           |          |           |          |           |

| 0                    | 111              | 110              | 5      | 5      | 5        | 1500      | NA       | NA        |          |           |          |           |          |           |

| 0                    | 111              | 101              | 5      | 5      | 5        | 2000      | NA       | NA        |          |           |          |           |          |           |

| 0                    | 111              | 100              | 5      | 5      | 5        | 3000      | NA       | NA        |          |           |          |           |          |           |

| 0                    | 111              | 011              | 5      | 9      | 5        | 1500      | 9        | 830       | NA       | NA        |          |           |          |           |

| 0                    | 111              | 010              | 5      | 9      | 5        | 2000      | 9        | 1110      | NA       | NA        |          |           |          |           |

| 0                    | 111              | 001              | 5      | 9      | 5        | 3000      | 9        | 1660      | NA       | NA        |          |           |          |           |

| 0                    | 111              | 000              | 5      | 9      | 5        | 4000      | 9        | 2220      | NA       | NA        |          |           |          |           |

| 0                    | 110              | 111              | 5      | 9      | 5        | 5000      | 9        | 2770      | NA       | NA        |          |           |          |           |

| 0                    | 110              | 110              | 5      | 12     | 5        | 1500      | 9        | 830       | 12       | 620       | NA       | NA        |          |           |

| 0                    | 110              | 101              | 5      | 12     | 5        | 2000      | 9        | 1110      | 12       | 830       | NA       | NA        |          |           |

| 0                    | 110              | 100              | 5      | 12     | 5        | 3000      | 9        | 1660      | 12       | 1250      | NA       | NA        |          |           |

| 0                    | 110              | 011              | 5      | 12     | 5        | 4000      | 9        | 2220      | 12       | 1660      | NA       | NA        |          |           |

| 0                    | 110              | 010              | 5      | 12     | 5        | 5000      | 9        | 2770      | 12       | 2080      | NA       | NA        |          |           |

| 0                    | 110              | 001              | 5      | 15     | 5        | 1500      | 9        | 830       | 12       | 620       | 15       | 500       | NA       | NA        |

| 0                    | 110              | 000              | 5      | 15     | 5        | 2000      | 9        | 1110      | 12       | 830       | 15       | 660       | NA       | NA        |

| 0                    | 101              | 111              | 5      | 15     | 5        | 3000      | 9        | 1660      | 12       | 1250      | 15       | 1000      | NA       | NA        |

| 0                    | 101              | 110              | 5      | 15     | 5        | 4000      | 9        | 2220      | 12       | 1660      | 15       | 1330      | NA       | NA        |

| 0                    | 101              | 101              | 5      | 15     | 5        | 5000      | 9        | 2770      | 12       | 2080      | 15       | 1660      | NA       | NA        |

| 0                    | 101              | 100              | 5      | 20     | 5        | 1500      | 9        | 830       | 12       | 620       | 15       | 500       | 20       | 370       |

| 0                    | 101              | 011              | 5      | 20     | 5        | 2000      | 9        | 1110      | 12       | 830       | 15       | 660       | 20       | 500       |

| 0                    | 101              | 010              | 5      | 20     | 5        | 3000      | 9        | 1660      | 12       | 1250      | 15       | 1000      | 20       | 750       |

| 0                    | 101              | 001              | 5      | 20     | 5        | 4000      | 9        | 2220      | 12       | 1660      | 15       | 1330      | 20       | 1000      |

| 0                    | 101              | 000              | 5      | 20     | 5        | 5000      | 9        | 2770      | 12       | 2080      | 15       | 1660      | 20       | 1250      |

| 0                    | 100              | 111              | 9      | 12     | 5        | 1800      | 9        | 1000      | 12       | 750       | NA       | NA        |          |           |

| 0                    | 100              | 110              | 9      | 12     | 5        | 2400      | 9        | 1330      | 12       | 1000      | NA       | NA        |          |           |

| 0                    | 100              | 101              | 9      | 12     | 5        | 3600      | 9        | 2000      | 12       | 1500      | NA       | NA        |          |           |

| 0                    | 100              | 100              | 9      | 12     | 5        | 4800      | 9        | 2660      | 12       | 2000      | NA       | NA        |          |           |

| 0                    | 100              | 011              | 9      | 12     | 5        | 5000      | 9        | 3000      | 12       | 2250      | NA       | NA        |          |           |

| 0                    | 100              | 010              | 9      | 12     | 5        | 5000      | 9        | 4000      | 12       | 3000      | NA       | NA        |          |           |

| 0                    | 100              | 001              | 9      | 12     | 5        | 5000      | 9        | 5000      | 12       | 3750      | NA       | NA        |          |           |

| 0                    | 100              | 000              | 9      | 15     | 5        | 1800      | 9        | 1000      | 12       | 750       | 15       | 600       | NA       | NA        |

| 0                    | 011              | 111              | 9      | 15     | 5        | 3000      | 9        | 1660      | 12       | 1250      | 15       | 1000      | NA       | NA        |

| 0                    | 011              | 110              | 9      | 15     | 5        | 4000      | 9        | 2220      | 12       | 1660      | 15       | 1330      | NA       | NA        |

| 0                    | 011              | 101              | 9      | 15     | 5        | 5000      | 9        | 3000      | 12       | 2250      | 15       | 1800      | NA       | NA        |

| 0                    | 011              | 100              | 9      | 15     | 5        | 5000      | 9        | 4000      | 12       | 3000      | 15       | 2400      | NA       | NA        |

| Table_SEL<br>Setting | PSEL2<br>Setting | PSEL1<br>Setting | Min. V | Max. V | PDO1     |           | PDO2     |           | PDO3     |           | PDO4     |           | PDO5     |           |

|----------------------|------------------|------------------|--------|--------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|-----------|

|                      |                  |                  |        |        | V<br>(V) | I<br>(mA) |

| 0                    | 011              | 011              | 9      | 15     | 5        | 5000      | 9        | 5000      | 12       | 3750      | 15       | 3000      | NA       | NA        |

| 0                    | 011              | 010              | 9      | 20     | 5        | 1800      | 9        | 1000      | 12       | 750       | 15       | 600       | 20       | 450       |

| 0                    | 011              | 001              | 9      | 20     | 5        | 3000      | 9        | 1660      | 12       | 1250      | 15       | 1000      | 20       | 750       |

| 0                    | 011              | 000              | 9      | 20     | 5        | 4000      | 9        | 2220      | 12       | 1660      | 15       | 1330      | 20       | 1000      |

| 0                    | 010              | 111              | 9      | 20     | 5        | 5000      | 9        | 3000      | 12       | 2250      | 15       | 1800      | 20       | 1350      |

| 0                    | 010              | 110              | 9      | 20     | 5        | 5000      | 9        | 4000      | 12       | 3000      | 15       | 2400      | 20       | 1800      |

| 0                    | 010              | 101              | 9      | 20     | 5        | 5000      | 9        | 5000      | 12       | 3750      | 15       | 3000      | 20       | 2250      |

| 0                    | 010              | 100              | 12     | 15     | 5        | 2000      | 12       | 830       | 15       | 660       | NA       | NA        |          |           |

| 0                    | 010              | 011              | 12     | 15     | 5        | 3000      | 12       | 1250      | 15       | 1000      | NA       | NA        |          |           |

| 0                    | 010              | 010              | 12     | 15     | 5        | 4800      | 12       | 2000      | 15       | 1600      | NA       | NA        |          |           |

| 0                    | 010              | 001              | 12     | 15     | 5        | 5000      | 12       | 2500      | 15       | 2000      | NA       | NA        |          |           |

| 0                    | 010              | 000              | 12     | 15     | 5        | 5000      | 12       | 3000      | 15       | 2400      | NA       | NA        |          |           |

| 0                    | 001              | 111              | 12     | 15     | 5        | 5000      | 12       | 3750      | 15       | 3000      | NA       | NA        |          |           |

| 0                    | 001              | 110              | 12     | 15     | 5        | 5000      | 12       | 5000      | 15       | 4000      | NA       | NA        |          |           |

| 0                    | 001              | 101              | 12     | 20     | 5        | 2000      | 12       | 830       | 15       | 660       | 20       | 500       | NA       | NA        |

| 0                    | 001              | 100              | 12     | 20     | 5        | 3000      | 12       | 1250      | 15       | 1000      | 20       | 750       | NA       | NA        |

| 0                    | 001              | 011              | 12     | 20     | 5        | 4800      | 12       | 2000      | 15       | 1600      | 20       | 1200      | NA       | NA        |

| 0                    | 001              | 010              | 12     | 20     | 5        | 5000      | 12       | 3000      | 15       | 2400      | 20       | 1800      | NA       | NA        |

| 0                    | 001              | 001              | 12     | 20     | 5        | 5000      | 12       | 3750      | 15       | 3000      | 20       | 2250      | NA       | NA        |

| 0                    | 001              | 000              | 12     | 20     | 5        | 5000      | 12       | 5000      | 15       | 4000      | 20       | 3000      | NA       | NA        |

| 0                    | 000              | 111              | 15     | 20     | 5        | 2000      | 15       | 660       | 20       | 500       | NA       | NA        |          |           |

| 0                    | 000              | 110              | 15     | 20     | 5        | 3000      | 15       | 1000      | 20       | 750       | NA       | NA        |          |           |

| 0                    | 000              | 101              | 15     | 20     | 5        | 4000      | 15       | 1330      | 20       | 1000      | NA       | NA        |          |           |

| 0                    | 000              | 100              | 15     | 20     | 5        | 5000      | 15       | 1660      | 20       | 1250      | NA       | NA        |          |           |

| 0                    | 000              | 011              | 15     | 20     | 5        | 5000      | 15       | 2000      | 20       | 1500      | NA       | NA        |          |           |

| 0                    | 000              | 010              | 15     | 20     | 5        | 5000      | 15       | 3000      | 20       | 2250      | NA       | NA        |          |           |

| 0                    | 000              | 001              | 15     | 20     | 5        | 5000      | 15       | 4000      | 20       | 3000      | NA       | NA        |          |           |

| 0                    | 000              | 000              | 15     | 20     | 5        | 5000      | 15       | 5000      | 20       | 3750      | NA       | NA        |          |           |

## 15.10 Path Option

| Path Option Setting | Resistance between Path_Opt and GND (unit: kΩ, ±1%) | 0x3F[2:0] | Behavior                                                        | HV Bound                                   | LV Bound                                               |

|---------------------|-----------------------------------------------------|-----------|-----------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------|

| Option 7            | Open                                                | 111       | The same with path option = 000                                 | The same with path option 0                | The same with path option 0                            |

| Option 6            | 887                                                 | 110       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | 20V                                        | 5V                                                     |

| Option 5            | 649                                                 | 101       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | 15V                                        | 5V                                                     |

| Option 4            | 453                                                 | 100       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | 12V                                        | 5V                                                     |

| Option 3            | 324                                                 | 011       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | 9V                                         | 5V                                                     |

| Option 2            | 143                                                 | 010       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | 5V                                         | 5V                                                     |

| Option 1            | 56.2                                                | 001       | PATHEN is low no matter if Sink PDO is matched with Source PDO. | Depending on Max. V of the Sink capability | Match: Depending on the requested PDO.<br>Mismatch: 5V |

| Option 0            | 0                                                   | 000       | Match: PATHEN is low.<br>Mismatch: PATHEN is high.              | Depending on Max. V of the Sink capability | Match: Depending on the requested PDO.<br>Mismatch: 5V |

The RT1719A will compare the source ability with the sink capability according to Table\_SEL, PSEL2, and PSEL1. The match condition is that a voltage in the source capability exactly meets a voltage in the sink capability, and the current provided by the source at that voltage is greater than or equal to the current at the same voltage in the sink capability.

| Source Type    | No Rp (VBUS Only) |       | Type-C Only     | PD                                 |

|----------------|-------------------|-------|-----------------|------------------------------------|

| Source Ability | Voltage           | 5V    | 5V              | Depending on "Source_Capabilities" |

|                | Current           | 500mA | Depending on Rp | Depending on "Source_Capabilities" |

## 15.11 HV Bound and LV Bound

When VBUS is higher than the HV bound, PATHEN will be floating to turn off PMOS for power path, CC pins will be opened and INT\_VBUS\_HV will be 1 (0x33[7] = 1). When VBUS is lower than the LV bound, PATHEN will be floating to turn off PMOS for power path and INT\_VBUS\_LV will be 1 (0x33[6] = 1).

### 15.12 PD Suspend Information

When the Source sends the Source\_Capabilities with a single PDO (5V/0A) and the RT1719A requests the PDO, the sink system is limited to consume Vbus power below 5V/5mA. After the Source accepts the request from RT1719A, the IRQB (Pin16) will be pulled low to inform the system if 0x2F[0]=1, and the power path will be turned off. After receiving new Source\_Capabilities, the power path will be turned on or off depending on Path\_Opt.

| Address | Bit | Bit Name           | Default | Type | Description                                                                           |

|---------|-----|--------------------|---------|------|---------------------------------------------------------------------------------------|

| 0x2F    | 0   | M_RX_5V0A_ACCEPT   | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                |

| 0x35    | 0   | INT_RX_5V0A_ACCEPT | 0       | WC   | 0: RX_5V0A_ACCEPT no changed. Cleared. (default)<br>1: RX_5V0A_ACCEPT status changed. |

| 0x38    | 7   | RX_5V0A_ACCEPT     | 0       | R    | PD suspend (25mW).<br>0: No PD suspend. (default)<br>1: PD suspend.                   |

## 16 Application Information

### (Note 6)

The system master can obtain port information and access PD messages through I<sup>2</sup>C bus. Sections 16.1 to 16.5 describe CC status, DR Swap, reading Source Capability, Request Source PDO, and editing Sink Capability Extend.

#### 16.1 CC Status

The CC status is reported in register 0x38[3:0]. Refer to the register map for more detailed information.

#### 16.2 DR Swap

Except for responding to DR Swap automatically according to USB setting (at pin 13), the system master can initiate DR Swap by writing 0x03[7] = 1. Make sure that the DR Swap is supported (0x3E[1:0] = 11) before initiating DR Swap (0x03[7] = 1) or I<sup>2</sup>C error will be triggered (0x30[0] = 1.) If Rp = 1.5A at PD3.0 or later version, initiating DR Swap (0x30[7] = 1) will also trigger I<sup>2</sup>C error (0x30[0] = 1). Set DRS\_FSM\_SRST\_EN (0x04[2] = 1) first and then initiate DR Swap (0x03[7] = 1.) After initiating DR Swap successfully, there will be four results as reported in 0x34[7:4].

| Address | Bit | Bit Name        | Default | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----|-----------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x03    | 7   | TX_DR_SWAP      | 0       | RW   | Initiated Data Role Swap request to source. To request change data role from DFP to UFP or UFP to DFP is controlled by MCU.<br>Requesting Data Role Swap when USB_SET configuration to not a dual role data will trigger INT_I2C_ERR.<br>Requesting Data Role Swap when TXNG(RP 1.5A) and negotiated at PD3.0 or later version will trigger INT_I2C_ERR.<br>0: No DR_Swap sent. (default)<br>1: DR_Swap sent and then 0x03[7] returns to 0. |

| 0x04    | 2   | DRS_FSM_SRST_EN | 0       | RW   | Enable DRS FSM to be reset to default when Policy triggers to transmit "Soft Reset" message.<br>0: no reset (default)<br>1: reset                                                                                                                                                                                                                                                                                                           |

| 0x2E    | 7   | M_DR_SW_ACCEPT  | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 6   | M_DR_SW_REJECT  | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 5   | M_DR_SW_WAIT    | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                                                                                                                                                                                                                                                                                                                                      |

|         | 4   | M_DR_SW_TIMEOUT | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x30    | 0   | M_I2C_ERR       | 0       | RW   | 0: Interrupt masked (default)<br>1: Interrupt unmasked                                                                                                                                                                                                                                                                                                                                                                                      |

| Address | Bit | Bit Name           | Default | Type | Description                                                                                                                                                                                                                                                                                       |

|---------|-----|--------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x34    | 7   | INT_DRD_SW_ACCEPT  | 0       | WC   | 0: No DR_Swap transmitted, or Accept not received. Cleared. (default)<br>1: Transmit DR_Swap and Accept received.                                                                                                                                                                                 |

|         | 6   | INT_DRD_SW_REJECT  | 0       | WC   | 0: No DR_Swap transmitted, or Reject not received. Cleared. (default)<br>1: Transmit DR_Swap and Reject received.                                                                                                                                                                                 |

|         | 5   | INT_DRD_SW_WAIT    | 0       | WC   | 0: No DR_Swap transmitted, or Wait not received. Cleared. (default)<br>1: Transmit DR_Swap and Wait received.                                                                                                                                                                                     |

|         | 4   | INT_DRD_SW_TIMEOUT | 0       | WC   | 0: No DR_Swap transmitted. Cleared. (default)<br>1: Transmit DR_Swap and no any response.                                                                                                                                                                                                         |

| 0x36    | 0   | INT_I2C_ERR        | 0       | WC   | 0: Cleared (default)<br>1: Transmit "Request" with invalid Object setting. E.g. Obj = 0, or Not Existing Obj number.<br>Transmit "DR_Swap" when Pins are configured to not a dual role data.<br>Transmit "Request", "DR_Swap" and "Get_Source_Cap" when RP level is 1.5A in PD 3.0 communication. |

### 16.3 Reading Source Capability

The RT1719A can record the source cap in the register from 0x11 to 0x2C. There is one Source PDO with  $V_{BUS} = 5V$  at least and seven Source PDO at most in the Source Capability. Register 0x0F[7:5] shows how many Source PDO in the Source Capability.

Note that the RT1719A will only compare the fixed supply of Source PDO with Sink PDO.

The selected Source PDO is recorded in register 0x10[2:0].

| PDO                 | Information  | Register                            | Description                                                                                    |

|---------------------|--------------|-------------------------------------|------------------------------------------------------------------------------------------------|

| 1 <sup>st</sup> PDO | Power Type   | 0x14[7:6]                           | 00: Fixed supply<br>01: Battery supply<br>10: Variable supply<br>11: Programmable power supply |

|                     | Vbus Voltage | 0x13[3:0] (MSB) and 0x12[7:2] (LSB) | Unit: 50mV                                                                                     |

|                     | Current      | 0x12[1:0] (MSB) and 0x11[7:0] (LSB) | Unit: 10mA                                                                                     |

| 2 <sup>nd</sup> PDO | Power Type   | 0x18[7:6]                           | 00: Fixed supply<br>01: Battery supply<br>10: Variable supply<br>11: Programmable power supply |

|                     | Vbus Voltage | 0x17[3:0] (MSB) and 0x16[7:2] (LSB) | Unit: 50mV                                                                                     |

|                     | Current      | 0x16[1:0] (MSB) and 0x15[7:0] (LSB) | Unit: 10mA                                                                                     |

| PDO                 | Information  | Register                            | Description                                                                                    |

|---------------------|--------------|-------------------------------------|------------------------------------------------------------------------------------------------|

| 3 <sup>rd</sup> PDO | Power Type   | 0x1C[7:6]                           | 00: Fixed supply<br>01: Battery supply<br>10: Variable supply<br>11: Programmable power supply |

|                     | Vbus Voltage | 0x1[3:0] (MSB) and 0x1A[7:2] (LSB)  | Unit: 50mV                                                                                     |

|                     | Current      | 0x1A[1:0] (MSB) and 0x19[7:0] (LSB) | Unit: 10mA                                                                                     |