# 3 Channel DC-DC Converters +LDO +LSW PMIC with I<sup>2</sup>C Interface for Industrial and Automotive Application

## **General Description**

The RT2070T is a highly-integrated low-power high-performance analog SOC with PMIC (Power Management IC) in one single chip designed for Industrial/Automotive applications.

The RT2070T PMIC includes one high voltage synchronous step-down DC-DC converter, two low voltage synchronous step-down DC-DC converters, one low dropout LDO and one load switch with soft-start control and current limit. All MOSFETs are integrated, and compensation networks are built-in.

The RT2070T also uses I<sup>2</sup>C interface to set timing of power on/off, sequence and discharge function, and includes power good indicator (PGOOD).

The RT2070T is an Automotive-Grade Product that is AEC-Q100 Grade 1 Qualified and provides fault condition protections, including over-current protection, undervoltage lockout, over-voltage protection and over-temperature protection.

## **Applications**

- Industrial/Automotive Camera Module

- Car Infotainment

#### **Features**

- Input Voltage Operating Range is 4.5V to 15V

- CH1 HV-Step-Down Regulator : V<sub>IN</sub> Range is 4.5V to 15V

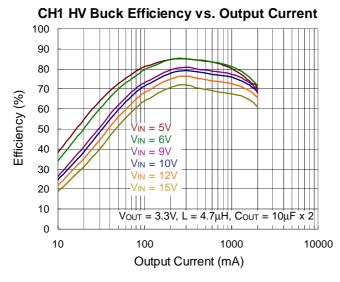

- Support Up to 2A Loading With Up to 90% Efficiency

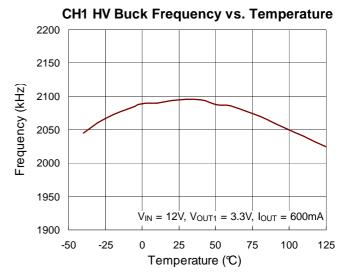

- ▶ Switching Frequency is 2MHz

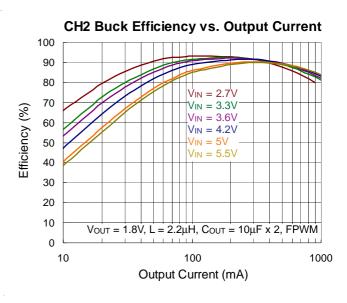

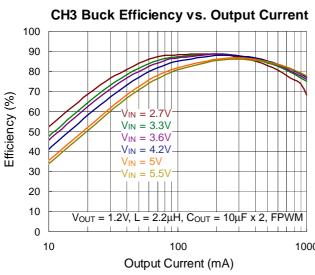

- CH2/3 LV Step-Down Regulator : V<sub>IN</sub> Range is 2.7V to 5.5V

- ► Support Up to 1A Loading, With Up to 90% Efficiency

- ▶ Switching Frequency is 2MHz

- Linear Regulator: VIN Range is 2.7V to 5.5V

- → Max Loading 0.5A

- Load Switch (LSW): VIN Range is 2.7V to 5.5V

- ▶ Max Loading 0.5A

- Sequence Can be Controlled by Setting the Resistances of the SEQ Pin

- AEC-Q100 Grade 1 Qualified

## **Marking Information**

5P= : Product Code YMDNN : Date Code

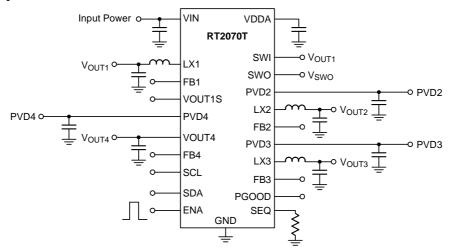

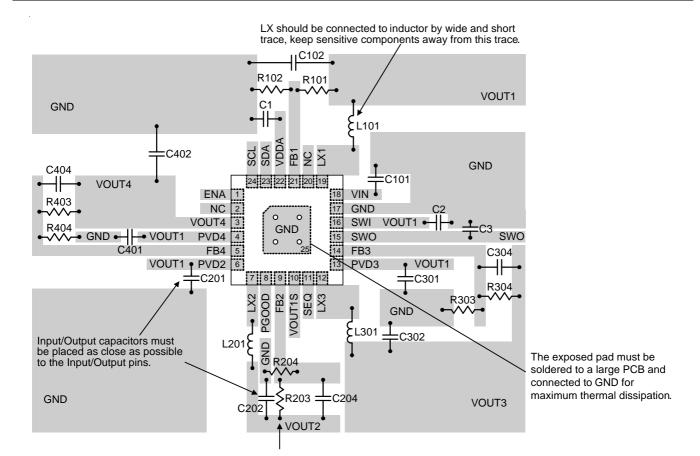

## **Simplified Application Circuit**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Ordering Information**

RT2070T Package Type

QW: WQFN-24L 4x4 (W-Type)

(Exposed Pad-Option 1)

Lead Plating System

G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

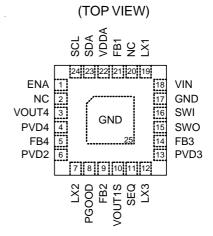

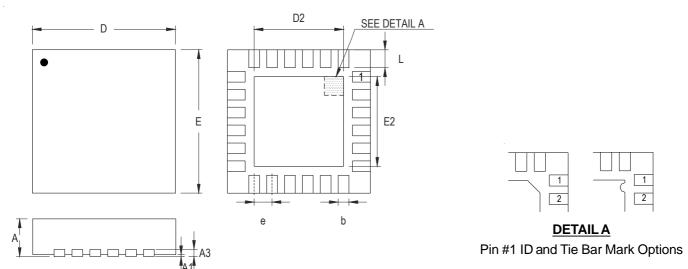

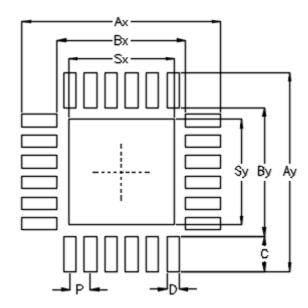

## **Pin Configuration**

WQFN-24L 4X4

## **Functional Pin Description**

| Pin No.                 | Pin Name | Pin Function                                                                                                                            |

|-------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | ENA      | IC enable control input. Hi active. Internal pull-down resister (100k $\Omega$ ).                                                       |

| 2, 20                   | NC       | No internal connection.                                                                                                                 |

| 3                       | VOUT4    | Output voltage regulation node for LDO4.                                                                                                |

| 4                       | PVD4     | Power input for LDO4.                                                                                                                   |

| 5                       | FB4      | Feedback voltage input for LDO4                                                                                                         |

| 6                       | PVD2     | Power input for Buck2.                                                                                                                  |

| 7                       | LX2      | Switch node of Buck2.                                                                                                                   |

| 8                       | PGOOD    | Buck1 to Buck 3, LDO4 and LSW PGOOD output node by open drain. Hi active.                                                               |

| 9                       | FB2      | Feedback voltage input for Buck2.                                                                                                       |

| 10                      | VOUT1S   | HV buck output voltage for OVP detection. Input HV buck (CH1) output.                                                                   |

| 11                      | SEQ      | Power sequence selection.                                                                                                               |

| 12                      | LX3      | Switch node of Buck3.                                                                                                                   |

| 13                      | PVD3     | Power input for Buck3.                                                                                                                  |

| 14                      | FB3      | Feedback voltage input for Buck3.                                                                                                       |

| 15                      | SWO      | Load switch output.                                                                                                                     |

| 16                      | SWI      | Load switch input.                                                                                                                      |

| 17,<br>25 (Exposed Pad) | GND      | IC power ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum thermal dissipation and current flow. |

| 18                      | VIN      | Power input for Buck1.                                                                                                                  |

| 19                      | LX1      | Switch node of Buck1.                                                                                                                   |

| 21                      | FB1      | Feedback voltage input for Buck1.                                                                                                       |

| 22                      | VDDA     | IC internal analog power output 4.45V (typ.). Only $1\mu F$ and SCL/SDA pull up resister can be connected.                              |

| 23                      | SDA      | I <sup>2</sup> C data input/output.                                                                                                     |

| 24                      | SCL      | I <sup>2</sup> C clock input.                                                                                                           |

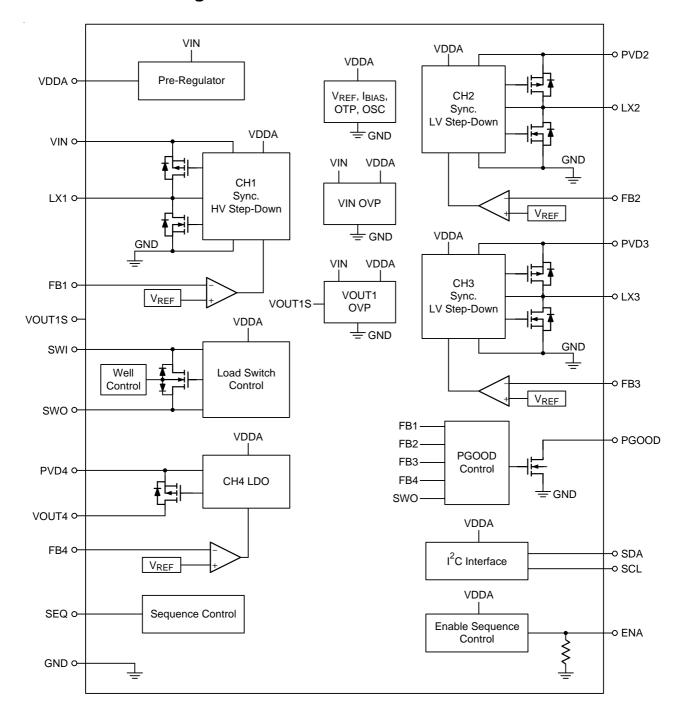

## **Functional Block Diagram**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## Operation

The RT2070T is a highly-integrated solution for automotive systems, including a 1-CH HV step-down DC-DC converter, 2-CH LV step-down DC-DC converter and 1-CH LDO. The RT2070T application mechanism will be introduced in later sections.

The power-on and power-off sequences are detected in the SEQ pin. Additionally, users control the next power on/off sequence by setting I<sup>2</sup>C registers from A01 to A12 when VDDA exists.

When the ENA pin is at Hi level, the PMIC follows the power-on sequence to turn on channels.

The IC turns on base and calibrates. Time is less than 500µs; during this time, the IC doesn't allow users to set I<sup>2</sup>C data.

#### **Pre-Regulator**

This HV regulator is designed to handle input operation range of 4.5V to 15V. The regulator provides low voltage power to supply the internal control circuits and avoid connecting any load from VDDA pin. In noisy environments, a 1µF decoupling capacitor must be connected between VDDA and GND.

The I<sup>2</sup>C compatible interface remains fully functional if VIN and VDDA are present. If the VDDA is under the threshold voltage, all internal registers are reset to their default values.

#### **Over-Temperature Protection**

An Over-Temperature Protection (OTP) is featured in the device. The protection is triggered to force device shutdown when the junction temperature exceeds 160°C typically. If OTP is set to Hiccup once the junction temperature drops below the hysteresis 20°C typically, the device is re-enabled and automatically reinstated the power-on sequence.

#### Input Over-Voltage Protection

The device provides an input Over-Voltage Protection (OVP) once the input voltage exceeds 15.5V typically; the OVP function is started and all channels will be turned off after 5ms. If OVP is set to Hiccup, once the input voltage drops below the hysteresis 2V typically, the device is re-enabled and automatically reinstates the power-on sequence. This OVP feature can easily minimize the input overshoot.

#### **ENA: IC Enable Pin**

The ENA pin is a device enable input. Pulling the ENA pin to logic low that is typically less than the set threshold voltage 1.2V shuts the device down and it enters a low quiescent current state of about 20µA. The regulator starts switching again once the ENA pin voltage exceeds the threshold voltage of 2V. In addition, the ENA pin features an internal  $100k\Omega$  pull-low resistor.

#### **Power Good (PGOOD) Control**

The power good output is an open-drain output and needs to be connected to a voltage source with a pull-up  $10k\Omega$ resistor to avoid PGOOD floating. Each channel turns on according to power-on sequence. When the last channel reaches 90% of its target voltage, PMU (Power Management Unit) starts counting  $t_{PGOOD} = 5ms$  (Power Good Delay Time) then pulls PGOOD Hi until ENA is pulled low or any other protection happens.

## Absolute Maximum Ratings (Note 1)

| • Analog Base Input Voltage, VIN                                            | -0.3V to 20V   |

|-----------------------------------------------------------------------------|----------------|

| Control Output Voltage, PGOOD                                               | -0.3V to 6V    |

| Control Input Voltage, ENA                                                  | -0.3V to 15V   |

| • HV Buck Power Switch (DC), LX1                                            | -0.3V to 15V   |

| • LV Buck Input Voltage, PVD2/3                                             | -0.3V to 6V    |

| • LV Buck Power Switch (DC), LX2, LX3                                       | -0.3V to 6V    |

| • LV Buck Power Switch (Spike Voltage < 200ns), LX2, LX3                    | -0.3V to 6V    |

| • Other Pins                                                                | -0.3V to 6V    |

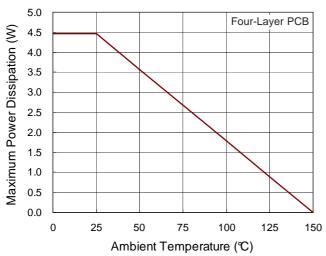

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WQFN-24L 4x4                                                                | 4.46W          |

| Package Thermal Resistance (Note 2) (Note 3)                                |                |

| WQFN-24L 4x4, $\theta_{JA}$                                                 | 28°C/W         |

| WQFN-24L 4x4, $\theta_{JC}$                                                 | 7°C/W          |

| • Junction Temperature                                                      | 150°C          |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Storage Temperature Range                                                 | –65°C to 150°C |

| • ESD Susceptibility (Note 4)                                               |                |

| HBM (Human Body Model)                                                      | 2kV            |

|                                                                             |                |

| Recommended Operating Conditions (Note 5)                                   |                |

• Junction Temperature Range ------ -40°C to 150°C • Ambient Temperature Range ----- --- -40°C to 125°C

## **Electrical Characteristics**

(Note 8)

| Parameter                            | Symbol           | Test Conditions                                                                                                   | Min  | Тур  | Max  | Unit |

|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VIN Operation Voltage<br>Range       |                  |                                                                                                                   | 4.5  |      | 15   | >    |

| Quiescent Current                    | lQ               | V <sub>IN</sub> = 5V, Bucks and LDOs are<br>ON with no load, HVBuck<br>switching, LVBucks are in FCCM<br>mode.    | 8    | 10   | 12   | mA   |

| Quiescent Current                    | IQ_PSM           | V <sub>IN</sub> = 5V, Bucks and LDOs are<br>ON with no load, HVBuck<br>non-switching, LVBucks are in<br>PSM mode. | 600  | 1000 | 1200 | μΑ   |

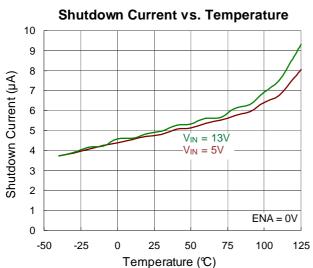

| Shutdown Current                     | I <sub>SHD</sub> | V <sub>IN</sub> = 5V, ENA = 0V, LDOs, Bucks are OFF.                                                              | 2    | 7    | 20   | μΑ   |

| Over-Temperature Protection          | OTP              |                                                                                                                   | 150  | 160  | 170  | °C   |

| OTP Hysteresis (Note 6)              | OTP_HYS          |                                                                                                                   | 10   | 20   | 30   | °C   |

| VIN OVP (Hysteresis High)            | OVP              |                                                                                                                   | 14.5 | 15.5 | 16.5 | V    |

| VIN OVP Hysteresis (Gap)<br>(Note 7) | OVP_HYS          |                                                                                                                   | 1.5  | 2    | 2.5  | V    |

Copyright©2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                         | Symbol               | Test Conditions                                                                                                                               | Min          | Тур | Max          | Unit |  |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|--------------|------|--|

| VIN UVLO2                         | UVLO2                |                                                                                                                                               | 3.7          | 3.9 | 4.1          | V    |  |

| UVLO2 Hysteresis (Gap)            | UVLO2_HYS            |                                                                                                                                               | 0.4          | 0.5 | 0.6          | V    |  |

| VDDA Voltage                      |                      |                                                                                                                                               | 4.2          | 4.5 | 4.8          | V    |  |

| Switching Frequency (CH1/CH2/CH3) | fsw                  |                                                                                                                                               | 2<br>-10%    | 2   | 2<br>+10%    | MHz  |  |

| CH1 HV-Buck                       |                      |                                                                                                                                               |              |     |              |      |  |

| Input Voltage Range               | VIN                  |                                                                                                                                               | 4.5          |     | 15           | V    |  |

| Output Voltage Range              | Vouт                 |                                                                                                                                               | 1.6          | 1   | 5            | >    |  |

| Feedback Voltage Accuracy         | FB1                  |                                                                                                                                               | 0.8 –<br>3%  | 0.8 | 0.8 +<br>3%  | V    |  |

| FB1 Under-Voltage Protection      | FB1_UVP              | FB1 = FB1 x 0.5 (50%)                                                                                                                         | 0.3          | 0.4 | 0.5          | V    |  |

| Suggest Inductor                  | LHVBuck              | Refer to Typical Application<br>Circuit                                                                                                       | 1            | 4.7 |              | μΗ   |  |

| Current Limit                     | CL1                  | T <sub>A</sub> = 25℃                                                                                                                          | 3 –<br>15%   | 3   | 3 +<br>15%   | ۸    |  |

| Current Limit                     | CL1_T                | -40℃ ≤ T <sub>A</sub> ≤ 125℃                                                                                                                  | 1 3 1        |     | 3 +<br>25%   | A    |  |

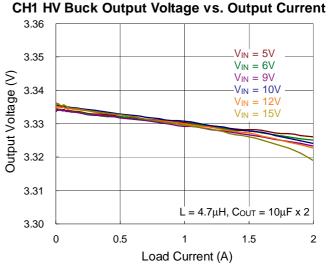

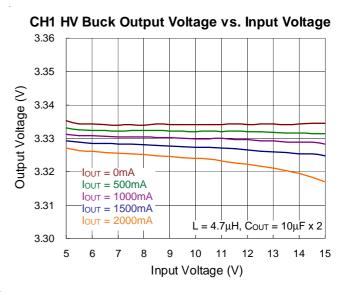

| Load Regulation                   |                      | T <sub>A</sub> = 25℃, V <sub>IN</sub> = 6V, V <sub>OUT</sub> = 3.3V,<br>Load = 0mA to 2000mA<br>Refer to Typical Operating<br>Characteristics | -1           |     | 1            | %    |  |

| Line Regulation                   |                      | T <sub>A</sub> = 25℃, V <sub>IN</sub> = 5V to 15V, V <sub>OUT</sub> = 3.3V, Load = 1000mA Refer to Typical Operating Characteristics          | -1           |     | 1            | %    |  |

| P-MOSFET On-Resistance            | R <sub>DS_ON_P</sub> | V <sub>IN</sub> = 5V, I <sub>LX1</sub> = 800mA                                                                                                | 230          | 330 | 470          | mΩ   |  |

| N-MOSFET On-Resistance            | RDS_ON_N             | V <sub>IN</sub> = 5V, I <sub>LX1</sub> = 800mA                                                                                                | 100          | 150 | 250          | mΩ   |  |

| Soft-Start Time                   | t <sub>r1</sub>      | $V_{OUT1} \ge 0.9 \text{ x } V_{Target},$ $I_{OUT} = 0 \text{mA}$                                                                             | 0.8          | 1.1 | 1.5          | ms   |  |

| Discharge Resistance              |                      | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 3.3V                                                                                                 | 870          | 970 | 1070         | Ω    |  |

| Load Switch (LSW)                 |                      |                                                                                                                                               |              |     |              |      |  |

| Supply Voltage                    | V <sub>swi</sub>     |                                                                                                                                               | 2.7          |     | 5.5          | V    |  |

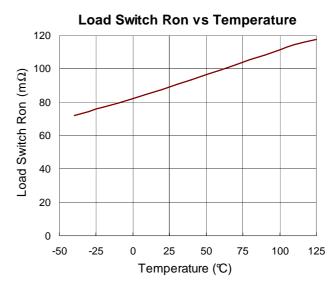

| MOSFET On-Resistance              | R <sub>DS_ON</sub>   | SWI = 3.3V, I <sub>OUT</sub> = 500mA                                                                                                          | 60           | 85  | 120          | mΩ   |  |

| Command Limit                     | CLSW                 | T <sub>A</sub> = 25℃                                                                                                                          | 750 –<br>15% | 750 | 750 +<br>15% | A    |  |

| Current Limit                     | CLSW_T               | -40℃ ≤ T <sub>A</sub> ≤ 125℃                                                                                                                  | 750 –<br>20% | 750 | 750 +<br>20% | mA   |  |

| Under-Voltage Threshold           | UVP_sw               | Vswi – Vswo                                                                                                                                   | 0.5          | 0.7 | 0.9          | V    |  |

| Soft-Start Time                   | t <sub>r_sw</sub>    | Vout ≥ 0.9 x V <sub>Target</sub> ,<br>Iout = 0mA                                                                                              | 0.9          | 1.3 | 1.8          | ms   |  |

| Discharge Resistance              |                      | V <sub>OUT1</sub> = 3.3V, SWO = 3.3V                                                                                                          | 400          | 440 | 480          | Ω    |  |

Copyright ©2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                      | Symbol            | Test Conditions                                                                                                                       | Min           | Тур     | Max           | Unit     |  |

|------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|---------------|----------|--|

| Buck2 to Buck3                                 |                   |                                                                                                                                       | '             |         | I.            |          |  |

| Input Voltage Range                            | PVD2/PVD3         |                                                                                                                                       | 2.7           |         | 5.5           | V        |  |

| Output Voltage Range                           | Vout              |                                                                                                                                       | 1             |         | 3.6           | ٧        |  |

| Feedback Voltage Accuracy                      | FB2/3             |                                                                                                                                       | 0.8 –<br>3%   | 0.8     | 0.8 +<br>3%   | V        |  |

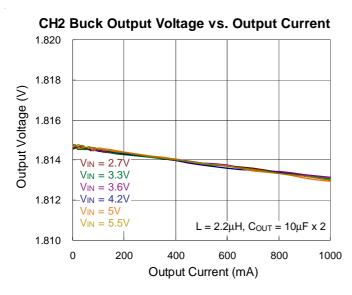

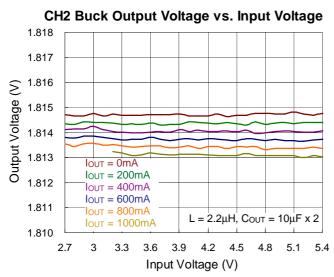

| Efficiency Peak                                | Eff               | V <sub>OUT</sub> = 1.8V, V <sub>IN</sub> = 3.3V, I <sub>LOAD</sub> = 300mA<br>Refer to Typical Operating<br>Characteristics           |               | 92      |               | %        |  |

| Suggest Inductor                               | L <sub>Buck</sub> | Refer to Typical Application<br>Circuit                                                                                               |               | 2.2     |               | μΗ       |  |

| Current Limit                                  | CL2/3             | T <sub>A</sub> = 25℃                                                                                                                  | 1300<br>- 15% | 1300    | 1300<br>+ 15% | mA       |  |

| Carrent Limit                                  | CL2/3_T           | -40℃ ≤ T <sub>A</sub> ≤ 125℃                                                                                                          | 1300<br>- 25% | 1300    | 1300<br>+ 25% | ША       |  |

| FB2/3 Under-Voltage<br>Protection              | UVP2/3            | FB2/3 = FB2/3 x 0.5 (50%)                                                                                                             |               | 0.4     |               | >        |  |

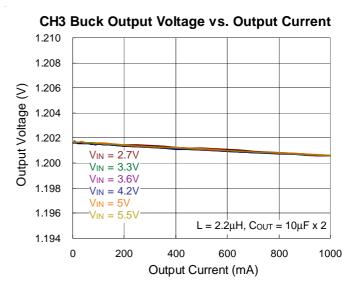

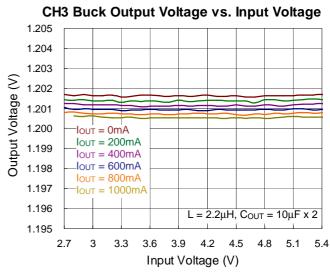

| Load Regulation                                |                   | T <sub>A</sub> = 25℃, PVD2/3 = 3.3V, V <sub>OUT</sub> = 1.2V, Load = 0mA to 1000mA Refer to Typical Operating Characteristics         | -1            |         | 1             | %        |  |

| Line Regulation                                |                   | T <sub>A</sub> = 25℃, PVD2/3 = 3V to 5.5V,<br>V <sub>OUT</sub> = 1.2V, Load = 1000mA<br>Refer to Typical Operating<br>Characteristics | -1            |         | 1             | %        |  |

| P-MOSFET On-Resistance                         | RDS_ON_P          | PVD2/3 = 3.3V                                                                                                                         | 180           | 270     | 370           | mΩ       |  |

| N-MOSFET On-Resistance                         | RDS_ON_N          | PVD2/3 = 3.3V                                                                                                                         | 100           | 175     | 250           | mΩ       |  |

| Soft-Start Time                                | t <sub>r2/3</sub> | V <sub>OUT2/3</sub> ≥ 0.9 x V <sub>Target</sub> , I <sub>OUT</sub> = 0mA                                                              | 0.8           | 1       | 1.5           | ms       |  |

| Discharge Resistance                           |                   | PVD2 = 3.3V, V <sub>OUT</sub> = 1.2V                                                                                                  | 5             | 6       | 7             | Ω        |  |

| Discharge Nesistance                           |                   | PVD3 = 3.3V, V <sub>OUT</sub> = 1.8V                                                                                                  | 6             | 7       | 8             | 22       |  |

| CH4 LDO                                        |                   |                                                                                                                                       |               |         |               |          |  |

| Input Voltage for PVD4                         | PVD4              |                                                                                                                                       | 2.7           |         | 5.5           | V        |  |

| Output Voltage Range                           | Vout              |                                                                                                                                       | 1             |         | 3.6           | V        |  |

| Feedback Voltage Accuracy                      | FB4               |                                                                                                                                       | 0.8 –<br>3%   | 0.8     | 0.8 +<br>3%   | ٧        |  |

| Current Limit                                  | CL4               | T <sub>A</sub> = 25℃                                                                                                                  | 750 –<br>15%  | 1 /50 1 |               | mΛ       |  |

| Current Limit                                  | CL4_T             | -40°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                        | 750 –<br>30%  | 750     | 750 +<br>35%  | mA       |  |

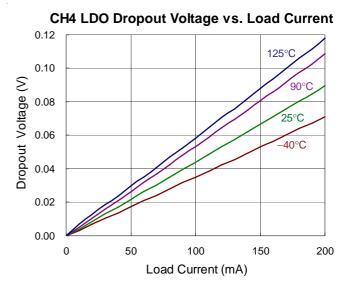

| Dropout Voltage<br>(PVD4 – V <sub>OUT4</sub> ) | VDROP             | I <sub>OUT</sub> = 150mA,<br>PVD4 = V <sub>OUT4</sub> - 0.1V                                                                          | 0.01          | -       | 0.15          | <b>V</b> |  |

Copyright@2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parame                     | eter                            | Symbol                          | Test Conditions                                                                                                                   | Min  | Тур | Max | Unit |

|----------------------------|---------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

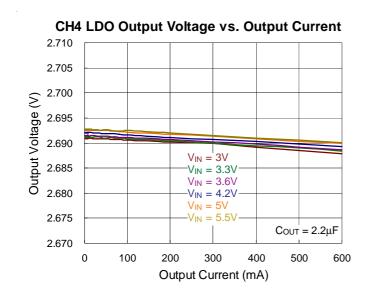

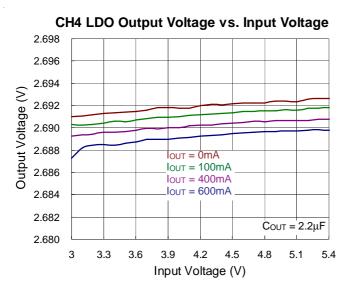

| Line Regulation            |                                 | LiR                             | T <sub>A</sub> = 25℃, PVD4 = 3V to 5V,<br>V <sub>OUT4</sub> = 2.7V, Load = 100mA<br>Refer to Typical Operating<br>Characteristics | -0.5 |     | 0.5 | %    |

| Load Regulation            |                                 | $T_A = 25$ °C,PVD4 = 3.3V, Load |                                                                                                                                   | 0    | 0.1 | 1   | %    |

| FB4 Under-Volta Protection | ge                              | FB4_UVP                         | FB4 = 0.8V x 0.4 (40%)                                                                                                            | 0.2  | 0.3 | 0.4 | V    |

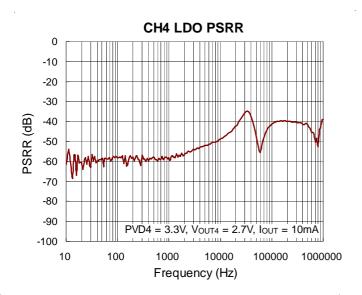

| PSRR                       |                                 |                                 | Feq = 1kHz, I <sub>OUT</sub> = 10mA,<br>V <sub>OUT</sub> = 2.7V<br>Refer to Typical Operating<br>Characteristics                  |      | 60  |     | dB   |

| Soft-Start Time            |                                 | t <sub>r4</sub>                 | V <sub>OUT4</sub> ≥ 0.9 x V <sub>Target</sub> , I <sub>OUT</sub> = 0mA                                                            | 0.6  | 1   | 1.5 | ms   |

| Discharge Resist           | tance                           |                                 | PVD4 = 3.3V, V <sub>OUT</sub> = 2.7V                                                                                              | 380  | 450 | 520 | Ω    |

| Power Good                 |                                 |                                 |                                                                                                                                   |      |     |     |      |

| Power Good Pull<br>Voltage | Power Good Pull-Down<br>Voltage |                                 | PGOOD current equal to 5mA                                                                                                        |      | 200 |     | mV   |

| Power Good Delay Time      |                                 | tpgood                          |                                                                                                                                   |      | 5   |     | ms   |

| Control                    |                                 |                                 |                                                                                                                                   |      |     | •   |      |

| ENA Input Logic-Hi         |                                 |                                 |                                                                                                                                   | 2    |     |     | V    |

| Voltage                    | Logic-Low                       |                                 |                                                                                                                                   |      |     | 0.5 | v    |

| ENA Pull High C            | urrent                          | IPULL                           | $V_{IN}$ = 5V, Temperature = -40°C to 125°C                                                                                       | 20   | 37  | 55  | μΑ   |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}\text{C}$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. The junction temperature( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in watts) according to the formula :  $T_J = T_A + (P_D \times \theta_{JA})$  where  $\theta_{JA}$  (in °C/W) in the package thermal impedance. Another,  $P_{IN} P_O = P_D$  and  $P_O = \eta \times P_{IN} \rightarrow P_D = (1 / \eta 1) \times P_O$  where  $P_{IN}$  is the total input power and Po is the total output power.

- Note 4. Devices are ESD sensitive. Handling precaution is recommended.

- Note 5. The device is not guaranteed to function outside its operating conditions.

- Note 6. When OTP is set to Hiccup by I<sup>2</sup>C.

- Note 7. When VIN OVP is set to Hiccup by I<sup>2</sup>C

- **Note 8.** Limits apply to the recommended  $V_{IN} = 4.5V$  to 15V,  $T_A = -40^{\circ}C$  to 125°C, unless otherwise noted. Minimum and maximum limits are verified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_A = 25^{\circ}C$ , and are provided for reference purposes only.

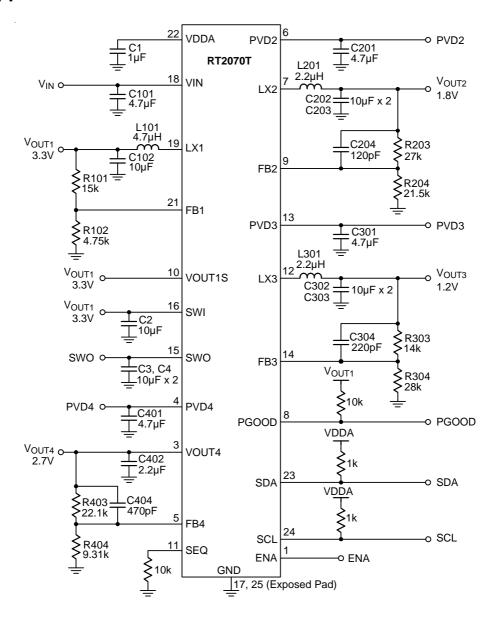

## **Typical Application Circuit**

If there is any CHx is not used that external components still must be existed and keep original application circuit.

If LSW isn't used, user can remove C2, C3 and C4, but the SWI pin must connect to VOUT1 and floating the SWO pin.

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

**Table 1. Suggested Components for Typical Application Circuit**

| Reference                                   | Q'ty | P/N                | Description   | Manufacturer |

|---------------------------------------------|------|--------------------|---------------|--------------|

| C1                                          | 1    | GCM188R61A105KA37D | 1μF/10V/X5R   | MURATA       |

| C2, C3, C4, C102, C202,<br>C203, C302, C303 | 8    | GCM21BR71A106KE22L | 10μF/10V/X7R  | MURATA       |

| C101                                        | 1    | GRM31CR71E475KA40  | 4.7μF/25V/X7S | MURATA       |

| C201, C301, C401                            | 3    | GCM21BC71A475KA73L | 4.7μF/10V/X7S | MURATA       |

| C402                                        | 1    | GCM21BR71A225KA01  | 2.2μF/10V/X7R | MURATA       |

| C204                                        | 1    | GCM1885C1H121JA16# | 120pF/50V/C0G | MURATA       |

| C304                                        | 1    | GCM1885C1H221JA16D | 220pF/50V/C0G | MURATA       |

| C404                                        | 1    | GCM1885C1H470JA16D | 470pF/50V/C0G | MURATA       |

| L101                                        | 1    | LQH5BPB4R7NT0L     | 4.7μΗ         | MURATA       |

| L201, L301                                  | 2    | LQH32PB2R2NN0L     | 2.2μΗ         | MURATA       |

| R101                                        | 1    | RM06FTN1502        | 15k/1%        | TA-I         |

| R102                                        | 1    | RM06FTN4751        | 4.75k/1%      | TA-I         |

| R203                                        | 1    | RM06FTN2702        | 27k/1%        | TA-I         |

| R204                                        | 1    | RM06FTN2152        | 21.5k/1%      | TA-I         |

| R303                                        | 1    | RM06FTN1402        | 14k/1%        | TA-I         |

| R304                                        | 1    | RM06FTN2802        | 28k/1%        | TA-I         |

| R403                                        | 1    | RM06FTN2212        | 22.1k/1%      | TA-I         |

| R404                                        | 1    | RM06FTN9311        | 9.31k/1%      | TA-I         |

## **Typical Operating Characteristics**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

## **Applications Information**

The RT2070T is a highly integrated automotive system Power Management IC that contains 3-CH switching DC-DC converters and one generic LDO and one load switch.

#### CH1: HV Step-Down DC-DC Converter

CH1 is a HV step-down converter for LV DC-DC converter power. The current-mode PWM converter with integrated internal MOSFETs and compensation network operates at fixed frequency. The output voltage of CH1 is set by external feedback resistors, as expressed in the following equation:

$$VOUT1 = (1 + R101 / R102) \times V_{FB1}$$

Where V<sub>FB1</sub> is 0.8V typically and suggested value for R101 is 10k to 500k.

#### CH2: Synchronous Step-Down DC-DC Converter

CH2 is a synchronous step-down converter for I/F power and it operates with typically 2MHz fixed frequency Pulse Width Modulation (PWM) at moderate to heavy load currents. At light load currents, the converter can automatically enter Power Save Mode and operates in PFM mode which can be set by I<sup>2</sup>C interface.

The converter output voltage is externally adjustable using a resistor divider at FB2.

The output voltage of CH2 is set by external feedback resistors, as expressed in the following equation:

$$VOUT2 = (1 + R203 / R204) \times V_{FB2}$$

Where V<sub>FB2</sub> is 0.8V typically and suggested value for R203 is 10k to 600k.

#### CH3: Synchronous Step-Down DC-DC Converter

CH3 is suitable for logic power. The converter with integrated internal MOSFETs and compensation network operates at synchronous PSM or fixed frequency PWM current mode which can be set by the I<sup>2</sup>C interface. The output voltage of CH3 is set by external feedback resistors, as expressed in the following equation:

$$VOUT3 = (1 + R303 / R304) \times V_{FB3}$$

Where V<sub>FB3</sub> is 0.8V typically and suggested value for R303 is 10k to 600k.

For CH2 and CH3, to improve control performance using a feedforward capacitor in parallel to R203 or R303 is recommended, the value for the feedforward capacitor can be calculated using below formula:

For CH2,

$$C_{FF} = \frac{3.16 \mu s}{R203}$$

For CH3,  $C_{FF} = \frac{3.16 \mu s}{R303}$

#### CH4: Generic LDO

CH4 is a low-dropout (LDO) voltage regulator which offers benefits of high input voltage and low-dropout voltage for sensor power. The output voltage of CH4 is set by external feedback resistors, as expressed in the following equation:

$$VOUT4 = (1 + R403 / R404) \times V_{FB4}$$

Where V<sub>FB4</sub> is 0.8V typically and suggested value for R403 is 5k to 500k.

To improve control performance using a feedforward capacitor in parallel to R403 is recommended, the value for the feedforward capacitor can be calculated using below formula:

$$C_{FF} = \frac{10.4 \mu s}{R403}$$

#### Load Switch: Load Switch

The load switch for core power is equipped with soft-start control and current limit function.

If LSW isn't used, user can remove C2, C3 and C4, but the SWI pin must connect to VOUT1 and floating the SWO pin.

#### Input and Output Capacitors Selection

The RT2070T is designed to work with low ESR ceramic capacitors. The effective value of these capacitors is defined as the actual capacitance under voltage bias and temperature. All ceramic capacitors have a large voltage coefficient, in addition to normal tolerances and temperature coefficients. Under D.C. bias, the capacitance value drops considerably. Larger case sizes or higher voltage capacitors are better in this regard. To help mitigate these effects, multiple small capacitors can be used in parallel to bring the minimum effective capacitance up to the desired value.

The input capacitance,  $C_{\text{IN}}$ , is needed to filter the trapezoidal current at the source of the top MOSFET. A low ESR input capacitor with larger ripple current rating should be used for the maximum RMS current. RMS current is given by:

$$I_{RMS} = I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} =$ I<sub>OUT</sub> / 2. This simple worst case condition is commonly used for design because even significant deviations do not offer much relief. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life, which makes it advisable to either further derate the capacitor or choose a capacitor rated at a higher temperature than required. Several capacitors may also be placed in parallel to meet size or height requirements in the design. The selection of C<sub>OUT</sub> is determined by the effective series resistance (ESR) that is required to minimize voltage ripple, load step transients, and the amount of bulk capacitance that is necessary to ensure that the control loop is stable. Loop stability can be examined by viewing the load transient response as described in a later section. The output ripple,  $\Delta V_{OUT}$ , is determined by:

$$\Delta V_{OUT} \le \Delta I_L \left[ ESR + \frac{1}{8fC_{OUT}} \right]$$

The output ripple is highest at maximum input voltage since DIL increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR but have lower capacitance density than other types. Tantalum capacitors have the highest capacitance density but it is important to only use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR but can be used in cost-sensitive applications provided that consideration is given to ripple current ratings and long-term reliability. Ceramic capacitors have excellent low ESR characteristics but can have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can also lead to significant ringing.

Suggestion ESR Range of output capacitor

| Application          | C <sub>OUT</sub> ESR Range |

|----------------------|----------------------------|

| CH1 C <sub>OUT</sub> | 5 to 15mΩ                  |

| CH2 C <sub>OUT</sub> | 5 to 15mΩ                  |

| CH3 C <sub>OUT</sub> | 5 to 15mΩ                  |

| CH4 C <sub>OUT</sub> | 5 to 10mΩ                  |

#### **Using Ceramic Input and Output Capacitors**

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. However, care must be taken when these capacitors are used at the input and output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input, V<sub>IN</sub>. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at VIN large enough to damage the part. Table 1 shows the nominal values of input/output capacitance recommenced for the RT2070T.

#### **Inductor Selection**

For a given input and output voltage, the inductor value and operating frequency determine the ripple current. The ripple current  $\Delta I_L$  increases with higher VIN and decreases with higher inductance :

$$\Delta I_{L} = \left[\frac{V_{OUT}}{f_{OSC} \times L}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN}}\right]$$

Having a lower ripple current reduces the ESR losses in the output capacitors and the output voltage ripple. Highest efficiency operation is achieved at low frequency with small ripple current. This, however, requires a large inductor. A reasonable starting point for selecting the ripple current is  $\Delta I_L = 0.4$  (I<sub>MAX</sub>). The largest ripple current occurs at the

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

highest V<sub>IN</sub>. To guarantee that the ripple current stays below a specified maximum, the inductor value should be chosen according to the following equation:

$$L = \left[\frac{V_{OUT}}{f_{OSC} \times \Delta I_{L(MAX)}}\right] \times \left[1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right]$$

#### **Inductor Core Selection**

Once the value for L is known, the type of inductor must be selected. High efficiency converters generally cannot afford the core loss found in low cost powdered iron cores, forcing the use of more expensive ferrite or permalloy cores. Actual core loss is independent of core size for a fixed inductor value but it is very dependent on the inductance selected. As the inductance increases, core losses decrease. However, increased inductance requires more turns of wire and therefore copper losses will increase.

Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation.

Ferrite core material saturates "hard", which means that inductance collapses abruptly when the peak design current is exceeded.

This results in an abrupt increase in inductor ripple current and consequent output voltage ripple.

Do not allow the core to saturate!

Different core materials and shapes will change the size/ current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate energy but generally cost more than powdered iron core inductors with similar characteristics. The choice of which style inductor to use mainly depend on the price vs. size requirements and any radiated field/EMI requirements.

#### **Power On/Off Control**

The register value will be recovered to default value as VIN plug in. In normal operation, users can set the power on/ off relative setting by I<sup>2</sup>C for next ENA power on. The RT2070T support 6 sets power on/off sequence selected by the SEQ pin. The sequence detection operation only work as VIN plug in. The RT2070T includes 6 sets power on/off sequence and the default value is decided by factory trim.

In the RT2070T, users can plan the next power on/off sequence by setting register A01/A02. The register value means the power on location, and "000" means this channel is power off. The RT2070T doesn't allow missing power on code or discrete code occurs.

| SEQ0 to SEQ5 |                        |                                              |                                                |  |  |  |

|--------------|------------------------|----------------------------------------------|------------------------------------------------|--|--|--|

|              | Output Voltage Setting | Soft-Start End Delay Time<br>(A01.Bit [7:6]) | Discharge Finish Delay Time<br>(A02.Bit [7:6]) |  |  |  |

| LSW          | SEQX_LSW [2:0]         |                                              |                                                |  |  |  |

| LSVV         | [001]                  |                                              |                                                |  |  |  |

| Duals?       | SEQX_Buk2 [2:0]        |                                              |                                                |  |  |  |

| Buck2        | [010]                  | [00]                                         | [00]                                           |  |  |  |

| Duals?       | SEQX_Buk3 [2:0]        | [00]                                         | [00]                                           |  |  |  |

| Buck3        | [011]                  |                                              |                                                |  |  |  |

| 1.004        | SEQX_LDO [2:0]         |                                              |                                                |  |  |  |

| LDO4         | [100]                  |                                              |                                                |  |  |  |

#### Note:

The default value will be decided in factory trim.

Define:

[000] means channel always turn off.

[001] means firstly turn on channel.

----

[100] means the finally turn on channel.

#### Example:

In above setting, the power on sequence is as below:

LSW (001)  $\rightarrow$  Buck2 (010)  $\rightarrow$  Buck3 (011)  $\rightarrow$  LDO4 (100).

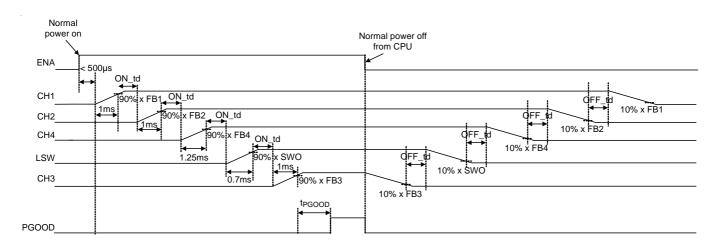

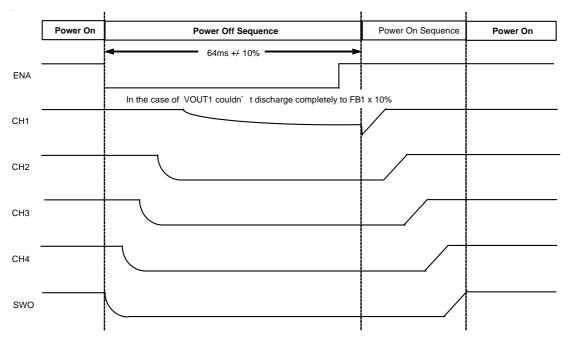

#### **Normally Power ON/OFF Sequence**

In the RT2070T, the power on sequence of the channels are decided by SEQ setting. The off sequence will follow first-on-last-off rule to turn off channels.

**Note**: ON\_td and OFF\_td time control by Register ON\_td <1:0> and OFF\_td <1:0>, default setting <00> = 0ms, and  $t_{PGOOD} = 5ms$ .

Figure 1. Sequence Example : CH1  $\rightarrow$  CH2  $\rightarrow$  CH4  $\rightarrow$  LSW  $\rightarrow$  CH3

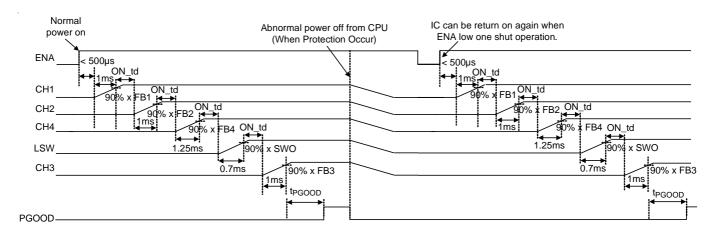

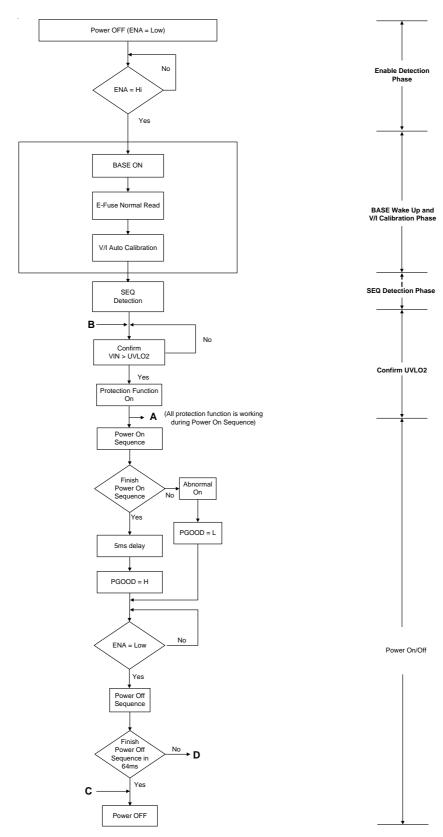

#### **Abnormal Off**

When the abnormal event occurs, all channels turns off immediately.

If users want to turn on again, users must pull ENA low to reset state then pull high to turn on again.

Note: ON\_td and OFF\_td time control by Register ON\_td <1:0> and OFF\_td <1:0> , default setting <00> = 0ms, and  $t_{PGOOD} = 5ms.$

Figure 2. Protection Example: Each Channel Shutdown at the Same Time

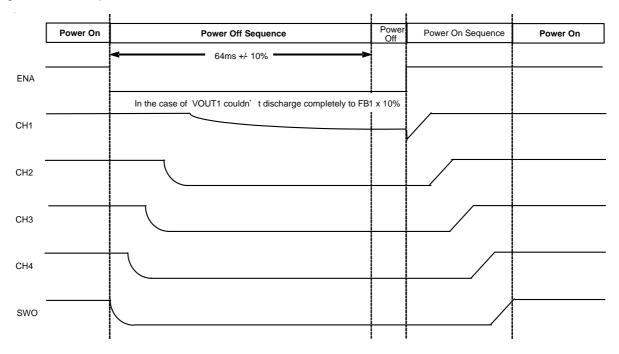

When output channel take time to discharge over 64ms and ENA keep low level, all channels turn off at 64ms after starting Power Off Sequence.

Figure 3. Sequence Example : Power ON (CH1 $\rightarrow$  CH2 $\rightarrow$  CH3 $\rightarrow$  CH4 $\rightarrow$  LSW), Power OFF (LSW  $\rightarrow$  CH4 $\rightarrow$  CH3  $\rightarrow$  CH2 $\rightarrow$  CH1)

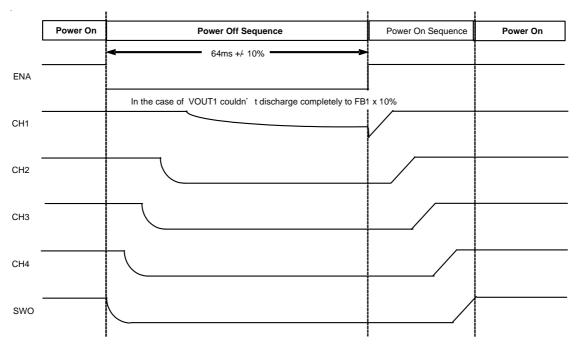

When output channel take time to discharge over 64ms and ENA goes high level at 64ms after starting Power Off Sequence, the RT2070T re-start immediately.

Figure 4. Sequence Example : Power ON (CH1→ CH2→ CH3→ CH4→ LSW), Power OFF (LSW → CH4 → CH3  $\rightarrow$  CH2  $\rightarrow$  CH1)

When output channel take time to discharge over 64ms and ENA keep high level at 64ms after starting Power Off Sequence, the RT2070T re-start immediately.

Figure 5. Sequence Example : Power ON (CH1 $\rightarrow$  CH2 $\rightarrow$  CH3 $\rightarrow$  CH4 $\rightarrow$  LSW), Power OFF (LSW  $\rightarrow$  CH4 $\rightarrow$  CH3  $\rightarrow$  CH2 $\rightarrow$  CH1)

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

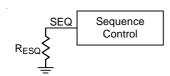

#### PMU On/Off Sequence Setting by SEQ

The SEQ pull-down resistance is used to define power on/off sequence (SEQ1 to SEQ5).

The RT2070T will do sequence detection as VIN plug in. Enable sequence will be executed when detection phase finish. If users don't change the sequence setting by I<sup>2</sup>C in register A01 to A12, the IC will follow default value to turn on IC set by factory trim. If there is any CHx is not used that external components still must be existed and keep original application circuit.

| SEQ  | RSEQ Range                                                        | Typical R <sub>SEQ</sub> |

|------|-------------------------------------------------------------------|--------------------------|

| SEQ0 | Short to VDDA                                                     |                          |

| SEQ1 | $64k\Omega > R_{SEQ} > 30k\Omega$                                 | 47kΩ                     |

| SEQ2 | $16k\Omega > R_{SEQ} > 6.8k\Omega$                                | 10kΩ                     |

| SEQ3 | $3.9 \text{k}\Omega > \text{R}_{\text{SEQ}} > 1.6 \text{k}\Omega$ | 2.4kΩ                    |

| SEQ4 | Short to GND                                                      |                          |

| SEQ5 | $200\text{k}\Omega > \text{RseQ} > 110\text{k}\Omega$             | 160kΩ                    |

Users can plan the combination of six sequences (SEQ0 to SEQ5).

| SEQ0 | CH1 | CH2 | LSW | СНЗ | CH4 |

|------|-----|-----|-----|-----|-----|

| SEQ1 | CH1 | LSW | CH4 | СНЗ | CH2 |

| SEQ2 | CH1 | CH4 | CH3 | CH2 | LSW |

| SEQ3 | CH1 | CH2 | CH3 | LSW | CH4 |

| SEQ4 | CH2 | CH1 | CH3 | CH4 | LSW |

| SEQ5 | CH1 | LSW | CH2 | CH4 | СНЗ |

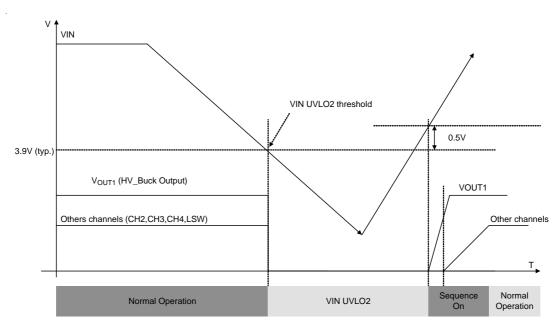

#### **VIN UVLO2 Operation**

If VIN is smaller than 3.9V, all channels will be turned off after 32µs.

Next, V<sub>IN</sub> is larger than 4.4V, the system will be sequence turn on by setting.

#### Max Load of Every Channel

| Purpose           | RT2070T     | Peak Current Limit | Max Loading (I <sub>OUT</sub> )* | Condition ( $V_{IN} \rightarrow V_{OUT}$ ) |

|-------------------|-------------|--------------------|----------------------------------|--------------------------------------------|

| HV to LV          | CH1_HV Buck | 3000mA             | 2000mA                           | $5V \rightarrow 3.3V$                      |

| V <sub>I</sub> /O | CH2_LV Buck | 1300mA             | 900mA                            | $3.3V \rightarrow 1.8V$                    |

| Vcore             | CH3_LV Buck | 1300mA             | 1000mA                           | $3.3V \rightarrow 1.2V$                    |

| VSENSOR           | CH4_LDO     | 750mA              | 500mA                            | $3.3\text{V} \rightarrow 2.7\text{V}$      |

| Load SW           | LSW         | 750mA              | 500mA                            | $3.3 \text{V} \rightarrow 3.3 \text{V}$    |

<sup>\*</sup> Buck converter V<sub>IN</sub>/V<sub>OUT</sub> levels will affect the max loading

Higher max loading current

Higher step-down ratio (V<sub>IN</sub>/V<sub>OUT</sub>) results in shorter switch on-time (t<sub>ON</sub>), hence lower peak switch current.

Lower max loading current

Lower step down ratio (V<sub>IN</sub> closer to V<sub>OUT</sub>) results a lower differential inductor voltage, so the slope of the inductor current during the ramp-up period is reduced.

Note: 0.5V is hysteresis voltage.

Figure 6. UVLO2 Diagram

#### **Protection Act**

|                   | UVLO2  |

|-------------------|--------|

| Protection Action | Hiccup |

| Vth_R(V)          | 4.4    |

| Vth_F(V)          | 3.9    |

| Power On Confirm  | YES    |

| Detect Power Pin  | VIN    |

\*Hiccup: Recover automatically.

#### Flow Chart

#### **Power ON/OFF Operation**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

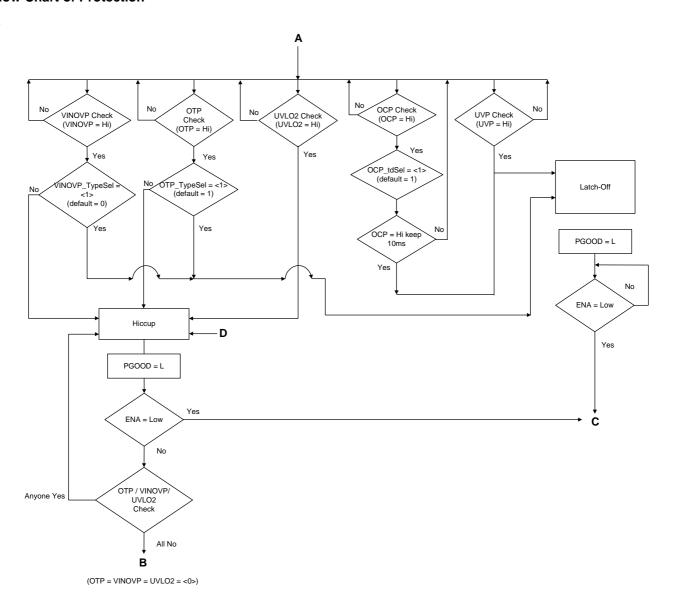

#### Flow Chart of Protection

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

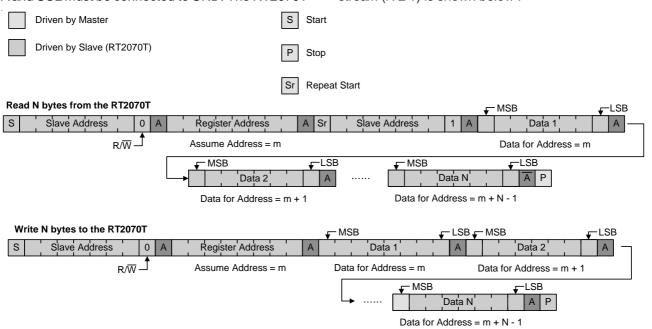

## I<sup>2</sup>C Interface

The RT2070T I<sup>2</sup>C interface bus power must be supplied by VDDA or equal potential node. If I<sup>2</sup>C interface isn't used, SDA and SCL must be connected to GND. The RT2070T

$I^2C$  slave address = 0110100 (7bits).  $I^2C$  interface supports fast mode (bit rate up to 400kb/s). The write or read bit stream (N  $\geq$  1) is shown below:

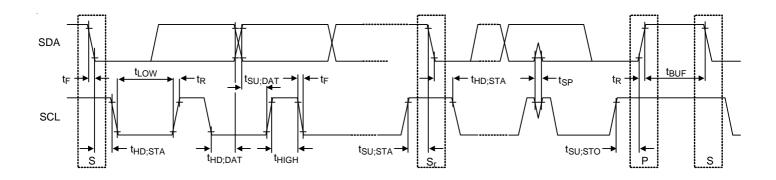

| Parameter                                                                                   | Symbol              | Test Conditions           | Min | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------|---------------------|---------------------------|-----|-----|------|------|

| I <sup>2</sup> C Interface Electrical Charac                                                | teristics           |                           |     |     |      |      |

| Pull Up Voltage Range                                                                       |                     |                           | 1.8 |     | VDDA | V    |

| SCLK Clock Rate                                                                             | f <sub>SCL</sub>    |                           |     |     | 400  | kHz  |

| Hold Time (Repeated) START Condition. After this period, the first clock pulse is generated | t <sub>HD;STA</sub> |                           | 0.6 |     |      | μs   |

| LOW Period of the SCL Clock                                                                 | tLOW                |                           | 1.3 |     |      | μs   |

| HIGH Period of the SCL Clock                                                                | thigh               |                           | 0.6 |     |      | μs   |

| Set-Up Time for a Repeated START Condition                                                  | tsu;sta             |                           | 0.6 |     |      | μs   |

| Data Hold Time                                                                              | t <sub>HD;DAT</sub> |                           | 0   |     | 0.9  | μs   |

| Data Set-Up Time                                                                            | t <sub>SU;DAT</sub> |                           | 100 |     |      | ns   |

| Set-Up Time for STOP<br>Condition                                                           | tsu;sto             |                           | 0.6 |     |      | μs   |

| Bus Free Time Between a STOP and START Condition                                            | t <sub>BUF</sub>    |                           | 1.3 |     |      | μs   |

| Rise Time of Both SDA and SCL Signals                                                       | t <sub>R</sub>      |                           | 20  |     | 300  | ns   |

| Fall Time of Both SDA and SCL Signals                                                       | tF                  |                           | 20  |     | 300  | ns   |

| SDA and SCL Output Low Sink Current                                                         | I <sub>OL</sub>     | SDA or SCL voltage = 0.4V | 2   |     |      | mA   |

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

#### I<sup>2</sup>C Waveform Information

## I<sup>2</sup>C Register Table

| Address<br>Name | Register<br>Address                                                                       | Description | Bit7                   | Bit6                                                    | Bit5                 | Bit4          | Bit3            | Bit2            | Bit1     | Bit0     |  |  |

|-----------------|-------------------------------------------------------------------------------------------|-------------|------------------------|---------------------------------------------------------|----------------------|---------------|-----------------|-----------------|----------|----------|--|--|

|                 |                                                                                           | Function    |                        | Buck Function Trim                                      |                      |               |                 |                 |          |          |  |  |

| A00             | 0x00                                                                                      | Meaning     | Reserved               | FPWM3                                                   | FPWM2                | EnDis_<br>LDO | EnDis_<br>buck3 | EnDis_<br>buck2 | Reserved | Reserved |  |  |

|                 |                                                                                           | Default     | 0                      | 1                                                       | 1                    | 1             | 1               | 1               | 0        | 0        |  |  |

|                 |                                                                                           | Read/Write  | R/W                    | R/W                                                     | R/W                  | R/W           | R/W             | R/W             | R/W      | R/W      |  |  |

|                 |                                                                                           |             | Define the             | e Buck3 s                                               | witching o           | peration m    | ode             |                 |          |          |  |  |

|                 | FPWM                                                                                      | 3           | 0 : Autom<br>1 : Force |                                                         | /PSM swit            | ching ope     | ration          |                 |          |          |  |  |

|                 |                                                                                           |             | Define the             | Define the Buck2 switching operation mode               |                      |               |                 |                 |          |          |  |  |

|                 | FPWM:                                                                                     | 2           |                        | 0 : Automatic PWM/PSM switching operation 1 : Force PWM |                      |               |                 |                 |          |          |  |  |

|                 |                                                                                           |             | LDO pow                | er off disc                                             | harge ena            | ble contro    | I               |                 |          |          |  |  |

|                 | EnDis_L[                                                                                  | 00          |                        | _                                                       | when LDO<br>LDO pow  | •             | ff              |                 |          |          |  |  |

|                 |                                                                                           |             | Buck3 po               | wer off dis                                             | scharge en           | able conti    | rol             |                 |          |          |  |  |

|                 | EnDis_buck3  0 : Won't discharge when Buck3 power off  1 : Discharge when Buck3 power off |             |                        |                                                         |                      |               |                 |                 |          |          |  |  |

|                 | Buck2 power off discharge enable control                                                  |             |                        |                                                         |                      |               |                 |                 |          |          |  |  |

|                 | EnDis_bu                                                                                  | ck2         |                        |                                                         | when Buc<br>Buck2 po |               | off             |                 |          |          |  |  |

Copyright © 2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Address<br>Name | Register<br>Address | Description | Bit7                                                                                                           | Bit6                                                                  | Bit5                     | Bit4          | Bit3       | Bit2       | Bit1       | Bit0 |  |

|-----------------|---------------------|-------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------|---------------|------------|------------|------------|------|--|

|                 |                     | Function    |                                                                                                                |                                                                       |                          | SEQ           | ) Trim     |            |            |      |  |

| A 0.4           | 0.404               | Meaning     | ON_td                                                                                                          | <1:0>                                                                 | SEC                      | 0_Buk2 <      | 2:0>       | SEC        | Q0_LSW <   | 2:0> |  |

| A01             | 0x01                | Default     | 0                                                                                                              | 0                                                                     | 0                        | 0             | 1          | 0          | 1          | 0    |  |

|                 |                     | Read/Write  | R/W                                                                                                            | R/W                                                                   | R/W                      | R/W           | R/W        | R/W        | R/W        | R/W  |  |

|                 |                     |             | Define th                                                                                                      | e interval b                                                          | etween so                | oft-start fin | sh and the | e next cha | nnel enabl | ed   |  |

|                 | ON_td <1            | :0>         | 11 : 2ms<br>10 : 1ms<br>01 : 0.5ms<br>00 : 0ms                                                                 |                                                                       |                          |               |            |            |            |      |  |

|                 |                     |             | Define Buck2 power on sequence in SEQ0 (Note : every channel can't choose the same code except <000> in SEQ0 ) |                                                                       |                          |               |            |            |            |      |  |

| SE              | Q0_Buck2            | 2 <2:0>     | 011 : the 010 : the                                                                                            | last turn of<br>third turn of<br>second turn<br>first turn of<br>able | on<br>rn on              |               |            |            |            |      |  |

|                 |                     |             |                                                                                                                | •                                                                     | on sequen<br>el can't ch |               |            | except <0  | 000> in SE | Q0)  |  |

| SE              | EQ0_LSW             | <2:0>       | 011 : the<br>010 : the                                                                                         | last turn of<br>third turn of<br>second turn<br>first turn of<br>able | on<br>rn on              |               |            |            |            |      |  |

| Address<br>Name | Register<br>Address | Description | Bit7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit6                                                              | Bit5      | Bit4       | Bit3      | Bit2       | Bit1        | Bit0 |

|-----------------|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------|------------|-----------|------------|-------------|------|

|                 |                     | Function    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                   |           | SEQ0       | Trim      | •          | •           |      |

| 400             | 0,400               | Meaning     | OFF_to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | d <1:0>                                                           | SEC       | Q0_LDO <   | 2:0>      | SEC        | Q0_Buk3 <   | 2:0> |