# **RT2571W**

#### Data sheet

Revision June 22, 2007

# **Applications**

IEEE802.11a/b/g Wireless Local Area Networks

Wireless Portable Device/Notebook Computer

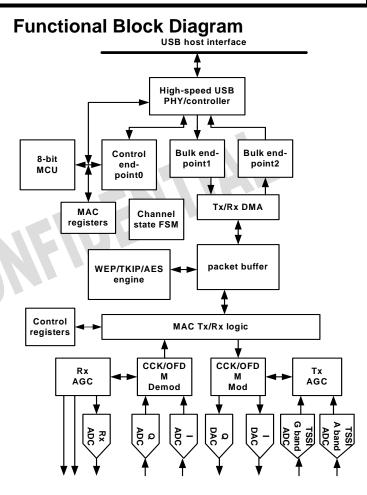

The RT2571W is a highly integrated MAC/baseband processor to support IEEE 802.11a/b/g USB wireless LAN Standards. The processor is part of Ralink chip set RT2501USB for the baseband part, it supports the Direct Sequence Spread Spectrum (DSSS) for 2.4GHz band and Orthogonal Frequency Division Multiplexing (OFDM) for 2.4GHz and 5GHz bands. Using advanced digital signal processing technologies, the optimal reception performance under severe multi-path environments is achieved.

For the MAC part, it provides all the required functions and many optional features in the IEEE standards, such as 802.11e (QOS), 802.11h (TPC/DFS), 802.11i (Security). It has many on-chip acceleration engines to ensure that the highest MAC performance is achieved without overloading host processing power.

Using advanced algorithms and design methodologies, the chip is best-in-class in terms of throughput, power consumption, range and multipath tolerance.

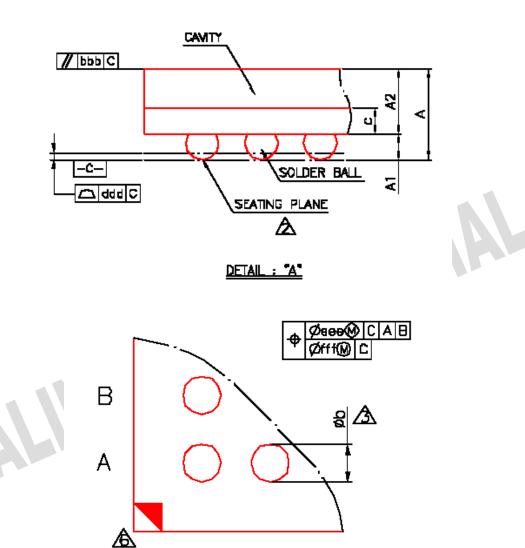

The RT2571W housed in a 180-pin  $12^{\star}12\text{mm}^2$  TFBGA package is well suited for embedded applications. External Interfaces include USB 1.1/ USB 2.0.

#### Features

- Host interface: USB1.1 / USB 2.0

- Full Implementation of the MAC Protocol specified in IEEE Standards 802.11-1999 and 802.11g and 802.11g-2003

- Supported Operating System: Windows XP, Windows2000, Windows ME, 98SE, Linux

- Security: 64/128 WEP, WPA, AES

- Advanced Power Saving Algorithm for Dynamic Network Traffic Environment

- On-Chip A/D and D/A Converters for I/Q

- Data, TSSI and AGCs

- Supports Short Preamble

- Proprietary Robust Demodulator with Patent Protection

- Mitigates Multipath Delay Spread up to 100ns at 54Mbps

- R G PIOs interface for W/A

- 8 GPIOs interface for WAN extension.

2 configurable LEDs to release CPU from

- LED routine loading

- Support NOR-type flash interface

- Support 6, 9, 12, 18, 24, 36, 48, 54

- Mbps for OFDM; 5.5, 11Mbps for CCK; and 1.2 Mbps for Barker modulation.

# **Order Information**

| Part Number | Temp Range  | Package              |

|-------------|-------------|----------------------|

| RT2571WF    | -10 to 85°C | Lead-free 180B TFBGA |

Ralink Technology, Corp. (Taiwan)

Tel:

886-3-567-8868

4<sup>th</sup> Fl. No. 2, Technology 5<sup>th</sup> Rd. SBIP Fax:

886-3-567-8818

Hsin-Chu, Taiwan, R.O.C.

Ralink Technology, Corp. (USA)

Tel:

(408) 725-8070

20833 Stevens Creek Blvd. Ste 200

Fax:(408)725-8069

Fax:(408)725-8069

Cupertino, CA95014

http://www.ralinktech.com

Revision June 22, 2007

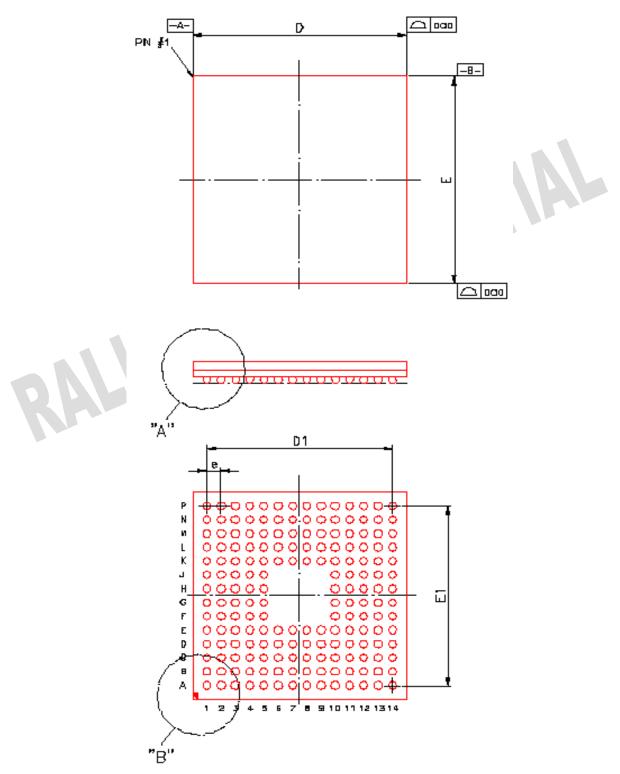

# Pin Out TFBGA180

|   | 1              | 2              | 3              | 4              | 5              | 6            | 7           | 8           | 9             | 10          | 11          | 12            | 13           | 14           |

|---|----------------|----------------|----------------|----------------|----------------|--------------|-------------|-------------|---------------|-------------|-------------|---------------|--------------|--------------|

| Α | DP             | DM             | ADDR12         | ADDR11         | ADDR10         | ADDR9        | ADDR6       | ADDR0       | DATA4         | DATA1       | NC          | IREQN         | PLLCLK       | NC           |

| В | NC             | RREF           | ADDR13         | ADDR14         | XSCO           | SUSPE<br>NDM | ADDR7       | ADDR3       | DATA6         | PCMRE<br>GN | WAITN       | NC            | NC           | GPIO7        |

| С | NC             | GND3_<br>U20   | VCC3_U<br>20   | XSCI           | ADDR8          | ADDR15       | ADDR5       | ADDR2       | DATA5         | DATA0       | NC          | BYPASS<br>PLL | NC           | GPIO6        |

| D | VCC3IO_U<br>20 | RPU            | GND18_<br>U20  | VCC18_<br>U20  | NC             | ADDR4        | ADDR1       | DATA7       | DATA2         | DATA3       | NC          | R/B           | PLLVDD<br>A  | GPIO5        |

| Ε | TEST_EN        | GNDA_<br>U20   | NC             | GRSTN          | GND            | VDD_C1<br>8  | GND         | VDDIO       | GND           | GND         | VDD_C1<br>8 | NC            | CEN          | GPIO4        |

| F | SCAN_EN        | UDCLK<br>SEL   | PLL_MO<br>DE   | VCCA_<br>U20   | GND            |              |             |             |               | GND         | VDDIO       | WPN           | NC           | GPIO3        |

| G | NC             | NC             | NC             | UDCLK          | VDDIO          |              |             | -1          |               | GND         | VDDIO       | GPIO1         | GPIO2        | RF_SD        |

| н | NC             | EECS           | EECLK          | VDD_C1<br>8    | GND            |              |             | 5           |               | GND         | VDD_C1<br>8 | RF_LE         | GPIO0        | RF_SCL<br>K  |

| J | NC             | EEDI           | LED_AC<br>T    | ANSEL_<br>P    | GND            |              |             |             |               | VSS33D      | VSS33D      | GNDSH         | NC           | NC           |

| κ | NC             | ANSEL_<br>N    | TR_SW<br>_P    | VDDIO          | GND            | GND          | VSS18       | VSS18       | VSS18         | VSS33A      | VSS33D      | VREF          | VREF02<br>5N | VREF02<br>5P |

| L | NC             | TR_SW<br>_N    | TR_PE          | PA_PE_<br>G    | VDD_C1<br>8    | VDDIO        | IREF        | VCC18       | VCC18         | VSS33A      | VSS33A      | VCC33D        | VCC33D       | VCC33A       |

| М | NC             | EEDO           | LED_RD<br>Y    | NC             | AGC_LN<br>A1   | VDDIO        | AGC         | VCC18       | GNDSH<br>_DAC | VSS33A      | VCC33A      | VCC33A        | VSS33A       | VCC33D       |

| Ν | RADIO_PE       | PA_PE_<br>A    | VGA_P<br>ULSE  | AGC_LN<br>A0   | VGA_VA<br>LUE1 | NC           | RFTXI_<br>P | RFTXI_<br>N | NC            | TSSI_A      | VCC33A      | VCC33A        | VREFN        | RFRXQ_<br>N  |

| Ρ | RF_PE          | VGA_VA<br>LUE0 | VGA_VA<br>LUE2 | VGA_VA<br>LUE3 | VGA_VA<br>LUE4 | NC           | RFTXQ_<br>P | RFTXQ_<br>N | NC            | TSSI_G      | RFRXI_<br>P | RFRXI_<br>N   | VREFP        | RFRXQ_<br>P  |

(The remainder of this page is left blank intentionally)

Revision June 22, 2007

# **Pin Description**

\*Notation: I (Input)., O (Output), I/O (Bi-direction)

| Pin No                                 | Pin Name                                     | I/O type                   | Description                                                                                                                                          |

|----------------------------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | • • • • • • • • • • • • • • • • • • •        | Global s                   | ignals (9)                                                                                                                                           |

| E4                                     | GRSTN                                        | l, pull-up                 | Global reset, active low.                                                                                                                            |

| E1                                     | TEST_EN                                      | I, pull-down               | Scan test mode enable. Connect to GND                                                                                                                |

|                                        |                                              |                            | 0: Normal mode.                                                                                                                                      |

|                                        |                                              |                            | 1: Test mode.                                                                                                                                        |

| F1                                     | SCAN_EN                                      | I, pull-down               | Scan enable. Connect to GND                                                                                                                          |

|                                        |                                              |                            | 0: Normal mode.                                                                                                                                      |

|                                        |                                              |                            | 1: Scan mode.                                                                                                                                        |

| G4                                     | UDCLK                                        | 0                          | 12MHz clock generated by internal PLL.                                                                                                               |

| F3                                     | PLL_MODE                                     | I                          | Internal PLL mode.                                                                                                                                   |

|                                        |                                              |                            | 0: PLL can be set to power-down by MAC.                                                                                                              |

|                                        |                                              |                            | 1: PLL is always active.                                                                                                                             |

|                                        |                                              |                            | Connect to VCC if use only one crystal.                                                                                                              |

| F2                                     | UDCLKSEL                                     | I, pull-down               | Connect to GND.                                                                                                                                      |

| A13                                    | PLLCLK                                       | I                          | Base-band 40MHz clock input.                                                                                                                         |

| C12                                    | BYPASSPLL                                    | I, pull-down               | Bypass internal base-band PLL. Connect to GND.                                                                                                       |

| B6                                     | SUSPENDM                                     | 0                          | Suspend for USB mode.                                                                                                                                |

|                                        |                                              |                            | 0: USB device is in power down mode                                                                                                                  |

|                                        |                                              |                            | 1: USB device is in normal mode                                                                                                                      |

|                                        |                                              |                            | face (37)                                                                                                                                            |

| J4                                     | ANSEL_P                                      | 0                          | Antenna select positive output.                                                                                                                      |

| K2                                     | ANSEL_N                                      | 0                          | Antenna select negative output.                                                                                                                      |

| M5, N4                                 | AGC_LNA[1:0]                                 | 0                          | AGC LNA control signals.                                                                                                                             |

| N3                                     | VGA_PULSE                                    | 0                          | VGA pulse for zero-IF RF.                                                                                                                            |

| P5,P4,P3,N5,P2                         | VGA_VALUE[4:0]                               | 0                          | VGA value output for zero-IF RF.                                                                                                                     |

| N1                                     | RADIO_PE                                     | 0                          | RADIO_PE control to RF system.                                                                                                                       |

| H12                                    | RF_LE                                        | 0                          | RF latch enable of serial control interface.                                                                                                         |

| K3                                     | TR_SW_P                                      | 0                          | TR_SW positive output.                                                                                                                               |

| L2                                     | TR_SW_N                                      | 0                          | TR_SW negative output.                                                                                                                               |

| H14                                    | RF_SCLK                                      | 0                          | RF serial interface clock.                                                                                                                           |

| G14                                    | RF_SD                                        | 0                          | RF serial interface data.                                                                                                                            |

| P1                                     | RF_PE                                        | 0                          | RF_PE output.                                                                                                                                        |

| L3                                     | TR_PE                                        | 0                          | TR_PE output to RF system.                                                                                                                           |

| L4                                     | PA_PE_G                                      | 0                          | Transmit PA Power enable to PA (Power Amplifier) of 2.4G RF.                                                                                         |

| N2                                     | PA_PE_A                                      | 0                          | Transmit PA Power enable to PA (Power Amplifier) of 5.2G RF.                                                                                         |

| M7                                     | AGC                                          | 0                          | Adaptive gain control to TX/RX side of RFIC.                                                                                                         |

| L7                                     | IREF                                         |                            | Reference current.                                                                                                                                   |

| N7                                     | RFTXI_P                                      | 0                          | Differential I+ output, from base-band DAC to RFIC.                                                                                                  |

| N8                                     | RFTXI_N                                      | 0                          | Differential I- output, from base-band DAC to RFIC.                                                                                                  |

| P7                                     | RFTXQ_P                                      | 0                          | Differential Q+ output, from base-band DAC to RFIC.                                                                                                  |

| P8                                     | RFTXQ_N                                      | 0                          | Differential Q- output, from base-band DAC to RFIC.                                                                                                  |

| P10                                    | TSSI_G                                       | li li                      | Transmitted signal strength indicator. From 2.5G RF PA.                                                                                              |

| N10                                    | TSSI_A                                       | 1                          | Transmitted signal strength indicator. From 5.2G RF PA.                                                                                              |

| P11                                    | RFRXI_P                                      | 1                          | Differential I+ input, from RFIC to base-band ADC.                                                                                                   |

| 1 1 1                                  | RFRXI_N                                      |                            | Differential I- input, from RFIC to base-band ADC.                                                                                                   |

|                                        |                                              | 1.                         | Reference voltage.                                                                                                                                   |

| P12                                    |                                              | Analog                     |                                                                                                                                                      |

| P12<br>P13                             | VREFP                                        | Analog<br>Analog           |                                                                                                                                                      |

| P12<br>P13<br>N13                      | VREFP<br>VREFN                               | Analog<br>Analog           | Reference voltage.                                                                                                                                   |

| P12<br>P13<br>N13<br>P14               | VREFP<br>VREFN<br>RFRXQ_P                    |                            | Reference voltage.<br>Differential Q+ input, from RFIC to base-band ADC.                                                                             |

| P12<br>P13<br>N13<br>P14<br>N14        | VREFP<br>VREFN<br>RFRXQ_P<br>RFRXQ_N         | Analog<br>I<br>I           | Reference voltage.<br>Differential Q+ input, from RFIC to base-band ADC.<br>Differential Q- input, from RFIC to base-band ADC.                       |

| P12<br>P13<br>N13<br>P14<br>N14<br>K12 | VREFP<br>VREFN<br>RFRXQ_P<br>RFRXQ_N<br>VREF | Analog<br>I<br>I<br>Analog | Reference voltage.<br>Differential Q+ input, from RFIC to base-band ADC.<br>Differential Q- input, from RFIC to base-band ADC.<br>Reference voltage. |

| P12<br>P13<br>N13<br>P14<br>N14        | VREFP<br>VREFN<br>RFRXQ_P<br>RFRXQ_N         | Analog<br>I<br>I           | Reference voltage.<br>Differential Q+ input, from RFIC to base-band ADC.<br>Differential Q- input, from RFIC to base-band ADC.                       |

Revision June 22, 2007

|                                                       | GPIO[7:0]  | I/O         | GPIO[7:0].                                                           |

|-------------------------------------------------------|------------|-------------|----------------------------------------------------------------------|

| F14,G13,G12,H13                                       | 5500       | 0           |                                                                      |

| H2                                                    | EECS       | 0           | EEPROM chip select.                                                  |

| H3                                                    | EECLK      | 0           | EEPROM clock.                                                        |

| J2                                                    | EEDI       | 0           | EEPROM data in.                                                      |

| M2                                                    | EEDO       | 1           | EEPROM data output.                                                  |

| J3                                                    | LED_ACT    | 0           | Activity LED. Active low.                                            |

| M3                                                    | LED_RDY    | 0           | Ready LED. Controlled by software.                                   |

| D13                                                   | PLLVDDA    | Analog      | Base-band PLL 1.8V analog power.                                     |

|                                                       |            | USB PI      |                                                                      |

| A1                                                    | DP         | I/O         | USB data in data positive pin terminal.                              |

| A2                                                    | DM         | I/O         | USB data in data negative pin terminal.                              |

| B2                                                    | RREF       | Analog      | Connect to external reference resistor (6.195k $\Omega\pm$ 5%) to    |

|                                                       |            | -           | analog ground.                                                       |

| D2                                                    | RPU        | Analog      | Connect to external resistor (1.5k $\Omega \pm 1\%$ ) to analog 3.3V |

|                                                       |            | s a ser e g | power.                                                               |

| C4                                                    | XSCI       | 1           | Crystal oscillator input (12MHz)                                     |

| 04<br>B5                                              | XSCO       | 0           | Crystal oscillator output (12MHz)                                    |

| D3                                                    | VCC3IO_U20 | Power       | Analog power pin. Connect to 3.3V power.                             |

| E2                                                    | GNDA_U20   | Power       | Ground pin.                                                          |

| E2<br>F4                                              | VCCA_U20   | Power       |                                                                      |

| F4<br>D4                                              |            | Power       | Analog power pin. Connect to 3.3V power                              |

|                                                       |            |             | Digital power pin. Connect to 1.8V power.                            |

| D3                                                    | GND18_U20  | Power       | Ground pin.                                                          |

| <u>C3</u>                                             | VCC3_U20   | Power       | Analog power pin. Connect to 3.3V power.                             |

| C2                                                    | GND3_U20   | Power       | Ground pin.                                                          |

|                                                       |            | Power/Gr    |                                                                      |

| M9                                                    | GNDSH_DAC  | Power       | Ground pin.                                                          |

| J12                                                   | GNDSH      | Power       | Ground pin.                                                          |

| M11, M12, N11,<br>N12, L14                            | VCC33A     | Power       | Analog power pins. Connect to 3.3V power.                            |

| K10, L10, L11, M13,<br>M10                            | VSS33A     | Power       | Ground pins.                                                         |

| L12, L13, M14                                         | VCC33D     | Power       | Digital power pins. Connect to 3.3V power.                           |

| J10, J11, K11                                         | VSS33D     | Power       | Ground pins.                                                         |

| L8, L9, M8                                            | VCC18      | Power       | Analog power pins. Connect to 1.8V power.                            |

| K7, K8, K9                                            | VSS18      | Power       | Ground pins.                                                         |

| E11, E6, H11, H4,                                     | VDD_C18    | Power       | Digital core power pins. Connect to 1.8V power.                      |

| L5                                                    | 100_010    |             |                                                                      |

| E8, F11, G11, G5,<br>K4, L6, M6                       | VDDIO      | Power       | Digital I/O power pins. Connect to 3.3V power.                       |

|                                                       | GND        | Power       | Ground pins.                                                         |

| K6, E5, E9, F10, F5,                                  |            | 1 0 1 0 1   |                                                                      |

| H10, J5, K5                                           |            |             |                                                                      |

|                                                       |            | Reserv      | ed (30)                                                              |

| C6,B4,B3,A3,A4,<br>A5,A6,C5,B7,A7,<br>C7,D6,B8,C8,D7, | ADDR[15:0] | 0           | NOR flash address. Left NC if no use.                                |

| A8<br>D8,B9,C9,A9,<br>D10,D9,A10,C10                  | DATA[7:0]  | I/O         | NOR flash data I/O.                                                  |

| B11                                                   | WAITN      | 0           | NOR flash OEN. Left NC if no use.                                    |

| A12                                                   | IREQN      | 0           | NOR flash WEN. Left NC if no use.                                    |

| B10                                                   | PCMREGN    | l.          | NOR flash mode selection.                                            |

| DIO                                                   |            | ľ           | 0: external NOR flash mode.                                          |

|                                                       |            |             | 1: internal ROM mode.                                                |

| D12                                                   | R/B        | 1           | Connect to VDD.                                                      |

|                                                       | CEN        | 0           |                                                                      |

| E13                                                   |            | -           | NOR flash CEN. Left NC if no use                                     |

| F12                                                   | WPN        | 0           | Left NC.                                                             |

(The remainder of this page is left blank intentionally)

Revision June 22, 2007

# **Electrical Specifications**

# **Absolute Maximum Ratings**

| Core Supply Voltage                                |

|----------------------------------------------------|

| I/O Supply Voltage                                 |

| Input, Output or I/O Voltage GND -0.3V to Vcc+0.3V |

# **Operating Conditions**

| Ambient Temperature Range          | -10 to 85°C     |

|------------------------------------|-----------------|

| Maximum Operation Case Temperature | . 95 <b>°</b> C |

| Core Supply Voltage                | 1.8V +/- 10%    |

| I/O Supply Voltage                 | 3.3V +/- 10%    |

# Thermal Information

Thermal Resistance *θ* JA (<sup>°</sup>C/W,Note) in free air for TFBGA (12x12mm) package.....51.4 <sup>°</sup>C/W Maximum Junction Temperature .....125<sup>°</sup>C Maximum Storage Temperature .....-40<sup>°</sup>C to 150<sup>°</sup>C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Note:

JA is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features.

# **DC Electrical Specifications**

| Parameter                   | Symbol              | Test Conditions                                                                  | MIN                 | TYP | MAX                 | Units |

|-----------------------------|---------------------|----------------------------------------------------------------------------------|---------------------|-----|---------------------|-------|

| 1.8 Power supply current    | I <sub>CC18PT</sub> | V <sub>DD</sub> = Max, transmit                                                  | -                   | 50  | -                   | mA    |

|                             | I <sub>CC18PR</sub> | V <sub>DD</sub> = Max, receive                                                   | -                   | 80  | -                   | mA    |

|                             | I <sub>CC18SB</sub> | V <sub>DD</sub> = Max, standby                                                   | -                   | 10  | -                   | μA    |

| 3.3V Power supply current   | I <sub>CC33PT</sub> | V <sub>DD</sub> = Max, transmit                                                  | -                   | 80  | -                   | mA    |

|                             | I <sub>CC33PR</sub> | $V_{DD}$ = Max, receive                                                          | -                   | 120 | -                   | mA    |

|                             | I <sub>CC33SB</sub> | V <sub>DD</sub> = Max, standby                                                   | -                   | 400 | -                   | μA    |

| Logical one input voltage   | V <sub>IH</sub>     |                                                                                  | $0.7 V_{DD}$        | -   | -                   | V     |

| Logical zero input voltage  | VIL                 |                                                                                  | -                   | -   | 0.3                 | V     |

| Logical one output voltage  | V <sub>OH</sub>     | $I_{OH} = -1mA$ , $V_{DD} = Min$                                                 | 0.9 V <sub>DD</sub> | -   | -                   | V     |

| Logical zero output voltage | V <sub>OL</sub>     | $I_{OL} = 2mA, V_{DD} = Min$                                                     | -                   | 0.1 | 0.1 V <sub>DD</sub> | V     |

| Input capacitance           | C <sub>IN</sub>     | CLKIN frequency 1MHz.<br>All measurements<br>referenced to GND. $T_A =$<br>25 °C | -                   | 5   | 10                  | pF    |

| Output capacitance          | C <sub>OUT</sub>    |                                                                                  | -                   | 5   | 10                  | pF    |

Revision June 22, 2007

# **AC Electrical Specifications**

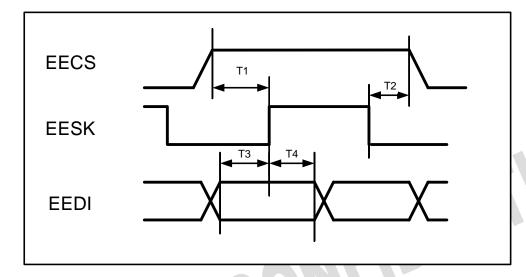

# **EEPROM Interface Timings**

|    |   | Symbol             | Parameter                            | Min | Max | Units | Notes |

|----|---|--------------------|--------------------------------------|-----|-----|-------|-------|

| T( | ) | <sup>t</sup> EESK  | Serial Clock Frequency               | 256 | 260 | KHz   |       |

| T1 | 1 | <sup>t</sup> EECSS | Delay from EECS High to<br>EESK High | 300 | -   | ns    |       |

| T2 | 2 | <sup>t</sup> EECSH | Delay from EESK Low to EECS Low      | 30  | -   | ns    |       |

| T3 | 3 | <sup>t</sup> EEDIS | Setup Time of EEDI to EESK           | 300 | -   | ns    |       |

| T∠ | 1 | <sup>t</sup> EEDIH | Hold Time of EEDI after<br>EESK      | 300 | -   | ns    |       |

Revision June 22, 2007

# **Register descriptions**

# **Register map**

|      | Function                        | Physical address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

|------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|      | USB registers                   | 0x0000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

|      | Control registers               | 0x0200H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Accessed by<br>firmware       |

|      | Packet buffer control registers | 0x0300H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

|      | WMM scheduler<br>registers      | 0x0400H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

|      | Reserved                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

| . 11 | MAC Key Table<br>(768x32)       | Ox1000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

|      | Reserved                        | 0x1BFFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

| RAL  | Shared memory<br>(512x32)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Accessed by<br>driver (vender |

|      | Reserved                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | command)                      |

|      | 32-bit MAC control registers    | 0x3000H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               |

|      | Reserved                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

|      | Packet Buffer<br>(4kx32)        | <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br>_ |                               |

# Security Key Table (Base Address = 0x1000)

# Security Key Entry Format (32 bytes per key entry)

| Offset | Field   | Туре | Description            |

|--------|---------|------|------------------------|

| 0x00   | Bit31:0 | R/W  | Security Key byte3~0   |

| 0x04   | Bit31:0 | R/W  | Security Key byte7~4   |

| 0x08   | Bit31:0 | R/W  | Security Key byte11~8  |

| 0x0C   | Bit31:0 | R/W  | Security Key byte15~12 |

| 0x10   | Bit31:0 | R/W  | TX MIC Key byte3~0     |

| 0x14   | Bit31:0 | R/W  | TX MIC Key byte7~4     |

| 0x18   | Bit31:0 | R/W  | RX MIC Key byte3~0     |

| 0x1C   | Bit31:0 | R/W  | RX MIC Key byte7~4     |

For WEP40, CKIP40: Security Key is valid at byte4~0. For WEP104, CKIP104: Security Key is valid at byte12~0 For TKIP, AES: Security Key is valid at byte15~0 TX/RX MIC Key is used only for TKIP MIC calculation.

### Pair-wised Transmitter Address Entry Format (8 bytes per key entry)

| Offset | Field   | Туре | Description                                                                                                                                                                                                  |

|--------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00   | Bit31:0 | R/W  | TA byte3~0                                                                                                                                                                                                   |

| 0x04   | Bit31:0 | R/W  | Bit [15:0] : TA byte5~4<br>Bit [18:16] : security mode for the pair<br>0=no security, 1=WEP40, 2=WEP104, 3=TKIP, 4=AES,<br>5=CKIP40<br>6=CKIP104, 7=reserved (no security for now)<br>Bit [31:19] : reserved |

# Security Key Table Layout (total 3072bytes)

The security key table is composed of: 16 shared key entries (32x16 bytes) 32 pair-wise key entries (32x64 bytes, for AP mode) 32 pair-wise transmitter address entries (8x64 bytes)

| Offset         | length         | Туре | Description                                                                                                                                                                                                                              |

|----------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x000<br>0x020 | 32bytes<br>x16 | R/W  | 16 shared key entries                                                                                                                                                                                                                    |

| 0x040          |                |      | According the multiple BSSID mask setting (MAC_CSR5)                                                                                                                                                                                     |

| 0x1e0          |                |      | CASE1. when BSSID mask = 2'b11 (one BSSID):<br>Key entries from 0x000 to 0x060 are treated as shared<br>keys for key id from 0 to 3.                                                                                                     |

|                |                |      | CASE2. when BSSID mask = 2'b01or 2'b10 (two BSSID):                                                                                                                                                                                      |

|                |                |      | Key entries from $0x000$ to $0x060$ are treat as shared<br>keys for key id from 0 to 3 if the masked BSSID bit = 0<br>Key entries from $0x080$ to $0x0e0$ are treat as shared<br>keys for key id from 0 to 3 if the masked BSSID bit = 1 |

| R              |                |      | CASE3. when BSSID mask = 2'b00 (four BSSID):<br>Key entries from 0x000 to 0x060 are treat as shared                                                                                                                                      |

|                |                |      | keys for key id from 0 to 3 if the masked BSSID bit = $00$<br>Key entries from 0x080 to 0x0e0 are treat as shared<br>keys for key id from 0 to 3 if the masked BSSID bit = $01$                                                          |

|                |                |      | Key entries from $0x100$ to $0x160$ are treat as shared<br>keys for key id from 0 to 3 if the masked BSSID bit = 10                                                                                                                      |

|                |                |      | Key entries from 0x180 to 0x1e0 are treat as shared keys for key id from 0 to 3 if the masked BSSID bit = 11                                                                                                                             |

|                |                |      | The key entry format is described above.                                                                                                                                                                                                 |

| 0x200<br>0x220 | 32bytes<br>x64 | R/W  | 64 Pair-wised key entries                                                                                                                                                                                                                |

| 0x240          |                |      | The key entry format is described above.                                                                                                                                                                                                 |

| 0x9e0          |                |      |                                                                                                                                                                                                                                          |

| 0xa00<br>0xa08 | 8bytes<br>x64  | R/W  | 64 Pair-wised transmitter address (TA) entries                                                                                                                                                                                           |

| 0xa10          |                |      | The mapping of pair-wised TA entries and pair-wised                                                                                                                                                                                      |

# RT2571W

Data sheet

Revision June 22, 2007

|       | key entries is one-to-one, where                        |

|-------|---------------------------------------------------------|

| 0xbf8 | TA entry at offset 0x600 maps to offset 0x200 key entry |

|       | TA entry at offset 0x608 maps to offset 0x220 key entry |

|       | and so on.                                              |

|       | TA entry at offset 0x6f8 maps to offset 0x5e0 key entry |

Revision June 22, 2007

# WMM Scheduler Register

#### AIFSN: Aifsn (offset = 0400h)

| Field        | Туре | Default | Description |  |  |

|--------------|------|---------|-------------|--|--|

| Bit<br>31:16 | R/O  | 0x0     | Reserved.   |  |  |

| Bit<br>15:12 | R/W  | 0x0     | AIFSN3.     |  |  |

| Bit 11:8     | R/W  | 0x0     | AIFSN2.     |  |  |

| Bit 7:4      | R/W  | 0x0     | AIFSN1.     |  |  |

| Bit 3:0      | R/W  | 0x0     | AIFSN0.     |  |  |

#### CW MIN: Cw min (offset = 0404h)

| CW_MIN: Cw_min (offset = 0404h) |      |         |             |  |  |

|---------------------------------|------|---------|-------------|--|--|

| Field                           | Туре | Default | Description |  |  |

| Bit<br>31:16                    | R/O  | 0x0     | Reserved.   |  |  |

| Bit<br>15:12                    | R/W  | 0x0     | Cw_min3.    |  |  |

| Bit 11:8                        | R/W  | 0x0     | Cw_min2.    |  |  |

| Bit 7:4                         | R/W  | 0x0     | Cw_min1.    |  |  |

| Bit 3:0                         | R/W  | 0x0     | Cw_min0.    |  |  |

#### CW\_MAX: Cw\_max (offset = 0408h)

| Field    | Туре | Default | Description |

|----------|------|---------|-------------|

| Bit      | R/W  | 0x0     | Reserved.   |

| 31:16    |      |         |             |

| Bit      | R/W  | 0x0     | Cw_max3.    |

| 15:12    |      |         |             |

| Bit 11:8 | R/W  | 0x0     | Cw_max2.    |

| Bit 7:4  | R/W  | 0x0     | Cw_max1.    |

| Bit 3:0  | R/W  | 0x0     | Cw_max0.    |

### TXOP01: TXOP0 and TXOP1 (offset = 040Ch)

| Field        | Туре | Default | Description           |

|--------------|------|---------|-----------------------|

| Bit<br>31:16 | R/W  | 0x0     | AC1 TXOP. Unit: 32uS. |

| 51.10        |      |         |                       |

| Bit 15:0     | R/W  | 0x0     | AC0 TXOP. Unit: 32uS. |

Revision June 22, 2007

# TXOP23: TXOP2 and TXOP3 (offset = 0410h)

| Field    | Туре | Default | Description           |

|----------|------|---------|-----------------------|

| Bit      | R/W  | 0x0     | AC3 TXOP. Unit: 32uS. |

| 31:16    |      |         |                       |

| Bit 15:0 | R/W  | 0x0     | AC2 TXOP. Unit: 32uS. |

# **MAC Control Register**

#### MAC\_CSR0: ASIC version number (offset = 3000h)

| Field    | Туре | Default | Description             |

|----------|------|---------|-------------------------|

| Bit 31:0 | R    | 0x2573a | MAC ASIC version number |

# MAC\_CSR1: System control register (offset = 3004h)

| Field    | Туре | Default | Description                           |

|----------|------|---------|---------------------------------------|

| Bit 31:3 | R    | 0x0     | Reserved                              |

| Bit 2    | R/W  | 0x0     | Host is ready to work                 |

|          |      |         | 1 = Ready                             |

| Bit 1    | R/W  | 0x1     | Hardware Reset BBP:                   |

|          |      |         | 1: reset BBP                          |

|          |      |         | 0: release reset                      |

| Bit 0    | R/W  | 0x0     | Soft-reset MAC                        |

|          |      |         | 1 = MAC in reset state                |

|          |      |         | 0 = MAC in normal state               |

|          |      |         | This won't reset MAC register values. |

### MAC\_CSR2: MAC address register 0 (offset = 3008h)

| Field     | Туре | Default | Description                                                                                                                                                                                                   |

|-----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 31:24 | R/W  | 0x0     | STA MAC address byte3                                                                                                                                                                                         |

| Bit 23:16 | R/W  | 0x0     | STA MAC address byte2                                                                                                                                                                                         |

| Bit 15:8  | R/W  | 0x0     | STA MAC address byte1                                                                                                                                                                                         |

| Bit 7:0   | R/W  | 0x0     | STA MAC address byte0<br>*Note: <b>byte0</b> is the first byte on network; its LSB is<br>the first bit on network. For a MAC address captured<br>on the network 00:01:02:03:04:05, byte0=00,<br>byte1=01 etc. |

# MAC\_CSR3: MAC address register 1 (offset = 300Ch)

| Field     | Туре | Default | Description                                                                                                      |  |

|-----------|------|---------|------------------------------------------------------------------------------------------------------------------|--|

| Bit 31:24 | R    | 0x0     | Reserved                                                                                                         |  |

| Bit 23:16 | R/W  | 0xFF    | "Unicast-to-me" comparison mask for received<br>Address1 and MAC Address on byte5<br>0: don't care<br>1: compare |  |

| Bit 15:8  | R/W  | 0x0     | STA MAC address byte5                                                                                            |  |

| Bit 7:0   | R/W  | 0x0     | STA MAC address byte4                                                                                            |  |

The multiple BSSID mask for byte5 in MAC\_CSR5 also takes effect on unicast-to-me comparison. The "final" unicast-to-me compare mask on byte5 is (uc\_to\_me\_mask[7:0] & bssid\_mask[1:0]).

**RT2571W**

#### MAC\_CSR4: BSSID register 0 (offset = 3010h)

| Field     | Туре | Default | Description |

|-----------|------|---------|-------------|

| Bit 31:24 | R/W  | 0x0     | BSSID byte3 |

| Bit 23:16 | R/W  | 0x0     | BSSID byte2 |

| Bit 15:8  | R/W  | 0x0     | BSSID byte1 |

| Bit 7:0   | R/W  | 0x0     | BSSID byte0 |

#### MAC\_CSR5: BSSID register 1 (offset = 3014h)

| Field     | Туре | Default | Description                                                                                                                                                                                 |

|-----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 31:18 | R    | 0x0     | Reserved                                                                                                                                                                                    |

| Bit 17:16 | R/W  | 0x3     | Multiple BSSID comparison mask, 0: don't care, 1:<br>enable<br>Bit16: comparison mask bit0 of BSSID<br>byte6(MAC_CSR5 bit8)<br>Bit17: comparison mask bit1 of BSSID<br>byte6(MAC_CSR5 bit9) |

|           |      |         | The value will also affect the number of shared keys<br>in the key table.<br>11: one BSSID; 01, 10: two BSSID; 00: four BSSID                                                               |

| Bit 15:8  | R/W  | 0x0     | BSSID byte5                                                                                                                                                                                 |

| Bit 7:0   | R/W  | 0x0     | BSSID byte4                                                                                                                                                                                 |

The multiple BSSID mask is used to make bit0, bit1 of BSSID byte5 "don't care" in RX BSSID comparison (which result in "is\_my\_bssid" flag in RX descriptor).

#### MAC\_CSR6: Maximum frame length register (offset = 3018h)

| Field    | Туре | Default | Description                                     |

|----------|------|---------|-------------------------------------------------|

| Bit      | R    | 0x0     | Reserved                                        |

| 31:12    |      |         |                                                 |

| Bit 11:0 | R/W  | 0x780   | Maximum Frame length in byte unit               |

|          |      |         | Default value is1920 bytes, i.e. (128Byte * 16) |

ASIC will block incoming frames longer than this maximum size to prevent overwriting RX buffer.

#### MAC\_CSR7: Reserved (offset = 301Ch)

| Field     | Туре | Default | Description |

|-----------|------|---------|-------------|

| Bit 31: 0 | R    | 0x0     | Reserved    |

#### MAC\_CSR8: SIFS / EIFS register (offset = 3020h)

| Field | Туре | Default | Description          |

|-------|------|---------|----------------------|

| Bit   | R/W  | 0x16C   | EIFS in unit of 1-us |

| 31:16 |      |         | Default 364 us       |

**RT2571W**

| Bit 15:8 | R/W | 0x00 | SIFS in unit of 1-us, applied after OFDM RX to<br>compensate OFDM RX PHY delay                                                                   |

|----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7:0  | R/W | 0x0A | SIFS in unit of 1-us, applied after CCK TX/RX and<br>OFDM TX<br>Default 10 us for 11b/g.<br>Driver will change it to 16 us when operating in 11a |

### MAC\_CSR9: Slot time / contention window register (offset = 3024h)

| Field        | Туре | Default | Description                                                                                                                                                               |

|--------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>31:17 | R    | 0x0     | Reserved                                                                                                                                                                  |

| Bit 16       | R/W  | 0x0     | Use following default value as {cwmin, cwmax} pair.<br>Ignore the {cwmin, cwmax} pair in TX descriptor.                                                                   |

| Bit<br>15:12 | R/W  | 0xa     | Defaul value of cwmax                                                                                                                                                     |

| Bit 11:8     | R/W  | 0x3     | Default value of cwmin                                                                                                                                                    |

| Bit 7:0      | R/W  | 0x14    | Slot time in unit of 1-us. This value is used by<br>Backoff engine to calculate the total backoff time.<br>Default 20us for 11b/g.<br>11a and 11g-short-slot-mode is 9 us |

#### MAC\_CSR10: Power mode configuration register (offset = 3028h)

| Field        | Туре | Default | Description                                              |

|--------------|------|---------|----------------------------------------------------------|

| Bit<br>31:13 | R    | 0x0     | Reserved                                                 |

| 31.13        |      |         |                                                          |

| Bit 12       | R/W  | 0x0     | BBP AD/DA power down in Awake state                      |

| Bit 11       | R/W  | 0x0     | BBP PLL power down in Awake state                        |

| Bit 10       | R/W  | 0x1     | RA_PE in Awake state                                     |

| Bit 9        | R/W  | 0x1     | RF_PE in Awake state                                     |

| Bit 8        | R/W  | 0x1     | TR_PE in Awake state (change to 0 automatically when TX) |

| Bit 7:5      | R    | 0x0     | Reserved                                                 |

| Bit 4        | R/W  | 0x1     | BBP AD/DA power down in Sleep state                      |

| Bit 3        | R/W  | 0x1     | BBP PLL power down in Sleep state                        |

| Bit 2        | R/W  | 0x0     | RA_PE in Sleep state                                     |

| Bit 1        | R/W  | 0x0     | RF_PE in Sleep state                                     |

| Bit 0        | R/W  | 0x0     | TR_PE in Sleep state                                     |

**RT2571W**

Revision June 22, 2007

| Field        | Туре | Default | Description                                                                                                                                                                                                                                  |

|--------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>31:20 | R    | 0x0     | Reserved                                                                                                                                                                                                                                     |

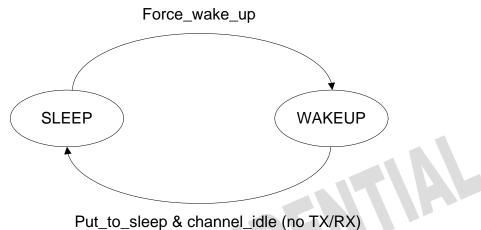

| Bit<br>19:16 | R/W  | 0xA     | Transition time from Sleep to Awake in units of 1-TU<br>(1.024ms)<br>Default: 10<br>state transition from awake to sleep is 0 by default<br>but will postpone until TX and RX process became<br>idle.                                        |

| Bit 15       | R/W  | 0x0     | Enable Auto Wakeup timer interrupt<br>Once enabled, ASIC will auto wakes up BBP/RF to<br>AWAKE state after the specified time (TbcnExp# *<br>BeaconInterval + DelayAfterLastTbcnExp) has past.                                               |

| Bit 14:8     | R/W  | 0x0     | Number of subsequent Tbcn Expirations before<br>Wakeup<br>Default: 0                                                                                                                                                                         |

| Bit 7:0      | R/W  | 0x50    | Delay after the last Tbcn expiration in unit of <del>1/16</del> 1-<br>TU<br>Default is 80, which means 20 TU ahead of next<br>TBTT. This lead time should be sufficient for BBP/RF<br>to recover from whatever power state to AWAKE<br>state |

# MAC\_CSR11: Power saving transition time register (offset = 302Ch)

CAUTION!! Please make sure TBTT timer is enabled if auto wakeup interrupt timer is enabled.

#### MAC\_CSR12: Power state control register (offset = 3030h)

| Field    | Туре | Default | Description                                         |

|----------|------|---------|-----------------------------------------------------|

| Bit 31:3 | R    | 0x0     | Reserved                                            |

| Bit 3    | R    | 0x0     | 0: BB/RF is not ready                               |

|          |      |         | 1: BB/RF is stable                                  |

| Bit 2    | WC   | 0x0     | Force wake up, write 1 to put BBP/RF to AWAKE       |

|          |      |         | state.                                              |

| Bit 1    | WC   | 0x0     | Put to sleep, write 1 to put BBP/RF to SLEEP state. |

| Bit 0    | R    | 0x0     | Power state, 0:SLEEP mode, 1: AWAKE state           |

"Put to sleep" command may not be execute right away due to channel busy. The command postpone time is random.

"Force wake up" command will cancel the "Put to sleep" command and wake up MAC immediately anyhow.

# **RT2571W**

Data sheet

Revision June 22, 2007

CAUTION!! If "Put to sleep" command is issued but power state does not go to sleep state after a long time(due to random postpone time), please issue "Force wake up" command to cancel "Put to sleep" command before treat MAC as in AWAKE state.

"Force wake up" command has higher priority than "Put to sleep" command if they are issued at the same time.

# MAC, CSR13: GPIO control register (offset = 3034b)

|          | AC_CONTS. OF IC CONTOFFEGISTER (OFISEL = 50541) |         |                                       |  |  |

|----------|-------------------------------------------------|---------|---------------------------------------|--|--|

| Field    | Туре                                            | Default | Description                           |  |  |

| Bit      | R                                               | 0x0     | Reserved                              |  |  |

| 31:16    |                                                 |         |                                       |  |  |

| Bit 15:8 | R/W                                             | Oxff    | GPIO7-0 direction, 0:input, 1: output |  |  |

| Bit 7:0  | R/W                                             | 0x00    | GPIO7-0 value                         |  |  |

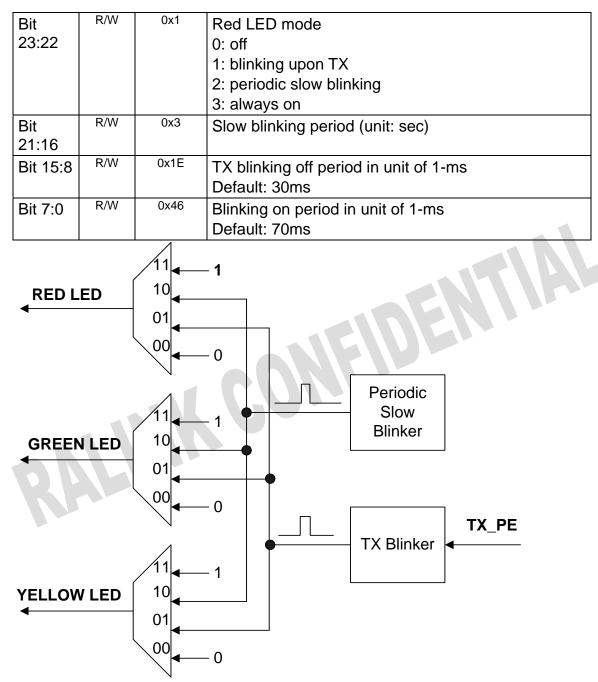

#### MAC\_CSR14: LED control register (offset = 3038h)

| 10.10_00 |      |         |                           |  |  |

|----------|------|---------|---------------------------|--|--|

| Field    | Туре | Default | Description               |  |  |

| Bit      | R    | 0x0     | Reserved                  |  |  |

| 31:29    |      |         |                           |  |  |

| Bit 28   | R/W  | 0x0     | LED polarity              |  |  |

|          |      |         | 0: active low             |  |  |

|          |      |         | 1: active high            |  |  |

| Bit      | R/W  | 0x0     | Yellow LED mode           |  |  |

| 27:26    |      |         | 0: off                    |  |  |

|          |      |         | 1: blinking upon TX       |  |  |