# **USB PD Type-C Controller for SMPS**

## **General Description**

The RT7207 is a secondary-side USB Power Delivery (USB PD) Type-C controller for high-efficiency off-line AC-DC converters with slim form factor. The RT7207 integrates an MCU as a policy engine to handle USB PD protocol, and also integrates a built-in Biphase Mark Coding (BMC) transceiver for USB PD or other proprietary protocols. An internal synchronous rectifier controller (SRC) can operate in both continuous-conduction mode (CCM) and discontinuous-conduction mode (DCM) even in the condition of a wide output voltage range of 3.3V to 20V. Dual operational amplifiers with respectively programmable reference voltages are included for voltage-loop and current-loop regulation to provide programmable constant-voltage (CV) and constant-current (CC) regulation in high precision.

# **Applications**

- USB PD Type-C Chargers/Adapters for Smart Phones, NBs, Tablets and All Other Electronics.

- USB PD Extension Cores with Offline AC-DC Converters.

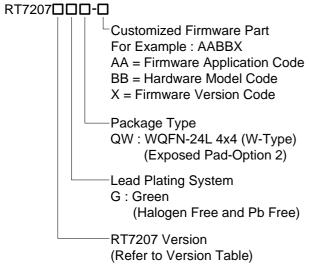

# **Ordering Information**

#### Note:

#### Richtek products are:

DS7207-00 January 2017

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Protocols Supported

- **▶ USB PD 2.0**

- ▶ Other Proprietary Protocols

- Highly Integrated

- ► Embedded MCU with an OTP-ROM of 32kB and an SRAM of 1kB

- **▶ Embedded BMC Transceiver**

- Built-in Synchronous Rectifier Driver and Controller

- ▶ Built-in Charge Pump for a Wide V<sub>DD</sub> Operatio Range of 3.3V to 20V

- ▶ Built-in Shunt Regulator for Constant-Voltage and Constant-Current Control

- ▶ Programmable Cable Compensation

- ▶ BLD Pin for Quick Discharge of Output Capacitor

- ▶ USBP Pin for Direct Drive of External Blocking P-MOSFET

- ▶ Power-Saving Mode in Standby Mode

- Protection

- Adaptive Output Over-Voltage Protection

- Adaptive Under-Voltage Protection

- ▶ Firmware-Programmable Over-Current Protection

- Firmware-Programmable Over-Temperature Protection

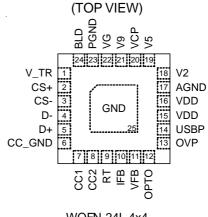

# **Pin Configuration**

WQFN-24L 4x4

# **Marking Information**

AB=YM DNNAA BBX AB=: Product Code YMDNN: Date Code AABBX: Firmware Code

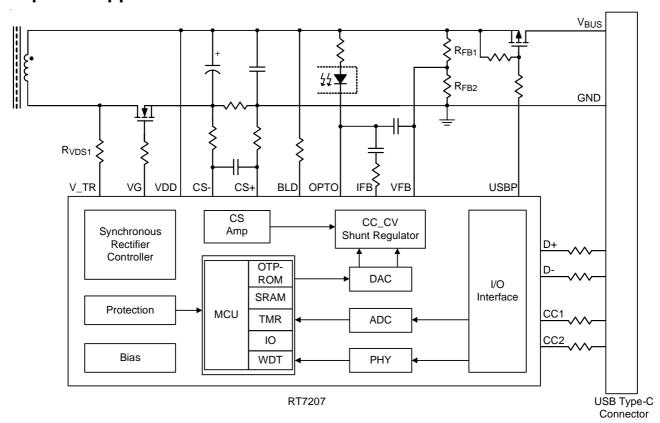

# **Simplified Application Circuit**

### **RT7207 Version Table**

| Version                                                                                                 | RT7207 | RT7207L |

|---------------------------------------------------------------------------------------------------------|--------|---------|

| Maximum Output Voltage                                                                                  | 20V    | 12V     |

| SR MOSFET V <sub>DS</sub> Scaling Factor [R <sub>VDS2</sub> / (R <sub>VDS1</sub> + R <sub>VDS2</sub> )] | 1/42   | 1/26    |

| V <sub>OUT</sub> Scaling Factor [R <sub>FB2</sub> / (R <sub>FB1</sub> + R <sub>FB2</sub> )]             | 1/8    | 1/5     |

**Functional Pin Description**

| Pin No. | Pin Name | Туре   | Pin Function                                                                                                                       |

|---------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V_TR     | Al     | Transformer voltage sense node.                                                                                                    |

| 2       | CS+      | Al     | Positive input of a current-sense amplifier for output current sensing.                                                            |

| 3       | CS-      | Al     | Negative input of a current-sense amplifier for output current sensing.                                                            |

| 4       | D-       | A/D IO | USB D- channel.                                                                                                                    |

| 5       | D+       | A/D IO | USB D+ channel.                                                                                                                    |

| 6       | CC_GND   | GND    | Alternative ground for CC1 and CC2.                                                                                                |

| 7       | CC1      | A/D IO | Type-C connector Configuration Channel (CC) 1, used to detect a cable plug event and determine the cable orientation.              |

| 8       | CC2      | A/D IO | Type-C connector Configuration Channel (CC) 2, used to detect a cable plug event and determine the cable orientation.              |

| 9       | RT       | A/D I  | Remote thermal sensor connection node for over-temperature protection.                                                             |

| 10      | IFB      | Al     | Feedback input for the constant-current loop.                                                                                      |

| 11      | VFB      | Al     | Feedback input for the constant-voltage loop.                                                                                      |

| 12      | OPTO     | AO     | Current sink output for optocoupler connection.                                                                                    |

| 13      | OVP      | AO     | Over-voltage fault indication output, used to pull low an optocoupler.                                                             |

| 14      | USBP     | DIO    | Control signal of the blocking P-MOSFET.                                                                                           |

| 15, 16  | VDD      | PWR    | Supply input voltage.                                                                                                              |

| 17      | AGND     | GND    | Analog ground.                                                                                                                     |

| 18      | V2       | PWR    | Regulated DC bias to supply for the MCU.                                                                                           |

| 19      | V5       | PWR    | Regulated DC bias to supply for internal circuitry.                                                                                |

| 20      | VCP      | AO     | Charge pump driver output.                                                                                                         |

| 21      | V9       | PWR    | Regulated DC bias to supply for the synchronous rectifier driver.                                                                  |

| 22      | VG       | AO     | Gate driver output for the SR MOSFET.                                                                                              |

| 23      | PGND     | GND    | Power ground.                                                                                                                      |

| 24      | BLD      | D IO   | Bleeder connection node to provide another path to discharge the output capacitor.                                                 |

| 25      | GND      | GND    | Power ground. The exposed pad must be connected to GND and well soldered to a large PCB copper area for maximum power dissipation. |

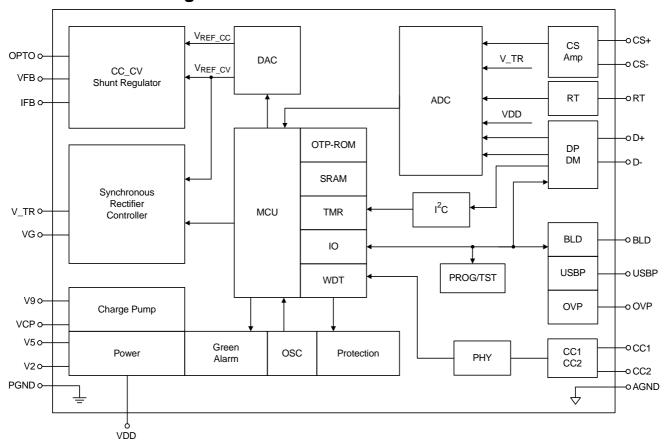

# **Functional Block Diagram**

# **Operation**

The RT7207 is a highly integrated secondary-side USB PDType-C controller with various functions and protections for off-line AC-DC converters.

#### **Power Structure**

Biased by the VDD pin, the RT7207 has two regulated DC output voltages,  $V_5$  and  $V_2$ , to supply the internal circuit and the internal microprocessor (MCU). The bypass capacitors at the V2 and V5 pins are required to improve stability of the internal LDO and to minimize regulated ripple voltages. The RT7207 also integrates a charge pump to generate a boost voltage  $V_9$  from  $V_5$  with VCP pin for capacitor connection so that the V9 voltage can be nearly 2 times of the V5 voltage and the VG pin can directly drive the SR MOSFET. Besides, the charge pump allows the controller to operate under low supply voltage condition as long as the output voltage is not below the programmed UVP level.

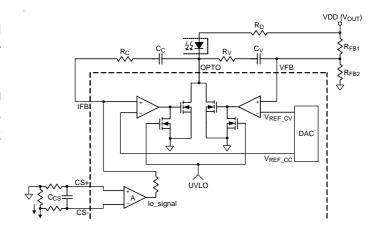

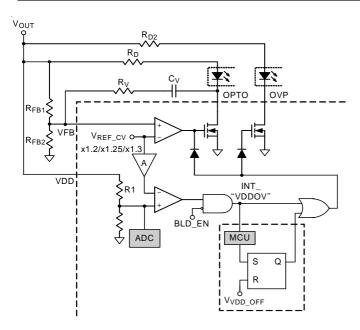

# Constant-Voltage and Constant-Current (CV/CC) Regulators

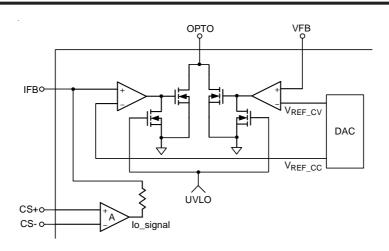

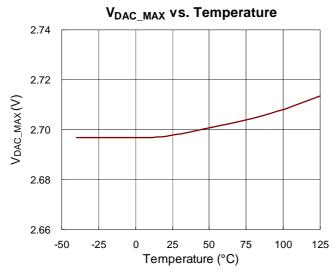

Two regulators are paralleled and connected to an opendrain output, OPTO pin. The operation of each feedback loop is similar to that of the traditional TL431 shunt regulator except that V<sub>OPTO</sub> operating range is wider, from 0.3V to 25V, which enables easy design of converters with a wider output range. The OPTO pin will be in high-impedance state, if the VDD voltage is still below a UVLO threshold V<sub>VDD</sub> ON, which ensures a smooth power-on sequence. The reference voltages, V<sub>REF\_CV</sub> and V<sub>REF\_CC</sub>, for the voltage and current feedback loops, respectively, are analog output voltages from the embedded DAC, and their digital counterparts are from the MCU. The analog output range of the 9-bit DAC is from 0 to V<sub>DAC MAX</sub> (typical 2.7V), which makes output voltage resolution as small as 42mV and 26mV for the RT7207 and RT7207L, respectively, to achieve high-precision CV regulation.

Figure 1. CV and CC Loops

#### **Current-Sense Amplifier**

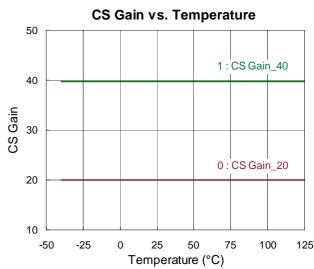

To minimize power loss of the current sense resistor in the converter, the RT7207 has an amplifier with virtually zero input offset voltage and with a register-programmable voltage gain of 20 or 40. The sensed output current is amplified by the current-sense amplifier, shown as "lo\_signal" in Figure 1, which is then sent to the current-loop regulator for constant-current regulation and also sent to the MCU, by way of an ADC for analog-to-digital conversion, to update the output current status for the MCU.

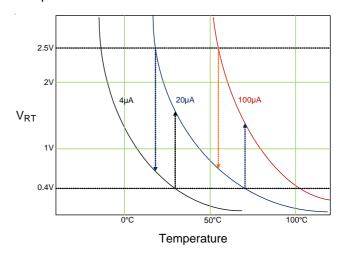

#### **External Temperature Sensing**

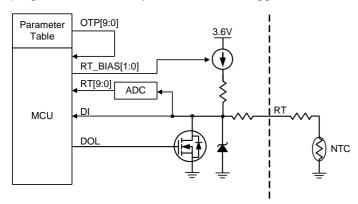

The RT7207 provides the RT pin, as a register-programmable current source to bias a remote thermal sensor, such as a thermistor (NTC), as shown in Figure 2. If the RT voltage is below an over-temperature protection (OTP) threshold and the condition sustains for a programmed time delay, the OTP will be triggered.

Figure 2. External Temperature Sensing

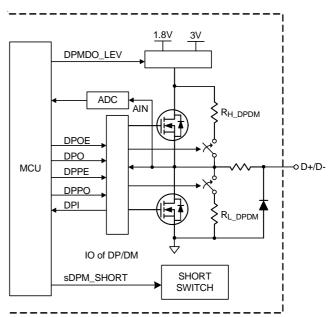

#### Interface of D+ and D-

The D+ and D- pins are used for BC1.2 compliance or for communication with other proprietary protocols. The D+ and D- pins, connected to the MCU via an ADC, can be reprogrammed for other purposes since they can be used as an analog/digital input or output, as shown in Figure 3.

Figure 3. Interface of D+ and D-

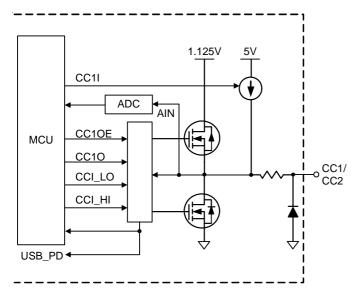

#### Interface of CC1 and CC2

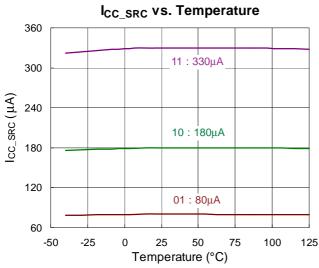

The CC1 and CC2 are used for compliance with USB PD Type-C specification. When configured as a Downstream Facing Port (DFP), three current capabilities of  $80\mu\text{A}$ ,  $180\mu\text{A}$ , and  $330\mu\text{A}$ , provided by each of the CC pins, will be advertised to an Upstream Facing Port (UFP) as default USB current, 1.5A, and 3.0A, respectively, as shown in Figure 4.

Figure 4. Interface of CC1 and CC2

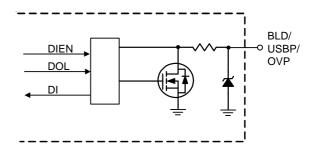

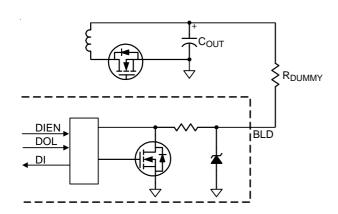

#### Open-Drain Drivers for BLD, USBP and OVP Pins

The BLD, USBP and OVP pins with their specific functions are driven by open-drain drivers, as shown in Figure 5 and explained below.

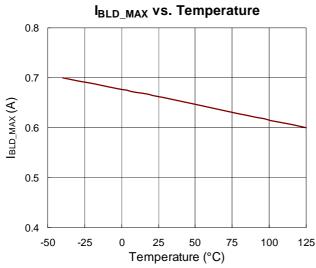

The BLD pin is used as a bleeder to help discharge the output capacitor to  $V_{safe5V}$  upon the detachment of a connected device, or to a lower desired output voltage level upon a UFP request, such as from 20V to 12V. A resistor is connected between  $V_{OUT}$  and the BLD pin and a power resistor can be used for better power dissipation capability.

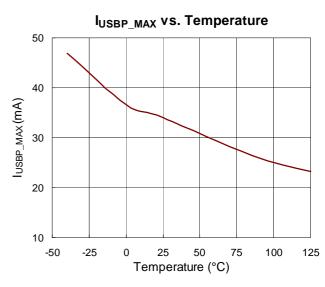

The USBP pin provides an active-low enable control for an external blocking P-MOSFET for  $V_{BUS}$  isolation, as shown in Typical Application Circuit. If no UFP is attached or any fault condition, such as over-voltage, under-voltage, over-temperature, or short-circuit, occurs, the USBP pin will be pulled high to disable the P-MOSFET for  $V_{BUS}$  isolation.

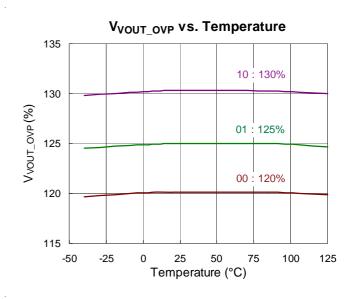

The OVP pin is pulled low when output over-voltage condition (register-programmable: 120%, 125%, 130%) occurs. By way of an optocoupler, it can shut down the primary-side controller (for example, RT7786).

Figure 5. Interface of the BLD, USBP and OVP Pins

#### **SR Control**

To improve the AC-DC converters efficiency, the RT7207 includes a SR controller, which has proprietary autotracking function to minimize dead time between the conduction intervals of the SR MOSFET and the main switch MOSFET, while it can still ensure safe operation in both DCM and CCM conditions and even in a wide output range. To prevent the on-time overlap of the main switch MOSFET and the SR MOSFET, the SR controller will be temporarily turned off under conditions of load transition, output voltage transition, output short circuit, or low output or input voltages with programmable thresholds. At light load or no load condition, the SR controller will also be disabled to reduce power consumption.

# Absolute Maximum Ratings (Note 1)

| • VDD, OPTO, BLD, OVP, USBP to GND                                          | -0.3V to 25V                                   |

|-----------------------------------------------------------------------------|------------------------------------------------|

| • V9, VG to GND                                                             | -0.3V to 12V                                   |

| • V5, VCP, VFB, IFB, V_TR, RT, D+, D-, CC1, CC2, CS+, CS- to GND            | -0.3V to $6.5V$                                |

| • V2 to GND                                                                 | -0.3V to $2.5V$                                |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                                |

| WQFN-24L 4x4                                                                | 3.57W                                          |

| Package Thermal Resistance (Note 2)                                         |                                                |

| WQFN-24L 4x4, $\theta_{JA}$                                                 | 28°C/W                                         |

| WQFN-24L 4x4, $\theta_{JC}$                                                 | 7.1°C/W                                        |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                                          |

| • Junction Temperature                                                      |                                                |

| Storage Temperature Range                                                   | $-65^{\circ}\text{C}$ to $150^{\circ}\text{C}$ |

| ESD Susceptibility (Note 3)                                                 |                                                |

| HBM (Human Body Model)                                                      | 2kV                                            |

|                                                                             |                                                |

| Recommended Operating Conditions (Note 4)                                   |                                                |

| • Supply Input Voltage, VDD                                                 | 3.3V to 22V                                    |

|                                                                             |                                                |

• Junction Temperature Range ------ -40°C to 125°C

• Ambient Temperature Range ------ -40°C to 85°C

# **Electrical Characteristics**

(T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                                        | Symbol                | Test Conditions                   | Min  | Тур  | Max  | Unit |

|--------------------------------------------------|-----------------------|-----------------------------------|------|------|------|------|

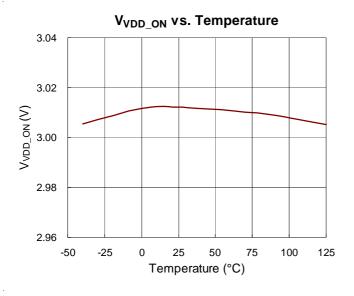

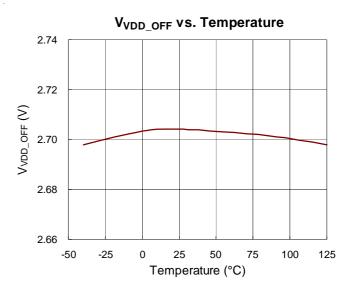

| VDD Section                                      |                       |                                   |      |      |      |      |

| VDD Turn-On Threshold Voltage                    | V <sub>VDD_ON</sub>   |                                   | 2.85 | 3    | 3.15 | V    |

| VDD Turn-Off Threshold<br>Voltage                | $V_{VDD\_OFF}$        |                                   | 2.55 | 2.7  | 2.85 | V    |

| VDD Start-Up Current                             | I <sub>DD_START</sub> | $V_{DD} = 5V$                     |      | 100  | 200  | μΑ   |

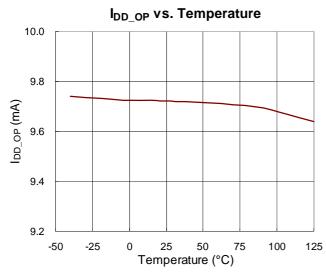

| VDD Operating Current                            | I <sub>DD_OP</sub>    | SR driver is disabled             |      | 10   |      | mA   |

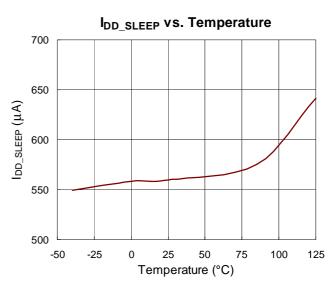

| VDD Sleep-Mode Current                           | I <sub>DD_SLEEP</sub> | In sleep mode                     |      | 750  |      | μΑ   |

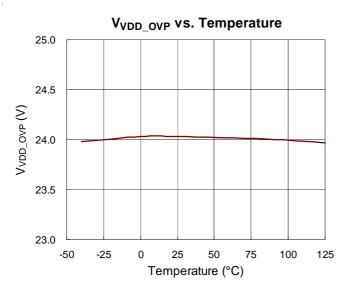

| VDD Over-Voltage Protection<br>Threshold Voltage | $V_{VDD\_OVP}$        |                                   | 23   | 24   | 25   | V    |

| VDD Over-Voltage Protection<br>Deglitch Time     | t <sub>D_VDDOVP</sub> |                                   |      | 50   |      | μЅ   |

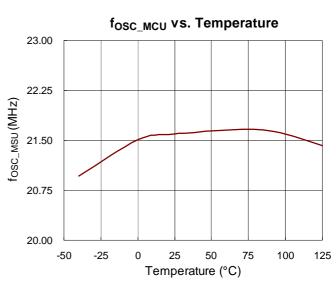

| MCU Operating Frequency                          | fosc_mcu              | V <sub>DD</sub> = 5V              | 20.5 | 21.6 | 22.7 | MHz  |

| Internal Bias                                    |                       |                                   |      |      |      |      |

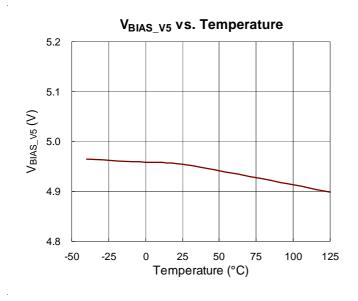

| V5                                               | V <sub>BIAS_V5</sub>  | 6V < V <sub>DD</sub> < 25V        | 4.75 | 5    | 5.25 | V    |

| Load Regulation                                  |                       | 1mA < I <sub>BIAS_V5</sub> < 30mA |      |      | 150  | mV   |

| V5 Output Short-Circuit Current                  | I <sub>V5</sub> _sc   |                                   | 60   | 90   | 120  | mA   |

Copyright@2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                                                  | Symbol                                   | Test Conditions                                      |       | Min  | Тур      | Max  | Unit |

|----------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|-------|------|----------|------|------|

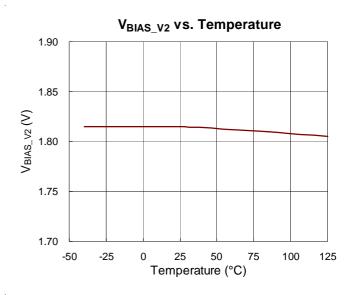

| V2                                                                         | V <sub>BIAS_V2</sub>                     | 3.3V < V <sub>DD</sub> < 25V                         |       | 1.71 | 1.8      | 1.89 | V    |

| Load Regulation                                                            |                                          | 1mA < I <sub>BIAS_V2</sub> < 20mA                    | 4     |      |          | 20   | mV   |

| V2 Output Short-Circuit Current                                            | I <sub>V2</sub> _sc                      |                                                      |       | 30   | 50       | 70   | mA   |

| Regulators Section                                                         | •                                        | •                                                    |       |      |          | •    | 1    |

| Maximum DAC Output Voltage for CC and CV Regulators                        | V <sub>DAC_MAX</sub>                     | 9-bit D/A conversion                                 |       | 2.67 | 2.7      | 2.73 | V    |

| Ratio of Change in Reference<br>Input Voltage to Change in<br>OPTO Voltage | $\frac{\Delta V_{REF}}{\Delta V_{OPTO}}$ | $\Delta V_{OPTO} = 25V \text{ to } V_{REF}$ (Note 5) |       | -    | -1.2     | -2.4 | mV/V |

| Reference Input Current                                                    | I <sub>REF</sub>                         | (Note 5)                                             |       |      | 0.1      |      | μΑ   |

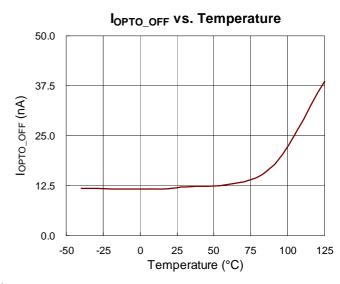

| Off-State OPTO Current                                                     | IOPTO_OFF                                | OPTO pin is open-circu                               | ited  |      | 230      | 500  | nA   |

| Dynamic Impedance                                                          | Z <sub>OPTO</sub>                        | VOPTO = VREF, IOPTO = 1mA, f < 1kHz (Note            |       |      | 0.22     | 0.5  | Ω    |

| OPTO Turn-On Impedance                                                     | Ron_орто                                 | IOPTO_SINK = 10mA<br>(Note 5)                        |       |      |          | 150  | Ω    |

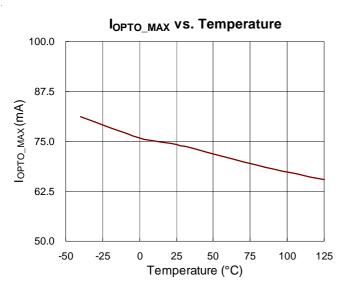

| Maximum OPTO Sinking Current                                               | Горто_мах                                |                                                      |       | 2    |          | 20   | mA   |

| Current-Sense Amplifier                                                    |                                          |                                                      |       |      |          |      |      |

| Register-Programmable Current-Sense Voltage Gain                           |                                          |                                                      | 0     |      | 20<br>40 |      | V/V  |

| Unit Gain Bandwidth                                                        |                                          | (Note 5)                                             |       | 1000 |          |      | kHz  |

| Output Current                                                             |                                          | (Note 5)                                             |       |      | 0.1      |      | mA   |

| Charge Pump Section                                                        |                                          | ,                                                    |       |      |          |      |      |

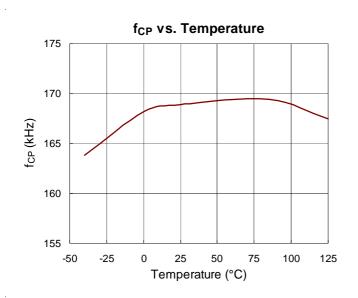

| Charge Pump Operating Frequency                                            | fcP                                      |                                                      |       | 150  | 170      | 190  | kHz  |

| Rise Time                                                                  | t <sub>R_CP</sub>                        | $C_L = 6nF, V_5 = 5V, from to 80\%$                  | 1 20% | 70   | 140      | 210  | ns   |

| Fall Time                                                                  | t <sub>F_CP</sub>                        | $C_L = 6nF, V_5 = 5V, from to 20\%$                  | n 80% | 60   | 110      | 160  | ns   |

| Charge Pump Driver Impedance                                               | ROUT_CP                                  | (Note 5)                                             |       |      |          | 10   | Ω    |

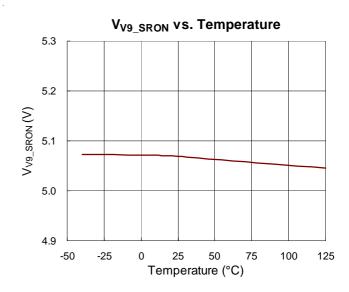

| SR Driver Turn-On Threshold                                                | Vv9_sron                                 |                                                      |       | 4.9  | 5.1      | 5.3  | V    |

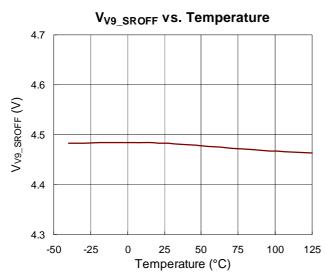

| SR Driver Turn-Off Threshold                                               | V <sub>V9</sub> _SROFF                   |                                                      |       | 4.3  | 4.5      | 4.7  | V    |

| Debounce Time                                                              | t <sub>D_V9</sub>                        | (Note 5)                                             |       |      | 50       |      | μS   |

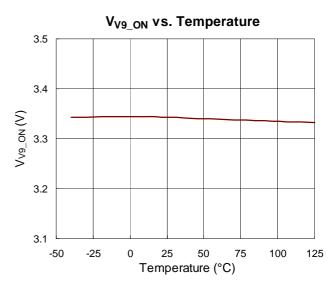

| V9 Turn-On Threshold Voltage                                               | V <sub>V9_ON</sub>                       |                                                      |       | 3.1  | 3.3      | 3.5  | V    |

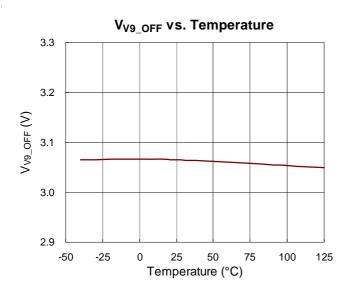

| V9 Turn-Off Threshold Voltage                                              | V <sub>V9_OFF</sub>                      |                                                      |       | 2.9  | 3.1      | 3.3  | V    |

| RT Section                                                                 |                                          |                                                      |       |      |          |      |      |

| Open-Loop Voltage                                                          | V <sub>RT_OP</sub>                       | $V_{DD} = 5V$                                        |       | 3.2  | 3.6      | 4    | V    |

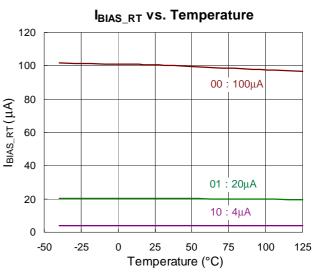

|                                                                            |                                          |                                                      | 00    | 90   | 100      | 110  |      |

| Register-Programmable Internal Bias Current                                | I <sub>BIAS_RT</sub>                     |                                                      | 01    | 18   | 20       | 22   | μΑ   |

| <del></del>                                                                |                                          |                                                      | 10    | 3.6  | 4        | 4.4  |      |

| Parameter                                    | Symbol                                       | Test Conditions                                      |          | Min        | Тур    | Max    | Unit |

|----------------------------------------------|----------------------------------------------|------------------------------------------------------|----------|------------|--------|--------|------|

| OVP Pin Section                              | •                                            | •                                                    |          | •          |        |        |      |

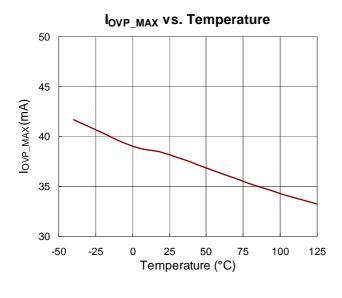

| Maximum OVP Sinking Current                  | I <sub>OVP_MAX</sub>                         |                                                      |          | 2          |        | 20     | mA   |

| Pull-Low Impedance                           | R <sub>L_OVP</sub>                           | (Note 5)                                             |          |            |        | 150    | Ω    |

| Register-Programmable                        |                                              |                                                      | 00       | 114        | 120    | 126    |      |

| Over-Voltage Protection                      | V <sub>VOUT_OVP</sub>                        | With respect to                                      | 01       | 118.75     | 125    | 131.25 | %    |

| Threshold                                    |                                              | VREF_CV                                              | 10       | 123.5      | 130    | 136.5  |      |

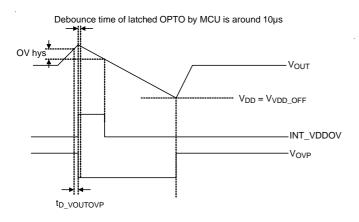

| Debounce Time                                | t <sub>D_</sub> VOUTOVP                      | OVP pin is latched till V below V <sub>VDD_OFF</sub> | DD is    |            | 50     |        | μS   |

| BLD Section                                  | •                                            | •                                                    |          | •          |        |        |      |

| Maximum BLD Sinking Current                  | I <sub>BLD_MAX</sub>                         | In 300ms                                             |          | 0.5        |        | 0.6    | Α    |

| Pull-Low Impedance                           | R <sub>L_BLD</sub>                           | (Note 5)                                             |          |            | 10     | 15     | Ω    |

| D+, D- Section                               | •                                            | •                                                    |          | •          |        |        |      |

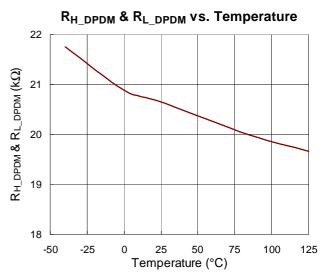

| Pull-High/-Low Resistance                    | R <sub>H_DPDM</sub> ,<br>R <sub>L_DPDM</sub> |                                                      |          | 15         | 20     | 25     | kΩ   |

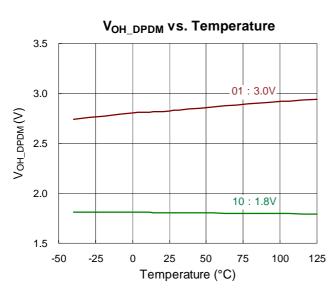

| Register-Programmable Output                 | VOH_3.0V                                     | $V_{DD} = 5V$ ,                                      | 01       | 2.7        | 3      | 3.3    | \ /  |

| High Voltage                                 | VOH_1.8V                                     | $R_{LOAD} = 15k\Omega$                               | 10       | 1.62       | 1.8    | 1.98   | V    |

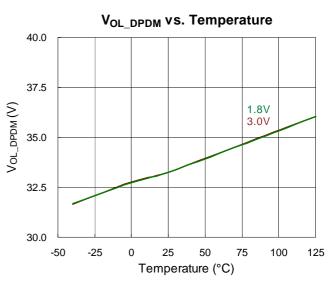

| Output Law Valtage                           | V <sub>OL_3.0V</sub>                         | $R_{LOAD} = 15k\Omega$                               |          |            |        | 0.0    | V    |

| Output Low Voltage                           | V <sub>OL_1.8</sub> V                        |                                                      |          |            |        | 0.2    | V    |

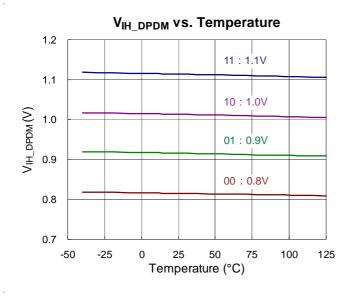

|                                              | VIH_DPDM                                     |                                                      | 00       | 0.7        | 0.8    | 0.9    |      |

| Register-Programmable Input                  |                                              |                                                      |          | 0.8        | 0.9    | 1      | V    |

| High Trip Voltage                            |                                              |                                                      | 10       | 0.9        | 1      | 1.1    |      |

|                                              |                                              |                                                      | 11       | 1          | 1.1    | 1.2    |      |

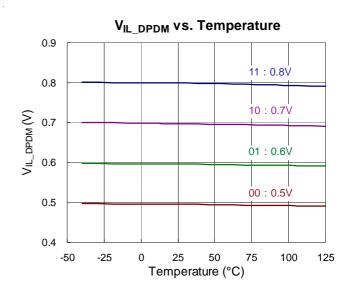

|                                              |                                              |                                                      | 00       | 0.4        | 0.5    | 0.6    |      |

| Register-Programmable Input Low Trip Voltage | VIL_ DPDM                                    |                                                      | 01<br>10 | 0.5<br>0.6 | 0.6    | 0.7    | V    |

|                                              |                                              |                                                      | 11       | 0.0        | 0.7    | 0.9    |      |

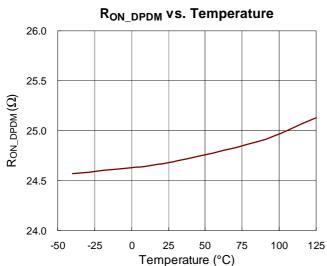

| DPDM Switch On-Resistance                    | RON DPDM                                     |                                                      | •••      |            |        | 40     | Ω    |

| CC1, CC2 Section                             |                                              |                                                      |          | l          |        |        |      |

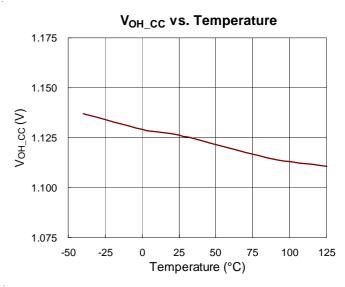

| Output High Voltage                          | Voh_cc                                       |                                                      |          | 1.05       | 1.125  | 1.2    | V    |

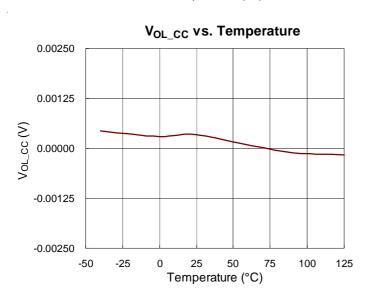

| Output Low Voltage                           | V <sub>OL_CC</sub>                           |                                                      |          | 0          | 0.0375 | 0.075  | V    |

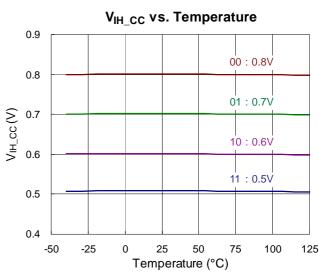

|                                              |                                              |                                                      | 00       | 0.7        | 0.8    | 0.9    |      |

| Register-Programmable Input                  |                                              |                                                      | 01       | 0.6        | 0.7    | 0.8    | 17   |

| High Trip Voltage                            | VIH_CC                                       |                                                      | 10       | 0.5        | 0.6    | 0.7    | V    |

|                                              |                                              |                                                      | 11       | 0.4        | 0.5    | 0.6    |      |

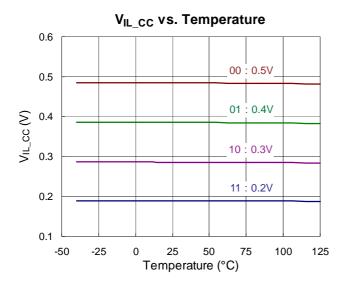

|                                              |                                              |                                                      | 00       | 0.4        | 0.5    | 0.6    |      |

| Register-Programmable Input                  | V <sub>IL_CC</sub>                           |                                                      | 01       | 0.3        | 0.4    | 0.5    | V    |

| Low Trip Voltage                             | VIL_CC                                       |                                                      | 10       | 0.2        | 0.3    | 0.4    | v    |

|                                              |                                              |                                                      | 11       | 0.1        | 0.2    | 0.3    |      |

| Parameter                              | Symbol                                   | Test Conditions                                                              |                           | Min   | Тур   | Max  | Unit |

|----------------------------------------|------------------------------------------|------------------------------------------------------------------------------|---------------------------|-------|-------|------|------|

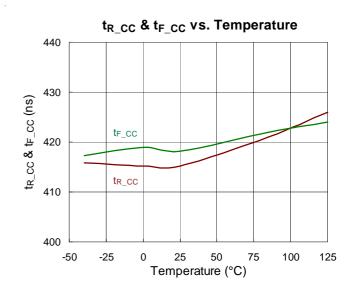

| Rise Time/Fall Time                    | t <sub>R_CC</sub> ,<br>t <sub>F_CC</sub> | C <sub>LOAD</sub> = 600pF                                                    | C <sub>LOAD</sub> = 600pF |       |       |      | ns   |

|                                        |                                          |                                                                              | 01                        | 72    | 80    | 88   |      |

| Register-Programmable Sourcing Current | ICC_SRC                                  |                                                                              | 10                        | 166   | 180   | 194  | μΑ   |

|                                        |                                          |                                                                              | 11                        | 304   | 330   | 356  |      |

| USBP Section                           |                                          | <del></del>                                                                  |                           |       |       |      |      |

| Maximum USBP Sinking Current           | I <sub>USBP_MAX</sub>                    |                                                                              |                           | 2     |       | 20   | mA   |

| Pull-Low Impedance                     | R <sub>L_USBP</sub>                      | (Note 5)                                                                     |                           |       |       | 150  | Ω    |

| SR Driver Section                      |                                          |                                                                              |                           |       |       |      |      |

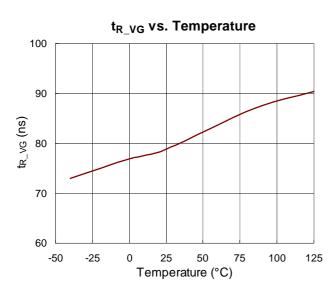

| Rise Time                              | t <sub>R_</sub> v <sub>G</sub>           | $C_L = 6nF, V_9 = 9V, from to 80\%$                                          | n 20%                     |       | 75    | 125  | ns   |

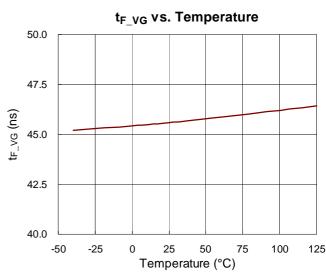

| Fall Time                              | tF_VG                                    | $C_L = 6nF, V_9 = 9V, from to 20\%$                                          | า 80%                     |       | 35    | 85   | ns   |

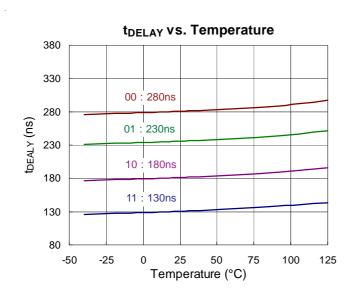

|                                        | tDELAY                                   | Delay and debounce<br>time of V_TR falling<br>tDELAY =<br>tV_TR_FALLING + tp | 00                        | 180   | 280   | 380  | ns . |

| OTP-Programmable Turn-On               |                                          |                                                                              | 01                        | 130   | 230   | 330  |      |

| Delay                                  |                                          |                                                                              | 10                        | 80    | 180   | 280  |      |

|                                        |                                          |                                                                              | 11                        | 30    | 130   | 230  |      |

| Propagation Delay                      | t₽                                       |                                                                              |                           |       | 100   |      | ns   |

| Internal Pull-Low Resistor             |                                          | (Note 5)                                                                     |                           |       | 20    |      | kΩ   |

| V_TR Section                           |                                          |                                                                              |                           |       |       |      |      |

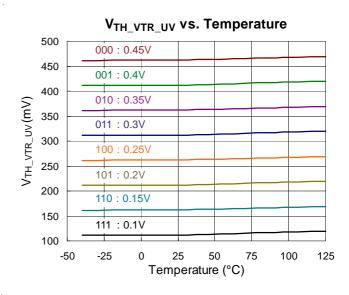

|                                        |                                          |                                                                              | 000                       | 0.35  | 0.45  | 0.55 |      |

|                                        |                                          |                                                                              | 001                       | 0.3   | 0.4   | 0.5  | V    |

|                                        |                                          | If V <sub>V_TR_SH</sub> – (V <sub>OUT</sub> x                                | 010                       | 0.25  | 0.35  | 0.45 |      |

| OTP-Programmable V_TR Under            | VTH_VTR_UV                               | K <sub>VDS_SR</sub> ) >                                                      | 011                       | 0.2   | 0.3   | 0.4  |      |

| Voltage Threshold                      | VIII_VIK_OV                              | V <sub>TH_VTR_UV</sub> , SR<br>driver is active                              | 100                       | 0.15  | 0.25  | 0.35 |      |

|                                        |                                          | unver is active                                                              | 101                       | 0.1   | 0.2   | 0.3  |      |

|                                        |                                          |                                                                              | 110                       | 0.05  | 0.15  | 0.25 |      |

|                                        |                                          |                                                                              | 111                       | 0     | 0.1   | 0.2  |      |

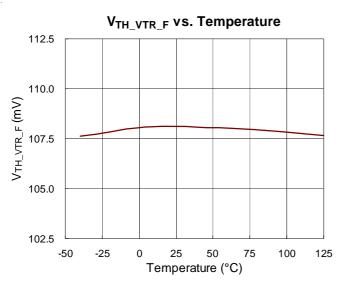

| V_TR Falling Edge Threshold<br>Voltage | VTH_VTR_F                                | SR turn-on trip point                                                        |                           | 0.025 | 0.125 | 0.2  | V    |

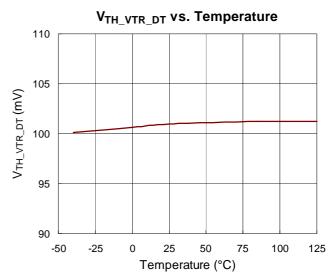

| Dead Time Comparator<br>Threshold      | V <sub>TH_VTR_DT</sub>                   |                                                                              |                           |       | 0.1   |      | V    |

| Dead Time Comparator Delay             |                                          | (Note 5)                                                                     |                           |       |       | 40   | ns   |

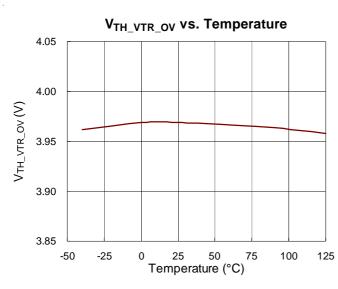

| V_TR Over-Voltage Threshold            | VTH_VTR_OV                               |                                                                              |                           | 3.8   | 4     | 4.2  | V    |

| Parameter                               | Symbol              | Test Conditions                                                                                                                              |         | Min  | Тур  | Max  | Unit      |

|-----------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|-----------|

| SR Control Section                      | •                   | •                                                                                                                                            |         | •    |      |      | •         |

| SR MOSFET V <sub>DS</sub> Scaling       | Kyro or             | R <sub>VDS2</sub> / (R <sub>VDS1</sub> + R <sub>VDS2</sub> )<br>(For RT7207) (Note 5)                                                        |         |      | 1/42 |      |           |

| Factor                                  | K <sub>VDS_SR</sub> | R <sub>VDS2</sub> / (R <sub>VDS1</sub> + R <sub>VDS</sub> (For RT7207L) (Note                                                                | •       |      | 1/26 |      |           |

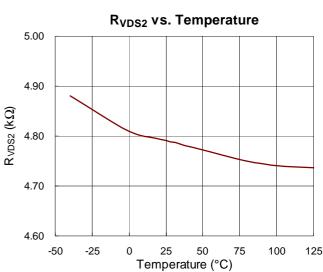

| V_TR Internal Resistance                | R <sub>VDS2</sub>   |                                                                                                                                              |         | 4.56 | 4.8  | 5.04 | kΩ        |

| Maximum Ratio of VG On-Time             | Ksron_max           | If tsr_on[n] > tsr_on[n-<br>Ksron_max, tsr_on[n] v<br>limited to tsr_on[n-1] x<br>Ksron_max and stop<br>automatic tracking cour<br>(Note 5)  | will    |      | 1.06 |      |           |

|                                         |                     | If tv_TR[n] > tv_TR[n-1]                                                                                                                     | 00      |      | 0.3  |      |           |

| OTP-Programmable V_TR                   |                     | + tpwLMT_VTR or<br>tv_TR[n] < tv_TR[n-1] -                                                                                                   | 01      |      | 0.5  |      |           |

| Pulse Width Expansion/Shrink Limit      | tpwlmt_vtr          | tpwLMT_VTR, reset<br>automatic tracking<br>counter<br>(Note 5)                                                                               | 10      |      | 0.7  |      | - μs<br>- |

|                                         |                     |                                                                                                                                              | 11      |      | 0.9  |      |           |

| Register-Programmable<br>Minimum Period | tperiod_min         | Interval limit from V_TR rising edge to VG falling edge The clock period is based on fosc_Mcu and can be set by the 12-bit register (Note 5) |         |      | 190  |      | μs        |

| PLL Function Section                    | •                   | 1                                                                                                                                            |         |      |      |      |           |

|                                         |                     | If VG falling edge to V <sub>TH_VTR_DT</sub> interval <                                                                                      | 00      |      | 2300 |      | ns        |

| Register-Programmable PLL               | <b>t</b>            | t <sub>DEAD_PLL</sub> , VG will                                                                                                              | 01      |      | 1800 |      |           |

| Dead Time                               | tDEAD_PLL           | skipped two cycles and reset automatic                                                                                                       | 10      |      | 1300 |      |           |

|                                         |                     | tracking counter (Note 5)                                                                                                                    | 11      |      | 800  |      |           |

| Fault PLL Ratio                         | KFAULT_PLL          | If t <sub>PW M</sub> [n] > K <sub>FAULT_PLL</sub> x<br>t <sub>PW M</sub> [n-1], reset automatic<br>tracking counter (Note 5)                 |         |      | 1.25 |      |           |

| Automatic Tracking Section              |                     |                                                                                                                                              |         |      |      |      |           |

|                                         |                     | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                                                       | 00      |      | 2500 |      |           |

| Register-Programmable                   | tDEAD_TRACK         | VG falling edge to V <sub>TH_VTR_DT</sub> interval                                                                                           | 01      |      | 2000 |      | ns        |

| Auto-Tracking Dead Time                 | INEAD_I KACK        | (Note 5)                                                                                                                                     | 10      |      | 1500 |      | 113       |

| Maximum Step Time for Tracking          |                     | With respect to V <sub>REF_C</sub> (Note 5)                                                                                                  | 11<br>v |      | 1000 |      | %         |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by design.

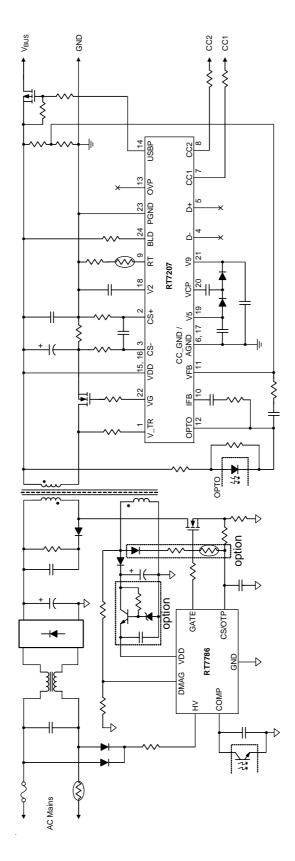

# **Typical Application Circuit**

Copyright@2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

# **Typical Operating Characteristics**

# **Application Information**

#### Constant-Voltage (CV) Loop

As shown in Figure 6, the RT7207 incorporates 2 error amplifiers (EA) inside to regulate the output voltage and current, respectively. The output voltage is determined as:

$$V_{OUT} = \left(1 + \frac{R_{FB1}}{R_{FB2}}\right) \times V_{REF\_CV}$$

For the RT7207 : The ratio of  $R_{FB1}$  /  $R_{FB2}\,$  is set as 7, and it is recommended to use  $91k\Omega$  and  $13k\Omega$  for minimizing power loss in the resistor divider.

For the RT7207L: The ratio of  $R_{FB1}$  /  $R_{FB2}$  is set as 4, and it is recommended to use  $30k\Omega$  and  $7.5k\Omega$  for better resolution of CV regulation.

Therefore, the  $V_{OUT}$  is determined by  $V_{REF\_CV}$ , the analog output from the DAC, and its digital counterpart, which is controlled by the MCU, as shown in Functional Block Diagram.

### Constant-Current (CC) Loop and Current-Sense Amplifier

The RT7207 integrates a virtually-zero input-offset-voltage current-sense amplifier with differential-mode inputs to minimize noise interference. The voltage gain of 20 or 40 can be set by the internal register. The amplified output current sense signal, sent to an ADC for A/D conversion, is monitored and processed by the MCU, and is also sent to the CC loop. The reference voltage of the CC loop is determined by V<sub>REF CC</sub> (from the DAC), which is programmed by chargers' requirements. Both the constantvoltage and constant-current compensation loops are connected together at the OPTO pin. The OPTO driver sinks current through an optocoupler and an external resistor R<sub>D</sub> from output voltage, and the optocoupler isolates the secondary side from the primary side and also provide the feedback compensation signal for the primary side. Note that for better linearity of the loop compensation range, RD should be designed to cover for operation at the minimum output voltage.

$$\frac{\left(V_{OUT\_MIN} - V_F - 0.3V\right)}{R_D} \times CTR \ \geq \ I_{COMP\_MAX}$$

CTR: Current transfer ratio of the optocoupler

V<sub>F</sub>: Forward voltage of the optocoupler

0.3V: The minimum OPTO voltage for the OPTO driver to sink 2mA.

$I_{COMP\_MAX}$ : The maximum COMP sourcing current of a traditional PWM controller in the primary side. It is a current sourced from an internal bias through a built-in pull-high resistor connected the COMP pin in the PWM controller.

Figure 6. CC and CV Loops and Current-Sense Amplifier

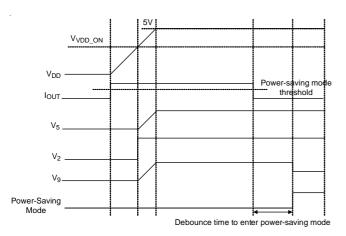

#### Power-Up Sequence

Figure 7 shows the timing diagram for the power-up sequence. When start-up, the default output is set at 5V. Once a Type-C cable is attached, the UFP will deliver voltage and current settings to the RT7207 for the MCU to decode and to program reference voltages, V<sub>REF\_CV</sub> and V<sub>REF\_CC</sub>, for the CV and CC loops, which are the analog outputs converted by the DAC. If the Type-C cable is detached, or the output current is lower than the power-saving mode threshold, which is typically programmed as 200mA, the RT7207 will enter power-saving mode, under which the RT7207 operates at ultra-low operating current and thus the total input power can be saved. If the output current increases and exceeds the power-saving mode threshold, or any input/output signal is toggled, the RT7207 will exit power-saving mode.

Figure 7. The Waveforms of the Bias Voltages during Start-Up

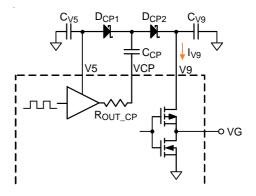

#### Internal Biases and Charge Pump

The RT7207 provides three regulated bias voltages,  $V_5$ ,  $V_2$ , and  $V_9$ . The  $V_5$  bias voltage is the output of a linear regulator powered by  $V_{DD}$ , and supplies the internal analog circuit and the charge pump driver. The  $V_2$  bias voltage is the output of a linear regulator powered by  $V_5$ , and supplies the MCU. As shown in Figure 8, the RT7207 also integrates a charge pump circuit to generate  $V_9$  to supply for the SR driver when  $V_{DD}$  is at lower levels, such as 3.3V to 5V. If the RT7207 enters power-saving mode, the charge pump driver will be disabled.

The minimum source/sink capability of charge pump driver is around 10mA at 170kHz of charge pump operating frequency  $f_{CP}$ . Bypass capacitor on the V5, V2 and V9 pins are required to minimize output ripples of the biases.

$$V_9 = V_5 \times 2 - V_{F\_DCP1} - V_{F\_DCP2} - I_{V9} \times R_{OUT\_CP}$$

When output voltage is set at lower levels (<5V),  $V_5$  will be lower, following  $V_{DD}$  by a voltage drop of a dropout voltage of the LDO. For higher  $V_9$ , a lower forward voltage for the Schottky diodes,  $D_{CP1}$  and  $D_{CP2}$ , is required.

The RT7207 provides V5 short-circuit protection against the condition that the V5, V2, or VCP pin is shorted to GND, and also provides under-voltage protection for V9. If the V9 voltage is below  $V_{V9\_SRON}$  (typical 4.5V), the SR driver will be turned off, that is, VG will be inactivated.

Figure 8. Charge Pump Circuit

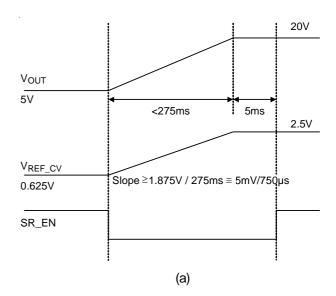

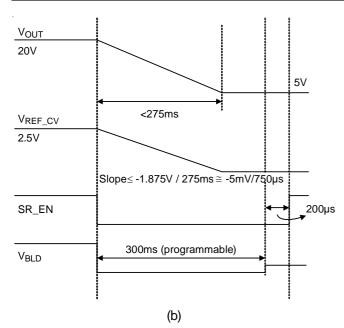

#### **Output Voltage Rises and Falls**

When the protocol is detected, the reference voltage  $V_{REF\_CV}$  can be set by the request of the UFP. Both the rise time and fall time of output voltages should be less than 275ms in accordance with the USB PD Specification, as shown in Figure 9.

During the time of  $V_{OUT}$  falling, as shown in Figure 10, the BLD driver will be turned on as a dummy load to provide an extra discharging path for the output capacitor so that  $V_{OUT}$  can be settled in a shorter duration. The designed  $R_{DUMMY}$  is as :

$$C_{OUT} \times (R_{DUMMY} + R_{L\_BLD}) \times 2 < 275 ms$$

During the time of  $V_{OUT}$  rising or falling, the SR driver will be turned off. After a firmware programmable delay time 300ms, the RT7207 will sense the load condition and may reactivate the SR driver.

Figure 9. (a) V<sub>OUT</sub> Rises. (b) V<sub>OUT</sub> Falls.

Figure 10. Application Circuit of an Active Dummy Load

#### **Temperature Sensing and Thermal Protection**

The RT7207 provides the RT pin for over-temperature protection or thermal monitoring. As shown in Figure 2, the RT pin sources a constant bias current for a remote thermal sensor of an NTC thermistor, connected from the RT pin to GND, for temperature sensing. If the RT voltage is below a programmable threshold voltage and the condition sustains for a programmable deglitch time, over-temperature protection will be triggered.

The bias current through the RT pin can be programmed as  $100\mu A$ ,  $20\mu A$ , or  $4\mu A$  by setting the internal register. With the appropriate bias current setting, linearity of temperature sensing over the temperature range of  $25^{\circ}C$

to 100°C can be improved. The RT7207 can deliver the sensed RT voltage data back to the UFP via the protocol (Vendor Defined Message), if necessary. Figure 11 shows the RT voltages vary with temperature at three different bias currents with an NTC thermistor TTC104 as an example.

Figure 11. The RT Voltages vs. Temperature at Three Bias Currents

#### **USBP Control**

The RT7207 provides an open-drain driver for controlling an external blocking P-MOSFET. Once the communication is set up with an UFP, or a  $5.1 k\Omega$  resistor at the CC1/CC2 pin of a Type-C connector of the UFP is detected, the P-MOSFET will be turned on. If  $V_{OUT}$  over-voltage condition occurs, the blocking P-MOSFET will be turned off to prevent the UFP from being damaged by the  $V_{OUT}$  over-voltage condition. If  $V_{OUT}$  is shorted to GND, the P-MOSFET will also be turned off automatically so that output power can be limited.

#### **Output Over-Voltage Protection**

As shown in the Figure 12, the RT7207 provides the OVP pin as a backup  $V_{OUT}$  over-voltage protection, in case the optocoupler of the feedback loop is malfunction due to aging. If the internal voltage related to  $V_{DD}$  is higher by the programmable threshold  $V_{VOUT\_OVP}$ , the OVP pin will be pulled low. The OVP pin voltage will be latched low until the VDD voltage drops below the VDD turn-off threshold  $V_{VDD\_OFF}$ , as shown in Figure 13.

Copyright@2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS7207-00 January 2017

www.richtek.com

Figure 12. OVP Pin Block Diagram

Figure 13. Timing Sequence of the OVP Pin Function

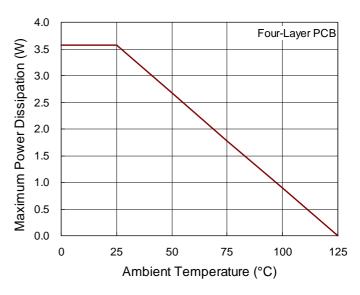

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WQFN-24L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 28°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated as below:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (28^{\circ}C/W) = 3.57W$  for a WQFN-24L 4x4 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 14 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 14. Derating Curve of Maximum Power Dissipation

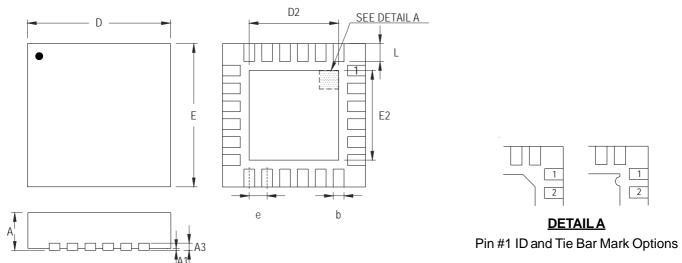

### **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol   |          | Dimensions I      | In Millimeters | Dimensions In Inches |       |  |  |

|----------|----------|-------------------|----------------|----------------------|-------|--|--|

|          |          | Min               | Min Max Min    |                      | Мах   |  |  |

|          | А        | 0.700             | 0.800          | 0.028                | 0.031 |  |  |

|          | A1       | 0.000             | 0.050          | 0.000                | 0.002 |  |  |

|          | А3       | 0.175             | 0.250          | 0.007                | 0.010 |  |  |

|          | b        | 0.180             | 0.300          | 0.007                | 0.012 |  |  |

|          | D        | 3.950             | 4.050          | 0.156                | 0.159 |  |  |

| D2       | Option 1 | 2.400             | 2.500          | 0.094                | 0.098 |  |  |

|          | Option 2 | 2.650             | 2.750          | 0.104                | 0.108 |  |  |

|          | E        | 3.950             | 4.050          | 0.156                | 0.159 |  |  |

| E2       | Option 1 | 2.400             | 2.500          | 0.094                | 0.098 |  |  |

| Option 2 |          | 2.650 2.750 0.104 |                | 0.104                | 0.108 |  |  |

|          | е        | 0.5               | 500            | 0.0                  | 20    |  |  |

|          | L        | 0.350             | 0.450          | 0.014                | 0.018 |  |  |

W-Type 24L QFN 4x4 Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS7207-00 January 2017 www.richtek.com