# **High Power Synchronous Boost Converter**

# **General Description**

The RT8540A is a high-efficiency, high-current Boost converter in all single-cell Lithium-ion / polymer battery operated products. The RT8540A maintains output current regulation by switching the internal high side and low side switch transistors. The transistor switches are pulse-width modulated at a fixed frequency of 2MHz. The high switching frequency allows the use of a small inductor and output capacitor, making the RT8540A ideally suited for small battery-powered applications. Output voltage can be set by an external resistor on the FB pin or by I<sup>2</sup>C interface.

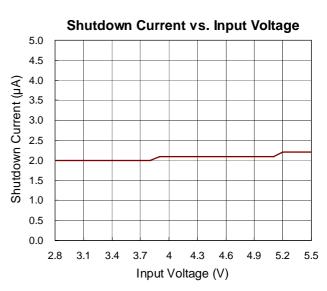

The RT8540A contains over voltage protection, over current protection and over temperature protection to prevent the device from output open circuit or short circuit condition. Built-in soft-start circuitry prevents excessive inrush current during start-up. The shutdown feature reduces quiescent current to less than  $5\mu A$ .

# **Marking Information**

0R=YM DNN 0R=: Product Code

YMDNN: Date Code

# **Features**

• Input Voltage Range: 2.8V to 5.5V

• True Load Disconnect

- Internal Synchronous Rectifier

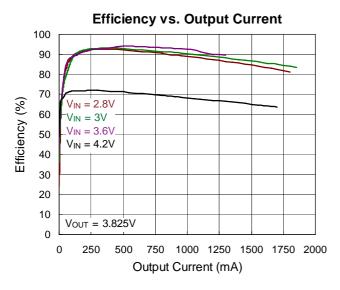

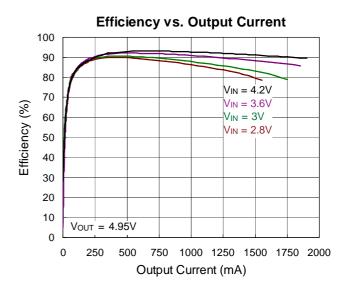

- Up to 90% Efficiency with Small Magnetics

- Current Mode PWM Operation with Internal Compensation

- Internal Soft-Start Control

- Flexible on/off Control by I2C or EN.

- Short Circuit Protection

- Input Current Limit up to 4A

- Over Voltage, Over Temperature Protection

- Shutdown Current : 2μA

- -40°C to 85°C Temperature Range

- 20-Lead WQFN Package

- RoHS Compliant and Halogen Free

# **Applications**

- Cellular Phones

- Digital Cameras

- Probable Instruments

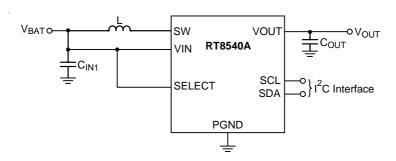

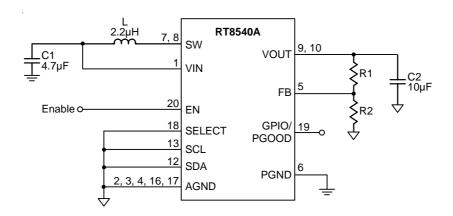

# **Simplified Application Circuit**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Ordering Information**

# RT8540A Package Type QW: WQFN-20L 4x4 (W-Type) (Exposed Pad-Option 1) Lead Plating System G: Green (Halogen Free and Pb Free)

### Note:

### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

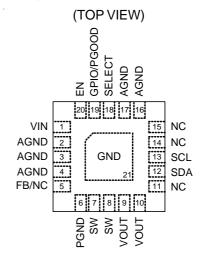

# **Pin Configurations**

WQFN-20L 4x4

# **Functional Pin Description**

| Pin No.              | Pin Name.  | Pin Function                                                                                                                                      |  |  |

|----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                    | VIN        | Power Input. Connect VIN to the power supply. Connect a $4.7\mu F$ or larger ceramic capacitor from VIN to ground as close as possible to the IC. |  |  |

| 2, 3, 4, 16, 17      | AGND       | Analog Ground. Connect AGND to GND at single point as close to the IC as possible.                                                                |  |  |

| 5                    | FB/NC      | Feedback Voltage Input. When the pin is floating, the output voltage is controlled by ${\rm I}^2{\rm C}$ interface.                               |  |  |

| 6                    | PGND       | Power Ground. Connect PGND to GND at a single point as close to the IC as possible.                                                               |  |  |

| 7, 8                 | SW         | Switch Node. Connect an inductor between SW and VIN.                                                                                              |  |  |

| 9, 10                | VOUT       | Output of the Boost Conductor. Connect a $10\mu F$ or larger ceramic capacitor from VOUT to ground as close as possible to the IC.                |  |  |

| 11, 14, 15           | NC         | No Internal Connection.                                                                                                                           |  |  |

| 12                   | SDA        | Data Signal Input for $I^2C$ . Open drain output, connect a $10k\Omega$ pull-up resistor.                                                         |  |  |

| 13                   | SCL        | Clock Signal Input for $I^2C$ . Open drain output, connect a $10k\Omega$ pull-up resistor.                                                        |  |  |

| 18                   | SELECT     | Select IC I <sup>2</sup> C/EN Control.  SELECT = HIGH. I <sup>2</sup> C control.  SELECT = LOW. EN control.                                       |  |  |

| 19                   | GPIO/PGOOD | General Purpose Input Output Input or Power Good Indicator Output.                                                                                |  |  |

| 20                   | EN         | Enable Control Input for non I <sup>2</sup> C control Version (Active High).                                                                      |  |  |

| 21 (Exposed Pad) GND |            | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                       |  |  |

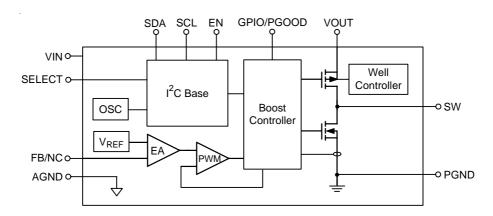

# **Function Block Diagram**

# **Operation**

### **Boost Controller**

The core of the Boost regulator with normal operations and provides protection functions like UVLO, OCP, OVP, OTP.

### osc

Generates 2MHz clock.

# **VREF**

Generates the reference voltage for Error-amp and other bias circuit.

### EΑ

Error amplifier generates COMP signal by the difference between FB and VREF.

### **PWM**

PWM comparator compares COMP signal and current feedback signal to initial PWM signal.

### I<sup>2</sup>C BASE

Digital logic and registers part.

### **Well Controller**

It compares VIN and VOUT, the higher one will be the big P-MOSFET well potential.

# Absolute Maximum Ratings (Note 1)

| • Supply Voltage, VIN                                                       | -0.3V to 6V    |

|-----------------------------------------------------------------------------|----------------|

| Boost Output Voltage, VOUT                                                  | -0.3V to 6.5V  |

| • Switching Voltage, SW                                                     | -0.3V to 6.5V  |

| • SCL, SDA, EN, GPIO/PGOOD, FB/NC, SELECT                                   | -0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WQFN-20L 4x4                                                                | · 3.57W        |

| Package Thermal Resistance (Note 2)                                         |                |

| WQFN-20L 4x4, $\theta_{JA}$                                                 | · 28°C/W       |

| WQFN-20L 4x4, $\theta_{JC}$                                                 | · 7°C/W        |

| • Junction Temperature                                                      | · 150°C        |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C        |

| Storage Temperature Range                                                   | -65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      | · 2kV          |

| MM (Machine Model)                                                          | · 200V         |

| CDM (Charge Device Model)                                                   | · 500V         |

|                                                                             |                |

# **Recommended Operating Conditions** (Note 4)

| • | <ul> <li>Input voltage, viiv</li> </ul> |   | 2.87 to 5.57 |  |

|---|-----------------------------------------|---|--------------|--|

|   |                                         | _ |              |  |

$\bullet \ \ \text{Junction Temperature Range------} \ \ -40^{\circ}\text{C to } 125^{\circ}\text{C}$

• Ambient Temperature Range ----- ----- -40°C to 85°C

# **Electrical Characteristics**

$(V_{IN} = 3.6V, C_{IN} = 4.7\mu F, C_{OUT} = 10\mu F, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter Symbol     |                       | Test Conditions                         | Min    | Тур  | Max    | Unit |

|----------------------|-----------------------|-----------------------------------------|--------|------|--------|------|

| Power Supply         | •                     |                                         | •      |      |        |      |

| Input Voltage Range  | V <sub>IN</sub>       |                                         | 2.8    |      | 5.5    | V    |

| UVLO                 | UV                    | VIN Falling                             |        | 2.4  |        | V    |

| VIN Supply Current   | IQ                    | I <sub>OUT</sub> = 0A                   |        | 590  | 700    | μΑ   |

| VIN Shutdown Current | I <sub>SHDN</sub>     | V <sub>IN</sub> = 5V                    |        | 1    | 5      | μΑ   |

| Output               |                       |                                         |        |      |        |      |

| Output Voltage Range | V <sub>OUT</sub>      | $I^2$ C Control, OV[3:0] = 0000 to 1111 | 3.825  | -    | 5.45   | V    |

| Feedback Voltage     | V <sub>FB</sub>       | EN Control                              | 0.9702 | 0.99 | 1.0098 | V    |

| Oscillator and Timer |                       |                                         | ,      |      | ,      |      |

| Operating Frequency  | fosc                  |                                         | 1.6    | 2    | 2.4    | MHz  |

| Maximum Duty Cycle   | D <sub>MAX</sub>      |                                         | 70     |      |        | %    |

| Power Switch         |                       |                                         |        |      |        |      |

| N-MOSFET Ron         | R <sub>DS(ON)_N</sub> | V <sub>OUT</sub> = 3.6V                 |        | 90   |        | mΩ   |

| P-MOSFET Ron         | R <sub>DS(ON)_P</sub> | V <sub>OUT</sub> = 3.6V                 |        | 110  |        | mΩ   |

| Leakage into SW      | I <sub>LKG_SW</sub>   | V <sub>OUT</sub> = 0V, EN = LOW         |        | 0.3  | 4      | μΑ   |

| Parameter                   | Symbol               | Test Conditions                                         | Min          | Тур  | Max   | Unit |

|-----------------------------|----------------------|---------------------------------------------------------|--------------|------|-------|------|

| Protection Function         |                      |                                                         |              |      |       |      |

| N-MOSFET Current Limit      | IOCP                 | V <sub>OUT</sub> = 5V                                   | 3.6          | 4    | 4.4   | Α    |

|                             |                      | VOUT Rising, 0000 ≤ OV[3:0] ≤ 0100                      | 4.464        | 4.65 | 4.836 | V    |

| Over Voltage Protection     | V <sub>OVP</sub>     | VOUT Rising, $0101 \le OV[3:0] \le 1111$ , SELECT = LOW | 5.568        | 5.8  | 6.032 | V    |

| OVP Hysteresis              | V <sub>OVP_HYS</sub> | VOUT Falling                                            |              | 150  |       | mV   |

| Thermal Shutdown            | T <sub>SD</sub>      |                                                         |              | 160  |       | °C   |

| Thermal Shutdown Hysteresis | T <sub>SD_HYS</sub>  |                                                         |              | 20   |       | °C   |

| Logic Control               |                      |                                                         |              |      |       |      |

| SELECT Logic High           | V <sub>SELH</sub>    |                                                         | 1.4          |      |       | V    |

| SELECT Logic Low            | V <sub>SELL</sub>    |                                                         |              |      | 0.4   | V    |

| EN Logic High               | V <sub>ENLH</sub>    |                                                         | 1.4          |      |       | V    |

| EN Logic Low                | V <sub>ENLL</sub>    |                                                         |              |      | 0.4   | V    |

| SCL Logic High              | Vsclh                |                                                         | 1.4          |      |       | V    |

| SCL Logic Low               | V <sub>SCLL</sub>    |                                                         |              |      | 0.4   | V    |

| SDA Logic High              | V <sub>SDAH</sub>    |                                                         | 1.4          |      |       | V    |

| SDA Logic Low               | V <sub>SDAL</sub>    |                                                         |              |      | 0.4   | V    |

| GPIO Output Voltage High    | Voh_gpio             | DIR = 1, GPIOTYPE = 0, I <sub>OH</sub> = 8mA            | VIN<br>- 0.4 |      |       | ٧    |

| GPIO Output Voltage Low     | V <sub>OL_GPIO</sub> | DIR = 1, I <sub>OL</sub> = 5mA                          |              |      | 0.3   | V    |

| EN Pull Low Resistance      | R <sub>EN</sub>      |                                                         |              | 400  |       | kΩ   |

| SELECT Pull Low Resistance  | R <sub>SEL</sub>     |                                                         |              | 400  |       | kΩ   |

| Clock Frequency of SCL      | f <sub>SCL</sub>     |                                                         |              |      | 400   | kHz  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

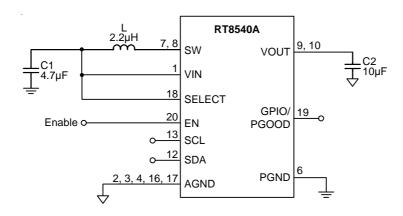

# **Typical Application Circuit**

Figure 1. For I<sup>2</sup>C Control

Figure 2. For EN Control

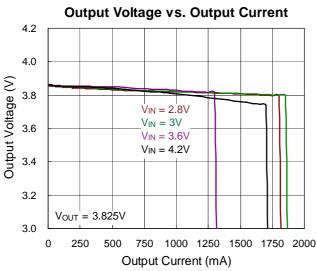

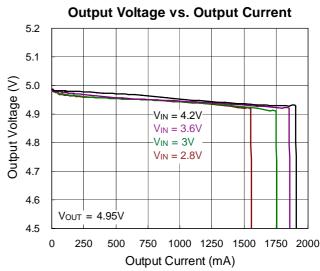

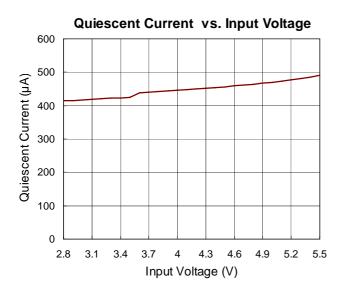

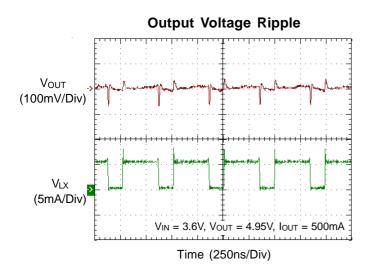

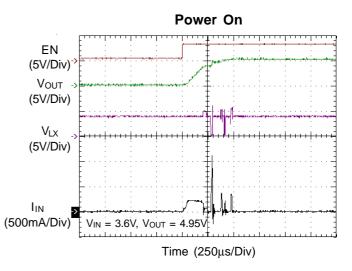

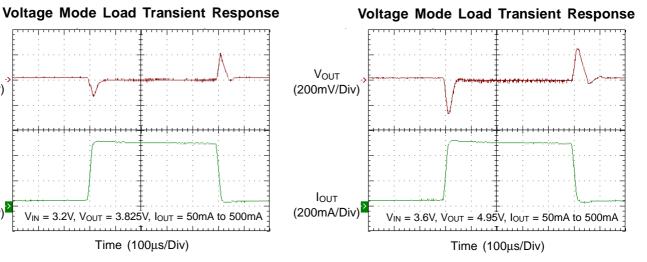

# **Typical Operating Characteristics**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# $V_{\text{OUT}}$ (200mV/Div)

Time (100µs/Div)

$V_{IN} = 3.2V$ ,  $V_{OUT}$

lout

(200mA/Div)

# **Application Information**

The RT8540A is a high-efficiency, high-current Boost converter in all single-cell Lithium-ion/polymer battery operated products. The RT8450A provides the ability to regulate the input voltage that is higher than the designed output voltage with its down-conversion mode. The RT8450A turns off its down-conversion mode automatically once the input voltage falls to approximately 200mV below the output voltage.

### Soft-Start

The RT8540A employs a soft-start feature to limit the inrush current. The soft-start circuit prevents the excessive inrush current and input voltage droop. The soft-start clamps the input inrush current for a typical period of  $400\mu s$ .

# **Input UVLO**

The input operating voltage range is from 2.8V to 5.5V. The RT8540A provides an Under Voltage Lockout (UVLO) function to prevent it from unstable issue when startup. The UVLO threshold of input rising voltage is set at 2.3V typically with a hysteresis of 200mV.

# **Over Voltage Protection (Open Circuit)**

The RT8540A provides an internal over voltage protection to limit its output voltage. The OVP function prevents the RT8540A from damaging while open circuit condition is occurred.

### **Over Current Protection**

The RT8540A provides an internal over current protection to limit its output current. The typical value of the maximum current is 4A.

### **Over Temperature Protection**

The RT8540A provides an over temperature protection to prevent the IC from overheating. When the junction temperature of the RT8540A rises above 160°C, the OTP function will be triggered and then the regulator will be shutdown. The OTP comes with a hysteresis of 20°C. Once the temperature is reduced below the over temperature protection threshold by 20°C, the output will soft-start again.

### **Inductor Selection**

The RT8540A adopts fixed frequency PWM control architecture. For stable operation and the 2MHz high switching frequency, it is recommended to use a  $2.2\mu H$  inductor. Small size and high efficiency are the major concerns for portable device, so the inductor should have low core loss at 2MHz and low DCR for better efficiency.

### **Capacitor Selection**

Input and output ceramic capacitors of  $10\mu F$  are recommended for RT8540A applications. For better voltage filtering, ceramic capacitors with low ESR are recommended. The best performance of the RT8540A can be achieved by using the capacitor of large capacitance. X5R and X7R types are suitable because of their wider voltage and temperature ranges.

### **Enable Selection Function**

There is a SELECT pin on the RT8450A which provides the selection of I<sup>2</sup>C enable or non-I<sup>2</sup>C enable. By setting the SELECT pin "Low", the IC enters non-I<sup>2</sup>C control operation. The IC will be enable when the EN pin is set "High", and the output is regulated by connecting the FB pin to VOUT with the dividing resistors. The VOUT is set between 3.825V and 5.45V. Setting the SELECT pin "High", the IC enters I<sup>2</sup>C control operation. The RT8450A provides an integrated software control bit ENVM bit to force the converter to enter normal operation. Under this condition, the output will be regulated by integrated software control bits OV[3:0].

| SELECT | EN | ENVM | Operation description |

|--------|----|------|-----------------------|

| 0      | 0  | 0    | Shutdown              |

| 0      | 1  | 0    | Enable                |

| 1      | Х  | 0    | Shutdown              |

| 1      | Х  | 1    | Enable                |

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Register Map

# Table 1. 0x04 Error Flag

| Description | PG                                                                                                                                                                                                                                                                                                                                                                                 | FREE                                                         | ОТР | FREE | FREE | Vout Short | FR | EE |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|------|------|------------|----|----|--|

| Bits        | D7                                                                                                                                                                                                                                                                                                                                                                                 | D6                                                           | D5  | D4   | D3   | D2         | D1 | D0 |  |

| Memory      | R/W                                                                                                                                                                                                                                                                                                                                                                                | R                                                            | R   | R    | R    | R          | R  | R  |  |

| Default     | 0                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                            | 0   | 0    | 0    | 0          | 0  | 0  |  |

| PG          | Power Good bit. In write mode, this bit selects the functionality of the GPIO/PG output. 0 : PG signal is routed to the GPIO port. 1 : GPIO PORT VALUE bit is routed to the GPIO port. In read mode, this bit indicates the output voltage conditions. 0 : The converter is not operating within the voltage regulation limits. 1 : The output voltage is within it nominal value. |                                                              |     |      |      |            |    |    |  |

| OTP         | Thermal shu                                                                                                                                                                                                                                                                                                                                                                        | Thermal shutdown tripped Indicator flag reset after readout. |     |      |      |            |    |    |  |

| VOUT Short  | VOUT Shor                                                                                                                                                                                                                                                                                                                                                                          | VOUT Short error flag reset after readout.                   |     |      |      |            |    |    |  |

# Table 2. 0x05

| Description | RESET                                                                                                    | ENPSM                                                                                         | DIR | GPIO | GPIOTYPE |    | FREE |    |  |  |

|-------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|------|----------|----|------|----|--|--|

| Bits        | D7                                                                                                       | D6                                                                                            | D5  | D4   | D3       | D2 | D1   | D0 |  |  |

| Memory      | R/W                                                                                                      | R/W                                                                                           | R/W | R/W  | R/W      | R  | R    | R  |  |  |

| Default     | 0                                                                                                        | 1                                                                                             | 1   | 0    | 1        | 0  | 0    | 0  |  |  |

| RESET       | 0 : Normal                                                                                               | Register Reset bit. 0: Normal operation. 1: Default values are set to all internal registers. |     |      |          |    |      |    |  |  |

| ENPSM       | Enable/Disable Power-Save Mode bit.  0 : Power-save mode disabled.  1 : Power-save mode enabled.         |                                                                                               |     |      |          |    |      |    |  |  |

| DIR         | 0 : GPIO co                                                                                              | GPIO Direction bit. 0 : GPIO configured as input. 1 : GPIO configured as output.              |     |      |          |    |      |    |  |  |

| GPIO        |                                                                                                          | GPIO Port Value. This bit contains the GPIO port Value.                                       |     |      |          |    |      |    |  |  |

| GPIOTYPE    | GPIO Port Type. 0 : GPIO is configured as push-pull output. 1 : GPIO is configured as open-drain output. |                                                                                               |     |      |          |    |      |    |  |  |

# Table 3. 0x06 Output Voltage

| Description | ENVM                                                                                                                                                                                                                                      |                                  | FREE |           |     | OV  | [3:0] |     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-----------|-----|-----|-------|-----|

| Bits        | D7                                                                                                                                                                                                                                        | D6                               | D5   | D4        | D3  | D2  | D1    | D0  |

| Memory      | R/W                                                                                                                                                                                                                                       | R                                | R    | R         | R/W | R/W | R/W   | R/W |

| Default     | 0                                                                                                                                                                                                                                         | 0                                | 0    | 0         | 1   | 0   | 0     | 1   |

| OV[3:0]     | Output Volta<br>0000 : 3.825<br>0001 : 3.95V<br>0010 : 4.075<br>0011 : 4.2V<br>0100 : 4.325<br>0101 : 4.45V<br>0110 : 4.575<br>0111 : 4.7V<br>1000 : 4.825<br>1001 : 4.95V<br>1010 : 5.075<br>1011 : 5.2V<br>1100 : 5.325<br>1101 to 1111 | V<br>V<br>V<br>V<br>V<br>: 5.45V |      | Control : |     |     |       |     |

| ENVM        | Enable Volta<br>0 : Shutdowi<br>1 : Normal o                                                                                                                                                                                              | n mode.                          |      |           |     |     |       |     |

# **Register Summary**

Address: 0110011x

| Register | Description | PG    | FREE  | ОТР  | FREE | FREE     | Vout<br>Short | FR   | EE   |

|----------|-------------|-------|-------|------|------|----------|---------------|------|------|

|          | Bits        | Bit7  | Bit6  | Bit5 | Bit4 | Bit3     | Bit2          | Bit1 | Bit0 |

| 0x04     | Memory      | R/W   | R     | R    | R    | R        | R             | R    | R    |

|          | Default     | 0     | 0     | 0    | 0    | 0        | 0             | 0    | 0    |

|          | Description | RESET | ENPSM | DIR  | GPIO | GPIOTYPE |               | FREE |      |

| 0x05     | Bits        | Bit7  | Bit6  | Bit5 | Bit4 | Bit3     | Bit2          | Bit1 | Bit0 |

| 0.000    | Memory      | 0     | 1     | 1    | 0    | 1        | 0             | 0    | 0    |

|          | Default     | R/W   | R/W   | R/W  | R/W  | R/W      | R             | R    | R    |

|          | Description | ENVM  |       | FREE |      |          | OV [3         | 3:0] |      |

| 0,406    | Bits        | Bit7  | Bit6  | Bit5 | Bit4 | Bit3     | Bit2          | Bit1 | Bit0 |

| 0x06     | Memory      | R/W   | R     | R    | R    | R/W      | R/W           | R/W  | R/W  |

|          | Default     | 0     | 0     | 0    | 0    | 1        | 0             | 0    | 1    |

Copyright ©2013 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

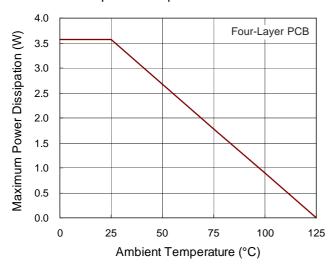

### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-20L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 28°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (28^{\circ}C/W) = 3.57W$$

for WQFN-20L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed T<sub>J(MAX)</sub> and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 3. Derating Curve of Maximum Power Dissipation

### **Layout Consideration**

For the best performance of the RT8540A, following PCB layout guidelines should be strictly followed.

- ▶ The PGND of the IC should be connected to the ground plane of the PCB

- > The output bypass capacitor should be placed as close to the IC as possible

- The trace lengths from the IC to the inductor, input capacitor and the output capacitor must be kept as short, direct and wide as possible.

- ▶ C<sub>IN</sub> and C<sub>OUT</sub> of the RT8540A should be placed as close as possible and connected to PGND of the IC.

- ▶ It is recommended to add additional PCB exposed pad area for the flash LEDs for maximized heat-sinking ability. This is necessary for high current application and long flash duration application.

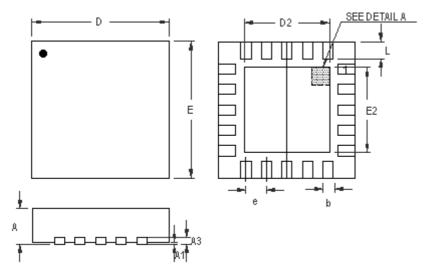

# **Outline Dimension**

**DETAIL A**Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol |          | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|----------|------------|----------------|----------------------|-------|--|

|        |          | Min        | Max            | Min                  | Max   |  |

|        | Α        | 0.700      | 0.800          | 0.028                | 0.031 |  |

|        | A1       | 0.000      | 0.050          | 0.000                | 0.002 |  |

|        | A3       | 0.175      | 0.250          | 0.007                | 0.010 |  |

|        | b        | 0.150      | 0.300          | 0.006                | 0.012 |  |

|        | D        | 3.900      | 4.100          | 0.154                | 0.161 |  |

| Da     | Option 1 | 2.650      | 2.750          | 0.104                | 0.108 |  |

| D2     | Option 2 | 2.100      | 2.200          | 0.083                | 0.087 |  |

|        | E        | 3.900      | 4.100          | 0.154                | 0.161 |  |

|        | Option 1 | 2.650      | 2.750          | 0.104                | 0.108 |  |

| E2     | Option 2 | 2.100      | 2.200          | 0.083                | 0.087 |  |

|        | е        | 0.5        | 500            | 0.0                  | )20   |  |

| L      |          | 0.350      | 0.450          | 0.014                | 0.018 |  |

W-Type 20L QFN 4x4 Package

# **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.