## Mini Analog Baseband Power Management IC

## **General Description**

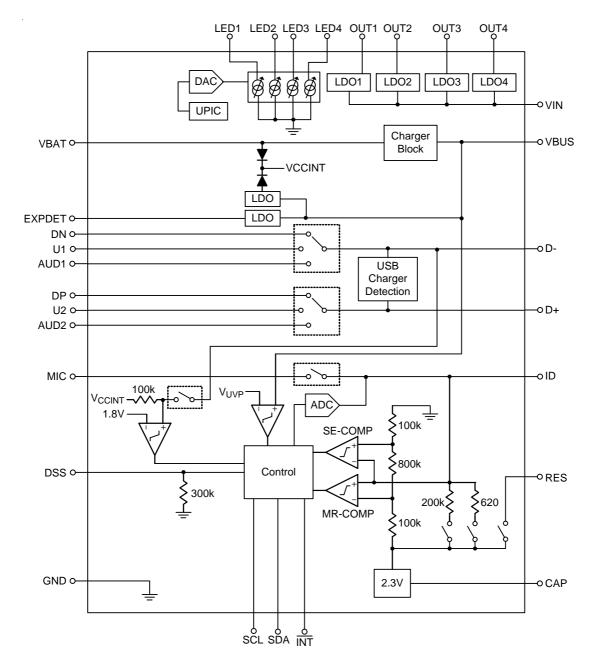

The RT8966H is an analog subsystem which includes a linear charger, 4 LDOs, a 4-CH current source, and a multiplexer for USB, UART, microphone, stereo and audio on a single mini/micro USB connector.

The RT8966H adopts an  $I^2C$  bus for control and uses an internal method to determine the connected device.

The USB input provides high speed USB connection. The audio inputs feature negative rail signal operation to realize simple DC coupled headset speakers. The RT8966H provides an internal device detection method by using the USB ID signal pin and the VBUS voltage. The resistor values and VBUS voltage determine the unique detection method of each accessory. The host microprocessor adopts  $I^2C$  to control the switch position and read the results of the accessory detection. The RT8966H can also detect USB chargers, including dedicated chargers (D+/D- shorted) and high, power, host/hub chargers.

The RT8966H has a linear charger with maximum 1A current capability. The charging current and end of charge current can be controlled by  $I^2C$  interface. It also provides a 50mA LDO to support the power of the peripheral circuit. In factory mode, the RT8966H provides 4.35V/2.3A power to support system operation.

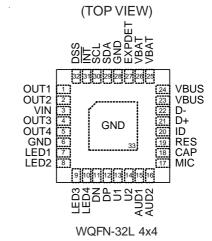

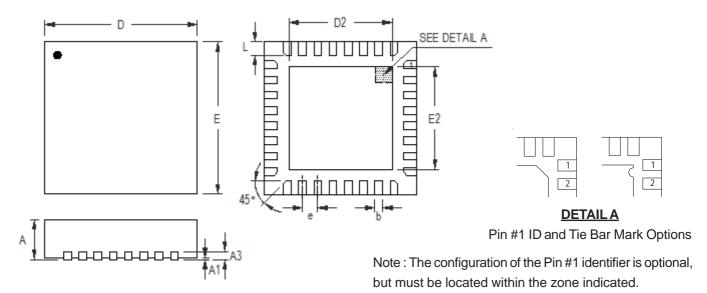

The RT8966H is available in a thin WQFN-32L 4x4 package.

## **Ordering Information**

RT8966H

Package Type

QW : WQFN-32L 4x4 (W-Type)

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## Features

- Hi-Speed USB Operation

- Interrupt for Device Insertion and Removal

- Interrupt for SEND/END Button Detection

- Interrupt for Protection Function

- Low Power Microphone Standby Mode

- Default Startup Mode for Factory Support

- Negative Rail Audio Signal Paths

- Internal LDO for Low Noise Microphone Bias

- 28V Maximum Rating for DC Adapter

- Internal Integrated Power MOSFETs of Charger

- Support 4.35V/2.3A Factory Mode

- I<sup>2</sup>C Controlled Interface

- 4 Current Sources with 32-Steps Current Setting

- 4 LDOs with Programmable Output Voltage

- Thin 32-Lead WQFN Package

- RoHS Compliant and Halogen Free

## **Applications**

- Cellular Phone

- Smart Handheld Device

## **Marking Information**

## **Pin Configurations**

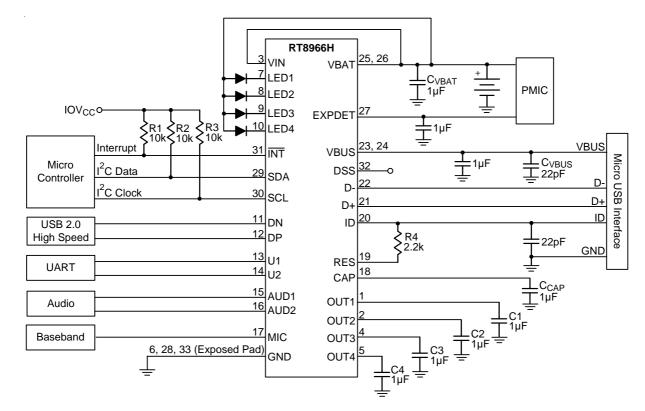

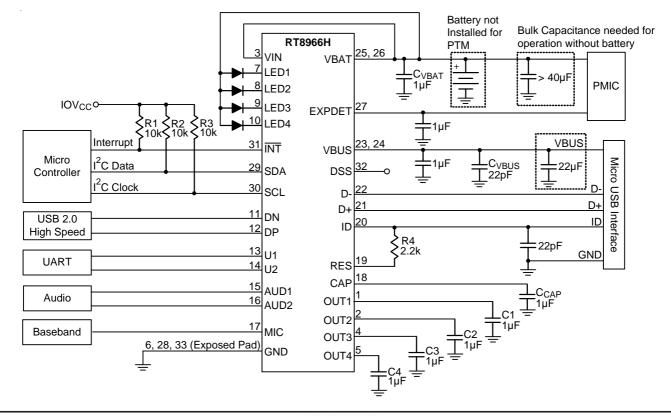

## **Typical Application Circuit**

Typical Application Circuit with Battery Installed :

Typical Application Circuit for Factory Mode with no Battery Installed :

## **Functional Pin Description**

|                            | Description |                                                                                                                                              |  |  |  |  |

|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.                    | Pin Name    | Pin Function                                                                                                                                 |  |  |  |  |

| 1                          | OUT1        | LDO1 Output Voltage.                                                                                                                         |  |  |  |  |

| 2                          | OUT2        | LDO2 Output Voltage.                                                                                                                         |  |  |  |  |

| 3                          | VIN         | LDO Input Power Supply.                                                                                                                      |  |  |  |  |

| 4                          | OUT3        | LDO3 Output Voltage.                                                                                                                         |  |  |  |  |

| 5                          | OUT4        | LDO4 Output Voltage.                                                                                                                         |  |  |  |  |

| 6, 28,<br>33 (Exposed Pad) | GND         | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                  |  |  |  |  |

| 7                          | LED1        | LED1 Current Source Output.                                                                                                                  |  |  |  |  |

| 8                          | LED2        | LED2 Current Source Output.                                                                                                                  |  |  |  |  |

| 9                          | LED3        | LED3 Current Source Output.                                                                                                                  |  |  |  |  |

| 10                         | LED4        | LED4 Current Source Output.                                                                                                                  |  |  |  |  |

| 11                         | DN          | USB Inout1 for D–.                                                                                                                           |  |  |  |  |

| 12                         | DP          | USB Input2 for D+.                                                                                                                           |  |  |  |  |

| 13                         | U1          | UART/USB Full Speed Input1.                                                                                                                  |  |  |  |  |

| 14                         | U2          | UART/USB Full Speed Input2.                                                                                                                  |  |  |  |  |

| 15                         | AUD1        | Stereo Audio Input1. (Negative rail capable).                                                                                                |  |  |  |  |

| 16                         | AUD2        | Stereo Audio Input2. (Negative rail capable).                                                                                                |  |  |  |  |

| 17                         | MIC         | Microphone Input.                                                                                                                            |  |  |  |  |

| 18                         | CAP         | Internal LDO Output. Connect a $1\mu$ F ceramic (X5R, X7R or better) capacitor between CAP and GND. Do not use CAP to power other circuitry. |  |  |  |  |

| 19                         | RES         | External Microphone Bias Resistor. Connect a resistor (typical $2.2k\Omega$ ) between RES and UID line.                                      |  |  |  |  |

| 20                         | ID          | USB ID Input. Connect to ID on mini/micro USB connector.                                                                                     |  |  |  |  |

| 21                         | D+          | Common Output2.Connect to D+ on min/micro USB connector.                                                                                     |  |  |  |  |

| 22                         | D-          | Common Output1.connect to D- on mini/micro USB connector.                                                                                    |  |  |  |  |

| 23, 24                     | VBUS        | USB VBUS Input. Provides power for internal circuitry in the case $V_{BAT} < V_{BUS}$ and used to sense presence of voltage on USB VBUS.     |  |  |  |  |

| 25, 26                     | VBAT        | Power Supply Input. Connect to Li-ion battery or other voltage source.                                                                       |  |  |  |  |

| 27                         | EXPDET      | LDO Output (4.9V). This pin provides 50mA output current.                                                                                    |  |  |  |  |

| 29                         | SDA         | I <sup>2</sup> C Serial Data Input/Output. Connect to an external pull up resistor.                                                          |  |  |  |  |

| 30                         | SCL         | I <sup>2</sup> C Serial Clock Input. Connect to an external pull up resistor.                                                                |  |  |  |  |

| 31                         | INT         | Interrupt Output-Open Drain. Connect to an external pull up resistor.                                                                        |  |  |  |  |

| 32                         | DSS         | Multiple Use Pin. Used to set Default Startup mode based on dc voltage when power is applied.                                                |  |  |  |  |

## **Function Block Diagram**

## Absolute Maximum Ratings (Note 1)

| • VBUS                                         | -0.3V to 28V                      |

|------------------------------------------------|-----------------------------------|

| All Other Inputs                               | -0.3V to (V <sub>IN</sub> + 0.3V) |

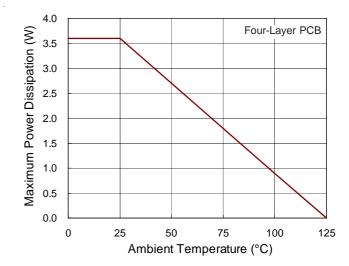

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                   |

| WQFN-32L 4x4                                   | 3.59W                             |

| Package Thermal Resistance (Note 2)            |                                   |

| WQFN-32L 4x4, θ <sub>JA</sub>                  | 27.8°C/W                          |

| WQFN-32L 4x4, $\theta_{JC}$                    | 7°C/W                             |

| Junction Temperature                           | 150°C                             |

| Lead Temperature (Soldering, 10 sec.)          | 260°C                             |

| Storage Temperature Range                      | –65°C to 150°C                    |

| ESD Susceptibility (Note 3)                    |                                   |

| HBM (Human Body Model)                         | 2kV                               |

| MM (Machine Model)                             | 200V                              |

## Recommended Operating Conditions (Note 4)

| Battery Supply Voltage Range, VBAT | 2.8V to 5.5V   |

|------------------------------------|----------------|

| USB Supply Voltage Range, VBUS     | 4.3V to 6.7V   |

| Junction Temperature Range         | –40°C to 125°C |

| Ambient Temperature Range          | –40°C to 85°C  |

## **Electrical Characteristics**

(V<sub>BAT</sub> = 3.7V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                     | Symbol               | ٢                                                                                | Test Conditions                   | Min | Тур  | Max | Unit              |  |  |

|-------------------------------|----------------------|----------------------------------------------------------------------------------|-----------------------------------|-----|------|-----|-------------------|--|--|

| DC Characteristics            |                      |                                                                                  |                                   |     |      |     |                   |  |  |

| VBUS OVP Threshold<br>Voltage | Vovp                 |                                                                                  |                                   | 6.7 | 6.9  | 7.1 | V                 |  |  |

| VBUS UVP Threshold Voltage    | VUVP                 |                                                                                  |                                   | 3.5 | 3.7  | 3.9 | V                 |  |  |

| OTP                           |                      | (Note 5)                                                                         |                                   |     | 135  |     | °C                |  |  |

| OTP Hysteresis                |                      | (Note 5)                                                                         |                                   |     | 10   |     | °C                |  |  |

| Internal Switch               | VSWPOS               | (Note 5)                                                                         |                                   |     | 3.4  |     | V                 |  |  |

| Supplies                      | Vswneg               | (Note 5)                                                                         |                                   |     | -1.9 |     |                   |  |  |

| VBAT UVLO                     | VUVLO_BAT            |                                                                                  |                                   | 2.1 | 2.5  | 2.8 | V                 |  |  |

|                               |                      | $\sqrt{2} = 2 = 2 = 1$                                                           | $I^2C$ bit : $V_{LDO} = 0$        | 2.5 | 2.6  | 2.7 | V                 |  |  |

| ID LDO Voltage                | Vldo                 | VBAT = 3.5V                                                                      | $I^2C$ bit : V <sub>LDO</sub> = 1 | 2.2 | 2.3  | 2.4 | v                 |  |  |

| ID LDO PSRR                   | PSRR <sub>LDO</sub>  | VLDO = 1, $V_{BAT}$ = 3.3 ± 0.2V, f = 217Hz,<br>I <sub>ID</sub> = 100µA (Note 5) |                                   |     | 90   |     | dB                |  |  |

| ID LDO Noise                  | N <sub>LDO</sub>     | $ID_2P2 = 1$ , MICLP = 0, f = 400Hz to 4kHz,<br>$I_{LOAD} = 100\mu A$ (Note 5)   |                                   |     | 5    |     | μV <sub>RMS</sub> |  |  |

| VBAT Supply PSRR              | PSRR <sub>VBAT</sub> |                                                                                  |                                   |     | 80   |     | dB                |  |  |

| Parameter                                                  | Symbol                | Test Conditions                                                                                                                                                                                                         | Min  | Тур | Max  | Unit  |

|------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| VBAT Leakage Current                                       | Ivbat_l               | $\label{eq:VBAT} \begin{array}{l} V_{BAT} = 4.5 V,  V_{BUS} = 0 V,  CP\_EN = 0, \\ ADCEN = 0,  SEMREN = 0;  ID\_200 = 0, \\ ID\_620 = 0,  ID\_2P2 = 0,  CHG\_OFF = 1, \\ CHG\_EN = 0,  SCL = 0,  SDA = 0 \end{array}$   |      | 10  | 15   | μA    |

| VBAT Supply Current                                        | IVBAT_S               | $V_{BAT} = 4.5V, V_{BUS} = 0V, V_{ID} = 0V,$<br>$CP_EN = 1 \text{ and either ADCEN} = 1 \text{ or}$<br>$SEMREN = 1, ID_620 = 0, ID_2P2 = 0,$<br>$D_200 = 0, CHG_OFF = 1, CHG_EN = 0$                                    |      | 44  |      | μΑ    |

| VBUS Supply Current                                        | I <sub>VBUS</sub>     | $\label{eq:bulk} \begin{array}{l} V_{BUS} = 5V,  V_{BAT} = 4.5V,  V_{ID} = 0V, \\ CP\_EN = 1,  either  ADCEN = 1  or \\ SEMREN = 1,  ID\_2P2 = 0,  ID\_620 = 0 \\ CHG\_OFF = 1,  CHG\_EN = 0,  ID\_200 = 0 \end{array}$ |      | 168 | 211  | μA    |

| D- Pull up Resistor                                        | R <sub>D-DET</sub>    | $V_{D-} = 0V$                                                                                                                                                                                                           | 63   | 106 | 332  | kΩ    |

| D- Comparator Threshold                                    | Vd-det                |                                                                                                                                                                                                                         | 0.86 | 1.8 | 2.83 | V     |

| Default Startup Switch<br>Position Comparator<br>Threshold | V <sub>DSP</sub>      | Measured at IC                                                                                                                                                                                                          |      | 1   |      | V     |

| Default Startup Switch<br>Position Pull down<br>Resistor   | R <sub>DSP</sub>      | Measured at IC                                                                                                                                                                                                          | 130  | 273 | 660  | kΩ    |

| Microphone Removal<br>Threshold                            | V <sub>MRCOMP</sub>   | In Percent of LDO voltage                                                                                                                                                                                               | 85   |     | 95   | %     |

| SEND/END Threshold                                         | V <sub>SECOMP</sub>   | In Percent of LDO voltage                                                                                                                                                                                               | 5    |     | 15   | %     |

| VDAT_SRC Voltage                                           | Vdat_src              | With IDAT_SRC = 0 to $200\mu$ A                                                                                                                                                                                         | 0.5  |     | 0.7  | V     |

| VDAT_REF Voltage                                           | V <sub>DAT_REF</sub>  |                                                                                                                                                                                                                         | 0.25 |     | 0.4  | V     |

| VLGC Voltage                                               | V <sub>LGC</sub>      |                                                                                                                                                                                                                         | 0.8  |     | 2    | V     |

| IDATA_SINK Current                                         | I <sub>DAT_SINK</sub> | May be a resistance if desired                                                                                                                                                                                          | 50   |     | 150  | μA    |

| IDPU1 Resistance                                           | RIDPU1                |                                                                                                                                                                                                                         |      | 200 |      | kΩ    |

| IDPU2 Resistance                                           | R <sub>IDPU2</sub>    |                                                                                                                                                                                                                         |      | 620 |      | Ω     |

| RCD Resistance                                             | R <sub>CD</sub>       |                                                                                                                                                                                                                         | 200  |     | 600  | kΩ    |

|                                                            |                       | GND                                                                                                                                                                                                                     |      |     | 5    |       |

|                                                            |                       | R1                                                                                                                                                                                                                      |      | 24  |      |       |

|                                                            |                       | R2                                                                                                                                                                                                                      |      | 56  |      |       |

|                                                            |                       | R3                                                                                                                                                                                                                      |      | 100 |      |       |

|                                                            |                       | R4                                                                                                                                                                                                                      |      | 130 |      |       |

| ADC Detection Resistors                                    | R <sub>ADC</sub>      | R5                                                                                                                                                                                                                      |      | 180 |      | kΩ    |

|                                                            | TADC                  | R6                                                                                                                                                                                                                      |      | 240 |      | 112.2 |

|                                                            |                       | R7                                                                                                                                                                                                                      |      | 330 |      |       |

|                                                            |                       | R8                                                                                                                                                                                                                      |      | 430 |      |       |

|                                                            |                       | R9                                                                                                                                                                                                                      |      | 620 |      |       |

|                                                            |                       | R10                                                                                                                                                                                                                     |      | 910 |      |       |

|                                                            |                       | Open                                                                                                                                                                                                                    | 1600 |     |      |       |

## RT8966H

| Parameter                               | Symbol                            | Test Conditions                                                                                                                          | Min                | Тур | Max                | Unit |

|-----------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

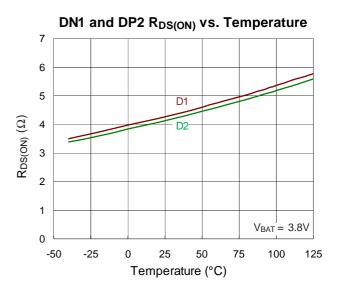

| USB Analog Switch (                     | -                                 |                                                                                                                                          |                    | - • |                    |      |

| Analog Signal Danga                     |                                   | CP_EN = 0                                                                                                                                | 0                  |     | V <sub>CCINT</sub> | V    |

| Analog Signal Range                     | $V_{DN1}, V_{DP2}$                | CP_EN = 1                                                                                                                                | V <sub>SWNEG</sub> |     | V <sub>SWPOS</sub> | V    |

| On-Resistance                           | R <sub>DS(ON)_USB</sub>           | $V_{BAT} = 3V, CP_EN = 1, I_{COMx} = 10mA,$<br>$V_{COMx} = 0V \text{ to } 3V$                                                            |                    | 3   |                    | Ω    |

| On-Resistance Match<br>Between Channels | $\Delta R_{DS(ON)}USB$            | $V_{BAT} = 3V, CP\_EN = 1, I_{COMx} = 10mA, V_{COMx} = 400mV$                                                                            |                    | 0.5 |                    | Ω    |

| Off Leakage Current                     | I <sub>USB_Off</sub>              | $V_{BAT} = 4.35V$ , Switch open, $V_{DN1}$ or<br>$V_{DP2} = 0.3V$ , 2.5V, $V_{COMx} = 2.5V$ , 0.3V                                       | -360               |     | 360                | nA   |

| On Leakage Current                      | I <sub>USB_On</sub>               | $V_{BAT}$ = 4.35V, Switch closed, $V_{DN1}$ or $V_{DP2}$ = 0.3V, 2.5V                                                                    | -360               |     | 360                | nA   |

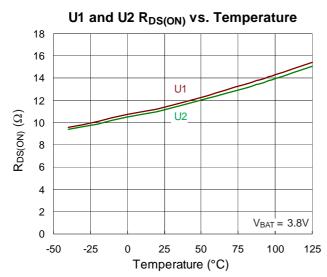

| UART/USB Analog S                       | witch (U1, U2)                    |                                                                                                                                          |                    |     |                    |      |

| Angles Circal Design                    |                                   | CP_EN = 0                                                                                                                                | 0                  |     | V <sub>CCINT</sub> |      |

| Analog Signal Range                     | V <sub>U1</sub> , V <sub>U2</sub> | CP_EN = 1                                                                                                                                | V <sub>SWNEG</sub> |     | V <sub>SWPOS</sub> | V    |

| On-Resistance                           | R <sub>DS(ON)_UART</sub>          | $V_{BAT} = 3V, CP\_EN = 1, I_{COMx} = 10mA,$<br>$V_{COMx} = 0V \text{ to } 3V$                                                           |                    | 12  |                    | Ω    |

| On-Resistance Match<br>Between Channels | $\Delta R_{DS(ON)}$ UART          | $V_{BAT} = 3V, CP\_EN = 1, I_{COMx} = 10mA, V_{COMx} = 1.5V$                                                                             |                    | 5   |                    | Ω    |

| Off Leakage Current                     | I <sub>UART_Off</sub>             | / <sub>BAT</sub> = 4.35V, Switch open, V <sub>U1</sub> or<br>/ <sub>U2</sub> = 0.3V, 2.5V, V <sub>COMx</sub> = 2.5V, 0.3V −360           |                    |     | 360                | nA   |

| On Leakage Current                      | I <sub>UART_On</sub>              | $V_{BAT}$ = 4.35V, Switch closed, $V_{U1}$ or $V_{U2}$ = 0.3V, 2.5V                                                                      | -360               |     | 360                | nA   |

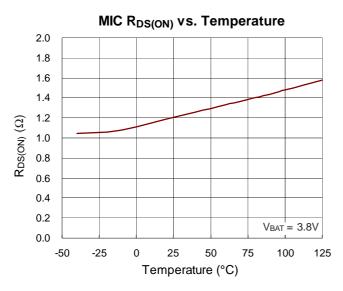

| MIC Analog Switch (I                    | MIC)                              |                                                                                                                                          |                    |     |                    |      |

| Analog Signal Range                     | Vino                              | CP_EN = 0                                                                                                                                | 0                  |     | V <sub>CCINT</sub> | V    |

| Analog Signal Range                     | V <sub>MIC</sub>                  | CP_EN = 1                                                                                                                                | V <sub>SWNEG</sub> |     | V <sub>SWPOS</sub> | v    |

| On-Resistance                           | R <sub>DS(ON)_M</sub>             | $V_{BAT} = 3V$ , $CP\_EN = 1$ , $I_{MIC} = 10mA$ ,<br>$V_{MIC} = 0V$ to $3V$                                                             |                    | 3.4 | 10                 | Ω    |

| On-Resistance<br>Flatness               | R <sub>FLATM</sub>                | $\label{eq:VBAT} \begin{array}{l} V_{BAT} = 3V, \ CP\_EN = 1, \ I_{MIC} = 10mA, \\ V_{MIC} = 0V \ to \ 3V \qquad (Note \ 5) \end{array}$ |                    | 0.1 |                    | Ω    |

| Off Leakage Current                     | I <sub>LM_Off</sub>               | $V_{BAT} = 4.35V$ , Switch open,<br>$V_{MIC} = 0.3V$ , 2.5V, $V_{ID} = 2.5V$ , 0.3V                                                      | -360               |     | 360                | nA   |

| On Leakage Current                      | I <sub>LM_On</sub>                | $V_{BAT} = 4.35V$ , Switch closed,<br>$V_{MIC} = 0.3V$ , 2.5V                                                                            | -360               |     | 360                | nA   |

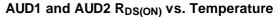

| Audio Analog Switch                     | (AUD1, AUD2)                      |                                                                                                                                          |                    |     |                    |      |

| Analog Signal Danga                     | Manage                            | CP_EN = 0                                                                                                                                | 0                  |     | V <sub>CCINT</sub> | V    |

| Analog Signal Range                     | V <sub>AUDIO</sub>                | CP_EN = 1                                                                                                                                | V <sub>SWNEG</sub> |     | V <sub>SWPOS</sub> | v    |

| On-Resistance                           | R <sub>DS(ON)_</sub> A            | $V_{BAT} = 3V, CP\_EN = 1, I_{COMx} = 10mA,$<br>$V_{COMx} = -2V \text{ to } 3V$                                                          |                    | 4   |                    | Ω    |

| On-Resistance Match<br>Between Channels | $\Delta R_{DS(ON)_A}$             | $V_{BAT} = 3V, CP_EN = 1, I_{COMx} = 10mA, V_{COMx} = 0V$                                                                                |                    | 0.2 |                    | Ω    |

| On-Resistance<br>Flatness               | R <sub>FLATA</sub>                | $V_{BAT} = 3V, CP_EN = 1, I_{COMx} = 10mA, V_{COMx} = -0.5 to 0.5V$ (Note 5)                                                             |                    | 1   |                    | Ω    |

| Paramet                       | ter        | Symbol                 | Test Condi                                                                                        | tions                | Min  | Тур        | Мах | Unit |

|-------------------------------|------------|------------------------|---------------------------------------------------------------------------------------------------|----------------------|------|------------|-----|------|

| Off Leakage Cur               |            | I <sub>LA_(OFF)</sub>  | $V_{BAT} = 4.35V$ , Switch<br>$V_{AUDx} = -0.5V$ to 0.5V<br>$V_{COMx} = -0.5V$ to 0.5V            | Open,<br>√,          | -360 |            | 360 | nA   |

| On Leakage Cur                | rent       | I <sub>LA_(ON)</sub>   | V <sub>BAT</sub> = 4.35V, Switch<br>V <sub>AUDx</sub> = -0.5V, 2V                                 | i Closed,            | -360 |            | 360 | nA   |

| Shunt Resistor                |            | R <sub>SHUNT</sub>     |                                                                                                   |                      | 30   | 100        | 200 | Ω    |

| Digital Signals               | (DSS, SCL, | SDA)                   |                                                                                                   |                      |      |            |     |      |

| SDA Input                     | Logic-High | VIH                    |                                                                                                   |                      | 1.4  |            |     | V    |

| Voltage<br>Threshold          | Logic-Low  | VIL                    |                                                                                                   |                      |      |            | 0.4 |      |

| Input Leakage C               | urrent     | I <sub>INLEAK</sub>    |                                                                                                   |                      | -1   |            | 1   | μA   |

| Open Drain Low                |            | V <sub>ODOL</sub>      | I <sub>SINK</sub> = 1mA                                                                           |                      |      |            | 0.4 | V    |

| DYNAMIC                       |            | -                      | -                                                                                                 |                      |      |            |     |      |

| I <sup>2</sup> C Max Clock    |            | fi2CCLK                |                                                                                                   |                      |      |            | 400 | kHz  |

| MIC_LP Detection              | on Pulse   | t <sub>MICLPDP</sub>   | MIC_LP = 1, SEMRE                                                                                 | N = 1                |      | 120        |     | μS   |

| MIC_LP Detection              | on Period  | t <sub>MICLPD</sub>    | MIC_LP = 1, SEMREN = 1                                                                            |                      |      | 120        |     | ms   |

| CP_EN Delay Ti                | me         | t <sub>CP_EN</sub>     | Not production tested                                                                             |                      |      |            | 1   | ms   |

| Analog Switch Turn On<br>Time |            | t <sub>ON</sub>        | $I^2C$ Stop to Switch On; $R_L = 50\Omega$                                                        |                      |      |            | 1   | ms   |

| Analog Switch To<br>Time      | urn Off    | t <sub>Off</sub>       | $I^2C$ Stop to Switch Off; $R_L = 50\Omega$                                                       |                      |      |            | 1   | ms   |

| Break-Before-Ma<br>Time       | ake Delay  | t <sub>D</sub>         | $R_L = 50\Omega$ (Note 5)                                                                         |                      | >0   |            |     | μS   |

| Charger Deboun                | ce Time    | tCHGR_DET_DBNC         |                                                                                                   |                      | 20   |            | 40  | ms   |

| VDAT_SRC ON                   |            | t <sub>DP_SRC_ON</sub> |                                                                                                   |                      | 100  |            | 200 | ms   |

| VDAT_SRC OFF<br>enable        | To ISET    | tdpsrc_hichrnt         |                                                                                                   |                      | 40   |            | 80  | ms   |

| Debounce Time                 |            | t <sub>MDEB</sub>      | All Comparators                                                                                   | -                    | 20   |            | 500 | ms   |

|                               |            |                        | $R_L = 50\Omega$ , f = 20kHz,                                                                     | DN1, DP2             |      | -60        |     |      |

| Off-Isolation                 |            | V <sub>ISO</sub>       | $V_{COMx} = 0.5Vp-p$                                                                              | U1, U2<br>AUD1, AUD2 |      | -60<br>-60 |     | dB   |

|                               |            |                        | (Note 5)                                                                                          | MIC                  |      | -60        |     |      |

| Cross-talk                    |            | V <sub>CT</sub>        | $R_L = 50\Omega$ , f = 20kHz,<br>$V_{COMx} = 1V_{RMS}$ (N                                         | lote 5)              |      | -115       |     | dB   |

| Total Harmonic Distortion     |            | THD                    | f = 20Hz to $20kHz$ ,<br>$V_{COMx} = 0.5Vp-p$ ,                                                   | MIC                  |      | 0.05       |     | 0/   |

|                               |            | ערוו                   | $\begin{array}{c} R_L = 50\Omega; DC \\ \text{bias=0}  (\text{Note 5}) \end{array}  \text{Audio}$ |                      |      | 0.05       |     | %    |

| Battery Charge                | r          |                        |                                                                                                   |                      |      |            |     |      |

| VBUS-VBAT VO                  | S Rising   |                        |                                                                                                   |                      |      | 75         | 150 | mV   |

| VBUS-VBAT VO                  | S Falling  |                        |                                                                                                   |                      | 18   | 32         |     | mV   |

| DPM Regulation                | Voltage    | V <sub>DPM</sub>       |                                                                                                   |                      | 3.9  | 3.95       | 4   | V    |

| Parameter                                  | Symbol                | Test Conditions                              | Min   | Тур  | Max   | Unit |

|--------------------------------------------|-----------------------|----------------------------------------------|-------|------|-------|------|

| VBAT Regulation Voltage                    |                       | $T_A = 0^{\circ}C$ to $85^{\circ}C$          | 4.307 | 4.35 | 4.393 | V    |

| Thermal Regulation                         |                       | (Note 5)                                     |       | 125  |       | °C   |

| Pre-Charge Threshold                       | V <sub>PRECH</sub>    | VBAT Rising                                  | 2.5   | 2.6  | 2.7   | V    |

| Pre-Charge Current Accuracy                |                       |                                              |       | 10   |       | mA   |

| Fast-Charge Current Accuracy               |                       |                                              |       | 5    |       | %    |

| Fast-Charge to Pre-Charge<br>Deglitch Time |                       |                                              |       | 25   |       | ms   |

| VBUS Power FET RDS(ON)                     |                       | I <sub>BAT</sub> = 1A                        |       | 250  | 500   | mV   |

| LDO R <sub>DS(ON)</sub>                    |                       |                                              |       | 3    | 6     | Ω    |

| LDO Output Voltage                         |                       |                                              | 4.75  | 4.9  | 5.05  | V    |

| LDO Maximum Output Current                 |                       |                                              | 60    | 120  | 180   | mA   |

| Factory Mode V <sub>OUT</sub>              |                       | $C_{VBUS} = 22 \mu F, \ C_{VBAT} > 40 \mu F$ | 4.263 | 4.35 | 4.437 | V    |

| Factory Mode Maximum<br>Output Current     |                       |                                              | 2.3   |      |       | А    |

| Linear Regulator                           |                       |                                              |       |      |       |      |

| LDO Output Voltage                         |                       | Setting OUTx = 3.3V                          | 3.2   | 3.3  | 3.4   | V    |

| Output Current                             | I <sub>OUT-LDO</sub>  |                                              | 300   |      |       | mA   |

| Drop Out Voltage                           | I <sub>DROP-LDO</sub> | $V_{IN} = OUTx - 100mV / I_{OUTx} = 100mA$   |       | 0.13 |       | V    |

| Supply Current                             | I <sub>Q-LDO</sub>    | $V_{IN} = 4.2V / I_{OUTx} = 0mA$             |       | 20   |       | μA   |

| Power Supply Rejection Ratio               | PSRR <sub>LDO</sub>   | (Note 5)                                     |       | 70   |       | dB   |

| LED Current Source                         |                       |                                              |       |      |       |      |

| LED Quiescent Current                      | I <sub>Q-LED</sub>    |                                              |       | 100  |       | μΑ   |

| Maximum LED Current                        | I <sub>LED(MAX)</sub> |                                              |       | 30   |       | mA   |

| LED Current Accuracy                       | $\Delta I_{LED}$      | Setting I <sub>LED</sub> = 20mA              |       | 5    |       | %    |

| LED Current Match                          |                       |                                              |       | 5    |       | %    |

Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by Design.

## **Typical Operating Characteristics**

## **Application Information**

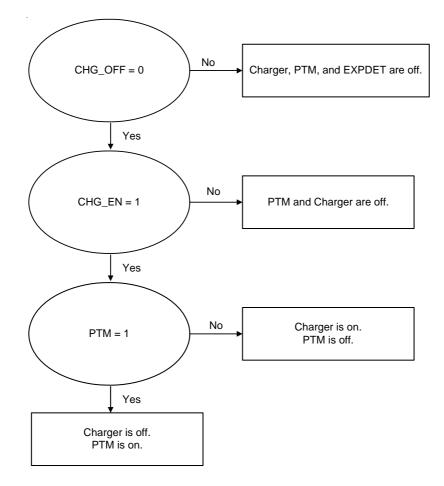

### **Charger Description**

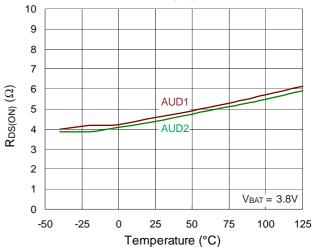

The RT8966H integrates a single-cell Li-ion battery charger IC with pre-charge mode, a fast charge mode (constant current mode) or constant voltage mode. The charge current is programmable via the I<sup>2</sup>C interface as shown in the control register address tables, CHG\_Ctrl1 and CHG\_Ctrl2. The CV mode voltage is fixed at 4.35V. The pre-charge threshold is fixed at 2.6V. If the battery voltage is below the pre-charge threshold, the RT8966H charges the battery with a trickle current until the battery voltage rises above the pre-charge threshold. The RT8966H is capable of being powered up from AC adapter and USB (Universal Serial Bus) port inputs. Moreover, the RT8966H includes a linear regulator (LDO 4.9V, 50mA) for supplying low power external circuitry.

### **Charger Over Voltage Protection**

The input voltage is monitored by the internal comparator and the input over voltage protection threshold is set to 6.9V. However, input voltage over 28V will still cause damage to the RT8966H. When the input voltage exceeds the threshold, the comparator outputs a logic signal to turn off the power P-MOSFET to prevent high input voltage from damaging the electronics in the handheld system. When the input over voltage condition is removed, the comparator re-enables the output by running through softstart.

### **Battery Charge Profile**

### Pre-Charge Mode :

Figure 1 shows the RT8966H charging state of the charging function. During a charge cycle, if the battery voltage is below the  $V_{PRECH}$  threshold (typical value is 2.6V), the charger enters pre-charge mode. This feature revives deeply discharged cells and protects battery life. The pre-charge current has a typical value of 50mA.

### Constant Current Mode :

Once the battery voltage is higher than 2.6V, the charger enters the constant current stage. The constant current level can be programmed from 90mA to 1A via the  $I^2C$  compatible interface but the default value is 400mA.

### **Constant Voltage Mode :**

Once the battery voltage level closes in at 4.35V, the charger enters constant voltage phase and the charging current begins to decrease. When the charging current becomes lower than  $I_{EOC}$  (end of charge current), the loop enters charge done mode.

The RT8966H will then send an interrupt and register CHG bit, as shown in Table 10. Finally, INT\_STA2 becomes 0 to indicate that the RT8966H has completed the charging.

### **Recharge Phase :**

When any loading or event causes  $V_{BAT}$  to drop or battery to discharge, the charger will automatically jump to the appropriate mode to recharge the battery.

Figure 1. Charging State of the Charger Function

## Charger for Factory Mode

The RT8966H provides factory mode for supplies up to 2.3A for powering external loads with no battery installed and  $V_{BAT}$  is regulated to 4.35V. The factory mode allows the user to supply system power with no battery connected. It is programmable by I<sup>2</sup>C via the PTM bit, as shown in Table 13.

In factory mode, thermal regulation is disabled, but thermal protection  $(135^{\circ}C)$  is still active. When using currents greater than 1.5A in factory mode, the user must limit the duty cycle at the maximum current to 20% with a maximum period of 10ms.

#### **Charger Sleep Mode**

The RT8966H enters sleep mode if the power is removed from the input. This feature prevents draining the battery during absence of input supply.

### **Charger Temperature Regulation and Thermal** Protection

In order to maximize charge rate, the RT8966H features a junction temperature regulation loop. This allows the RT8966H to limit the charge current in order to maintain a junction temperature around the thermal regulation threshold (125°C). The RT8966H monitors the junction temperature, T<sub>J</sub>, of the die and disconnects the battery from the input if T<sub>J</sub> exceeds 125°C. This operation continues until junction temperature falls below thermal regulation threshold (125°C) by the hysteresis level. This feature prevents maximum power dissipation from exceeding typical design conditions.

#### **Charger Input and Output Capacitors Selection**

For most applications, a high frequency decoupling capacitor place near the input is usually sufficient. A 1µF ceramic capacitor, should work well. However, in other applications, depending on the power supply characteristics and cable length, it may be necessary to add an additional 10µF ceramic capacitor to the input.

The RT8966H also requires a small output capacitor for loop stability. A typical 1µF ceramic capacitor placed between the VBATT pin and GND is sufficient.

#### Input DPM Mode

When USB sources are selected, the input voltage, VBUS, is monitored. If VBUS falls to VDPM, the input current limit is reduced to prevent the input voltage from falling further. This prevents the IC from crashing poorly designed or incorrectly configured USB sourced.

### **EXPDET Linear Regulator**

The RT8966H integrates one low dropout linear regulator (LDO) that supplies up to 50mA of output current. The LDO can be enabled by  $I^2C$  via the EXTPDET bit, as shown in Table 13. Note that the LDO current is independent and not monitored by the charge current limit.

#### Linear Regulator

There are four LDOs in the RT8966H. These LDOs can be programmed via I<sup>2</sup>C in the following control registers Enable, OUT Set1, OUT Set2. These registers include each LDO's enable/disable control as well as its output voltage selection from 1V to 3.3V.

#### Linear Regulator Capacitor Selection

In order to maintain regulator stability and performance, better quality ceramic capacitor, such as X7R/X5R, should be selected.

Like any low-dropout regulator, the external capacitors used with the RT8966H must be carefully selected for regulator stability and performance. Use a capacitor with value larger than 1µF on the RT8966H input. The amount of capacitance can be increased without limit. The input capacitor should be located at a distance of not more than 0.5 inch from the input pin of the IC and returned to a clean analog ground. A capacitor with larger value and lower ESR (equivalent series resistance) provides better PSRR and line-transient response.

The output capacitor must meet requirements for both minimum amount of capacitance and ESR in all LDOs application. The RT8966H is designed specifically to work with low ESR ceramic output capacitor for space-saving and performance consideration. Using a ceramic capacitor whose value is at least  $1\mu$ F with ESR >  $30m\Omega$  on the RT8966H output ensures stability. The RT8966H still works well with output capacitor of other types due to the wide stable ESR range. Output capacitor with larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The output capacitor should be located at a distance of not more than 0.5 inch from the OUTx pin of the RT8966H and returned to a clean analog ground.

#### **Current Source LED Driver**

There are four current source LED drivers in the RT8966H. These current sources can be programmed via I<sup>2</sup>C in the following control registers, Enable and LED Set. These registers include each driver's enable/disable control, source current control, and LED brightness dimming.

Copyright @2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

## RT8966H

The RT8966H provides a constant current for the white LEDs. Each channel supports up to 30mA current and regulates a constant current for uniform intensity. In order to maintain LED constant current, the input voltage must provide the required LED forward voltage and current source dropout voltage. If the forward voltage of the white LEDs is 3.3V, the input voltage should be higher than 3.4V to provide enough voltage headroom for maintaining constant brightness.

### I<sup>2</sup>C Control Interface

The RT8966H uses an I<sup>2</sup>C to be the control interface. The I<sup>2</sup>C interface allows the host microprocessor to control the switches and the accessory detection ADC. The status of the device detection may be sent through the I<sup>2</sup>C bus. The interrupt line may also be used to signal a status change to the host microprocessor. The I<sup>2</sup>C interface and interrupt output are compliant with 1.8V logic voltage levels. The SCL pin is only an input and the SDA pin is an input or open drain output. The interrupt line is only an open drain output.

$I^2C$  Device Address = 1000100x (where x is the read/write bit)

### Switches

The RT8966H provides a multiple input multiplexer to support USB high Speed, UART, stereo audio, mono audio and a microphone. The output of the multiplexer is used to connect to a mini or micro USB connector. When the VBUS voltage is higher than the VB Detect threshold voltage, the RT8966H can turn on and turn off the paths of USB, UART and Audio. However, when the VBUS voltage is lower than the VB Detect threshold voltage, the RT8966H can then only turn on and turn off the paths of stereo audio and mono audio. The following table shows the switch status versus VBUS level.

|             | USB<br>Switches | UART<br>Switches | Audio<br>Switches |  |

|-------------|-----------------|------------------|-------------------|--|

| VBUS = High | Allow           | Allow            | Allow             |  |

| VBUS = Low  | Not Allow       | Not Allow        | Allow             |  |

The default startup of the RT8966H can be set as USB or UART according to the voltage at the DSS pin. The voltage on the DSS pin will be sampled immediately once the

first power supply is attached to the RT8966H through VB or BAT and is latched by the first rising voltage on the SCL pin. The DSS pin voltage controls the switch state during this period. If the voltage of the DSS pin rises or falls below 0.4V before the first rising edge on the SCL pin, the switch state will be changed between USB or UART positions.

When the DSS pin voltage is below 1V, the default startup will be USB. If the DSS pin voltage is greater than 1V, the UART will be set as the default startup. The DSS pin provides an internal  $300k\Omega$  pull down resistor for USB startup. The DSS pin can also be left unconnected or connected to GND. For UART startup, connect the DSS pin with an external  $300k\Omega$  resistor to BAT.

#### **Multiplexer Inputs**

#### DN/DP :

These two pins can support all speed ranges of the USB including USB high speed, full Speed, low speed and UART signals from 0V to 3.3V. In order to function, the CP\_EN bit in the register must be set to 1 when signals pass through the switch. DN/DP channel of the RT8966H will be routed to the D-/D+ lines on a mini/micro USB connector.

### U1/U2 :

These two pins can also support the speed range of the USB including USB full speed, low speed and UART signals from 0V to 3.3V. Similarly, the CP\_EN bit must be set to 1 when signals pass through the switch. U1/U2 channel of the RT8966H will be routed to D-/D+ lines on a mini/micro USB connector.

Voice Audio : The RT8966H can support one mono microphone in which the signal is routed to the ID line. For routing to a headset, the microphone audio will be used with the stereo audio input. CP\_EN must be 1 when signals pass through the switch.

Stereo Audio : The RT8966H supports a stereo audio amplifier connected with a mono microphone. The LEFT and RIGHT channel audio of the RT8966H is routed to the D+ and D– lines on the mini/micro USB connector, while the microphone is routed to the ID line on the mini/micro

## RICHTEK

USB connector. The RT8966H provides internal  $100k\Omega$  shunt resistors on the AUD1 and AUD2 speaker lines. Those resistors are used to reduce pops and clicks when the audio amplifier is switched on due to the ac coupling capacitors. If a Direct Drive audio amplifier is adopted, the  $100k\Omega$  switched shunt resistors can be removed. CP\_EN must be 1 when signals pass through the switch.

### Multiplexer Output with High Impedance Mode

The RT8966H provides an I<sup>2</sup>C control to set the D-, D+ and ID pins in high impedance condition. CP\_EN must be 1 when the multiplexer output is connected to high impedance. The D-, D+ and ID pin of the multiplexer outputs must always be connected to the D-, D+ and ID pin of the mini/micro USB connector respectively. This allows the D-, D+ and ID pins to maintain in a "safe" position when a headset is inserted. If the D-, D+ switches are left connected to one of the 4 inputs, it is possible that a dc voltage will be present to cause a pop in the speakers.

### **Enable Power Saving Mode**

The RT8966H provides multiple power saving modes. The power saving mode is used to turn off the internal LDO, charge pump and comparator when not in use. The VB OVP will not be affected by any power saving mode. The RT8966H provides three  $I^2C$  bits for power saving operation.

CP\_EN : CP\_EN is used to control the charge pump to achieve proper operation of the analog switches. This bit must be set to 1 when a signal passes through a switch and also any time a negative rail signal is connected to an audio switch input (AUD1, AUD2). The charge pump provides low on-resistance for the switches when they are in conduction condition.

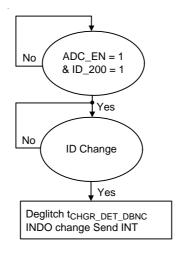

ADC\_EN : ADC\_EN is used to control the internal ADC and the ID LD0. When this bit is set to disable, the ADC bits will be 0000 and no interrupt signal will be generated. Any pending interrupt signals arising from the change in ADC value will not be cleared unless a READ is sent manually to the STATUS register.

SEMREN : This bit controls the internal comparators used for the SEND/END switch, microphone removal and the ID LDO. When this bit is set to disable, the SE\_COMP and MR\_COMP registers will be set to zero and no interrupt signal will be generated. Any pending interrupt signals arising from the change in the SE\_COMP and MR\_COMP comparators will not be cleared. It can only be cleared manually by sending a READ to the STATUS register. (ID LDO Enable = ADC\_EN or SEMREN)

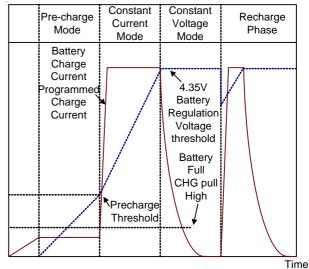

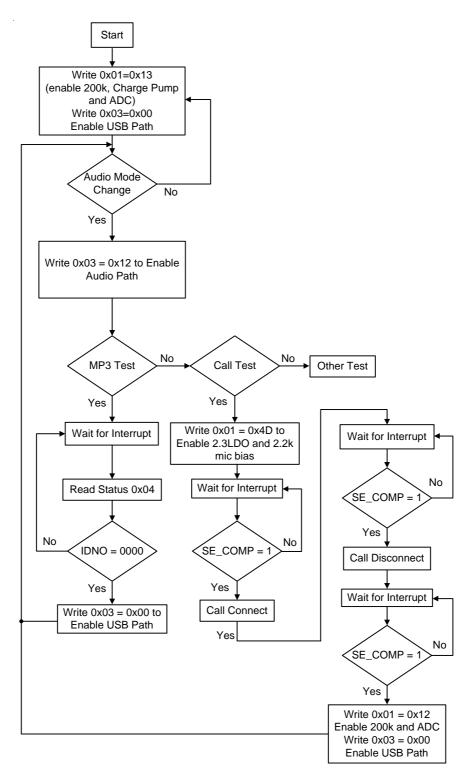

### Microphone Power Saving Mode

The microphone can draw a large current due to the typical  $2.2k\Omega$  bias resistor when it is plugged in. This current will be dissipated even if the microphone is not used for audio input (not in a call or voice recorder not in use, etc.) This is done to allow for the SEND/END button detection's operation. The RT8966H provides a method to reduce the drawn current by turning off the  $2.2k\Omega$  pull up resistor. This resistor will be turned on only for short durations to check whether the SEND/END was being pressed. The detail of the microphone power saving circuit is shown in Figure 2. When the external  $2.2k\Omega$  resistor is turned off, the internal 200k $\Omega$  resistor will be turned on to immediately detect a microphone removal event once it occurs. When the register bit MIC LP = 1, an interrupt signal will be generated for both a microphone removal (MR\_COMP) event and a SEND/END button detection (SE COMP).

Figure 2. The Microphone Power Saving Circuit of the RT8966H

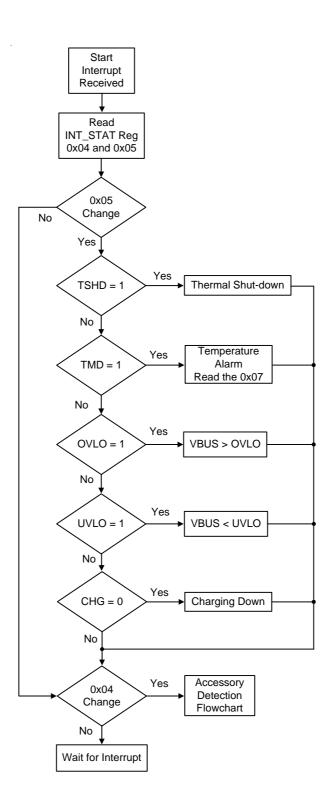

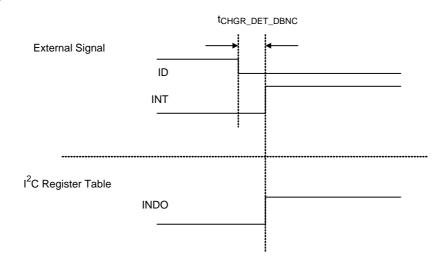

### **Event Detection and Interrupt Generation**

When a specific event occurs, the RT8966H will be able to detect it and then will generate an interrupt signal. The above-mentioned specific events include CHGDET, MR\_COMP, SE\_COMP, VBUS and IDNO. For details of those specific events, please refer to Table 9, under

## RT8966H

"INT\_STA1 0x04". If the ADC reads and detects that there is a plugged device with an ID resistor or microphone present, an interrupt signal will be generated. If a device is removed and the ADC reads a high voltage on the ID line, an interrupt signal is generated. If the voltage on the VB pin rises above or drops below the VB detect threshold,  $V_{DET_VB}$  for the detection/removal of an USB cable, an interrupt signal will also be generated. Interrupt will also be generated once the status changes on the SE\_OMP and MR\_COMP comparators. The interrupt signal will be cleared by reading the STATUS register. The interrupt signal is triggered by different levels and the interrupt polarity can be set through the  $I^2C$  bus.

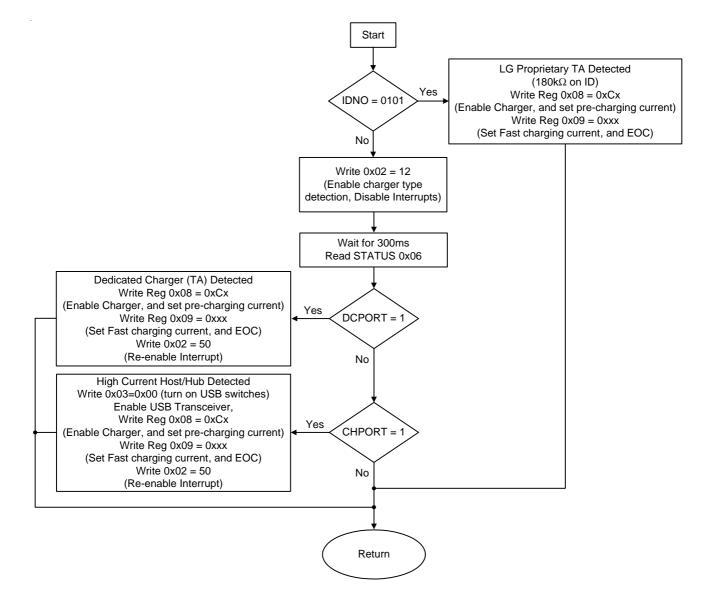

#### **CHGDET : Charger Detection**

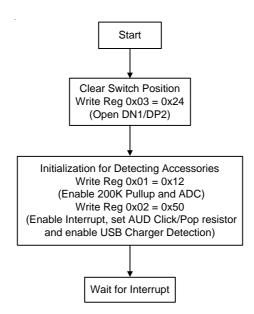

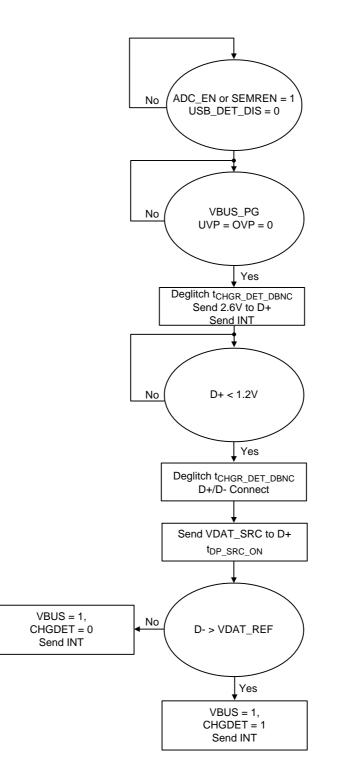

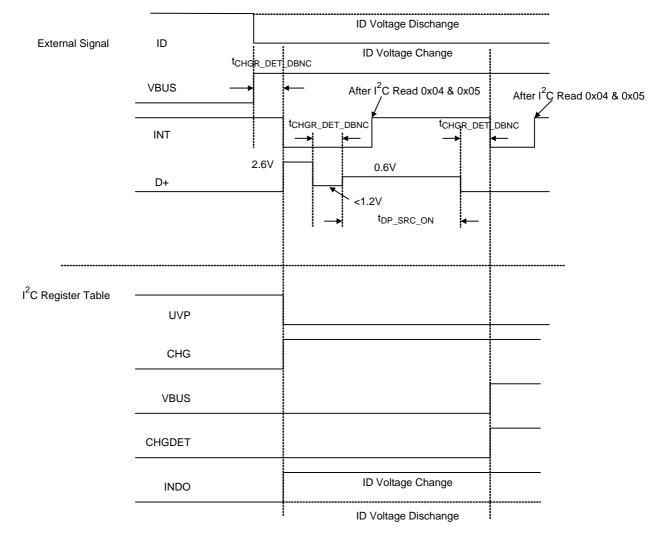

The RT8966H is compliant with the USB Battery Charging Specification Revision 1. The RT8966H is capable of detecting dedicated chargers, host/hub chargers and standard USB port. The RT8966H USB detection function is off (USB\_DET\_DIS = 1) by default and requires an  $I^2C$  WRITE to enable the detection.

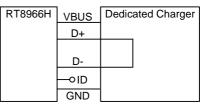

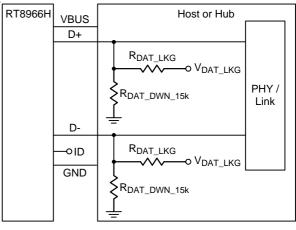

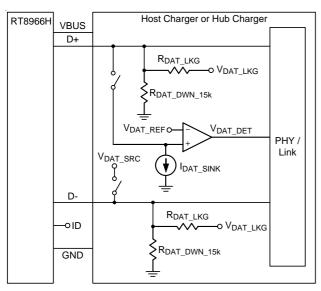

The RT8966H charger detection includes internal logic to allow valid charger detection (D+/D- shorted for host/hub charger) and an external open drain for automatic ISET signal generation. The charger detection sequence is started once VBUS rises above V<sub>DET VB</sub>. However, the charge detection will not be activated if the cable ID resistor value is  $56k\Omega$  since this value is already designated as the UART cable. Besides, it can only be started if the USB\_DET\_DIS bit is equal to 0. When V<sub>DAT SRC</sub> is applied to D+, the V<sub>DAT SRC</sub> voltage will also be applied to the Dline by the dedicated charger since D+ and D- are shorted. The dedicated charger detection is shown in Figure 3. As for the host/hub charger, D+ receives V<sub>DAT SRC</sub> and retransfers it on D-. Thus, it acts similarly to the dedicated charger. The host/hub charger detection is shown in Figure 4. However, when a standard USB port is inserted instead, the D- will not receive the VDAT\_SRT after D+ sends out the VDAT\_SRT signal. The standard USB port is shown in Figure 5. It is through such method that the RT8966H differentiates between a standard USB port and a charger port. (either dedicated charger or host/hub charger).

The distinction between a dedicated charger or a high

current host/hub can be achieved by the manual operation started with an I<sup>2</sup>C WRITE. After an interrupt signal is sent to the host, it reads the IN\_STAT register which can be used to set the CHGDET and VBUS bits (USB high current host/hub or dedicated charger detected). The host will set the CHG\_TYP bit to perform the type detection. The detection is achieved by connecting a high value pull up resistor (300k to 600k) to D+. If D– stays low (below 0.8V), a high current hub/host is detected. A dedicated charger will be detected if D– goes high. The output of this detection is two bits in the STATUS register. The CHGDET bit in INT\_STAT rather than the interrupt signal is guaranteed by the register. After the charger type detection is completed, the CHG\_TYP bit will automatically reset to 0.

The ISET pin of the RT8966H is an external open-drain connected to an external charger to indicate whether the inserted USB is a charger or not. When the inserted one is a standard USB port, the ISET pin will be high impedance. When the inserted one is a charger (dedicated charger or host/hub charger), the ISET pin will be pulled low. ISET controls the external battery charger current limit. If ISET is high impedance, the charger current will be limited at 100mA. If ISET is low, then the charger current is allowed to be drawn up to 1.5A.

Figure 3. Dedicated Charger Detection

Figure 4. Host/Hub Charger Detection

## RICHTEK

Figure 5. Standard USB Port

## MR\_COMP, SE\_COMP : Microphone Removal Detection and Send/End Switch

The RT8966H provides MR\_COMP for microphone removal detection and SE\_COMP for Send/End switch detection by checking the voltage on ID when a microphone is detected on the ID pin. A bias resistor (typical 2.2k) should be connected between ID and a bias voltage source (typical 2.3V). When the microphone is not connected, the ID pin voltage will be pulled high to equal the bias voltage and the comparator will detect this voltage rise.

The microphone removal threshold voltage will be 90% of the microphone bias voltage. There is a switch included in the headset which is connected between the ID line and ground to signal a SEND or END condition. The voltage drop of the ID line will be detected by an internal comparator with a typical threshold of 10% bias voltage source. If the voltage on the ID pin rises above the microphone removal threshold voltage or drops below the SEND/END threshold, the host microprocessor will read the status of these comparators across the I<sup>2</sup>C bus. An ID voltage >90% means the microphone is removed, an ID voltage <10% means push, and an ID voltage between 10% to 90% means the microphone is plugged.

### **VBUS : VB Voltage Detection**

When the VB voltage is lower than  $V_{DET_VB}$ , the VBUS bit will be equal to 0. If the VB voltage is higher than  $V_{DET_VB}$ , the VBUS bit will be equal to 1.

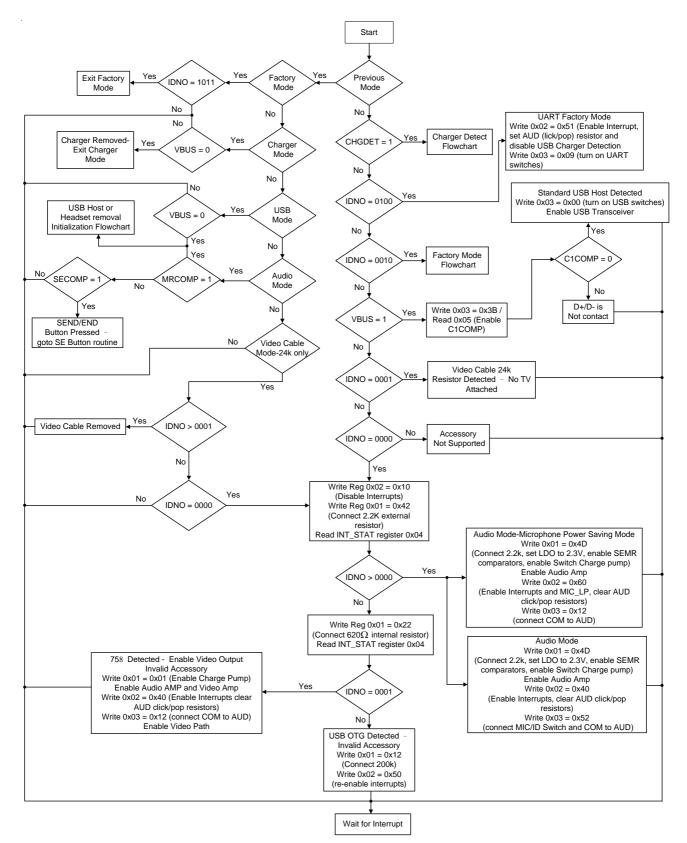

#### **Device Identification**

The RT8966H supports multiple accessories by detecting unique characteristics, such as VBUS voltage, ID resistor value and shorted USB data lines. These characteristics are shown in Tables 1 to 3. The detection of connected accessories is performed by using an internal  $200k\Omega$  pull up resistor.

| ADC Voltage | ID Resistor k $\Omega$                                                                                                                                                                        | D+ Condition                                                                                                                                                                                                                                                                                                                                                                                                     | D- Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100%        | Open                                                                                                                                                                                          | 15k to GND                                                                                                                                                                                                                                                                                                                                                                                                       | 15k to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | USB Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 100%        | Open                                                                                                                                                                                          | Shorted                                                                                                                                                                                                                                                                                                                                                                                                          | Shorted                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TA Charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 81.90%      | 910                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 75.60%      | 620                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |