RTL8306E-CG

# SINGLE-CHIP 6-PORT 10/100MBPS ETHERNET SWITCH CONTROLLER WITH DUAL MII/RMII INTERFACES

## **DATASHEET**

(CONFIDENTIAL: Development Partners Only)

Rev. 1.1 03 November 2010

**Track ID: JATR-2265-11**

Realtek Semiconductor Corp.

No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, Taiwan Tel.: +886-3-578-0211. Fax: +886-3-577-6047 www.realtek.com

#### **COPYRIGHT**

©2010 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

#### **DISCLAIMER**

Realtek provides this document "as is", without warranty of any kind. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

#### **TRADEMARKS**

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

#### **USING THIS DOCUMENT**

This document is intended for the software engineer's reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide.

## **REVISION HISTORY**

| Revision               | Release Date                                                             | Summary                                                     |  |

|------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------|--|

| 1.0                    | 2010/08/05                                                               | First release.                                              |  |

| 1.1                    | 2010/11/03                                                               | Revised Table 3 Mode Configuration Pin Definitions, page 9. |  |

|                        | Revised Table 29 Spd and Bi-Color Link/Act Truth Table when the RTL8306E |                                                             |  |

| Controls LED, page 77. |                                                                          |                                                             |  |

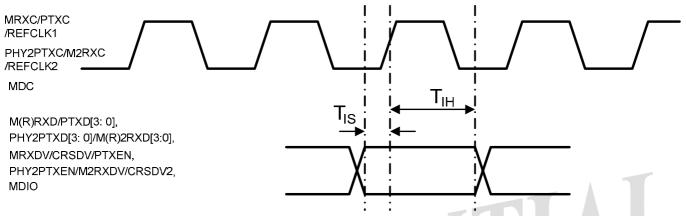

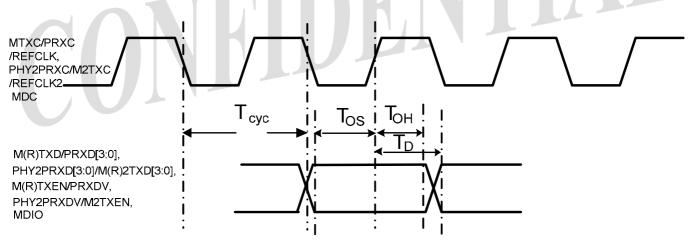

|                        |                                                                          | Revised Table 78 MII/TMII/RMII/SMI Timing, page 110.        |  |

# **Table of Contents**

| 1.     |     | GENERAL DESCRIPTION                                               | 1  |

|--------|-----|-------------------------------------------------------------------|----|

| 2.     |     | FEATURES                                                          |    |

| <br>3. |     | SYSTEM APPLICATIONS                                               |    |

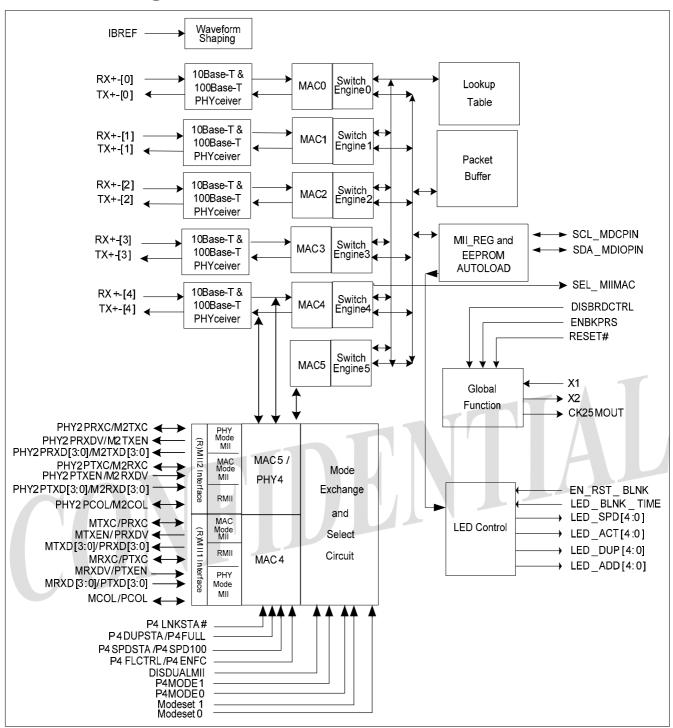

|        |     | BLOCK DIAGRAM                                                     |    |

| 4.     |     |                                                                   |    |

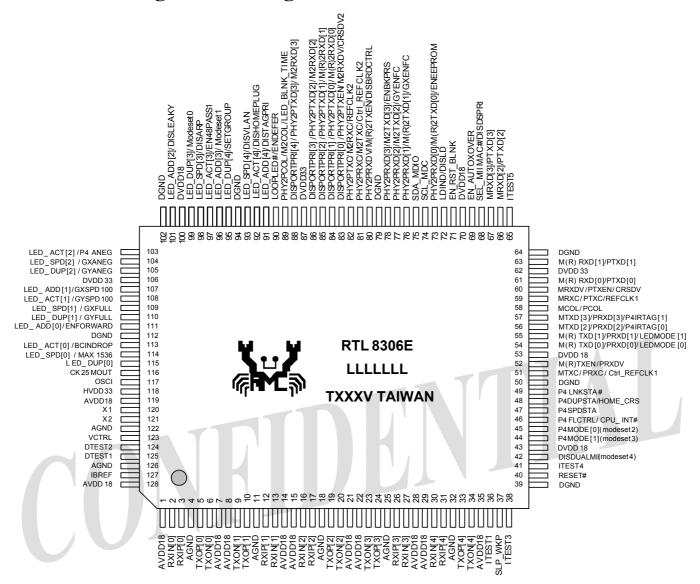

| 5.     |     | PIN ASSIGNMENTS                                                   | 6  |

|        | 5.1 |                                                                   |    |

|        | 5.2 |                                                                   |    |

|        | 5.3 | 3. PIN ASSIGNMENTS TABLE                                          |    |

| 6.     |     | PIN DESCRIPTIONS                                                  | 9  |

|        | 6.1 | 1. Media Connection Pins                                          | 9  |

|        | 6.2 |                                                                   |    |

|        | 6.3 |                                                                   |    |

|        | 6.4 |                                                                   |    |

|        | 6.5 |                                                                   |    |

|        | 6.6 |                                                                   |    |

|        | 6.7 |                                                                   |    |

|        | 6.8 |                                                                   |    |

|        | 6.9 |                                                                   |    |

|        | 6.1 |                                                                   |    |

| 7.     |     | BASIC FUNCTIONAL DESCRIPTION                                      | 28 |

|        | 7.1 | 1. SWITCH CORE FUNCTION OVERVIEW                                  | 28 |

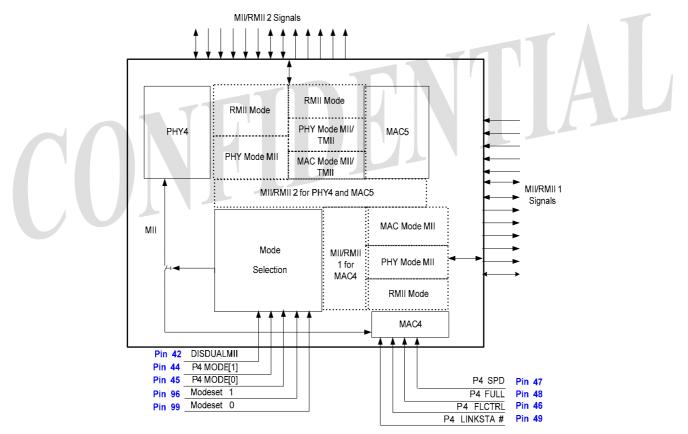

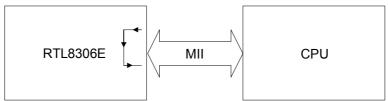

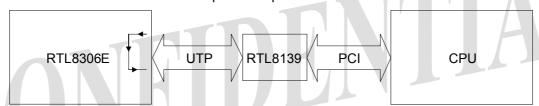

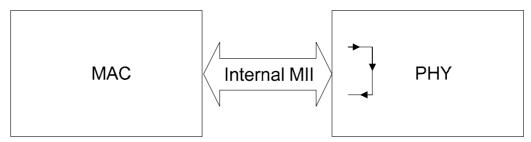

|        |     | 7.1.1. Dual MII/RMII                                              |    |

|        |     | 7.1.1.1 Description                                               | 28 |

|        |     | 7.1.1.2 Dual MII/RMII Mode Configuration                          | 29 |

|        |     | 7.1.1.3 Port4 (5th Port) and Port5 (6th MAC) Status Configuration |    |

|        |     | 7.1.2. Port0, 1, 2, 3 Status Configuration                        |    |

|        |     | 7.1.3. Flow Control                                               |    |

|        |     | 7.1.3.1 IEEE 802.3x Full Duplex Flow Control                      | 31 |

|        |     | 7.1.3.3 Half Duplex Back Pressure                                 |    |

|        |     | 7.1.3.4 NWay Mode                                                 |    |

|        |     | 7.1.3.5 Force Mode                                                | 32 |

|        |     | 7.1.4. Address Search, Learning, and Aging                        | 32 |

|        |     | 7.1.5. Half Duplex Operation                                      |    |

|        |     | 7.1.6. InterFrame Gap                                             | 33 |

|        |     | 7.1.7. Illegal Frame                                              |    |

|        | 7.2 |                                                                   |    |

|        |     | 7.2.1. Auto-Negotiation for UTP                                   |    |

|        |     | 7.2.2. 10Base-T Transmit Function                                 |    |

|        |     | 7.2.3. 10Base-T Receive Function                                  |    |

|        |     | 7.2.4. Link Monitor                                               |    |

|        |     | 7.2.5. 100Base-TX Transmit Function                               |    |

|        |     | 7.2.0. 100base-1A receive Function                                |    |

|        |     | 7.2.8. Crossover Detection and Auto Correction                    |    |

|        |     | 7.2.9. Polarity Detection and Correction                          |    |

|        | 7.3 |                                                                   |    |

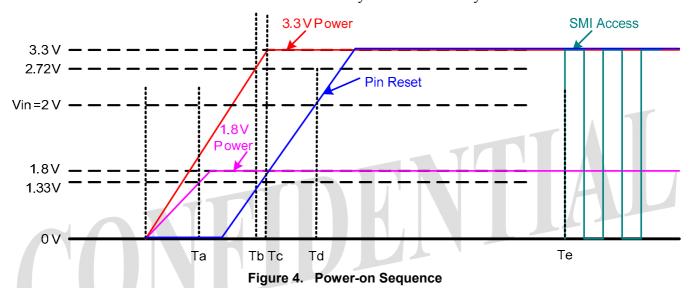

|        |     | 7.3.1. Power-on Sequence                                          |    |

|        |     |                                                                   |    |

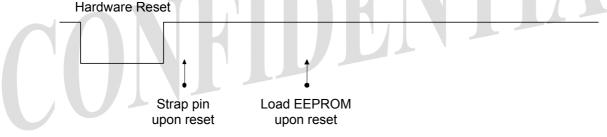

|    | 7.3.2.             | Reset                                             | 30 |

|----|--------------------|---------------------------------------------------|----|

|    |                    | Setup and Configuration                           |    |

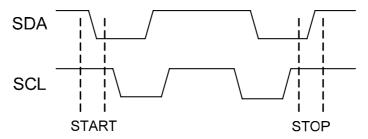

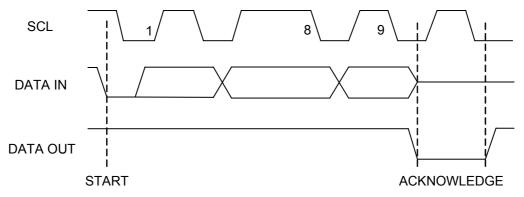

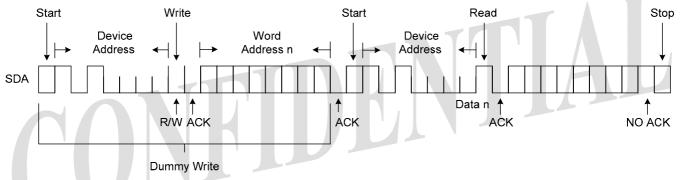

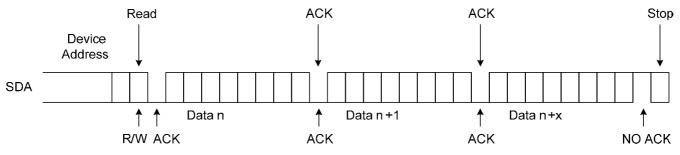

|    |                    | Serial EEPROM Example: 24LC01/02/04               |    |

|    | 7.3.4.1            |                                                   |    |

|    | 7.3.4.2            |                                                   |    |

|    | 7.3.5.             | <i>SMI</i>                                        |    |

|    |                    | Head-Of-Line Blocking                             |    |

|    |                    | Filtering/Forwarding Reserved Control Frame       |    |

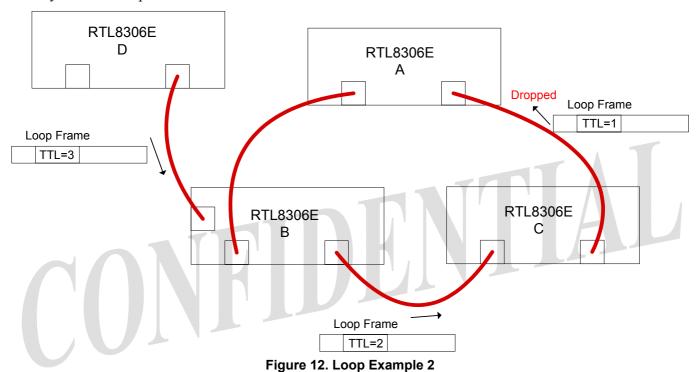

|    |                    | Loop Detection                                    |    |

|    |                    | MAC Local Loopback Return to External             |    |

|    | 7.3.10.            | Reg. 0.14 PHY Digital Loopback Return to Internal |    |

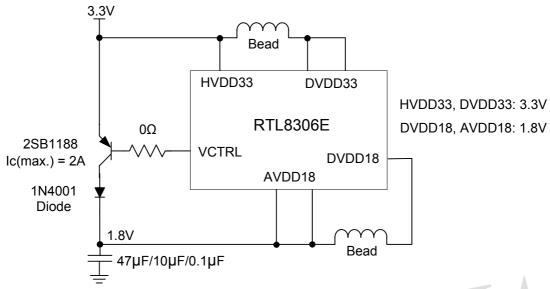

|    | 7.3.11.            | 1.8V Power Generation                             |    |

|    | 7.3.11.            | Crystal/Oscillator                                |    |

|    |                    | •                                                 |    |

| 3. | ADVAN              | ICED FUNCTION DESCRIPTION                         | 4  |

|    | 8.1. AC            | CL Function                                       | 1  |

|    |                    | AC LIMIT                                          |    |

|    |                    | ORT ISOLATION                                     |    |

|    |                    |                                                   |    |

|    |                    | LAN FUNCTION                                      |    |

|    |                    |                                                   |    |

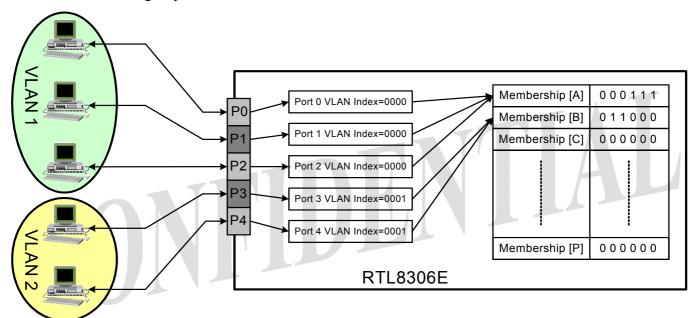

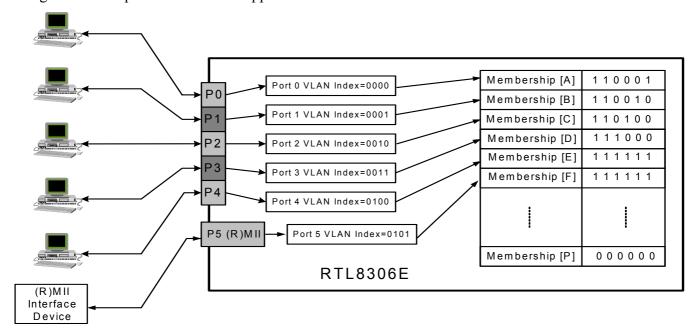

|    |                    | Port-Based VLAN                                   |    |

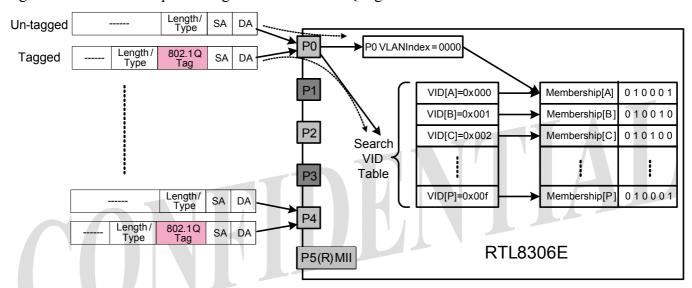

|    |                    | IEEE 802.1Q Tagged-VID Based VLAN                 |    |

|    |                    | Insert/Remove/Replace Tag                         |    |

|    | 8.4.5.             | VLAN Translation                                  |    |

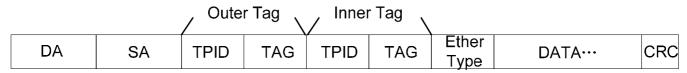

|    |                    | QinQ Function                                     |    |

|    |                    | Ingress and Egress Rules                          |    |

|    |                    | EE 802.1p Remarking Function                      |    |

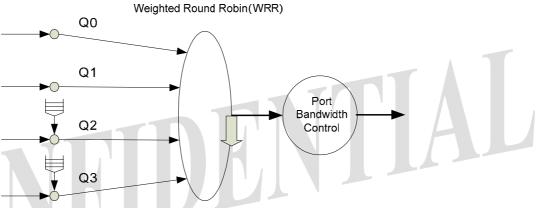

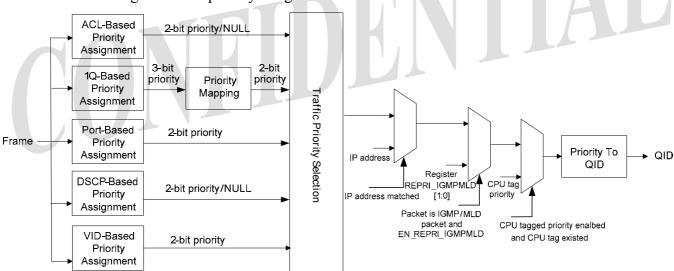

|    |                    | OS FUNCTION                                       |    |

|    |                    | Bandwidth Control                                 |    |

|    | 8.6.1.1            |                                                   |    |

|    | 8.6.1.2            |                                                   |    |

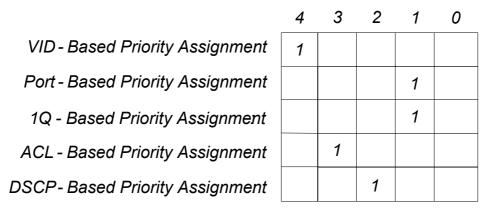

|    |                    | Priority Assignment                               | 50 |

|    | 8.6.2.1            |                                                   |    |

|    | 8.6.2.2<br>8.6.2.3 |                                                   |    |

|    | 8.6.2.4            |                                                   |    |

|    | 8.6.2.5            |                                                   |    |

|    | 8.6.2.0            |                                                   |    |

|    | 8.6.2.7            |                                                   |    |

|    | 8.6.2.8            |                                                   |    |

|    | 8.6.2.9            |                                                   |    |

|    | 8.6.2.             | 10 Packet Priority Selection                      | 5  |

|    | 8.6.2.             | 11 Priority Controlled By Strapping Pin           | 59 |

|    | 8.7. Lo            | OOKUP TABLE FUNCTION                              | 60 |

|    | 8.7.1.             | Function Description                              | 6  |

|    | 8.7.2.             | Address Search, Learning, and Aging               | 6  |

|    | <i>8.7.3</i> .     | Lookup and CAM Table Definition                   | 62 |

|    | 8.7.3.1            | Lookup Table Access                               | 62 |

|    | 8.7.3.2            |                                                   |    |

|    |                    | IBS Function                                      | 63 |

|    | 8.8.1.             | MIB Counter Description                           | 6. |

|    | 8.8.2.             | MIB Counter Enable/Clear                          | 6. |

|    | <i>8.8.3</i> .     | MIB Counter Timeout                               | 6  |

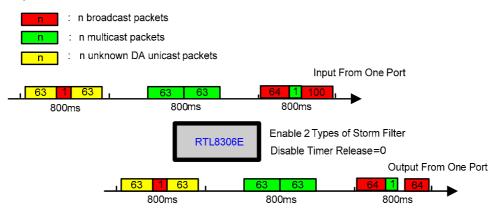

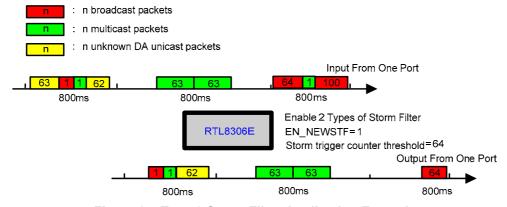

|    | 8.9. ST            | ORM FILTER FUNCTION                               | 64 |

|    | 8.9.1.             | Definition                                        | 6  |

|    |                    | Type 1 Storm Filter                               |    |

|    |                    |                                                   |    |

| <i>8.9.3</i> .   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 8.10.            | CPU INTERRUPT FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

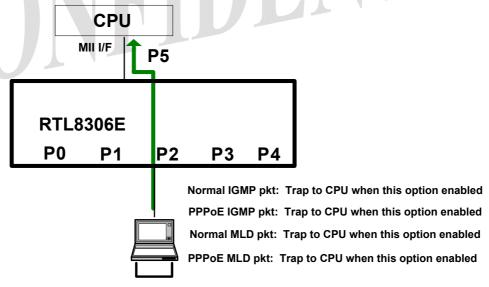

|                  | IGMP & MLD Snooping Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

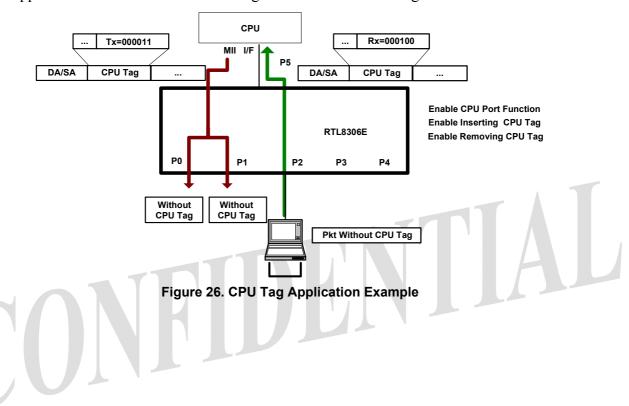

| 8.12.            | CPU TAG FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 |

| 8.13.            | IEEE 802.1x Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 8.13.1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 8.13.2           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                  | IEEE 802.1D Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

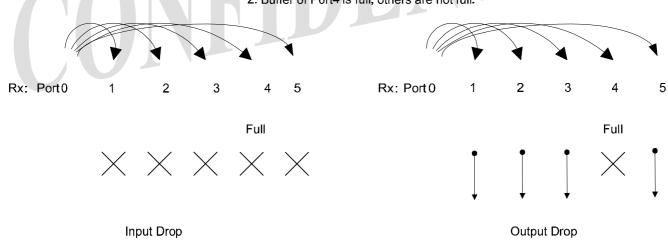

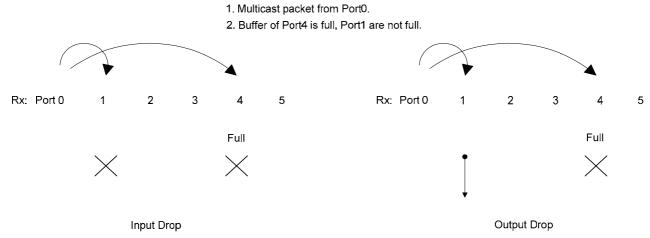

|                  | INPUT & OUTPUT DROP FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|                  | Port Mirroring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

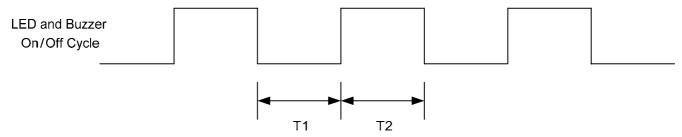

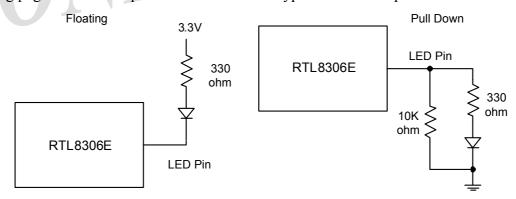

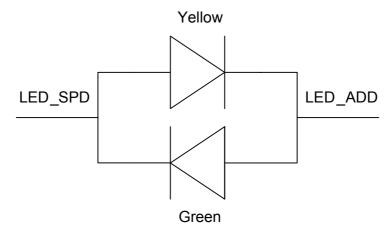

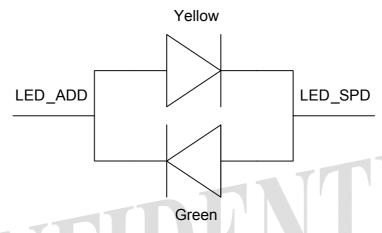

|                  | LED FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 8.17.1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 8.17.2           | O Company of the comp |    |

|                  | Green Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|                  | ENERGY-EFFICIENT ETHERNET (EEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                  | WAKE-ON-LAN (WOL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|                  | CPU PORT TRAFFIC RATE MONITOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 0.22.            | Cable Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 9. REGI          | STER DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80 |

| 9.1.             | REGISTER LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80 |

|                  | PHY 0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                  | PHY 0 Register 0 (Page 0, 1, 2, 3): Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 9.2.2.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 9.2.3.           | PHY 0 Register 2 (Page 0, 1, 2, 3): PHY Identifier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 9.2.4.           | PHY 0 Register 3 (Page 0, 1, 2, 3): PHY Identifier 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 9.2.5.           | PHY 0 Register 4 (Page 0, 1, 2, 3): Auto-Negotiation Advertisement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 9.2.6.           | PHY 0 Register 5 (Page 0, 1, 2, 3): Auto-Negotiation Link Partner Ability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 9.2.7.           | PHY 0 Register 16 (Page 0, 1, 2, 3): Global Control 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 9.2.8.           | PHY 0 Register 18 (Page 0, 1): Global Control 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 9.2.9.           | PHY 0 Register 19 (Page 0, 1): Global Control 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 9.2.10           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88 |

| 9.2.11           | . PHY 0 Register 24 (Page 0, 1): Port 0 Control Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89 |