## **S-19312 Series**

## AUTOMOTIVE, 125°C OPERATION, 36 V INPUT, 400 mA VOLTAGE REGULATOR WITH RESET FUNCTION

www.ablicinc.com

© ABLIC Inc., 2017 Rev.1.0\_01

The S-19312 Series, developed by using high-withstand voltage CMOS technology, is a positive voltage regulator with the reset function, which has high-withstand voltage and high-accuracy output voltage. This IC has a built-in low on-resistance output transistor which provides a small dropout voltage and a large output current. Also, a built-in overcurrent protection circuit to limit overcurrent of the output transistor and a built-in thermal shutdown circuit to limit heat are included. High heat radiation TO-252-5S(A) and HSOP-8A packages enable high-density mounting.

Caution This product can be used in vehicle equipment and in-vehicle equipment. Before using the product in the purpose, contact to ABLIC Inc. is indispensable.

#### ■ Features

#### Regulator block

• Output voltage: 3.0 V to 5.3 V, selectable in 0.1 V step

• Input voltage: 4.0 V to 36.0 V

• Output voltage accuracy:  $\pm 2.0\%$  (T<sub>i</sub> = -40°C to +150°C)

Dropout voltage: 120 mV typ. (5.0 V output product, I<sub>OUT</sub> = 100 mA)

Output current: Possible to output 400 mA (V<sub>IN</sub> = V<sub>OUT(S)</sub> + 1.0 V)<sup>\*1</sup>

Input and output capacitors: A ceramic capacitor of 2.2 μF or more can be used.

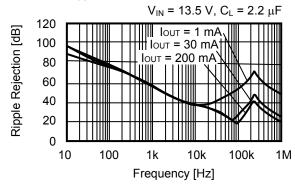

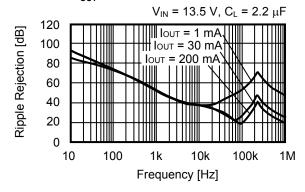

• Ripple rejection: 70 dB typ. (f = 100 Hz)

Built-in overcurrent protection circuit: Limits overcurrent of output transistor.

Built-in thermal shutdown circuit: Detection temperature 170°C typ.

#### **Detector block**

Detection voltage:

Detection voltage accuracy:

2.6 V to 5.0 V, selectable in 0.1 V step

±100 mV (T<sub>i</sub> = -40°C to +150°C)

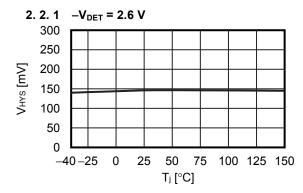

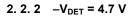

• Hysteresis width: 0.12 V min.

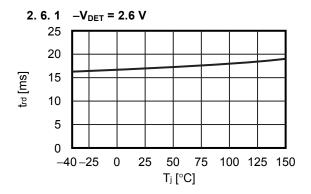

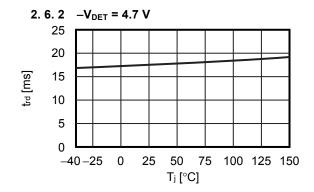

• Release delay time: 18 ms typ.  $(C_{DLY} = 47 \text{ nF})$

Output form:

Nch open-drain output (Built-in pull-up resistor)

#### Overall

• Current consumption: During operation: 60  $\mu$ A typ., 95  $\mu$ A max. ( $T_i = -40^{\circ}$ C to +150°C)

• Operation temperature range:  $Ta = -40^{\circ}C \text{ to } +125^{\circ}C$

• Lead-free (Sn 100%), halogen-free

Withstand 45 V load dump

AEC-Q100 qualified<sup>\*2</sup>

- \*1. Please make sure that the loss of the IC will not exceed the power dissipation when the output current is large.

- \*2. Contact our sales office for details.

#### ■ Applications

- Constant-voltage power supply and reset circuit for automotive electric component

- For automotive use (engine, transmission, suspension, ABS, related-devices for EV / HEV / PHEV, etc.)

#### Packages

- TO-252-5S(A)

- HSOP-8A

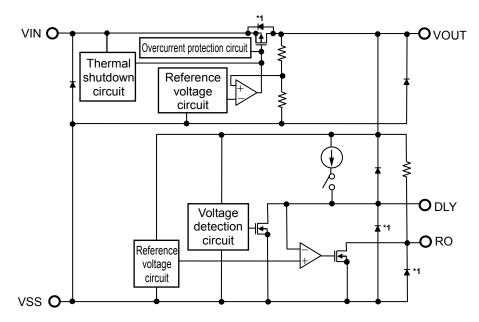

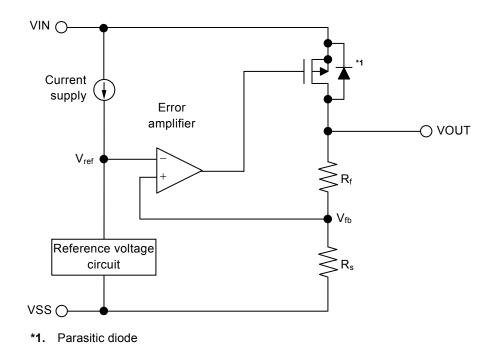

## ■ Block Diagram

\*1. Parasitic diode

Figure 1

#### ■ AEC-Q100 Qualified

This IC supports AEC-Q100 for operation temperature grade 1. Contact our sales office for details of AEC-Q100 reliability specification.

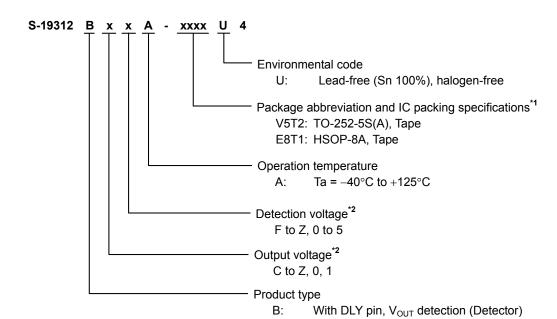

#### **■ Product Name Structure**

Users can select the output voltage and detection voltage for the S-19312 Series. Refer to "1. Product name" regarding the contents of product name, "3. Packages" regarding the package drawings and "4. Product name list" for details of product names.

#### 1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "2. Product option list".

#### 2. Product option list

#### 2. 1 Output voltage

| Set Output<br>Voltage | Symbol |

|-----------------------|--------|

| 5.3 V                 | С      |

| 5.2 V                 | D      |

| 5.1 V                 | E      |

| 5.0 V                 | F      |

| 4.9 V                 | G      |

| 4.8 V                 | Н      |

| 4.7 V                 | J      |

| 4.6 V                 | K      |

| 4.5 V                 | L      |

| 4.4 V                 | М      |

| 4.3 V                 | N      |

| 4.2 V                 | Р      |

| Set Output<br>Voltage | Symbol |

|-----------------------|--------|

| 4.1 V                 | Q      |

| 4.0 V                 | R      |

| 3.9 V                 | S      |

| 3.8 V                 | Т      |

| 3.7 V                 | U      |

| 3.6 V                 | V      |

| 3.5 V                 | W      |

| 3.4 V                 | Χ      |

| 3.3 V                 | Υ      |

| 3.2 V                 | Ζ      |

| 3.1 V                 | 0      |

| 3.0 V                 | 1      |

2. 2 Detection voltage

| Set Detection<br>Voltage | Symbol |

|--------------------------|--------|

| 5.0 V                    | F      |

| 4.9 V                    | G      |

| 4.8 V                    | Н      |

| 4.7 V                    | J      |

| 4.6 V                    | K      |

| 4.5 V                    | L      |

| 4.4 V                    | М      |

| 4.3 V                    | N      |

| 4.2 V                    | Р      |

| 4.1 V                    | Q      |

| 4.0 V                    | R      |

| 3.9 V                    | S      |

| 3.8 V                    | Т      |

| Symbol |

|--------|

| U      |

| V      |

| W      |

| Х      |

| Υ      |

| Z      |

| 0      |

| 1      |

| 2      |

| 3      |

| 4      |

| 5      |

|        |

**Remark** Set output voltage  $\geq$  Set detection voltage + 0.3 V

#### 3. Packages

Table 1 Package Drawing Codes

| Package Name | Dimension    | Tape         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| TO-252-5S(A) | VA005-A-P-SD | VA005-A-C-SD | VA005-A-R-SD | VA005-A-L-SD |

| HSOP-8A      | FH008-A-P-SD | FH008-A-C-SD | FH008-A-R-SD | FH008-A-L-SD |

#### 4. Product name list

Table 2

| Output Voltage             | Detection Voltage                 | TO-252-5S(A)       | HSOP-8A            |

|----------------------------|-----------------------------------|--------------------|--------------------|

| $3.3~\textrm{V}\pm2.0\%$   | $2.9~V \pm 0.1~V$                 | S-19312BY2A-V5T2U4 | S-19312BY2A-E8T1U4 |

| $5.0~\textrm{V} \pm 2.0\%$ | $2.9~\textrm{V}\pm0.1~\textrm{V}$ | S-19312BF2A-V5T2U4 | S-19312BF2A-E8T1U4 |

| 5.0 V ± 2.0%               | 4.2 V ± 0.1 V                     | S-19312BFPA-V5T2U4 | S-19312BFPA-E8T1U4 |

| 5.0 V ± 2.0%               | 4.6 V ± 0.1 V                     | S-19312BFKA-V5T2U4 | S-19312BFKA-E8T1U4 |

**Remark** Please contact our sales office for products with specifications other than the above.

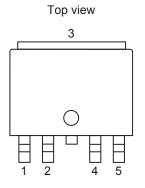

## **■** Pin Configurations

#### 1. TO-252-5S(A)

| Table 3 |                            |                                                    |  |  |  |

|---------|----------------------------|----------------------------------------------------|--|--|--|

| Pin No. | Pin No. Symbol Description |                                                    |  |  |  |

| 1       | VOUT                       | Voltage output pin (Regulator block)               |  |  |  |

| 2       | DLY                        | Connection pin for delay time adjustment capacitor |  |  |  |

| 3       | VSS                        | GND pin                                            |  |  |  |

| 4       | RO                         | Reset output pin                                   |  |  |  |

| 5       | VIN                        | Voltage input pin (Regulator block)                |  |  |  |

Figure 2

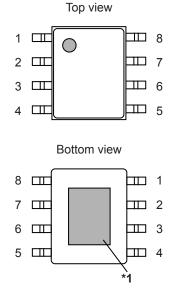

#### 2. HSOP-8A

| Table 4 |                            |                                                    |  |  |  |  |

|---------|----------------------------|----------------------------------------------------|--|--|--|--|

| Pin No. | Pin No. Symbol Description |                                                    |  |  |  |  |

| 1       | VOUT                       | Voltage output pin (Regulator block)               |  |  |  |  |

| 2       | NC <sup>*2</sup>           | No connection                                      |  |  |  |  |

| 3       | VSS                        | GND pin                                            |  |  |  |  |

| 4       | DLY                        | Connection pin for delay time adjustment capacitor |  |  |  |  |

| 5       | RO                         | Reset output pin                                   |  |  |  |  |

| 6       | NC <sup>*2</sup>           | No connection                                      |  |  |  |  |

| 7       | NC <sup>*2</sup>           | No connection                                      |  |  |  |  |

| 8       | VIN                        | Voltage input pin (Regulator block)                |  |  |  |  |

Figure 3

- **\*1.** Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2. The NC pin is electrically open.

The NC pin can be connected to the VDD pin or the VSS pin.

## ■ Absolute Maximum Ratings

Table 5

$(T_i = -40^{\circ}C \text{ to } +150^{\circ}C \text{ unless otherwise specified})$

| Item                          | Symbol           | Absolute Maximum Rating                                   | Unit |

|-------------------------------|------------------|-----------------------------------------------------------|------|

| VIN pin voltage               | $V_{IN}$         | $V_{SS}-0.3$ to $V_{SS}+45.0$                             | V    |

| VOUT pin voltage              | V <sub>OUT</sub> | $V_{SS}-0.3$ to $V_{IN}+0.3 \leq V_{SS}+7.0$              | V    |

| DLY pin voltage               | $V_{DLY}$        | $V_{SS} - 0.3 \text{ to } V_{OUT} + 0.3 \le V_{SS} + 7.0$ | V    |

| RO pin voltage                | $V_{RO}$         | $V_{SS} - 0.3 \text{ to } V_{OUT} + 0.3 \le V_{SS} + 7.0$ | V    |

| Output current                | I <sub>OUT</sub> | 520                                                       | mA   |

| Junction temperature          | T <sub>i</sub>   | -40 to +150                                               | °C   |

| Operation ambient temperature | $T_{opr}$        | -40 to +125                                               | °C   |

| Storage temperature           | T <sub>stg</sub> | -40 to +150                                               | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

#### **■** Thermal Resistance Value

Table 6

| Item                        | Symbol        | Condit       | ion     | Min. | Тур. | Max. | Unit |

|-----------------------------|---------------|--------------|---------|------|------|------|------|

|                             |               |              | Board A | -    | 86   | -    | °C/W |

|                             |               |              | Board B | -    | 60   | 1    | °C/W |

| Junction-to-ambient thermal |               | TO-252-5S(A) | Board C | _    | 38   | -    | °C/W |

|                             |               |              | Board D | -    | 31   | 1    | °C/W |

|                             | $\theta_{JA}$ |              | Board E | -    | 28   | 1    | °C/W |

| resistance*1                | OJA           | HSOP-8A      | Board A | _    | 104  | _    | °C/W |

|                             |               |              | Board B | _    | 74   | _    | °C/W |

|                             |               |              | Board C | -    | 39   | _    | °C/W |

|                             |               |              | Board D | _    | 37   | _    | °C/W |

|                             |               |              | Board E | _    | 31   | _    | °C/W |

<sup>\*1.</sup> Test environment: compliance with JEDEC STANDARD JESD51-2A

Remark Refer to "■ Power Dissipation" and "Test Board" for details.

#### **■** Electrical Characteristics

#### 1. Regulator block

Table 7

(V<sub>IN</sub> = 13.5 V,  $T_j$  = -40°C to +150°C unless otherwise specified)

| Item                                   | Symbol                                                  | Condition                                                                                                                         | Min.                       | Тур.                | Max.                          | Unit | Test<br>Circuit |

|----------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|-------------------------------|------|-----------------|

| Output voltage*1                       | V <sub>OUT(E)</sub>                                     | V <sub>IN</sub> = 13.5 V, I <sub>OUT</sub> = 30 mA                                                                                | V <sub>OUT(S)</sub> - 2.0% | V <sub>OUT(S)</sub> | V <sub>OUT(S)</sub><br>+ 2.0% | V    | 1               |

| Output current*2                       | Гоит                                                    | $V_{IN} \ge V_{OUT(S)} + 1.0 \text{ V}$                                                                                           | 400 <sup>*4</sup>          | _                   | _                             | mA   | 2               |

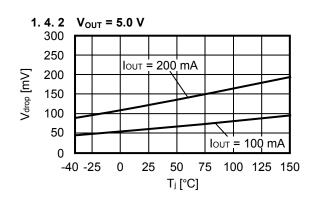

| Dropout voltage <sup>*3</sup>          | V                                                       | $I_{OUT}$ = 100 mA, Ta = +25°C,<br>$V_{OUT(S)}$ = 3.0 V to 5.3 V                                                                  | _                          | 120                 | 200                           | mV   | 1               |

| Dropout voltage                        | $V_{drop}$                                              | $I_{OUT}$ = 200 mA, Ta = +25°C,<br>$V_{OUT(S)}$ = 3.0 V to 5.3 V                                                                  | -                          | 240                 | 400                           | mV   | 1               |

| Line regulation                        | $\frac{\Delta V_{OUT1}}{\Delta V_{IN} \bullet V_{OUT}}$ | $V_{OUT(S)} + 1.0 \text{ V} \le V_{IN} \le 36.0 \text{ V},$<br>$I_{OUT} = 30 \text{ mA}, \text{ Ta} = +25^{\circ}\text{C}$        | _                          | 0.02                | 0.10                          | %/V  | 1               |

| Load regulation                        | $\Delta V_{OUT2}$                                       | $V_{\text{IN}} = 13.5 \text{ V}, \ 100 \ \mu\text{A} \leq I_{\text{OUT}} \leq 100 \ \text{mA},$ $\text{Ta} = +25^{\circ}\text{C}$ | -                          | 20                  | 40                            | mV   | 1               |

| Input voltage                          | $V_{IN}$                                                | _                                                                                                                                 | 4.0                        | _                   | 36.0                          | ٧    | _               |

| Ripple rejection                       | RR                                                      | $V_{IN}$ = 13.5 V, $I_{OUT}$ = 30 mA,<br>f = 100 Hz, $\Delta V_{rip}$ = 1.0 $V_{p-p}$                                             | _                          | 70                  | -                             | dB   | 3               |

| Short-circuit current                  | I <sub>short</sub>                                      | $V_{IN} = 13.5 \text{ V}, V_{OUT} = 0 \text{ V},$ $Ta = +25^{\circ}C$                                                             | _                          | 105                 | ı                             | mA   | 2               |

| Thermal shutdown detection temperature | T <sub>SD</sub>                                         | Junction temperature                                                                                                              | _                          | 170                 | _                             | °C   | _               |

| Thermal shutdown release temperature   | T <sub>SR</sub>                                         | Junction temperature                                                                                                              | _                          | 135                 | -                             | °C   | _               |

<sup>\*1.</sup> V<sub>OUT(S)</sub>: Set output voltage

Due to limitation of the power dissipation, this value may not be satisfied. Attention should be paid to the power dissipation when the output current is large.

This specification is guaranteed by design.

V<sub>OUT(E)</sub>: Actual output voltage

Output voltage when fixing I<sub>OUT</sub> (= 30 mA) and inputting 13.5 V

<sup>\*2.</sup> The output current at which the output voltage becomes 95% of V<sub>OUT(E)</sub> after gradually increasing the output current.

<sup>\*3.</sup>  $V_{drop} = V_{IN1} - (V_{OUT3} \times 0.98)$

$V_{OUT3}$  is the output voltage when  $V_{IN} = V_{OUT(S)} + 1.0 \text{ V}$ .

$V_{\text{IN1}}$  is the input voltage at which the output voltage becomes 98% of  $V_{\text{OUT3}}$  after gradually decreasing the input voltage.

<sup>\*4.</sup> The output current can be at least this value.

#### 2. Detector block

#### Table 8

( $V_{IN}$  = 13.5 V,  $T_i$  = -40°C to +150°C unless otherwise specified)

| Item                                 | Symbol             | Condition                                                                                                  | Min.                          | Тур.                 | Max.                       | Unit        | Test<br>Circuit |

|--------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|----------------------------|-------------|-----------------|

| Detection voltage*1                  | -V <sub>DET</sub>  | -                                                                                                          | -V <sub>DET(S)</sub><br>- 0.1 | -V <sub>DET(S)</sub> | -V <sub>DET(S)</sub> + 0.1 | ٧           | 4               |

| Hysteresis width                     | $V_{HYS}$          | _                                                                                                          | 120                           | 150                  | -                          | mV          | 4               |

| Reset output voltage "H"             | V <sub>ROH</sub>   | -                                                                                                          | $V_{OUT(S)} \times 0.9$       | 1                    | _                          | <b>&gt;</b> | 4               |

| Reset output voltage "L"             | V <sub>ROL</sub>   | $\begin{split} V_{OUT} \geq 1.0 \ V, \ R_{ext} \geq 3 \ k\Omega, \\ Connect \ to \ VOUT \ pin \end{split}$ | _                             | 0.2                  | 0.4                        | <b>V</b>    | 4               |

| Reset pull-up resistance             | R <sub>RO</sub>    | VOUT pin internal resistance                                                                               | 20                            | 30                   | 45                         | kΩ          | _               |

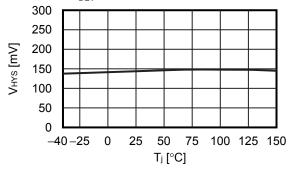

| Reset output current                 | I <sub>RO</sub>    | $V_{RO} = 0.4 \text{ V}, V_{OUT} = -V_{DET(S)} - 0.1 \text{ V}$                                            | 3.0                           | ı                    |                            | mA          | 5               |

| Lower reset timing threshold voltage | $V_{DRL}$          | -                                                                                                          | 0.2                           | 0.3                  | 0.4                        | <b>V</b>    | 6               |

| Upper timing threshold voltage       | $V_{DU}$           | -                                                                                                          | 1.5                           | 1.9                  | 2.3                        | <b>V</b>    | 6               |

| Charge current                       | I <sub>D,cha</sub> | V <sub>DLY</sub> = 1.0 V                                                                                   | 2.0                           | 5.0                  | 8.0                        | μΑ          | 6               |

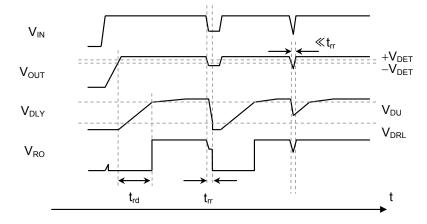

| Release delay time*2                 | t <sub>rd</sub>    | C <sub>DLY</sub> = 47 nF                                                                                   | 11                            | 18                   | 25                         | ms          | 4               |

| Reset reaction time*3                | t <sub>rr</sub>    | C <sub>DLY</sub> = 47 nF                                                                                   | -                             | -                    | 50                         | μS          | 4               |

<sup>\*1. -</sup>V<sub>DET</sub>: Actual detection voltage, -V<sub>DET(S)</sub>: Set detection voltage

#### 3. Overall

#### Table 9

$(V_{IN} = 13.5 \text{ V}, T_i = -40^{\circ}\text{C} \text{ to } +150^{\circ}\text{C} \text{ unless otherwise specified})$

|                                      |                  | (1111 13:3 1,                                     |      |      | arnoco ot |      | 000007          |

|--------------------------------------|------------------|---------------------------------------------------|------|------|-----------|------|-----------------|

| Item                                 | Symbol           | Condition                                         | Min. | Тур. | Max.      | Unit | Test<br>Circuit |

| Current consumption during operation | I <sub>SS1</sub> | V <sub>IN</sub> = 13.5 V, I <sub>OUT</sub> = 0 mA | -    | 60   | 95        | μА   | 7               |

8

<sup>\*2.</sup> The time period from when  $V_{OUT}$  changes to  $-V_{DET(S)} - 0.15 \text{ V} \rightarrow V_{OUT(S)}$  to when  $V_{RO}$  reaches  $V_{OUT}$  / 2.

<sup>\*3.</sup> The time period from when  $V_{OUT}$  changes to  $V_{OUT(S)} \rightarrow -V_{DET(S)} - 0.15 \text{ V}$  to when  $V_{RO}$  reaches  $V_{OUT}$  / 2.

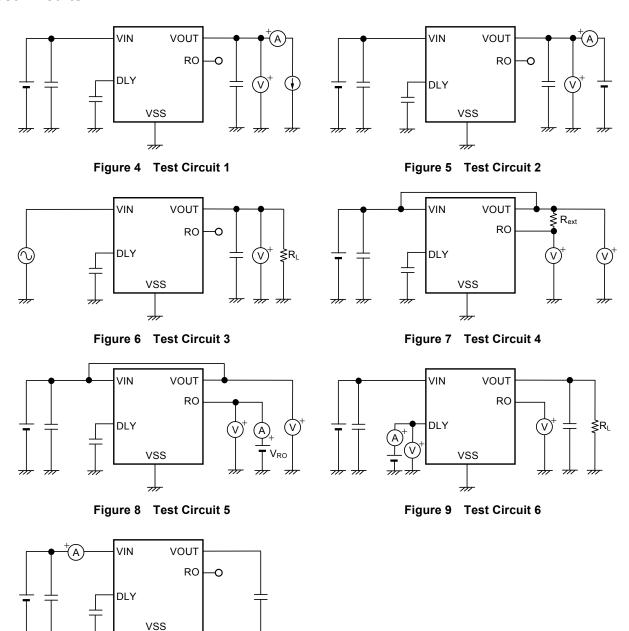

#### **■** Test Circuits

Figure 10 Test Circuit 7

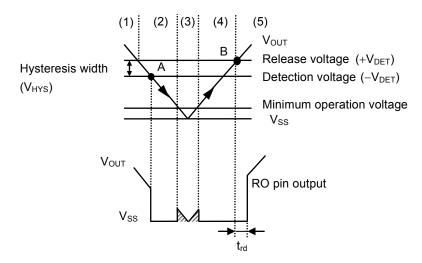

# ■ Timing Chart

Figure 11 Example of Detector Operation

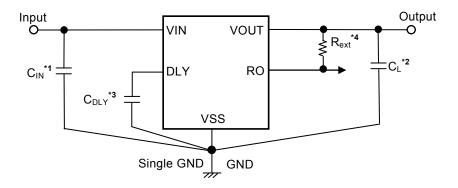

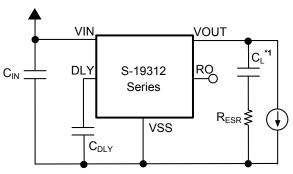

#### ■ Standard Circuit

Figure 12

- \*1. C<sub>IN</sub> is a capacitor for stabilizing the input.

- \*2.  $C_L$  is a capacitor for stabilizing the output. A ceramic capacitor of 2.2  $\mu F$  or more can be used.

- \*3. C<sub>DLY</sub> is the delay time adjustment capacitor.

- \*4. R<sub>ext</sub> is the external pull-up resistor for the reset output pin.

Connection of the external pull-up resistor is not absolutely essential since the S-19312 Series has a built-in pull-up resistor.

Caution The above connection diagram and constants will not guarantee successful operation. Perform thorough evaluation using an actual application to set the constants.

#### ■ Condition of Application

$\begin{array}{lll} \mbox{Input capacitor } (C_{\text{IN}}) & : 2.2 \ \mu \mbox{F or more} \\ \mbox{Output capacitor } (C_{\text{L}}) & : 2.2 \ \mu \mbox{F or more} \\ \mbox{ESR of output capacitor} & : 50 \ \Omega \ \mbox{or less} \\ \mbox{Delay time adjustment capacitor } (C_{\text{DLY}}) & : 1.0 \ \mbox{nF or more} \\ \mbox{External pull-up resistor } (R_{\text{ext}}) & : 3 \ \mbox{k} \Omega \ \mbox{or more} \\ \end{array}$

Caution Generally a series regulator may cause oscillation, depending on the selection of external parts.

Confirm that no oscillation occurs in the application for which the above capacitors are used.

## ■ Selection of Input and Output Capacitors (C<sub>IN</sub>, C<sub>L</sub>)

The S-19312 Series requires  $C_L$  between the VOUT pin and the VSS pin for phase compensation. Operation is stabilized by a ceramic capacitor with an output capacitance of 2.2  $\mu F$  or more over the entire temperature range. When using an OS capacitor, a tantalum capacitor, or an aluminum electrolytic capacitor, the capacitance must be 2.2  $\mu F$  or more, and the ESR must be 50  $\Omega$  or less.

The values of output overshoot and undershoot, which are transient response characteristics, vary depending on the value of the output capacitor.

The required value of capacitance for the input capacitor differs depending on the application.

Caution Define the capacitance of C<sub>IN</sub> and C<sub>L</sub> by sufficient evaluation including the temperature characteristics under the actual usage conditions.

## ■ Selection of Delay Time Adjustment Capacitor (C<sub>DLY</sub>)

In the S-19312 Series, the delay time adjustment capacitor ( $C_{DLY}$ ) is necessary between the DLY pin and the VSS pin to adjust the release delay time ( $t_{rd}$ ) of the detector.

The set release delay time  $(t_{rd(S)})$ , is calculated by using following equation.

The release delay time  $(t_{rd})$  at the time of the condition of  $C_{DLY}$  = 47 nF is shown in " Electrical Characteristics".

$$t_{\text{rd}(S)} \, [\text{ms}] = t_{\text{rd}} \, [\text{ms}] \times \, \frac{C_{\text{DLY}} \, [\text{nF}]}{47 \, [\text{nF}]}$$

- Caution 1. The above equation will not guarantee successful operation. Perform thorough evaluation including the temperature characteristics using an actual application to set the constants.

- 2. Mounted board layout should be made in such a way that no current flows into or flows from the DLY pin since the impedance of the DLY pin is high, otherwise correct delay time may not be provided.

- 3. Select C<sub>DLY</sub> whose leakage current can be ignored against the built-in constant current. The leakage current may cause deviation in delay time and monitoring time. When the leakage current is larger than the built-in constant current, no release takes place.

#### ■ Explanation of Terms

#### 1. Regulator block

#### 1. 1 Low dropout voltage regulator

This voltage regulator has the low dropout voltage due to its built-in low on-resistance transistor.

#### 1. 2 Output voltage (Vout)

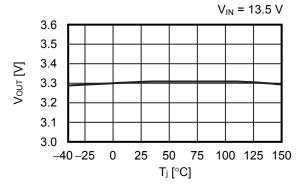

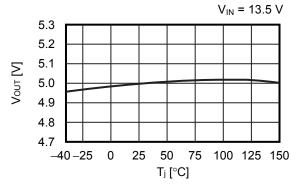

The accuracy of the output voltage is ensured at ±2.0% under specified conditions of fixed input voltage\*1, fixed output current, and fixed temperature.

\*1. Differs depending on the product.

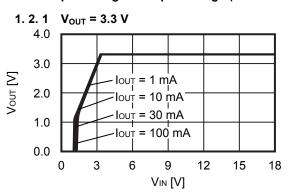

Caution If the above conditions change, the output voltage value may vary and exceed the accuracy range of the output voltage. Refer to "1. Regulator block" in "■ Electrical Characteristics" and "1. Regulator block" in "■ Characteristics (Typical Data)" for details.

1. 3 Line regulation

$$\left(\frac{\Delta V_{OUT1}}{\Delta V_{IN} \bullet V_{OUT}}\right)$$

Indicates the dependency of the output voltage against the input voltage. That is, the value shows how much the output voltage changes due to a change in the input voltage after fixing output current constant.

#### 1. 4 Load regulation (ΔV<sub>OUT2</sub>)

Indicates the dependency of the output voltage against the output current. That is, the value shows how much the output voltage changes due to a change in the output current after fixing input voltage constant.

#### 1. 5 Dropout voltage (V<sub>drop</sub>)

Indicates the difference between input voltage ( $V_{IN1}$ ) and the output voltage when; decreasing input voltage ( $V_{IN}$ ) gradually until the output voltage has dropped out to the value of 98% of output voltage ( $V_{OUT3}$ ), which is at  $V_{IN} = V_{OUT(S)} + 1.0 \text{ V}$ .

$$V_{drop} = V_{IN1} - (V_{OUT3} \times 0.98)$$

#### 2. Detector block

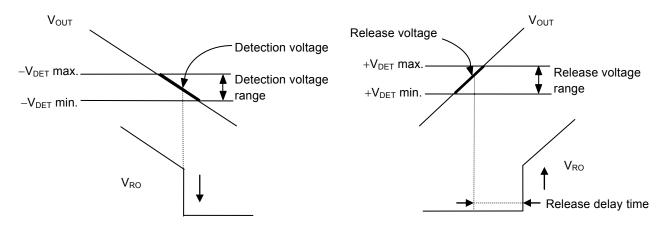

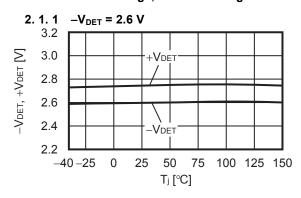

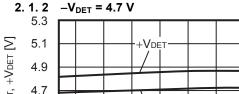

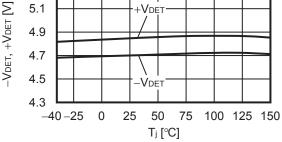

#### 2. 1 Detection voltage (-V<sub>DET</sub>)

The detection voltage is a voltage at which the output of the RO pin turns to "L". The detection voltage varies slightly among products of the same specification. The variation of detection voltage between the specified minimum ( $-V_{DET}$  min.) and the maximum ( $-V_{DET}$  max.) is called the detection voltage range (Refer to **Figure 13**).

#### 2. 2 Release voltage (+V<sub>DET</sub>)

The release voltage is a voltage at which the output of the RO pin turns to "H". The release voltage varies slightly among products of the same specification. The variation of release voltage between the specified minimum ( $+V_{DET}$  min.) and the maximum ( $+V_{DET}$  max.) is called the release voltage range (Refer to **Figure 14**). This value is calculated from the actual detection voltage ( $-V_{DET}$ ) of a product and the hysteresis width ( $V_{HYS}$ ), and is  $+V_{DET} = -V_{DET} + V_{HYS}$ .

Figure 13 Detection Voltage

Figure 14 Release Voltage

#### 2. 3 Hysteresis width (V<sub>HYS</sub>)

The hysteresis width is the voltage difference between the detection voltage and the release voltage. Setting the hysteresis width between the detection voltage and the release voltage prevents malfunction caused by noise on the VOUT pin voltage (V<sub>OUT</sub>).

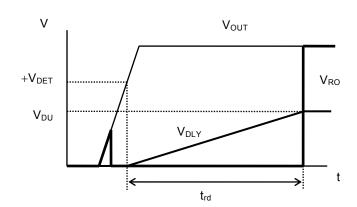

#### 2. 4 Release delay time (t<sub>rd</sub>)

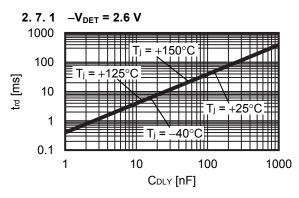

The release delay time is the time period from when  $V_{OUT}$  exceeds the release voltage (+ $V_{DET}$ ) to when the RO pin output inverts (Refer to **Figure 15**), and this value changes according to the delay time adjustment capacitor ( $C_{DLY}$ ).  $t_{rd}$  is determined by a built-in constant current which charges  $C_{DLY}$ , the charge detection threshold of the DLY pin, and the capacitance of  $C_{DLY}$ . It is calculated by using the following equation.

$$t_{rd} = C_{DLY} \times \frac{V_{DU}}{I_{D,cha}}$$

14

Figure 15 Release Delay Time

ABLIC Inc.

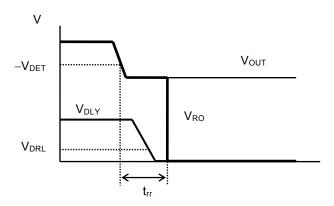

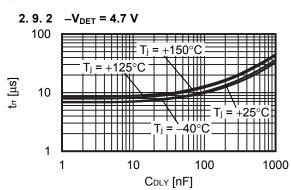

#### 2. 5 Reset reaction time (t<sub>rr</sub>)

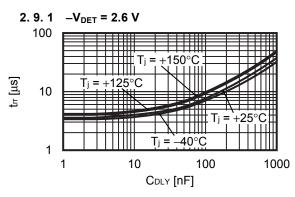

The reset reaction time is the time period from when  $V_{OUT}$  falls below the detection voltage  $(-V_{DET})$  to when the RO pin output inverts (Refer to **Figure 16**). Since  $t_{rr}$  depends on the reaction time of internal circuit and the discharge time of  $C_{DLY}$ , it becomes longer if the capacitance of  $C_{DLY}$  becomes larger. Refer to "2. 9 Reset reaction time vs. Capacitance for delay time adjustment capacitor" in "

Characteristics (Typical Data)".

Figure 16 Reset Reaction Time

#### Operation

#### 1. Regulator block

#### 1. 1 Basic operation

Figure 17 shows the block diagram of the regulator in the S-19312 Series.

The error amplifier compares the reference voltage ( $V_{ref}$ ) with feedback voltage ( $V_{fb}$ ), which is the output voltage resistance-divided by feedback resistors ( $R_s$  and  $R_f$ ). It supplies the gate voltage necessary to maintain the constant output voltage which is not influenced by the input voltage and temperature change, to the output transistor.

Figure 17

#### 1. 2 Output transistor

In the S-19312 Series, a low on-resistance P-channel MOS FET is used as the output transistor.

Be sure that  $V_{OUT}$  does not exceed  $V_{IN} + 0.3$  V to prevent the voltage regulator from being damaged due to reverse current flowing from the VOUT pin through a parasitic diode to the VIN pin, when the potential of  $V_{OUT}$  became higher than  $V_{IN}$ .

16 ABLIC Inc.

#### 1. 3 Overcurrent protection circuit

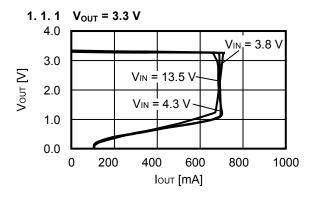

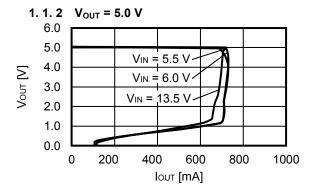

The S-19312 Series includes an overcurrent protection circuit which having the characteristics shown in "1. 1 Output voltage vs. Output current (When load current increases) ( $Ta = +25^{\circ}$ C)" of "1. Regulator block" in " Characteristics (Typical Data)", in order to limit an excessive output current and overcurrent of the output transistor due to short-circuiting between the VOUT pin and the VSS pin. The current when the output pin is short-circuited ( $I_{short}$ ) is internally set at approx. 105 mA typ., and the load current when short-circuiting is limited based on this value. The output voltage restarts regulating if the output transistor is released from overcurrent status.

Caution This overcurrent protection circuit does not work as for thermal protection. If this IC long keeps short circuiting, pay attention to the conditions of input voltage and load current so that, under the usage conditions including short circuit, the loss of the IC will not exceed power dissipation.

#### 1. 4 Thermal shutdown circuit

The S-19312 Series has a thermal shutdown circuit to limit self-heating. When the junction temperature rises to 170°C typ., the thermal shutdown circuit operates to stop regulating. After that, when the junction temperature drops to 135°C typ., the thermal shutdown circuit is released to restart regulating.

Due to self-heating of the S-19312 Series, if the thermal shutdown circuit starts operating, it stops regulating so that the output voltage drops. For this reason, self-heating is limited and the IC's temperature drops.

When the temperature drops, the thermal shutdown circuit is released to restart regulating, thus self-heating is generated again due to rising of the output voltage. Repeating this procedure makes the waveform of the VOUT pin output into a pulse-like form. This phenomenon continues unless decreasing either or both of the input voltage and the output current in order to reduce the internal power consumption, or decreasing the ambient temperature. Note that the product may suffer physical damage such as deterioration if the above phenomenon occurs continuously.

Table 10

| Thermal Shutdown Circuit | VOUT Pin Voltage      |

|--------------------------|-----------------------|

| Detect: 170°C typ.*1     | V <sub>SS</sub> level |

| Release: 135°C typ.*1    | Set value             |

<sup>\*1.</sup> Junction temperature

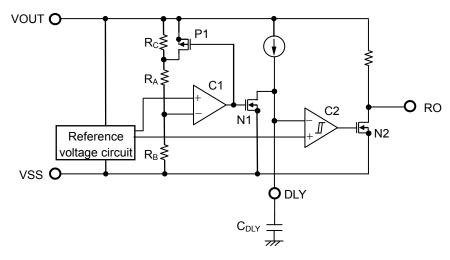

#### 2. Detector block

#### 2. 1 Basic operation

- (1) When the output voltage  $(V_{OUT})$  of the regulator is release voltage  $(+V_{DET})$  of the detector or higher, the Nch transistor (N1 and N2) are turned off and "H" is output to the RO pin. Since the Pch transistor (P1) is turned on, the input voltage to the comparator (C1) is  $\frac{R_B \bullet V_{OUT}}{R_A + R_B}$ .

- (2) Even if  $V_{OUT}$  decreases to  $+V_{DET}$  or lower, "H" is output to the RO pin when  $V_{OUT}$  is the detection voltage ( $-V_{DET}$ ) or higher. When  $V_{OUT}$  decreases to  $-V_{DET}$  (point A in **Figure 19**) or lower, N1 which is controlled by C1 is turned on, and  $C_{DLY}$  is discharged. If the DLY pin voltage ( $V_{DLY}$ ) decreases to the lower reset timing threshold voltage ( $V_{DRL}$ ) or lower, N2 of output stage of C2 is turned on, and then "L" is output to the RO pin. At this time, P1 is turned off, and the input voltage to C1 is  $\frac{R_B \bullet V_{OUT}}{R_A + R_B + R_C}$ .

- (3) If V<sub>OUT</sub> further decreases to the IC's minimum operation voltage or lower, the RO pin output is "H".

- (4) When  $V_{OUT}$  increases to the IC's minimum operation voltage or higher, "L" is output to the RO pin. Moreover, even if  $V_{OUT}$  exceeds  $-V_{DET}$ , the output is "L" when  $V_{OUT}$  is lower than  $+V_{DET}$ .

- (5) When  $V_{OUT}$  increases to  $+V_{DET}$  (point B in **Figure 19**) or higher, N1 is turned off and  $C_{DLY}$  is charged. N2 is turned off if  $V_{DLY}$  increases to the upper timing threshold voltage ( $V_{DU}$ ) or higher, and "H" is output to the RO pin.

Figure 18 Operation of Detector Block

Figure 19 Timing Chart of Detector Block

ABLIC Inc.

#### 2. 2 Delay circuit

When the output voltage  $(V_{OUT})$  of the regulator rises under the status that "L" is output to the RO pin, the reset release signal is output to the RO pin later than when  $V_{OUT}$  becomes  $+V_{DET}$ . The release delay time  $(t_{rd})$  changes according to  $C_{DLY}$ . Refer to " $\blacksquare$  Selection of Delay Time Adjustment Capacitor  $(C_{DLY})$ " for details.

Moreover, when  $V_{\text{OUT}}$  decreases to  $-V_{\text{DET}}$  or lower, the delay time of the same time length as the reset reaction time ( $t_{\text{rr}}$ ) occurs in the output to the RO pin. Refer to "2. **Detector block"** in "**Explanation of Terms"** for details.

If the time period from when  $V_{OUT}$  decreases to  $-V_{DET}$  or lower to when  $V_{OUT}$  increases to  $+V_{DET}$  or higher is significantly shorter compared to the length of  $t_{rr}$ ,  $V_{DLY}$  may not decrease to  $V_{DRL}$  or lower. In that case, "H" output remains in the RO pin.

Caution Since  $t_{rd}$  depends on the charge time of  $C_{DLY}$ ,  $t_{rd}$  may be shorter than the set value if the charge operation is initiated under the condition that a residual electric charge is left in  $C_{DLY}$ .

#### 2. 3 Output circuit

The output form of the RO pin is Nch open-drain. The RO pin can output a signal without an external pull-up resistor since it has a built-in resistor to pull up to the VOUT pin internally.

Do not connect to the pin other than VOUT pin when connecting an external pull-up resistor to the RO pin.

Caution Define the external pull-up resistance by sufficient evaluation including the temperature characteristics under the actual usage conditions.

#### ■ Precautions

- Wiring patterns for the VIN pin, the VOUT pin and GND should be designed so that the impedance is low. When mounting an output capacitor between the VOUT pin and the VSS pin (C<sub>L</sub>) and an input capacitor between the VIN pin and the VSS pin (C<sub>IN</sub>), the distance from the capacitors to these pins should be as short as possible.

- Note that generally the output voltage may increase when a series regulator is used at low load current (0.1 mA or less).

- Note that generally the output voltage may increase due to the leakage current from an output transistor when a series regulator is used at high temperature.

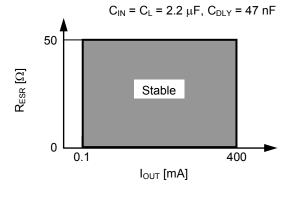

- Generally a series regulator may cause oscillation, depending on the selection of external parts. The following conditions are recommended for the S-19312 Series. However, be sure to perform sufficient evaluation under the actual usage conditions for selection, including evaluation of temperature characteristics. Refer to "4. Example of equivalent series resistance vs. Output current characteristics (Ta = +25°C)" in "■ Reference Data" for the equivalent series resistance (R<sub>ESR</sub>) of the output capacitor.

Input capacitor ( $C_{IN}$ ): 2.2  $\mu F$  or more Output capacitor ( $C_L$ ): 2.2  $\mu F$  or more

- In a series regulator, generally the values of overshoot and undershoot in the output voltage vary depending on the variation factors of power-on, power supply fluctuation and load fluctuation, or output capacitance.

Determine the conditions of the output capacitor after sufficiently evaluating the temperature characteristics of overshoot or undershoot in the output voltage with the actual device.

- The voltage regulator may oscillate when the impedance of the power supply is high and the input capacitance is small or an input capacitor is not connected.

- Overshoot may occur in the output voltage momentarily if the voltage is rapidly raised at power-on or when the power supply fluctuates. Sufficiently evaluate the output voltage at that time with the actual device.

- If the VOUT pin is steeply shorted with GND, a negative voltage exceeding the absolute maximum ratings may occur

to the VOUT pin due to resonance of the wiring inductance and the output capacitance in the application. The

negative voltage can be limited by inserting a protection diode between the VOUT pin and the VSS pin or inserting a

series resistor to the output capacitor.

- The application conditions for the input voltage, the output voltage, and the load current should not exceed the power dissipation.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- In determining the output current, attention should be paid to the output current value specified in **Table 7** in **"■ Electrical Characteristics"** and footnote \*4 of the table.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

## ■ Characteristics (Typical Data)

#### 1. Regulator block

1. 1 Output voltage vs. Output current (When load current increases) (Ta = +25°C)

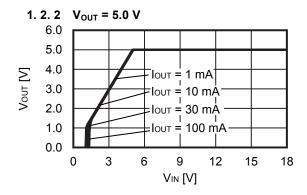

#### 1. 2 Output voltage vs. Input voltage (Ta = +25°C)

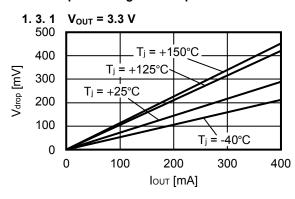

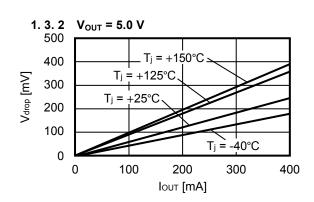

#### 1. 3 Dropout voltage vs. Output current

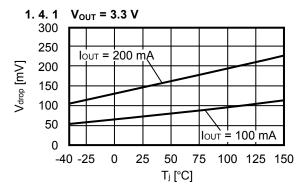

### 1. 4 Dropout voltage vs. Junction temperature

#### 1. 5 Output voltage vs. Junction temperature

#### 1. 5. 1 $V_{OUT} = 3.3 V$

#### 1. 5. 2 V<sub>OUT</sub> = 5.0 V

#### 1. 6 Ripple rejection (Ta = +25°C)

1. 6. 1  $V_{OUT} = 3.3 V$

#### 1. 6. 2 $V_{OUT} = 5.0 V$

#### 2. Detector block

#### 2. 1 Detection voltage, Release voltage vs. Junction temperature

#### 2. 2 Hysteresis width vs. Junction temperature

22 ABLIC Inc.

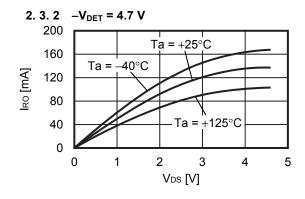

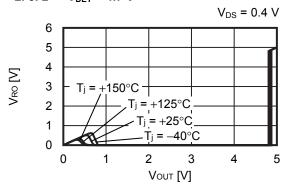

#### 2. 3 Nch transistor output current vs. V<sub>DS</sub>

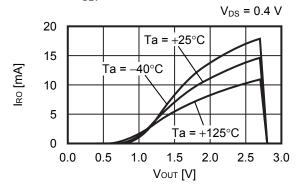

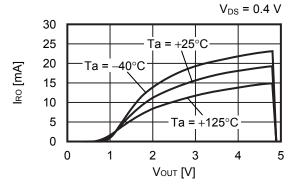

#### 2. 4 Nch transistor output current vs. Output voltage

2. 4. 1

$$-V_{DET} = 2.6 V$$

2. 4. 2

$$-V_{DET} = 4.7 \text{ V}$$

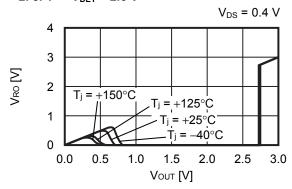

#### 2. 5 Nch transistor output voltage vs. Output voltage

2. 5. 1

$$-V_{DET} = 2.6 \text{ V}$$

2. 5. 2

$$-V_{DET} = 4.7 \text{ V}$$

**Remark** V<sub>DS</sub>: Drain-to-source voltage of the output transistor

#### 2. 6 Release delay time vs. Junction temperature

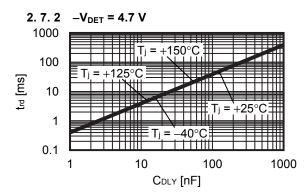

#### 2. 7 Release delay time vs. Capacitance for delay time adjustment capacitor

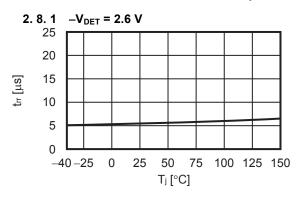

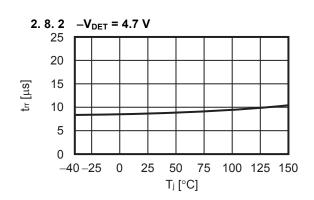

#### 2. 8 Reset reaction time vs. Junction temperature

#### 2. 9 Reset reaction time vs. Capacitance for delay time adjustment capacitor

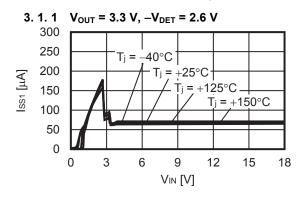

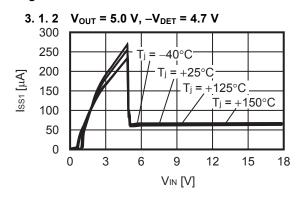

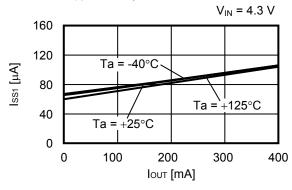

#### 3. Overall

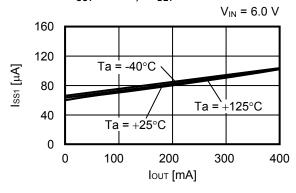

#### 3. 1 Current consumption during operation vs. input voltage

#### 3. 2 Current consumption during operation vs. Output current

3. 2. 1

$$V_{OUT} = 3.3 V, -V_{DET} = 2.6 V$$

3. 2. 2

$$V_{OUT} = 5.0 \text{ V}, -V_{DET} = 4.7 \text{ V}$$

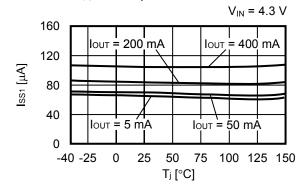

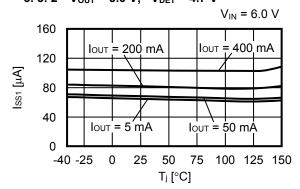

#### 3. 3 Current consumption during operation vs. Junction temperature

3. 3. 1  $V_{OUT} = 3.3 V, -V_{DET} = 2.6 V$

3. 3. 2

$$V_{OUT} = 5.0 \text{ V}, -V_{DET} = 4.7 \text{ V}$$

#### ■ Reference Data

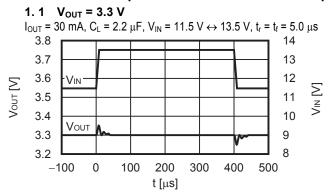

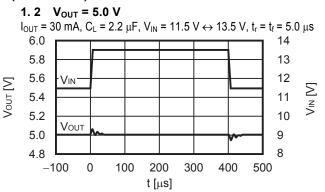

#### 1. Transient response characteristics when input ( $Ta = +25^{\circ}C$ )

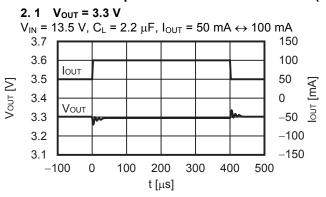

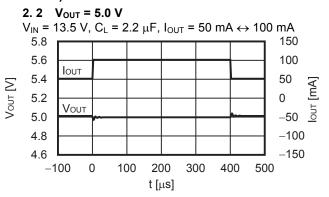

#### 2. Transient response characteristics of load (Ta = +25°C)

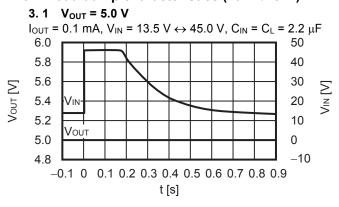

#### 3. Load dump characteristics ( $Ta = +25^{\circ}C$ )

### 4. Example of equivalent series resistance vs. Output current characteristics (Ta = +25°C)

\*1.  $C_L$ : Murata Manufacturing Co., Ltd. GCM31CR71H225K (2.2  $\mu$ F)

Figure 21

Figure 20

ABLIC Inc.

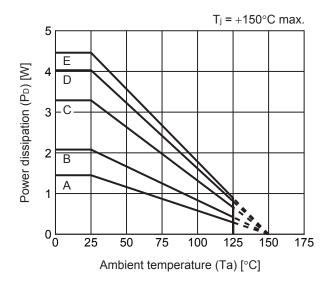

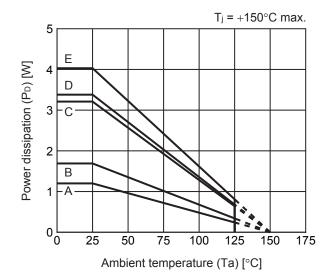

## **■** Power Dissipation

TO-252-5S(A)

| HSOP-8A |

|---------|

|---------|

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| Α     | 1.45 W                              |

| В     | 2.08 W                              |

| С     | 3.29 W                              |

| D     | 4.03 W                              |

| Е     | 4.46 W                              |

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| Α     | 1.20 W                              |

| В     | 1.69 W                              |

| С     | 3.21 W                              |

| D     | 3.38 W                              |

| Ē     | 4.03 W                              |

# **TO-252-5S** Test Board

## (1) Board A

| Item                        |   | Specification                               |  |

|-----------------------------|---|---------------------------------------------|--|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |  |

| Material                    |   | FR-4                                        |  |

| Number of copper foil layer |   | 2                                           |  |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |  |

|                             | 2 | -                                           |  |

|                             | 3 | -                                           |  |

|                             | 4 | 74.2 x 74.2 x t0.070                        |  |

| Thermal via                 |   | -                                           |  |

## (2) Board B

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (3) Board C

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm               |

No. TO252-5S-A-Board-SD-1.0

# **TO-252-5S** Test Board

## (4) Board D

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | -                                                      |

## (5) Board E

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm                          |

No. TO252-5S-A-Board-SD-1.0

# **HSOP-8A** Test Board

## (1) Board A

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 2                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | -                                           |

|                             | 3 | -                                           |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (2) Board B

| Item                        |   | Specification                               |  |

|-----------------------------|---|---------------------------------------------|--|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |  |

| Material                    |   | FR-4                                        |  |

| Number of copper foil layer |   | 4                                           |  |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |  |

|                             | 2 | 74.2 x 74.2 x t0.035                        |  |

|                             | 3 | 74.2 x 74.2 x t0.035                        |  |

|                             | 4 | 74.2 x 74.2 x t0.070                        |  |

| Thermal via                 |   | -                                           |  |

#### (3) Board C

| Item                        |   | Specification                               |  |

|-----------------------------|---|---------------------------------------------|--|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |  |

| Material                    |   | FR-4                                        |  |

| Number of copper foil layer |   | 4                                           |  |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |  |

|                             | 2 | 74.2 x 74.2 x t0.035                        |  |

|                             | 3 | 74.2 x 74.2 x t0.035                        |  |

|                             | 4 | 74.2 x 74.2 x t0.070                        |  |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm               |  |

enlarged view

No. HSOP8A-A-Board-SD-1.0

# **HSOP-8A** Test Board

## (4) Board D

| Item                        |   | Specification                              |  |

|-----------------------------|---|--------------------------------------------|--|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                        |  |

| Material                    |   | FR-4                                       |  |

| Number of copper foil layer |   | 4                                          |  |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm2 t0.070 |  |

|                             | 2 | 74.2 x 74.2 x t0.035                       |  |

|                             | 3 | 74.2 x 74.2 x t0.035                       |  |

|                             | 4 | 74.2 x 74.2 x t0.070                       |  |

| Thermal via                 |   | -                                          |  |

## (5) Board E

| Item                        |   | Specification                                          |  |

|-----------------------------|---|--------------------------------------------------------|--|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |  |

| Material                    |   | FR-4                                                   |  |

| Number of copper foil layer |   | 4                                                      |  |

|                             | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |  |

| Connor foil layer [mm]      | 2 | 74.2 x 74.2 x t0.035                                   |  |

| Copper foil layer [mm]      | 3 | 74.2 x 74.2 x t0.035                                   |  |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |  |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm                          |  |

enlarged view

No. HSOP8A-A-Board-SD-1.0

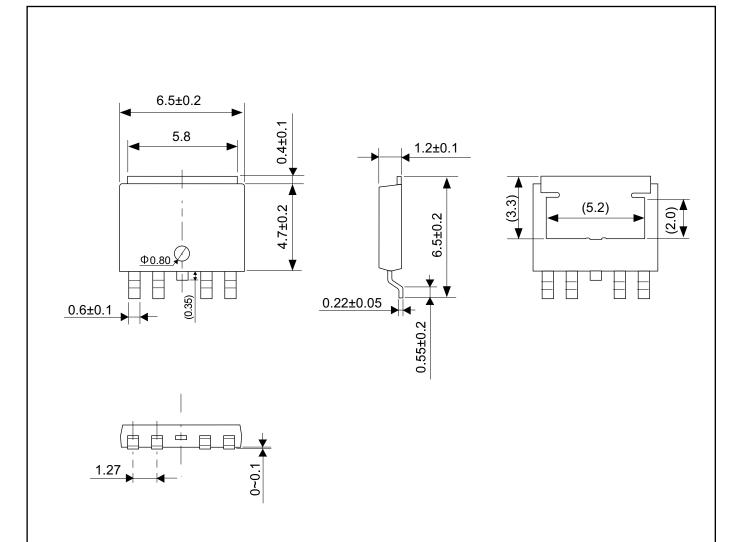

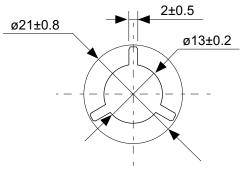

# No. VA005-A-P-SD-2.0

| TITLE      | TO-252-5S-A-PKG Dimensions |  |

|------------|----------------------------|--|

| No.        | VA005-A-P-SD-2.0           |  |

| ANGLE      | $\oplus$                   |  |

| UNIT       | mm                         |  |

|            |                            |  |

|            |                            |  |

|            |                            |  |

| ABLIC Inc. |                            |  |

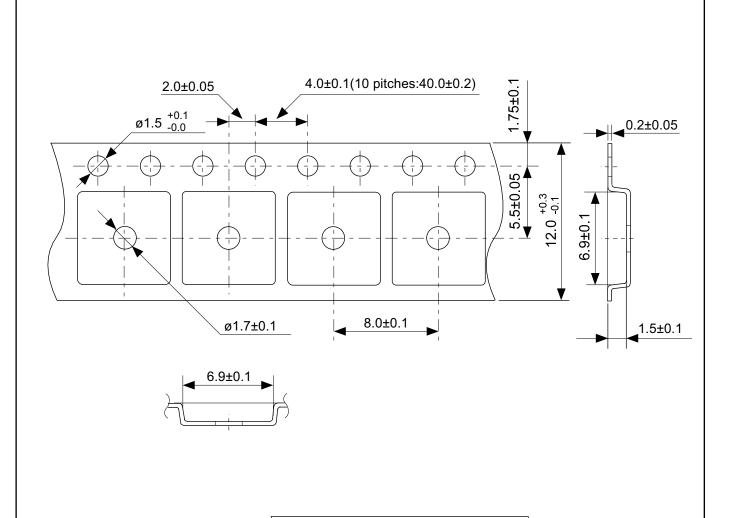

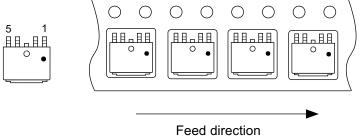

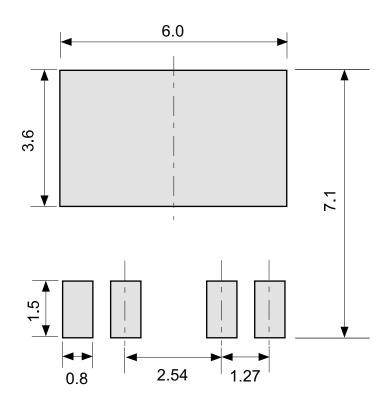

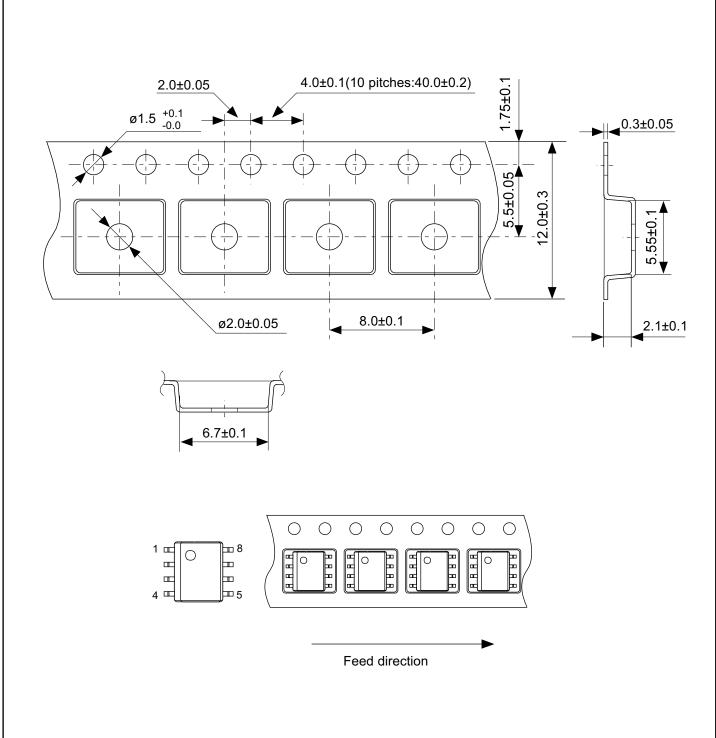

No. VA005-A-C-SD-1.0

| TITLE      | TO-252-5S-A-Carrier Tape |  |

|------------|--------------------------|--|

| No.        | VA005-A-C-SD-1.0         |  |

| ANGLE      |                          |  |

| UNIT       | mm                       |  |

|            |                          |  |

|            |                          |  |

|            |                          |  |

| ABLIC Inc. |                          |  |

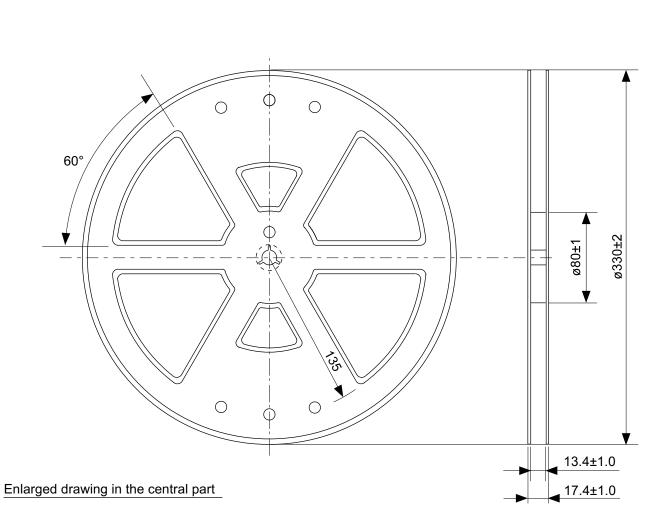

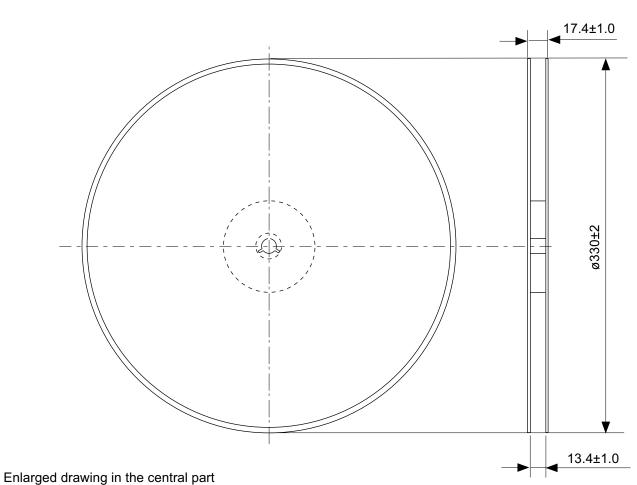

No. VA005-A-R-SD-1.0

| TITLE      | TO-252-5S-A-Reel |      |       |

|------------|------------------|------|-------|

| No.        | VA005-A-R-SD-1.0 |      |       |

| ANGLE      |                  | QTY. | 4,000 |

| UNIT       | mm               |      |       |

|            |                  |      |       |

|            |                  |      |       |

|            |                  |      |       |

| ABLIC Inc. |                  |      |       |

# No. VA005-A-L-SD-1.0

| TITLE | TO-252-5S-A<br>-Land Recommendation |  |  |

|-------|-------------------------------------|--|--|

| No.   | VA005-A-L-SD-1.0                    |  |  |

| ANGLE |                                     |  |  |

| UNIT  | mm                                  |  |  |

|       |                                     |  |  |

|       |                                     |  |  |

|       | ABLIC Inc.                          |  |  |

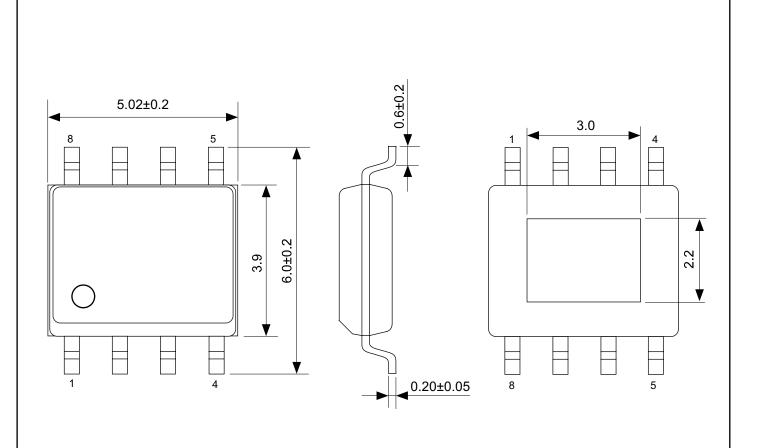

# No. FH008-A-P-SD-2.0

| TITLE      | HSOP8A-A-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | FH008-A-P-SD-2.0        |  |

| ANGLE      | <b>\$</b> =1            |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

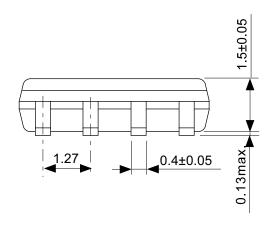

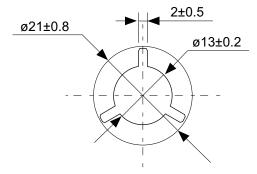

## No. FH008-A-C-SD-1.0

| TITLE      | HSOP8A-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | FH008-A-C-SD-1.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

Enlarged drawing in the central part

# No. FH008-A-R-SD-1.0

| TITLE      | HSOP             | 8A-A-Re | el    |

|------------|------------------|---------|-------|

| No.        | FH008-A-R-SD-1.0 |         |       |

| ANGLE      |                  | QTY.    | 4,000 |

| UNIT       | mm               |         |       |

|            |                  |         |       |

|            |                  |         |       |

|            |                  |         |       |

| ABLIC Inc. |                  |         |       |

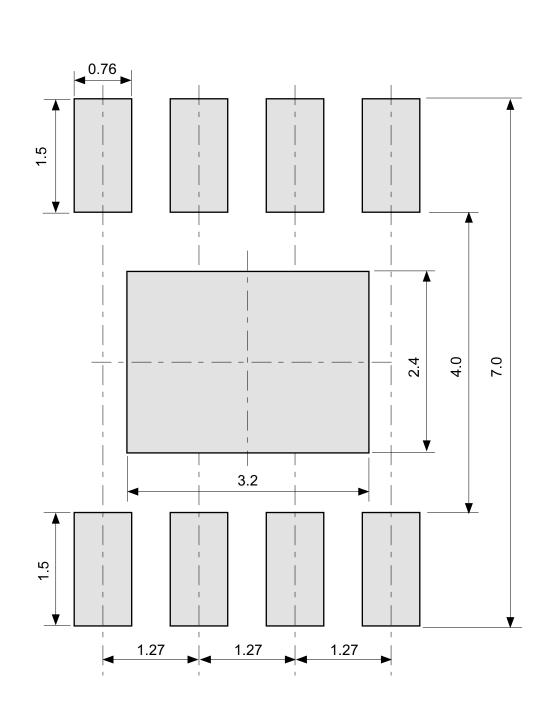

# No. FH008-A-L-SD-1.0

| TITLE      | HSOP8A-A -Land Recommendation |  |

|------------|-------------------------------|--|

| No.        | FH008-A-L-SD-1.0              |  |

| ANGLE      |                               |  |

| UNIT       | mm                            |  |

|            |                               |  |

|            |                               |  |

|            |                               |  |

| ABLIC Inc. |                               |  |

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not responsible for damages caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not responsible for damages caused by the incorrect information described herein.

- 4. Be careful to use the products within their specified ranges. Pay special attention to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not responsible for damages caused by failures and / or accidents, etc. that occur due to the use of the products outside their specified ranges.

- 5. When using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products must not be used or provided (exported) for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not responsible for any provision (export) to those whose purpose is to develop, manufacture, use or store nuclear, biological or chemical weapons, missiles, or other military use.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses. Do not apply the products to the above listed devices and equipments without prior written permission by ABLIC Inc. Especially, the products cannot be used for life support devices, devices implanted in the human body and devices that directly affect human life, etc.

- Prior consultation with our sales office is required when considering the above uses.

- ABLIC Inc. is not responsible for damages caused by unauthorized or unspecified use of our products.

- 9. Semiconductor products may fail or malfunction with some probability.

- The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system must be sufficiently evaluated and applied on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc.

The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party without the express permission of ABLIC Inc. is strictly prohibited.

- 14. For more details on the information described herein, contact our sales office.

2.0-2018.01