# **ABLIC**

### S-8426A Series

### www.ablicinc.com

### **BATTERY BACKUP SWITCHING IC**

© ABLIC Inc., 2006-2015 Rev.2.0\_03

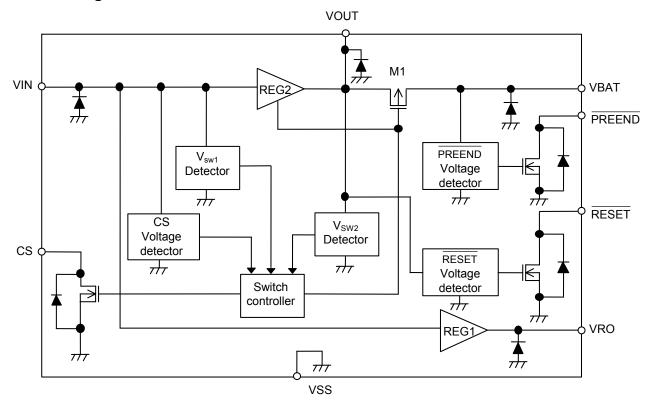

The S-8426A Series is a CMOS IC designed for use in the switching circuits of primary and backup power supplies on a single chip. It consists of two voltage regulators, three voltage detectors, a power supply switch and its controller, as well as other functions.

In addition to the switching function between the primary and backup power supply, the S-8426A Series can provide the micro controllers with three types of voltage detection output signals corresponding to the power supply voltage.

Moreover adopting a special sequence for switch control enables the effective use of the backup power supply, making this IC ideal for configuring a backup system.

### ■ Features

• Low power consumption

Normal operation: 15  $\mu$ A Max. ( $V_{IN} = 6 V$ )

Backup: 4.5 μA Max.

Voltage regulator

Output voltage tolerance: ±2%

Output voltage: Independently selectable in 0.1 V steps in the range of 2.3 to 5.4 V

• Three built-in voltage detectors (CS, PREEND, RESET)

Detection voltage precision: ±2%

Detection voltage: Selectable in 0.1 V steps in the range of 2.4 to 5.3 V (CS voltage detector)

Selectable in 0.1 V steps in the range of 1.7 to 3.4 V (PREEND, RESET voltage

detector

- · Switching circuit for primary power supply and backup power supply configurable on one chip

- Efficient use of backup power supply possible

- Special sequence

Backup voltage is not output when the primary power supply voltage does not reach the initial voltage at which the switch unit operates.

- Lead-free, Sn 100%, halogen-free\*1

- \*1. Refer to "■ Product Name Structure" for details.

### ■ Applications

- Video camera recorders

- Still video cameras

- · Memory cards

- SRAM backup equipment

### ■ Packages

- 8-Pin TSSOP

- 8-Pin SOP(JEDEC)

### ■ Block Diagram

Figure 1

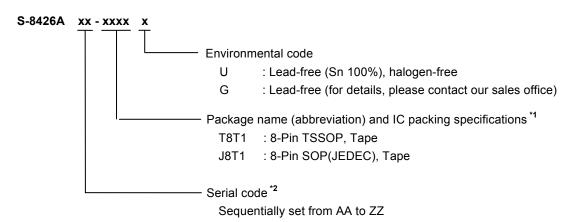

### ■ Product Name Structure

### 1. Product Name

- \*1. Refer to the taping specifications.

- \*2. Refer to the "3. Product Name List".

### 2. Package

| Package Name     |                        | Drawing Code |              |              |  |

|------------------|------------------------|--------------|--------------|--------------|--|

|                  |                        | Package      | Tape         | Reel         |  |

| 0 Di- T000D      | Environmental code = G | FT008-A-P-SD | FT008-E-C-SD | FT008-E-R-SD |  |

| 8-Pin TSSOP      | Environmental code = U | FT008-A-P-SD | FT008-E-C-SD | FT008-E-R-S1 |  |

| 0 Din COD/JEDEC) | Environmental code = G | FJ008-A-P-SD | FJ008-D-C-SD | FJ008-D-R-SD |  |

| 8-Pin SOP(JEDEC) | Environmental code = U | FJ008-A-P-SD | FJ008-D-C-SD | FJ008-D-R-S1 |  |

### 3. Product Name List

Table 1

| Model No.       | Output<br>Voltage | Output<br>Voltage | CS<br>Voltage      | CS<br>Voltage            | RESET Voltage      | RESET Voltage      | PREEND<br>Voltage  | PREEND<br>Voltage  | Switch<br>Voltage              |

|-----------------|-------------------|-------------------|--------------------|--------------------------|--------------------|--------------------|--------------------|--------------------|--------------------------------|

| model Ne.       | V <sub>RO</sub>   | V <sub>OUT</sub>  | -V <sub>DET1</sub> | +V <sub>DET1</sub>       | -V <sub>DET2</sub> | +V <sub>DET2</sub> | -V <sub>DET3</sub> | +V <sub>DET3</sub> | V <sub>SW1</sub>               |

| S-8426AAA-J8T1x | 5.000             | 5.000             | 4.500              | +V <sub>OUT</sub> × 0.95 | 2.900              | 3.068              | 2.100              | 2.207              | $+V_{DET4}^{*1}$ $\times 0.77$ |

\*1.  $+V_{DET4}$  can be calculated by  $-V_{DET1}$  with the following equation.

$+V_{DET4} = (+V_{DET1}) + 15 \times \{(-V_{DET1}) - 0.8\} \div 372$

Caution Set the CS voltage so that the switch voltage ( $V_{SW1}$ ) is equal to or greater than the  $\overline{RESET}$  detection voltage ( $-V_{DET2}$ ).

$\label{eq:Remark 1.} \textbf{ The selection range is as follows.}$

$\begin{array}{lll} V_{RO},\,V_{OUT}; & 2.3 \text{ to } 5.4 \text{ V } (0.1 \text{ V steps}) \\ -V_{DET1}; & 2.4 \text{ to } 5.3 \text{ V } (0.1 \text{ V steps}) \\ -V_{DET2}; & 1.7 \text{ to } 3.4 \text{ V } (0.1 \text{ V steps}) \\ -V_{DET3}; & 1.7 \text{ to } 3.4 \text{ V } (0.1 \text{ V steps}) \end{array}$

2.  $V_{SW1}$ :  $+V_{DET1} \times 0.85$  or  $+V_{DET1} \times 0.77$ When  $V_{SW2} > +V_{DET1}$ ,  $+V_{DET4} \times 0.85$  or  $+V_{DET4} \times 0.77$

- 3. If a product with a voltage other than above is required, contact our sales representative.

- 4. x: G or U

- 5. Please select products of environmental code = U for Sn 100%, halogen-free products.

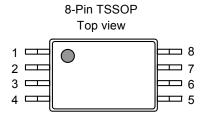

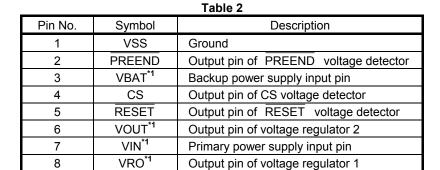

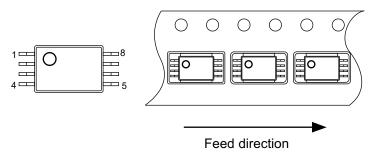

### ■ Pin Configurations

Figure 2

\*1. Mount capacitors between VSS (GND pin) and the VIN, VBAT, VOUT, and VRO pins. (Refer to the "■ Standard Circuit")

Figure 3

### Table 3

| Pin No. | Symbol            | Description                           |

|---------|-------------------|---------------------------------------|

| 1       | VSS               | Ground                                |

| 2       | PREEND            | Output pin of PREEND voltage detector |

| 3       | VBAT*1            | Backup power supply input pin         |

| 4       | CS                | Output pin of CS voltage detector     |

| 5       | RESET             | Output pin of RESET voltage detector  |

| 6       | VOUT*1            | Output pin of voltage regulator 2     |

| 7       | VIN <sup>*1</sup> | Primary power supply input pin        |

| 8       | VRO*1             | Output pin of voltage regulator 1     |

<sup>\*1.</sup> Mount capacitors between VSS (GND pin) and the VIN, VBAT, VOUT, and VRO pins. (Refer to the "■ Standard Circuit")

### ■ Absolute Maximum Ratings

Table 4

(Unless otherwise specified: Ta = 25 °C)

|                               |                  |                                    | ,                                           |      |

|-------------------------------|------------------|------------------------------------|---------------------------------------------|------|

| Item                          |                  | Symbol                             | Absolute Maximum Tatings                    | Unit |

| Primary power supply          | input voltage    | V <sub>IN</sub>                    | $V_{SS}$ -0.3 to $V_{SS}$ +18               | V    |

| Backup power supply           | input voltage    | $V_{BAT}$                          | $V_{SS}$ –0.3 to $V_{SS}$ +18               | V    |

| Output voltage of volt        | age regulator    | V <sub>RO</sub> , V <sub>OUT</sub> | $V_{SS}$ -0.3 to $V_{IN}$ +0.3              | V    |

| CS output voltage             |                  | V <sub>CS</sub>                    | V <sub>SS</sub> -0.3 to V <sub>SS</sub> +18 | V    |

| RESET output voltage          |                  | VRESET                             | $V_{SS}$ -0.3 to $V_{SS}$ +18               | V    |

| PREEND output volta           | ige              | VPREEND                            | V <sub>SS</sub> -0.3 to V <sub>SS</sub> +18 | V    |

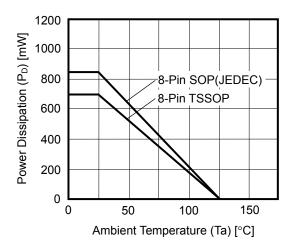

| Davis dia dia attau           | 8-Pin TSSOP      |                                    | 700 <sup>*1</sup>                           | mW   |

| Power dissipation             | 8-Pin SOP(JEDEC) | P <sub>D</sub>                     | 850 <sup>*1</sup>                           | mW   |

| Operating ambient temperature |                  | T <sub>opr</sub>                   | -40 to +85                                  | °C   |

| Storage temperature           |                  | T <sub>stq</sub>                   | -40 to +125                                 | °C   |

**<sup>\*1.</sup>** At mounted on printed circuit board

[Mounted board]

(1) Board size: 114.3 mm × 76.2 mm × t1.6 mm (2) Board name: JEDEC STANDARD51-7

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 4 Power Dissipation of Package (Mounted on Printed Circuit Board)

### **■** Electrical Characteristics

### 1. S-8426AAA

Table 5 (1 / 2)

(Unless otherwise specified: Ta = 25 °C) Test Item Symbol Conditions Min. Typ. Max. Unit Circuit 4.900 5.000 5.100 ٧ 1 Output voltage 1  $V_{RO}$  $V_{IN}$  = 6 V,  $I_{RO}$  = 30 mA V<sub>IN</sub> = 6 V<sub>, I<sub>RO</sub> = 30 mA</sub> 356 474 Dropout voltage 1 mV 1  $V_{drop1}$ 50 100 Load stability 1  $V_{IN} = 6 \text{ V}, I_{RO} = 0.1 \text{ to } 40 \text{ mA}$ \_ mV 1  $\Delta V_{RO1}$ Input stability 1  $\Delta V_{RO2}$  $V_{IN}$  = 6 to 16 V,  $I_{RO}$  = 30 mA 5 20 mV 1 regul  $\Delta V_{\text{RO}}$ Output voltage temperature ppm/ Ta = -40 to +85 °C ±100 1 ∆Ta • VRO coefficient 1 °C Output voltage 2  $V_{OUT}$  $V_{IN} = 6 \text{ V}, I_{OUT} = 50 \text{ mA}$ 4.900 5.000 5.100 V 1 Φ oltage 401 540  $V_{IN} = 6 \text{ V}, I_{OUT} = 50 \text{ mA}$ mV 1 Dropout voltage 2  $V_{drop2}$  $V_{IN}$  = 6 V,  $I_{OUT}$  = 0.1 to 60 mA 50 100 mV 1 Load stability 2  $\Delta V_{OUT1}$ Input stability 2  $V_{IN} = 6 \text{ to } 16 \text{ V}, I_{OUT} = 50 \text{ mA}$ 10 30 mV 1  $\Delta V_{OUT2}$  $\Delta V$ out Output voltage temperature ppm/ ±100 1 Ta = -40 to +85 °C coefficient 2 **ΔTa • V**ouτ ٥С \_ 16 V Primary power input voltage  $V_{IN}$ 1 4.410 4.500 4.590 CS detection voltage  $-V_{\mathsf{DET1}}$ V<sub>IN</sub> voltage detection V 2  $+V_{OUT}$  $+V_{OUT}$  $+V_{OUT}$ ٧ 2 CS release voltage  $+V_{DET1}$  $\times 0.93$  $\times~0.95$  $\times$  0.97 2.842 2.900 2.958 2  $-V_{DET2}$ V<sub>OUT</sub> voltage detection V RESET detection voltage 2.994 3.068 3.142 ٧ RESET release voltage  $+V_{DET2}$ 2 detecto 2.058 2.100 2.142 V 2 V<sub>BAT</sub> voltage detection PREEND detection voltage  $-V_{DET3}$ 2.154 2.207 2.260 PREEND release voltage  $+V_{DET3}$ V 2 1.7 ٧  $V_{opr}$  $V_{IN}$  or  $V_{BAT}$ 16 2 Operating voltage  $\Delta - V_{DET1}$ Φ ppm/ 2 Ta = -40 to +85 °C ±100 Ď  $\Delta Ta \bullet - V_{DET1}$ °C oltag  $\Delta - V_{DET2}$ Detection voltage ppm/ Ta =  $-40 \text{ to } +85 \,^{\circ}\text{C}$ 2 ±100 ΔTa • −VDET2 temperature coefficient °C  $\Delta - V_{\text{DET3}}$ ppm/ Ta = -40 to +85 °C ±100 2 **ΔTa •** −**V**DET3 ٥С RESET 1.50 2.30 mΑ 3  $V_{DS} = 0.5 V$ Sink current 3 1.50 2.30 I<sub>SINK</sub> **PREEND** mΑ  $V_{IN} = V_{BAT} = 2.0 \text{ V}$ CS 1.50 2.30  $\mathsf{m}\mathsf{A}$ 3 I<sub>LEAK</sub>  $V_{DS} = 16 \text{ V}, V_{IN} = 16 \text{ V}$ 3 Leakage current 0.1 цΑ

Table 5 (2 / 2)

|          | Item                                              | Symbol                                             | Condition                                                   | S            | Min.                           | Тур.                         | Max.                         | Unit       | Test<br>Circuit |

|----------|---------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|--------------|--------------------------------|------------------------------|------------------------------|------------|-----------------|

|          | Switch voltage                                    | V <sub>SW1</sub>                                   | V <sub>BAT</sub> = 2.8 V, V <sub>IN</sub> voltage detection |              | $+V_{DET4}^{*1}$ $\times 0.75$ | +V <sub>DET4</sub> *1 × 0.77 | +V <sub>DET4</sub> *1 × 0.79 | ٧          | 4               |

| unit     | CS output inhibit voltage                         | V <sub>SW2</sub>                                   | $V_{BAT} = 3.0 \text{ V}, V_{OUT} \text{ volta}$            | ge detection | $V_{OUT} \times 0.93$          | $V_{OUT} \times 0.95$        | $V_{OUT} \times 0.97$        | >          | 5               |

| witch    | V <sub>BAT</sub> switch<br>leakage current        | I <sub>LEAK</sub>                                  | $V_{IN} = 6 \text{ V}, V_{BAT} = 0 \text{ V}$               |              | -                              | _                            | 0.1                          | μΑ         | 6               |

| Swi      | V <sub>BAT</sub> switch resistance                | R <sub>SW</sub>                                    | $V_{IN}$ = Open,<br>$V_{BAT}$ = 3.0 V, $I_{OUT}$ = 10       | to 500 μA    | _                              | 30                           | 60                           | Ω          | 7               |

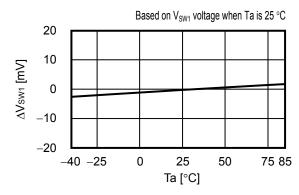

|          | Switch voltage temperature coefficient            | ΔVsw1<br>ΔTa • Vsw1                                | Ta = -40 to +85°C                                           |              | -                              | ±100                         | -                            | ppm/<br>°C | 4               |

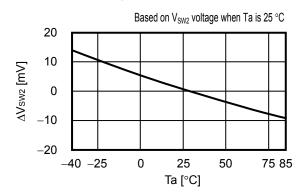

|          | CS output inhibit voltage temperature coefficient | $\frac{\Delta V_{SW2}}{\Delta Ta \bullet V_{SW2}}$ | Ta = -40 to +85°C                                           |              | _                              | ±100                         | 1                            | ppm/<br>°C | 5               |

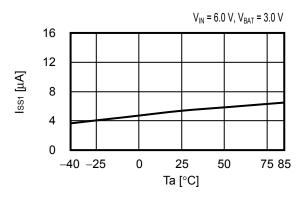

|          |                                                   | I <sub>SS1</sub>                                   | $V_{IN} = 6 \text{ V}, V_{BAT} = 3.0 \text{ V}$             | , no load    | _                              | 6                            | 15                           | μΑ         | 8               |

| <u>a</u> |                                                   | I <sub>SS2</sub>                                   | $V_{IN} = 16 \text{ V}, V_{BAT} = 3.0$                      | V, no load   | -                              | 7                            | 20                           | μΑ         | 8               |

| o t a    | Current consumption                               | I <sub>BAT1</sub>                                  | $V_{IN} = 6 \text{ V}, V_{BAT} = 3.0 \text{ V}$             | , no load    | _                              | 0.5                          | 3.5                          | μΑ         | 8               |

|          |                                                   |                                                    | V <sub>IN</sub> = Open,                                     | Ta = 25 °C   | -                              | 1.5                          | 4.5                          | μΑ         | 8               |

|          |                                                   | I <sub>BAT2</sub>                                  | $V_{BAT}$ = 3.0 V, no load                                  | Ta = 85 °C   | -                              | _                            | 5.0                          | μΑ         | 8               |

|          | Backup power supply input voltage                 | $V_{BAT}$                                          | _                                                           |              | 1.7                            | _                            | 4.0                          | ٧          | 7               |

<sup>\*1.</sup>  $+V_{DET4}$  can be calculated by  $-V_{DET1}$  with the following equation.

**Remark** The number in the Test Circuit column corresponds to the circuit number in the "■ Test Circuits" section.

$<sup>+</sup>V_{DET4}$  =  $(+V_{DET1})$  + 15 ×  $\{(-V_{DET1})$  - 0.8 $\}$  ÷ 372

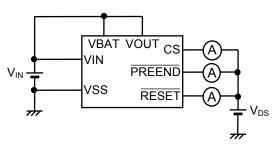

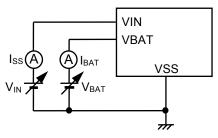

### **■** Test Circuits

VBAT VOUT

VIN PREEND

VSS CS

V V V V

To measure  $V_{\text{DET3}}$ , apply 6 V to VIN.

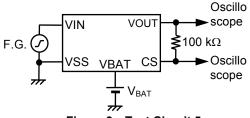

Figure 6 Test Circuit 2

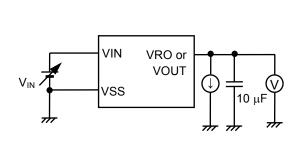

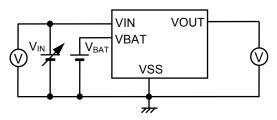

Figure 5 Test Circuit 1

Figure 7 Test Circuit 3

Measure the value after applying 6 V to VIN.

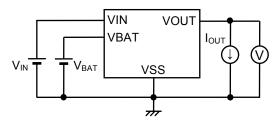

Figure 8 Test Circuit 4

Figure 9 Test Circuit 5

Figure 10 Test Circuit 6

Leave open and measure the value after applying 6 V to VIN.

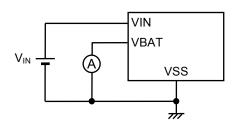

Figure 11 Test Circuit 7

To measure  $I_{\text{BAT2}},$  apply 6 V to VIN and then leave VIN open and measure  $I_{\text{BAT}}.$

Figure 12 Test Circuit 8

### Operation

The internal configuration of the S-8426A Series is as follows.

- Voltage regulator 1, which stabilizes input voltage (V<sub>IN</sub>) and outputs it to V<sub>RO</sub>

- Voltage regulator 2, which stabilizes input voltage (V<sub>IN</sub>) and outputs it to V<sub>OUT</sub>

- CS voltage detector, which monitors input voltage (V<sub>IN</sub>)

- PREEND voltage detector, which monitors output voltage (VBAT)

- RESET voltage detector, which monitors output voltage (Vout)

- Switch unit

The functions and operations of the above-listed elements are described below.

### 1. Voltage Regulators

The S-8426A Series features on-chip voltage regulators with a small dropout voltage. The voltage of the VRO and VOUT pins (the output pins of the voltage regulator) can separately be selected for the output voltage in 0.1 V steps between the range of 2.3 to 5.4 V.

### 1. 1 Dropout voltage V<sub>drop1</sub>, V<sub>drop2</sub>

Assume that the voltage output from the VRO pin is  $V_{RO(E)}$  under the conditions of output voltage 1 described in the electrical characteristics table.  $V_{IN1}$  is defined as the input voltage at which output voltage from the VRO pin becomes 98% of  $V_{RO(E)}$  when the input voltage  $V_{IN}$  is decreased. Then, the dropout voltage  $V_{drop1}$  is calculated by the following expression.

$$V_{drop1} = V_{IN1} - V_{RO(E)} \times 0.98$$

Similarly, assume that the voltage of the VOUT pin is  $V_{\text{OUT}(E)}$  under the conditions of output voltage 2 described in the electrical characteristics table.  $V_{\text{IN2}}$  is defined as the input voltage at which the output voltage from the VOUT pin becomes 98% of  $V_{\text{OUT}(E)}$ . Then, the dropout voltage  $V_{\text{drop2}}$  is calculated by the following expression.

$$V_{drop2} = V_{IN2} - V_{OUT(E)} \times 0.98$$

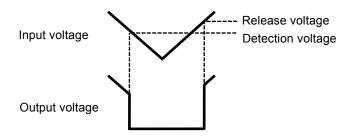

### 2. Voltage Detector

The S-8426A Series incorporates three high-precision, low power consuming voltage detectors with hysteresis characteristics. The power of the CS voltage detector is supplied from the VIN and VBAT pins. Therefore, the output is stable as long as the primary or backup power supplies are within the operating voltage range (1.7 to 16 V). All outputs are Nch open-drain, and need pull-up resistors of about 100 k $\Omega$ .

### 2. 1 CS Voltage Detector

The CS voltage detector monitors the input voltage ( $V_{IN}$ ) (VIN pin voltage). The detection voltage can be selected from between 2.4 and 5.3 V in 0.1 V steps. The result of detection is output at the CS pin: "Low" for lower voltage than the detection level and "High" for higher voltage than the release level (however, when the VOUT pin voltage is the CS output inhibit voltage ( $V_{SW2}$ ), a low level is output).

Figure 13 Definition of Detection and Release Voltages

### 2. 2 PREEND Voltage Detector

The  $\overline{\text{PREEND}}$  voltage detector monitors input voltage (V<sub>BAT</sub>) (VBAT pin voltage). The detection voltage can be selected in the range of 1.7 to 3.4 V in 0.1 V step. By using this function, IC notifies if the backup battery is scarce. The result of detection is output at the  $\overline{\text{PREEND}}$  pin: "Low" for lower voltages than the detection level and "High" for higher voltages than the release level.

### 2. 3 RESET Voltage Detector

The  $\overline{\text{RESET}}$  voltage detector monitors output voltage (V<sub>OUT</sub>) (VOUT pin voltage). The detection voltage can be selected in the range of 1.7 to 3.4 V in 0.1 V step. The result of detection is output at the  $\overline{\text{RESET}}$  pin: "Low" for lower voltages than the detection level and "High" for higher voltages than the release level.  $\overline{\text{RESET}}$  outputs the normal logic if the VOUT pin voltage is 1.0 V or more.

Caution The PREEND and RESET voltage detectors use the different pins, respectively.

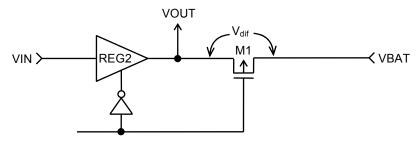

Practically, the current is taken from the VBAT side, and consider the I/O voltage difference (V<sub>dif</sub>) of M1 when M1 is ON.

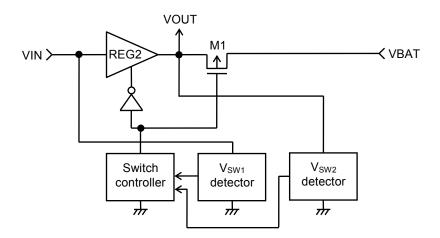

### 3. Switch Unit

10

The switch unit consists of the  $V_{SW1}$  and  $V_{SW2}$  detectors, a switch controller, voltage regulator 2, and switch transistor M1 (Refer to **Figure 14**).

Figure 14

### 3. 1 V<sub>SW1</sub> Detector

The  $V_{SW1}$  detector monitors the power supply voltage  $V_{IN}$  and sends the results of detection to the switch controller. The detection voltage ( $V_{SW1}$ ) can be set to 77  $\pm 2\%$  or 85  $\pm 2\%$  of the CS release voltage ( $+V_{DET1}$ ).

In the products  $V_{SW2} > +V_{DET1}$ , the setting value is 77  $\pm 2\%$  or 85  $\pm 2\%$  of  $+V_{DET4}$  which is calculated with the following equation.

$$+V_{DET4} = (-V_{DET1}) + 15 \times \{ (-V_{DET1}) - 0.8 \} \div 372$$

### 3. 2 V<sub>SW2</sub> Detector

The  $V_{SW2}$  detector monitors the VOUT pin voltage and keeps the CS release voltage output low until the  $V_{OUT}$  pin voltage rises to  $V_{SW2}$  voltage. The CS pin output then changes from low to high if the VIN pin voltage is more than the CS release voltage (+ $V_{DET1}$ ) when the VOUT pin voltage rises to 95 ±2% of the output voltage of voltage regulator 2 ( $V_{OUT}$ ). The CS pin output changes from high to low regardless of the  $V_{SW2}$  voltage when the VIN pin voltage drops to less than the CS detection voltage (- $V_{DET1}$ ).

The CS pin output remains high if the VIN pin voltage stays higher than the CS detection voltage ( $-V_{DET1}$ ) when the VOUT pin voltage drops to less than the  $V_{SW2}$  voltage due to an undershoot.

### 3. 3 Switch Controller

The switch controller controls voltage regulator 2 and switch transistor M1. There are two statuses corresponding to the power supply voltage  $(V_{IN})$  (or power supply voltage  $(V_{BAT})$ ) sequence: a special sequence status and a normal sequence status. When the power supply voltage  $(V_{IN})$  rises and becomes equal to or exceeds the CS release voltage  $(+V_{DET1})$ , the normal sequence status is entered, but until then the special sequence status is maintained.

### (1) Special sequence status

The switch controller sets voltage regulator 2 ON and switch transistor M1 OFF from the initial status until the primary power supply voltage  $(V_{IN})$  is connected and reaches more than the CS release voltage  $(+V_{DET1})$  in order to prevent consumption of the backup power supply regardless of the  $V_{SW1}$  detector status. This status is called the special sequence status.

### (2) Normal sequence status

The switch controller enters the normal sequence status from the special sequence status once the primary power supply voltage  $(V_{IN})$  reaches more than the CS release voltage  $(+V_{DET1})$ .

Once the normal sequence is entered, the switch controller switches voltage regulator 2 and switch transistor M1 ON/OFF as shown in **Table 6** according to the power supply voltage  $V_{IN}$ . The time required for voltage regulator 2 to be switched from OFF to ON is a few hundred  $\mu s$  at most. During this interval, voltage regulator 2 and switch transistor M1 may both switch OFF and the VOUT pin voltage may drop. To prevent this, connect a capacitor of 10  $\mu F$  or more to the VOUT pin.

When the VOUT pin voltage becomes lower than the RESET detection voltage, the status returns to the special sequence status.

Table 6 ON/OFF Switching of Voltage Regulator 2 and Switch Transistor M1 According to Power Supply Voltage (V<sub>IN</sub>)

| Power Supply Voltage (V <sub>IN</sub> ) | Voltage Regulator 2 | Switch Transistor M1 | VOUT Pin Voltage    |

|-----------------------------------------|---------------------|----------------------|---------------------|

| $V_{IN} > V_{SW1}$                      | ON                  | OFF                  | V <sub>OUT</sub>    |

| $V_{IN} < V_{SW1}$                      | OFF                 | ON                   | $V_{BAT} - V_{dif}$ |

### 3. 4 Switch Transistor M1

Voltage regulator 2 is also used to switch from VIN pin to VOUT pin. Therefore, no reverse current flows from VOUT pin to VIN pin when voltage regulator 2 is OFF. The output voltage of voltage regulator 2 can be selected from between 2.3 V and 5.4 V in 0.1 V steps.

The on-resistance of switch transistor M1 is 60  $\Omega$  or lower (I  $_{OUT}$  = 10 to 500  $\mu A).$

Therefore, when M1 is switched ON and VOUT pin is connected to VBAT pin, the voltage drop ( $V_{dif}$ ) caused by M1 is  $60 \times I_{OUT}$  (output current) at maximum., and  $V_{BAT} - V_{dif}$  (max.) is output to the VOUT pin at minimum.

When voltage regulator 2 is ON and M1 is OFF, the leakage current of M1 is kept below 0.1  $\mu$ A max. ( $V_{IN}$  = 6 V, Ta = 25 °C) with the VBAT pin grounded (VSS pin).

Figure 15 Definition of V<sub>dif</sub>

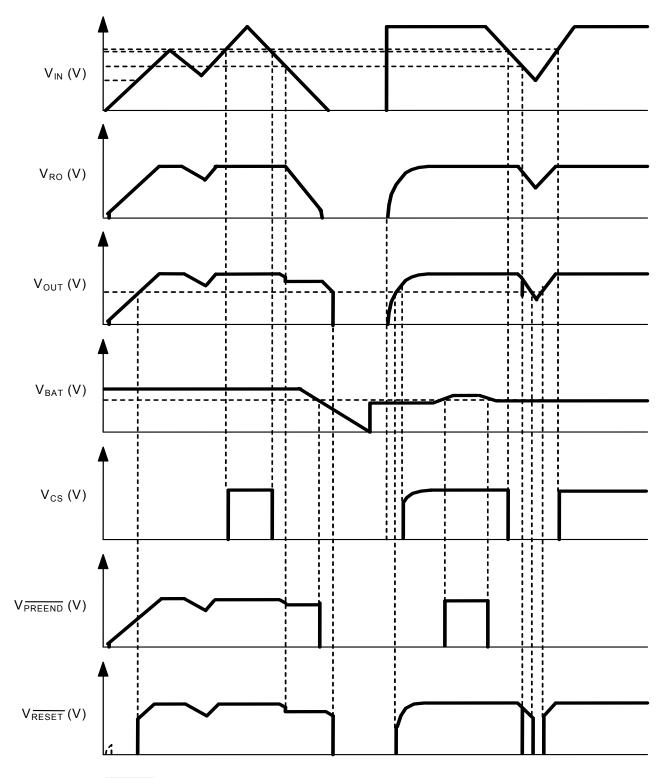

### ■ Timing Chart

$\textbf{Remark} \quad \text{CS}, \ \overline{\text{PREEND}} \quad \text{and} \quad \overline{\text{RESET}} \quad \text{are pulled up to V}_{\text{OUT}}. \ \text{Y-axis is an arbitrary scale}.$

Figure 16 Operation Timing Chart

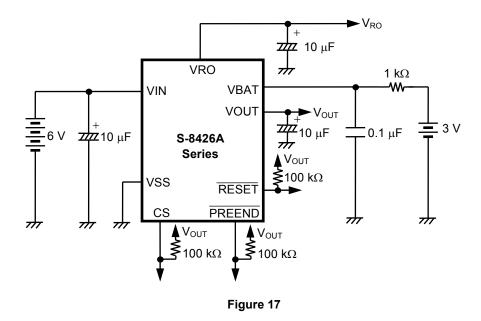

### ■ Standard Circuit

Caution 1. Be sure to add a 10  $\mu F$  or more capacitor to the VOUT and VRO pins.

2. The above connections and values will not guarantee correct operation. Before setting these values, perform sufficient evaluation on the application to be actually used.

### ■ Precautions

- In applications with small I<sub>RO</sub> or I<sub>OUT</sub>, the output voltages V<sub>RO</sub> and V<sub>OUT</sub> may rise, causing the load stability to exceed standard levels. Set I<sub>RO</sub> and I<sub>OUT</sub> to 10 μA or more.

- Attach the proper capacitor to the VOUT pin to prevent the RESET voltage detector (which monitors the VOUT pin) from coming active due to undershoot.

- Watch for overshoot and ensure it does not exceed the ratings of the IC chips and/or capacitors attached to the VRO and VOUT pins.

- Add a 10  $\mu F$  or more capacitor to the VOUT and VRO pins.

- When  $V_{IN}$  rises from the voltage more than  $V_{SW1}$ , a low pulse of less than 4 ms flows through the PREEND pin even when  $V_{BAT}$  is more than the PREEND release voltage. Thus when monitoring the PREEND pin, make sure to take the 4 ms interval or more after the rise of  $V_{IN}$ .

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any and all disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

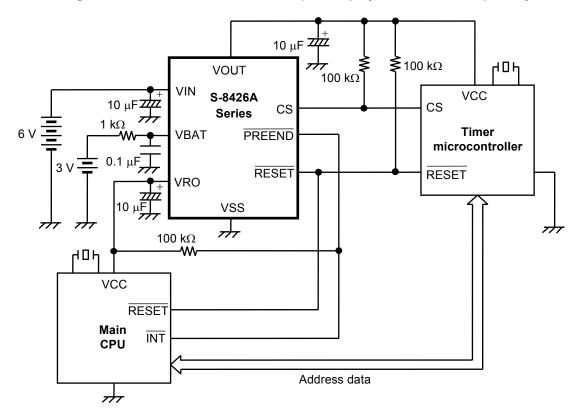

### **■** Application Circuits

1. When Using Timer Micro controllers for Backup to display PREEND in the primary CPU

Figure 18 Application Circuit 1

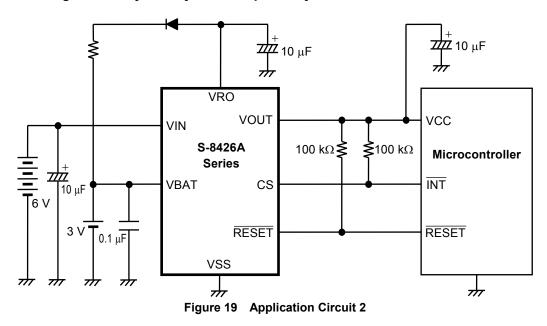

### 2. When Using Secondary Battery as Backup Battery

Remark The backup battery can be floating-recharged by using voltage regulator 1.

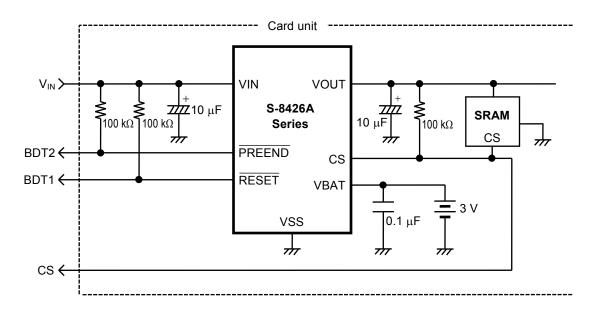

### 3. Memory Card

Figure 20 Application Circuit 3

Caution The above connections and values will not guarantee correct operation. Before setting these values, perform sufficient evaluation on the application to be actually used.

16 ABLIC Inc.

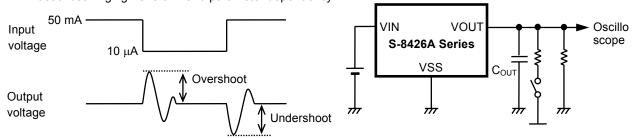

### ■ Transient Response

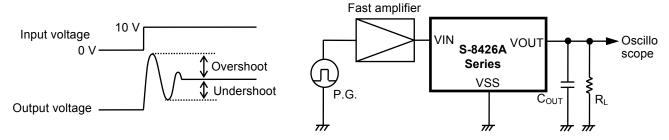

### 1. Line Transient Response Against Input Voltage Variation

The input voltage variation differs depending on whether the power supply input (0 to 10 V square wave) is applied or the power supply variation (6 V and 10 V square waves) is applied. This section describes the ringing waveforms and parameter dependency of each type. The test circuit is shown for reference.

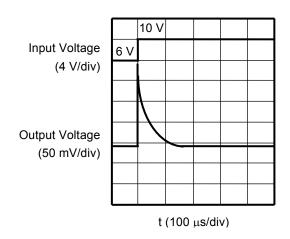

### 1. 1 Power supply application: 0 to 10 V Square wave

Figure 21 Power Supply Application: 0 to 10 V Square Wave

Figure 22 Test Circuit

### **VOUT** pin

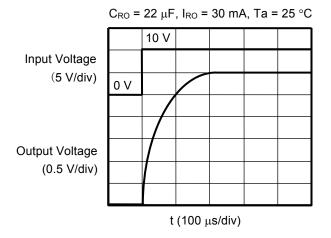

# $C_{OUT} = 22 \ \mu\text{F}, \ I_{OUT} = 50 \ \text{mA}, \ Ta = 25 \ ^{\circ}\text{C}$ $10 \ \text{V}$ $0 \ \text{V}$ $Output \ \text{Voltage}$ $(0.5 \ \text{V/div})$ $t \ (100 \ \mu\text{s/div})$

### VRO pin

Figure 23 Ringing Waveform of Power Supply Application (VOUT Pin)

Figure 24 Ringing Waveform of Power Supply Application (VRO Pin)

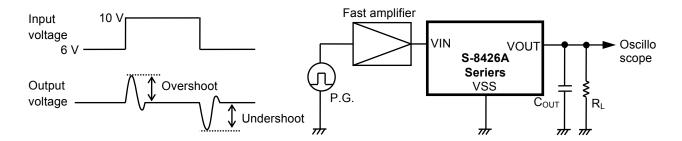

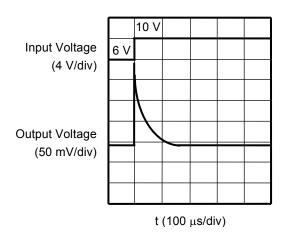

### 1. 2 Power supply variation: 6 V and 10 V square waves

Figure 25 Power Supply Variation: 6 V and 10 V Square Waves

Figure 26 Test Circuit

**VOUT** pin

Figure 27 Ringing Waveform of Power Supply Variation (VOUT Pin)

### VRO pin

Figure 28 Ringing Waveform of Power Supply Variation (VRO Pin)

18 ABLIC Inc.

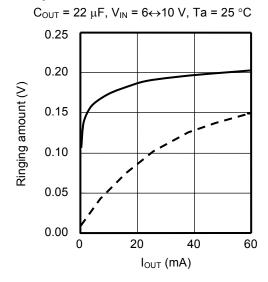

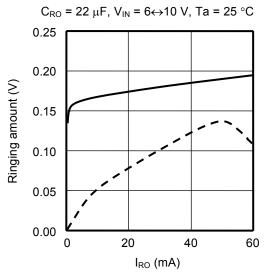

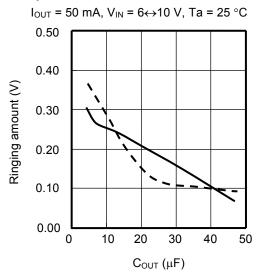

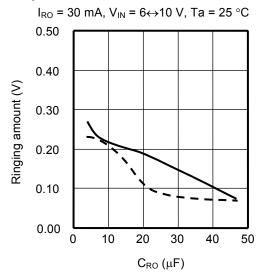

# 1. 3 Reference data: Dependency of output current ( $I_{OUT}$ ), load capacitance ( $C_{OUT}$ ), input variation width ( $\Delta V_{IN}$ ), temperature (Ta)

For reference, the following pages describe the results of measuring the ringing amounts at the VOUT and VRO pins using the output current ( $I_{OUT}$ ), load capacitance ( $C_{OUT}$ ), input variation width ( $\Delta V_{IN}$ ), and temperature (Ta) as parameters.

### (1) I<sub>OUT</sub> Dependency

### (a) VOUT pin

Figure 29

### (b) VRO pin

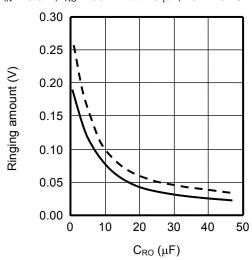

### (2) C<sub>OUT</sub> Dependency

### (a) VOUT pin

Figure 31

### (b) VRO pin

Figure32

Overshoot

Undershoot

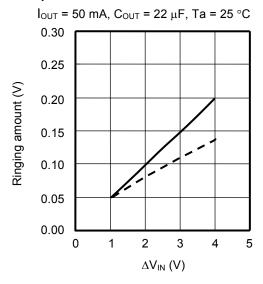

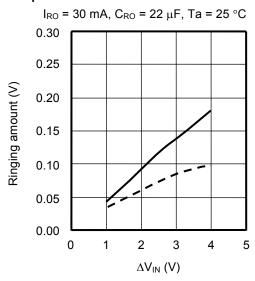

### (3) $\Delta V_{IN}$ Dependency

$\Delta V_{IN}$  shows the difference between the low voltage fixed to 6 V and the high voltage. For example,  $\Delta V_{IN}$  = 2 V means the difference between 6 V and 8 V.

### (a) VOUT pin

Figure 33

### (b) VRO pin

Figure34

Overshoot

Undershoot

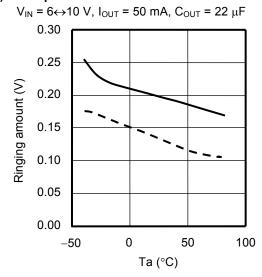

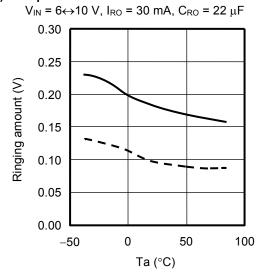

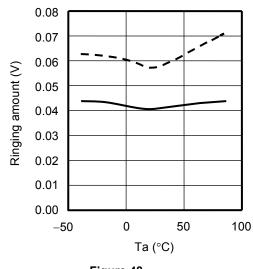

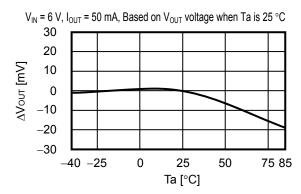

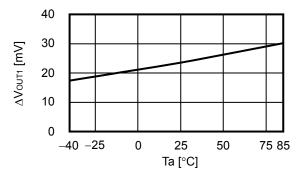

### (4) Temperature Dependency

### (a) VOUT pin

Figure 35

### (b) VRO pin

---- Overshoot

---- Undershoot

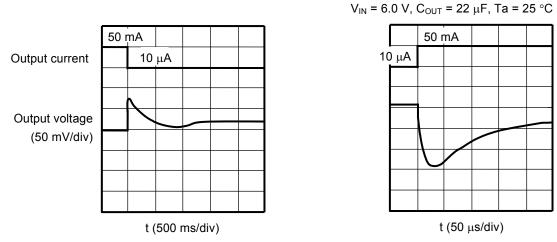

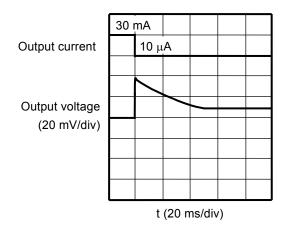

### 2. Load Transient Response Based on Output Current Fluctuation

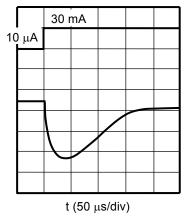

The overshoot and undershoot are caused in the output voltage if the output current fluctuates between 10  $\mu$ A and 50 mA (V<sub>RO</sub> is between 10  $\mu$ A and 30 mA) while the input voltage is constant. **Figure 37** shows the output voltage variation due to the output current. **Figure 38** shows the test circuit for reference. The latter half of this section describes ringing waveform and parameter dependency.

Figure 37 Output Voltage Variation due to Output Current

Figure 38 Test Circuit

### 2. 1 Load Variation

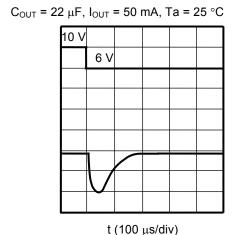

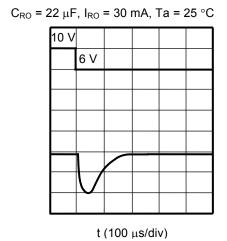

**Figure 39** shows the ringing waveforms at the VOUT pin and **Figure 40** shows the ringing waveforms at the VRO pin due to the load variation, respectively.

### **VOUT** pin

Figure 39 Ringing Waveform due to Load Variation (VOUT Pin)

### **VRO** pin

Figure 40 Ringing Waveform due to Load Variation (VRO Pin)

ABLIC Inc.

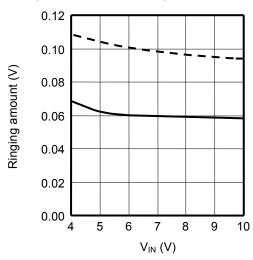

# 2. 2 Reference data: Dependency of input voltage ( $V_{IN}$ ), load capacitance ( $C_{OUT}$ ), output variation width ( $\Delta I_{OUT}$ ), and temperature (Ta)

### (1) V<sub>IN</sub> Dependency

### (a) VOUT pin

$C_{OUT}$  = 22  $\mu F,~I_{OUT}$  = 50 mA  $\leftrightarrow$  10  $\mu A,~Ta$  = 25  $^{\circ}C$

Figure 41

### (b) VRO pin

$C_{RO}$  = 22  $\mu$ F,  $I_{RO}$  = 30 mA  $\leftrightarrow$  10  $\mu$ A, Ta = 25 °C

Figure 42

Overshoot

---- Undershoot

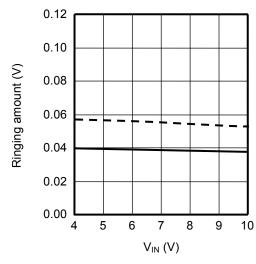

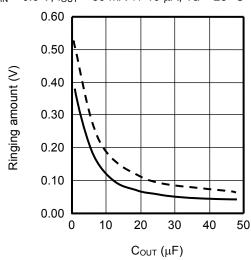

### (2) C<sub>OUT</sub> Dependency

### (a) VOUT pin

$V_{IN}$  = 6.0 V,  $I_{OUT}$  = 50 mA  $\leftrightarrow$  10  $\mu$ A, Ta = 25 °C

Figure 43

### (b) VRO pin

$V_{IN}$  = 6.0 V,  $I_{RO}$  = 30 mA  $\leftrightarrow$  10  $\mu$ A, Ta = 25 °C

Figure 44

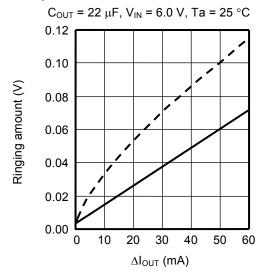

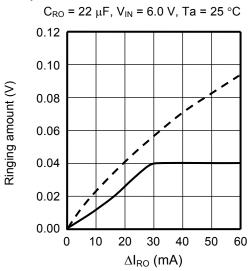

### (3) $\Delta I_{OUT}$ Dependency

$\Delta I_{OUT}$  and  $\Delta I_{RO}$  show the fluctuation between the low current stabilized at 10  $\mu A$  and the high current. For example,  $\Delta I_{OUT}$  = 10 mA means a fluctuation between 10  $\mu A$  and 10 mA.

### (a) VOUT pin

Figure 45

### (b) VRO pin

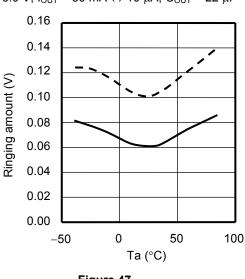

### (4) Temperature Dependency

### (a) VOUT pin

$$V_{IN}$$

= 6.0 V,  $I_{OUT}$  = 50 mA  $\leftrightarrow$  10  $\mu$ A,  $C_{OUT}$  = 22  $\mu$ F

Figure 47

### (b) VRO pin

$$V_{\text{IN}}$$

= 6.0 V,  $I_{\text{RO}}$  = 30 mA  $\leftrightarrow$  10  $\mu\text{A},\,C_{\text{RO}}$  = 22  $\mu\text{F}$

Figure 48

- Caution 1. Be sure to add a 10  $\mu F$  or more capacitor to the VOUT and VRO pins.

- 2. The above connections and values will not guarantee correct operation. Before setting these values, perform sufficient evaluation on the application to be actually used.

### ■ Characteristics (Typical Data)

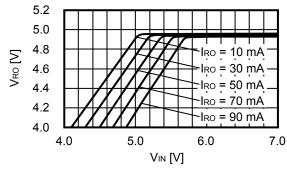

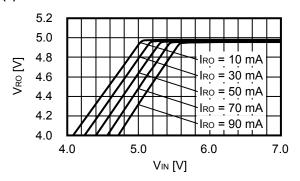

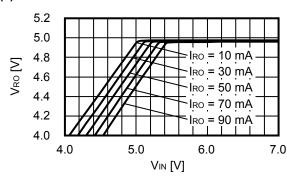

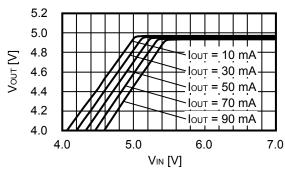

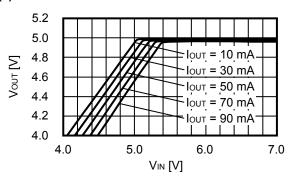

- 1. Voltage Regulator Unit  $(V_{RO} = V_{OUT} = 5.0 \text{ V})$

- 1. 1 Input Voltage  $(V_{IN})$  vs. Output Voltage  $(V_{RO})$  Characteristics (REG1)

(2) Ta = 25 °C

1. 2 Input Voltage (V<sub>IN</sub>) vs. Output Voltage (V<sub>OUT</sub>) Characteristics (REG2)

24 ABLIC Inc.

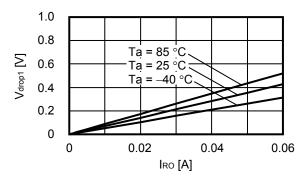

# 1. 3 Output Current (I<sub>RO</sub>) vs. Dropout Voltage (V<sub>drop1</sub>) Characteristics

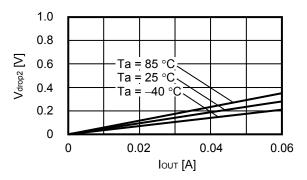

### 1. 4 Output Current ( $I_{OUT}$ ) vs. Dropout Voltage ( $V_{drop2}$ ) Characteristics

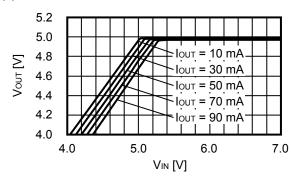

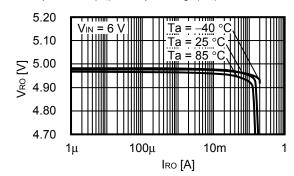

1. 5 Output Current (I<sub>RO</sub>) vs. Output Voltage (V<sub>RO</sub>) Characteristics

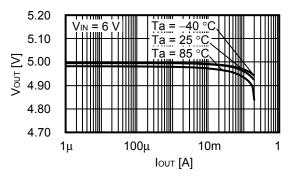

1. 6 Output Current (I<sub>OUT</sub>) vs. Output Voltage (V<sub>OUT</sub>) Characteristics

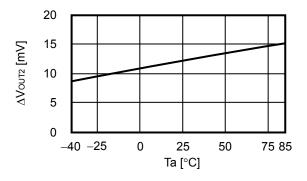

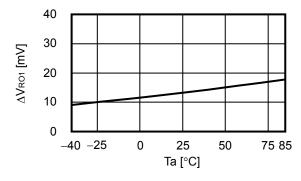

### 1.7 Output voltage (V<sub>RO</sub>) Temperature Characteristics

1. 8 Output voltage (V<sub>OUT</sub>) Temperature Characteristics

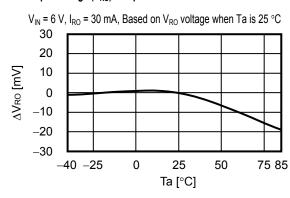

1. 9 Input Stability (V<sub>RO</sub>) Temperature Characteristics

1. 10 Input Stability (V<sub>OUT</sub>) Temperature Characteristics

### 1. 11 Load Stability ( $V_{RO}$ ) Temperature Characteristics

### 1. 12 Load Stability (V<sub>RO</sub>) Temperature Characteristics

### 2. Voltage Detector

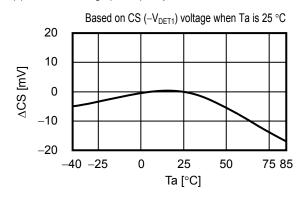

### 2. 1 CS Voltage Detector $(-V_{DET1} = 4.5 \text{ V})$

### (1) Detection voltage ( $-V_{\text{DET1}}$ ) temperature characteristics

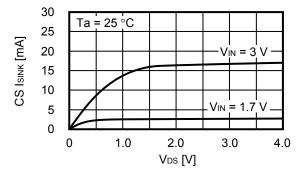

### (2) Output current (I<sub>SINK</sub>) characteristics

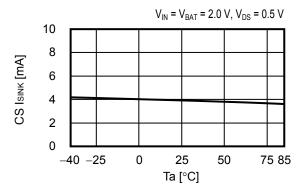

### (3) Output current ( $I_{SINK}$ ) temperature characteristics

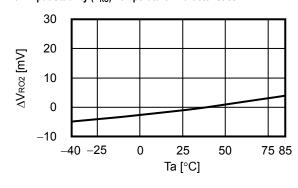

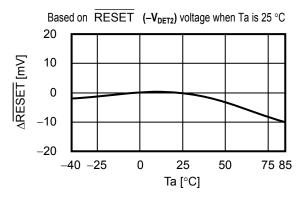

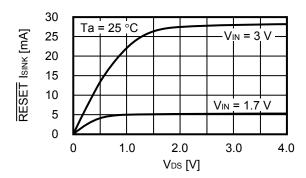

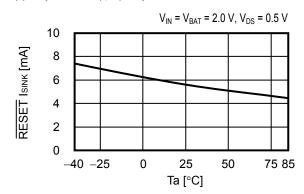

### 2. 2 RESET Voltage Detector ( $-V_{DET2} = 2.9 \text{ V}$ )

(1) Detection voltage (-V<sub>DET2</sub>) temperature characteristics

(2) Output current (I<sub>SINK</sub>) characteristics

(3) Output current (I<sub>SINK</sub>) temperature characteristics

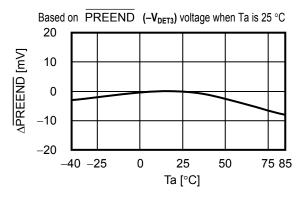

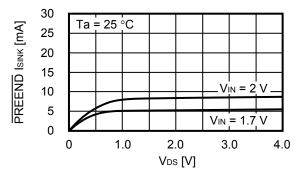

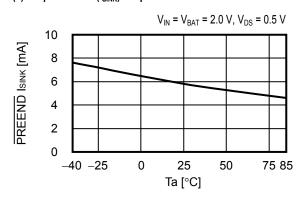

### 2. 3 $\overline{\text{PREEND}}$ Voltage Detector ( $-V_{\text{DET3}} = 2.1 \text{ V}$ )

(1) Detection voltage (-V<sub>DET3</sub>) temperature characteristics

(2) Output current (I<sub>SINK</sub>) characteristics

(3) Output current (I<sub>SINK</sub>) temperature characteristics

### 3. Switch Unit

### 3. 1 Switch Voltage (V<sub>SW1</sub>) Temperature Characteristics

### 3. 2 CS Output Inhibit Voltage (V<sub>SW2</sub>) Temperature Characteristics

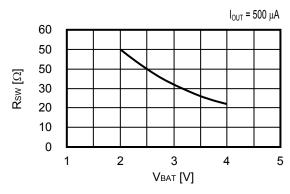

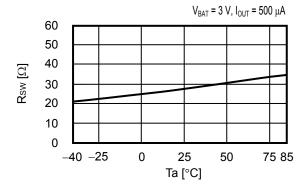

3.3 Input Voltage (V<sub>BAT</sub>) vs. VBAT Switch Resistance (R<sub>SW</sub>) Characteristics 3.4 V<sub>BAT</sub> Switch Resistance (R<sub>SW</sub>) Temperature Characteristics

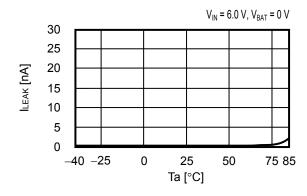

3. 5  $V_{BAT}$  Switch Leakage Current ( $I_{LEAK}$ ) Temperature Characteristics

### 4. Consumption Current

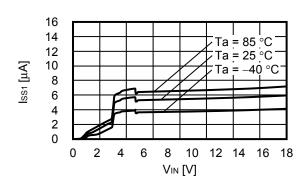

### 4. 1 $V_{IN}$ vs. $V_{IN}$ Consumption Current (I<sub>SS1</sub>) Characteristics

### 4. 2 Consumption Current Temperature

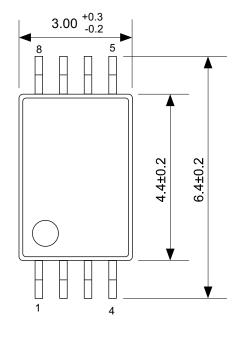

### No. FT008-A-P-SD-1.2

| TITLE      | TSSOP8-E-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | FT008-A-P-SD-1.2        |  |

| ANGLE      | <b>\$</b> \displaystart |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

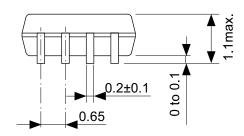

### No. FT008-E-C-SD-1.0

| TITLE      | TSSOP8-E-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | FT008-E-C-SD-1.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

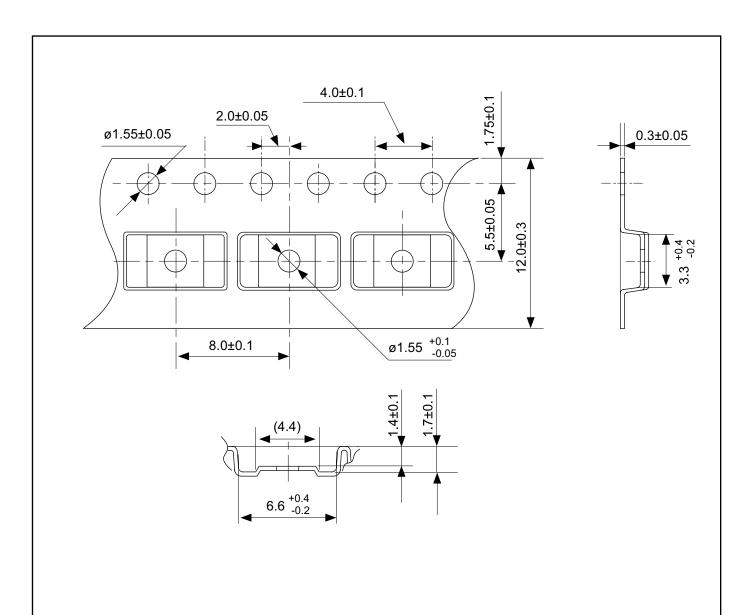

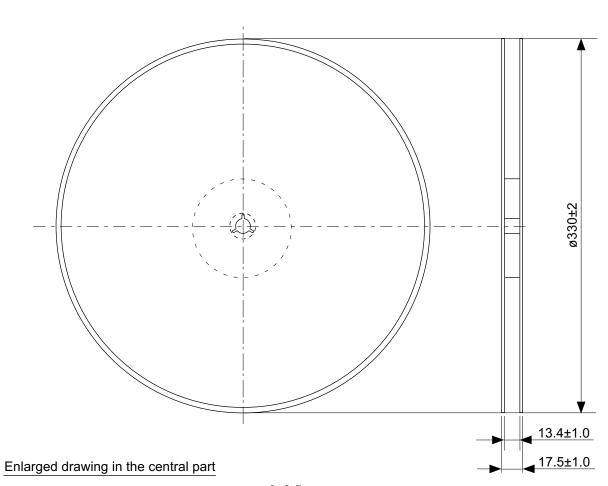

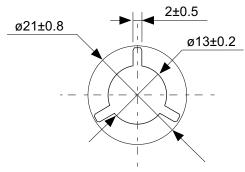

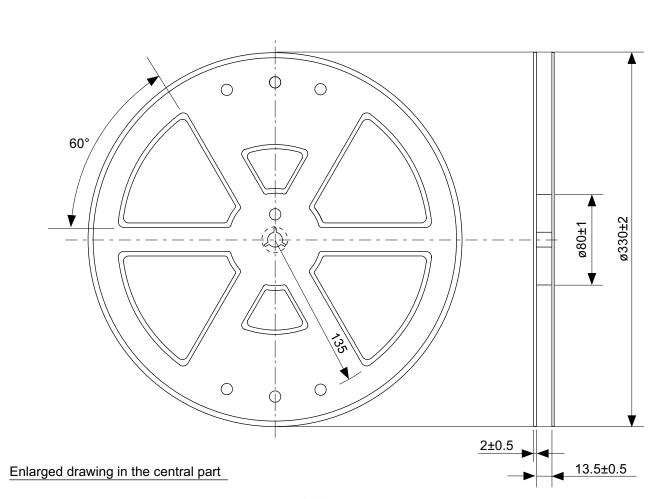

### No. FT008-E-R-SD-1.0

| TITLE      | TSSOP8-E-Reel |           |       |  |

|------------|---------------|-----------|-------|--|

| No.        | FT008         | B-E-R-SD- | 1.0   |  |

| ANGLE      |               | QTY.      | 3,000 |  |

| UNIT       | mm            |           |       |  |

|            |               |           |       |  |

|            |               |           |       |  |

|            |               |           |       |  |

| ABLIC Inc. |               |           |       |  |

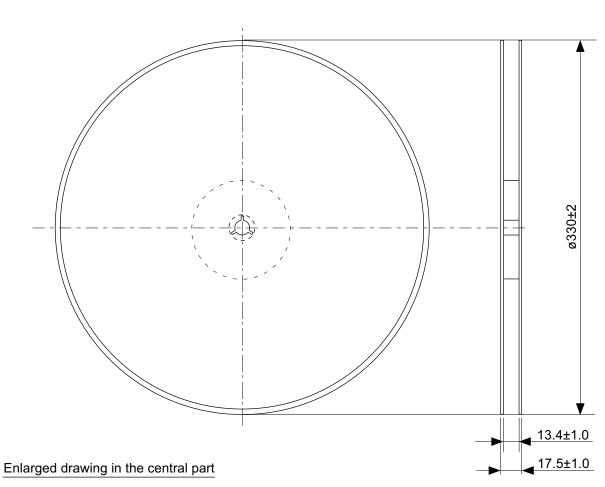

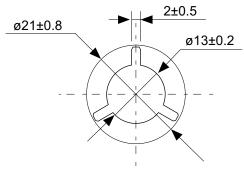

### No. FT008-E-R-S1-1.0

| TITLE      | TSSOP8-E-Reel |          |       |  |  |

|------------|---------------|----------|-------|--|--|

| No.        | FT00          | 8-E-R-S1 | -1.0  |  |  |

| ANGLE      |               | QTY.     | 4,000 |  |  |

| UNIT       | mm            |          |       |  |  |

|            |               |          |       |  |  |

|            |               |          |       |  |  |

|            |               |          |       |  |  |

| ABLIC Inc. |               |          |       |  |  |

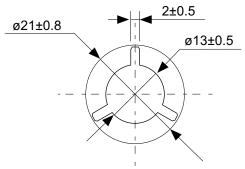

## No. FJ008-A-P-SD-2.2

| TITLE      | SOP8J-D-PKG Dimensions |  |

|------------|------------------------|--|

| No.        | FJ008-A-P-SD-2.2       |  |

| ANGLE      | <b>\$ = 1</b>          |  |

| UNIT       | mm                     |  |

|            |                        |  |

|            |                        |  |

|            |                        |  |

| ABLIC Inc. |                        |  |

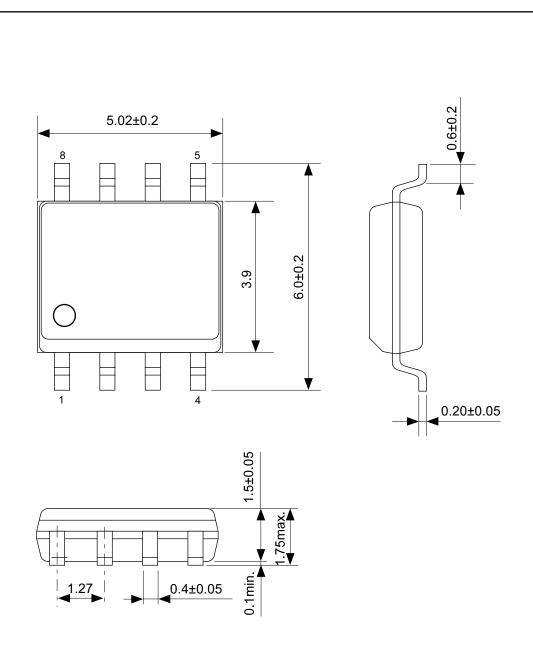

| TITLE      | SOP8J-D-Carrier Tape |  |

|------------|----------------------|--|

| No.        | FJ008-D-C-SD-1.1     |  |

| ANGLE      |                      |  |

| UNIT       | mm                   |  |

|            |                      |  |

|            |                      |  |

|            |                      |  |

| ABLIC Inc. |                      |  |

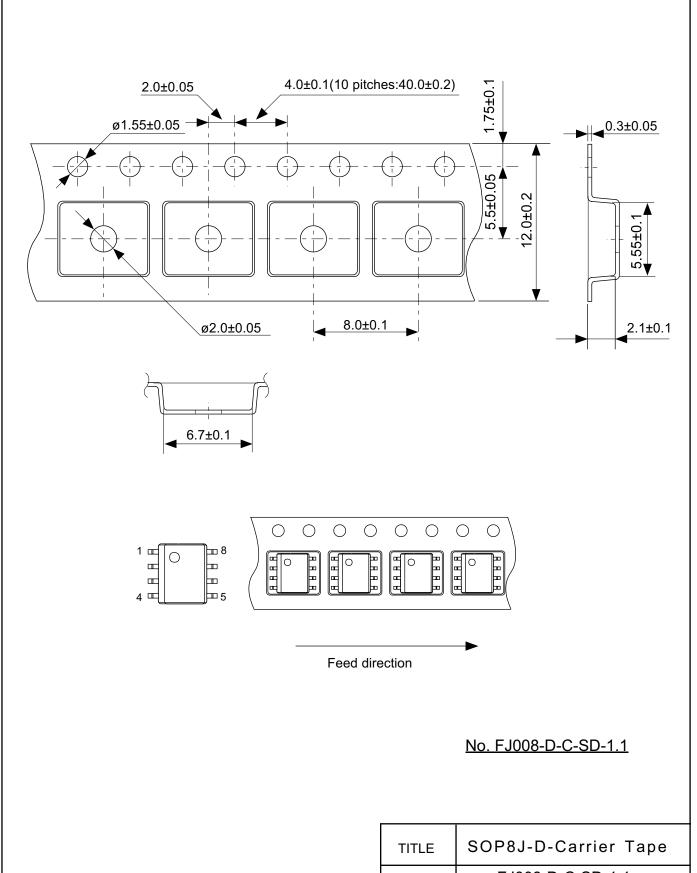

### No. FJ008-D-R-SD-1.1

| TITLE      | SOP8J-D-Reel     |  |      |       |  |

|------------|------------------|--|------|-------|--|

| No.        | FJ008-D-R-SD-1.1 |  |      |       |  |

| ANGLE      |                  |  | QTY. | 2,000 |  |

| UNIT       | mm               |  |      |       |  |

|            |                  |  |      |       |  |

|            |                  |  |      |       |  |

|            |                  |  |      |       |  |

| ABLIC Inc. |                  |  |      |       |  |

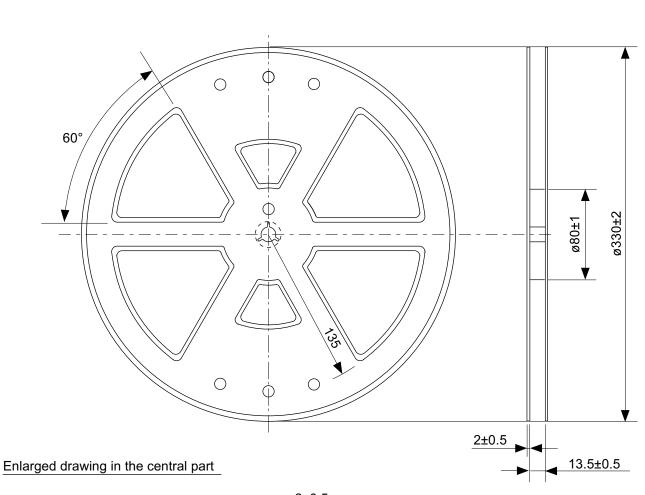

### No. FJ008-D-R-S1-1.0

| TITLE      | SOP8J-D-Reel     |      |       |  |  |

|------------|------------------|------|-------|--|--|

| No.        | FJ008-D-R-S1-1.0 |      |       |  |  |

| ANGLE      |                  | QTY. | 4,000 |  |  |

| UNIT       | mm               |      |       |  |  |

|            |                  |      |       |  |  |

|            |                  |      |       |  |  |

|            |                  |      |       |  |  |

| ABLIC Inc. |                  |      |       |  |  |

### **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not responsible for damages caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not responsible for damages caused by the incorrect information described herein.

- 4. Be careful to use the products within their specified ranges. Pay special attention to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not responsible for damages caused by failures and / or accidents, etc. that occur due to the use of the products outside their specified ranges.

- 5. When using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products must not be used or provided (exported) for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not responsible for any provision (export) to those whose purpose is to develop, manufacture, use or store nuclear, biological or chemical weapons, missiles, or other military use.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses. Do not apply the products to the above listed devices and equipments without prior written permission by ABLIC Inc. Especially, the products cannot be used for life support devices, devices implanted in the human body and devices that directly affect human life, etc.

- Prior consultation with our sales office is required when considering the above uses.

- ABLIC Inc. is not responsible for damages caused by unauthorized or unspecified use of our products.

- 9. Semiconductor products may fail or malfunction with some probability.

- The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system must be sufficiently evaluated and applied on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party without the express permission of ABLIC Inc. is strictly prohibited.

- 14. For more details on the information described herein, contact our sales office.

2.0-2018.01