# S1D15104 Series Technical Manual

S1D15104D00B000

Rev.0.1

- This specification is a preliminary version.

- All values in this specification are tentative and may change in the later.

#### Evaluation board/kit and Development tool important notice

- 1. This evaluation board/kit or development tool is designed for use for engineering evaluation, demonstration, or development purposes only. Do not use it for other purposes. It is not intended to meet the requirements of design for finished products.

- 2. This evaluation board/kit or development tool is intended for use by an electronics engineer and is not a consumer product. The user should use it properly and in a safe manner. Seiko Epson dose not assume any responsibility or liability of any kind of damage and/or fire coursed by the use of it. The user should cease to use it when any abnormal issue occurs even during proper and safe use.

- 3. The part used for this evaluation board/kit or development tool may be changed without any notice.

#### **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2016, All rights reserve

# **Table of Contents**

| 1. | Des          | scription                                       | 1  |

|----|--------------|-------------------------------------------------|----|

| 2. | Fea          | ntures                                          | 2  |

| 3. | Blo          | ck Diagram                                      | 3  |

| 4. | Pin          | Assignment                                      | 4  |

|    |              | Chip Specifications                             |    |

| _  |              | Bump Center Coordinates                         |    |

|    |              | Description                                     |    |

|    |              |                                                 |    |

| _  |              | Power Pins                                      |    |

| _  |              | Power Pins for LCD Drive                        |    |

| 5  |              | MPU Interface Pins                              |    |

| 5  |              | Display Timing Pins                             |    |

| 5  |              | LCD Output Pins                                 |    |

| 5  | .6           | Test Pins                                       | 13 |

| 6  | Fur          | nctional Description                            | 14 |

|    |              | MPU Interface                                   |    |

| U  | . i<br>6.1.1 |                                                 |    |

|    | 6.1.2        |                                                 |    |

|    | 6.1.3        |                                                 |    |

|    | 6.1.4        | 4 Chip Select                                   | 21 |

| 6  | .2 (         | Command Decoder                                 | 21 |

| 6  | .3 I         | Display Data RAM                                | 22 |

|    | 6.3.1        |                                                 |    |

|    | 6.3.2        | 2 Memory Map of Display Data RAM                | 22 |

|    | 6.3.3        |                                                 |    |

|    | 6.3.4        |                                                 |    |

|    | 6.3.5        | 1 2                                             |    |

| 6  |              | Oscillatio <mark>n Circuit</mark>               |    |

| 6  | .5 I         | Display T <mark>iming Generating</mark> Circuit | 34 |

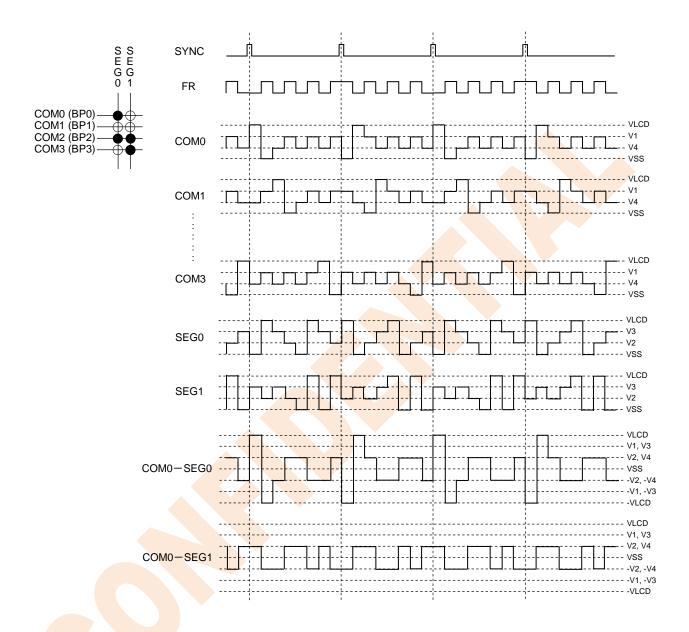

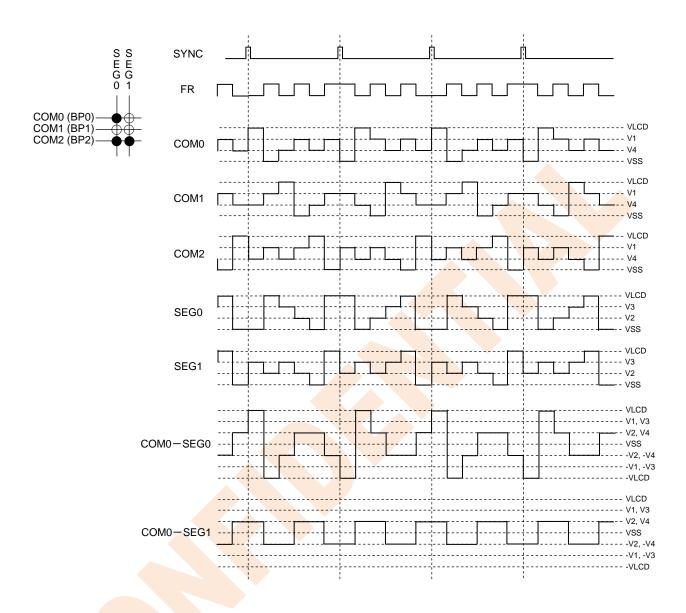

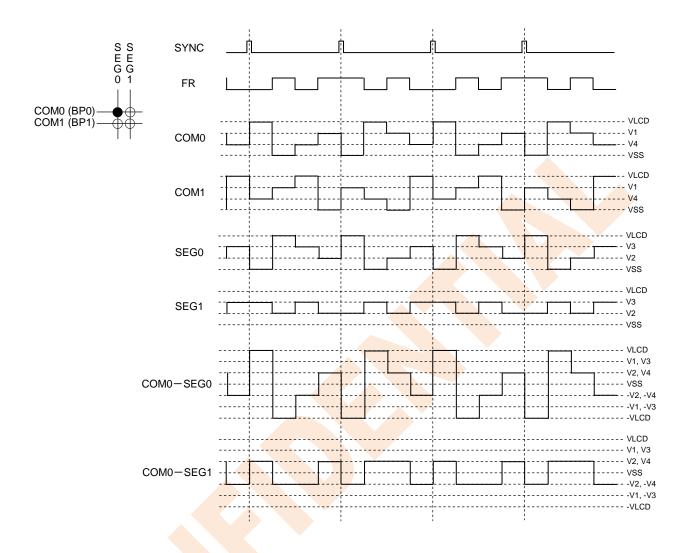

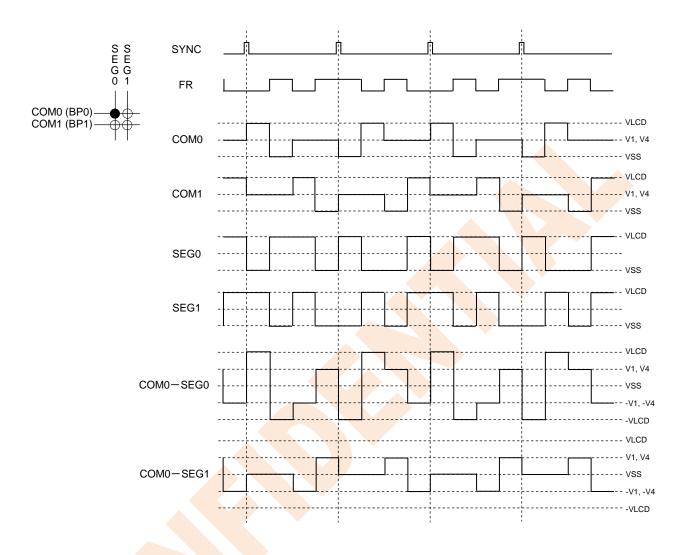

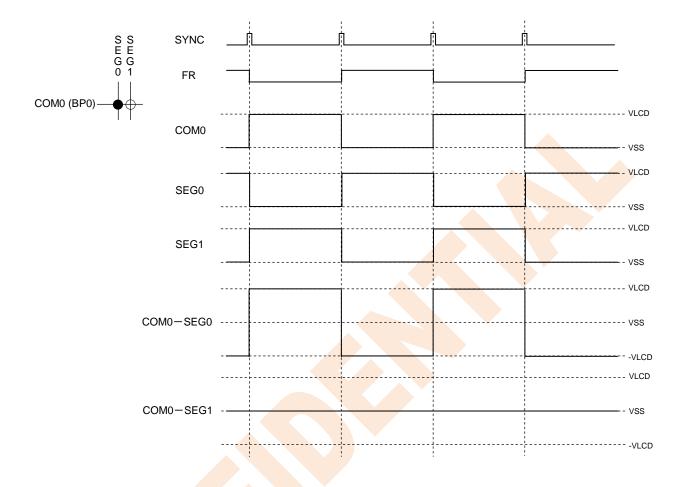

| 6  | .6 I         | LCD Drive Circuit                               |    |

|    | 6.6.1        |                                                 |    |

|    |              | 2 Common Driver                                 |    |

|    | 6.6.3        | · · · · · · · · · · · · · · · · · · ·           |    |

|    | 6.6.4        |                                                 |    |

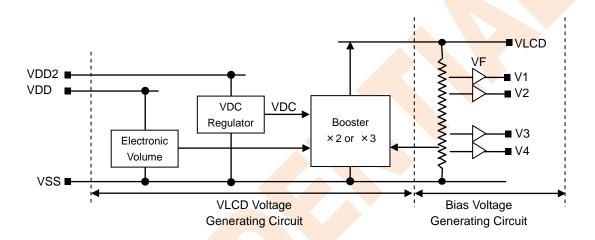

| 6  | \ \          | Power Supply Circuit for LCD Drive              |    |

|    | 6.7.1        |                                                 |    |

|    | 6.7.2        | VLCD Voltage Generating Circuit                 |    |

|    | _            | 7.2.2 VDC Regulator                             |    |

|    | _            | 7.2.3 Booster Circuit                           |    |

|    | 6.7.3        |                                                 |    |

|    | 6.7.4        | 4 Discharge Circuit                             | 48 |

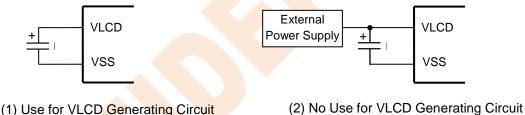

|    | 6.7.5        | 3 3                                             |    |

|    | 6.7.6        | S Examples of External Connection               | 50 |

| 6  |              | Error Detection Circuit                         |    |

|    | 6.8.1        | 3                                               |    |

|    | 6.8.2        | 2 Operating State Detection of IC Test Circuit  | 51 |

| 6.9    | Reset                                                                          | 51 |

|--------|--------------------------------------------------------------------------------|----|

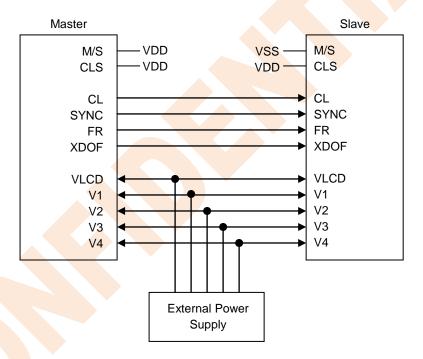

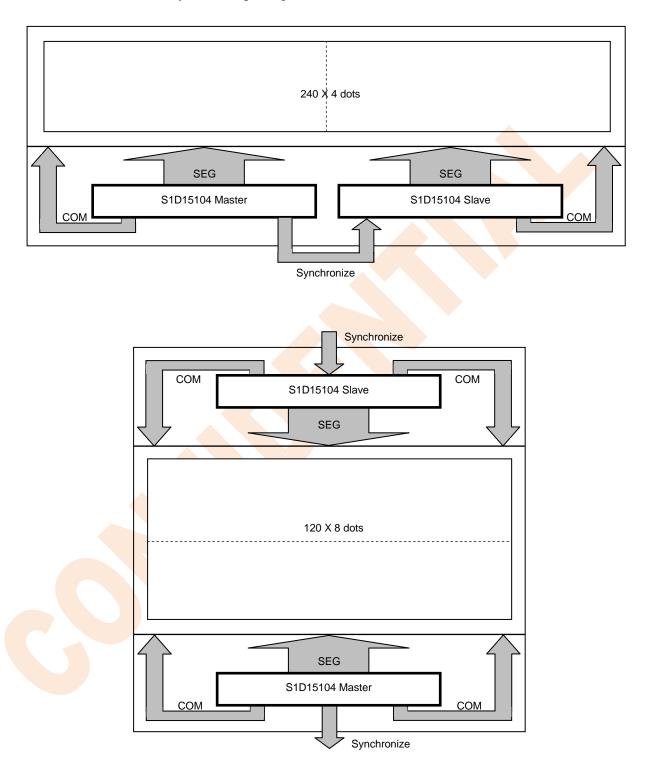

| 6.10   | Master/Slave Mode                                                              | 52 |

| 7 C    | ommands                                                                        | 53 |

| 7. 00  | Commands List                                                                  |    |

|        |                                                                                |    |

| 7.2    | Initial Setting Value of Command Parameters                                    |    |

| 7.3    | Command Descriptions                                                           |    |

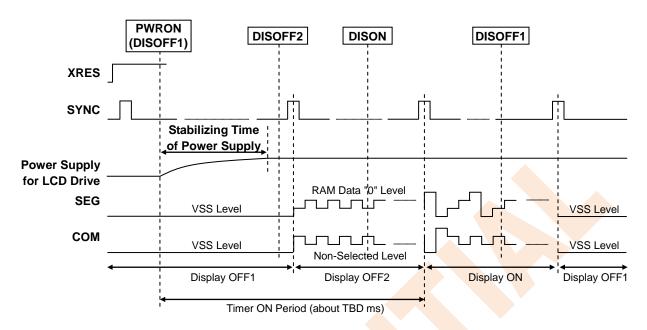

|        | 1) DISON (DISplay ON): Display ON                                              |    |

| -      | 2) DISOFF1 (DISplay OFF mode 1): Display OFF mode 1                            |    |

| -      | 3) DISOFF2 (DISplay OFF mode 2): Display OFF mode 2                            |    |

| -      | 4) DISSET (DISplay mode SET): Display mode set                                 |    |

| -      | 6) COMRVS (COMmon output status ReVerSe): Common output status Reverse         |    |

| 1      | 7) DISSTLIN (DISplay STart LINe set): Display start line set                   |    |

| •      | 8) PASET (Page Address SET): Page address set                                  |    |

| -      | 9) CASET (Column Address SET): Column address set                              |    |

| -      | 10) CANOR (Column Address direction NORmal): Column address direction Normal   |    |

| (      | 11) CARVS (Column Address direction ReVerSe): Column address direction Reverse | 59 |

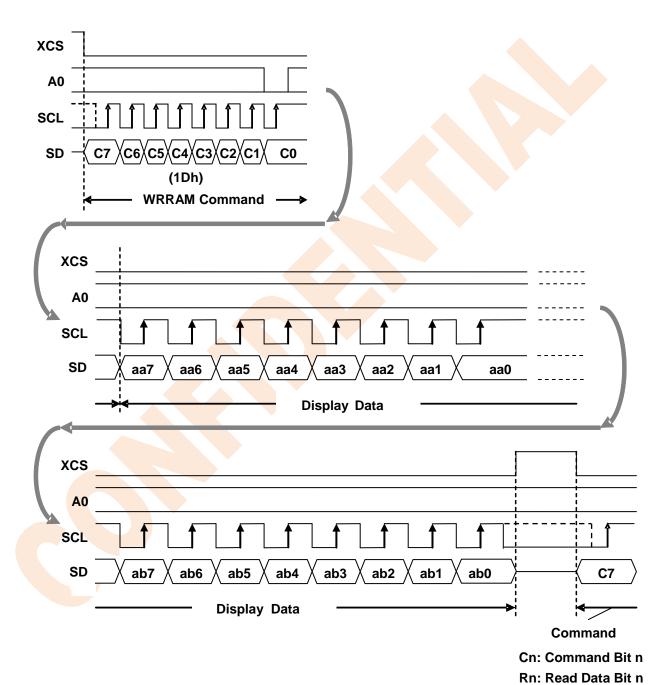

| (      | 12) WRRAM (WRite RAM): Display data RAM write                                  | 59 |

| (      | 13) NLSET (N Line inversion SET): N-line set                                   | 60 |

| (      | 14) DISLINSET (number of DISplay LINes SET): Number of display lines set       |    |

| -      | 15) OSCON (OSCillator ON): Built-in oscillation circuit ON                     |    |

| (      | 16) OSCOFF (OSCillator OFF): Built-in oscillation circuit OFF                  |    |

| -      | 17) FCLSEL (Frequency of display CLock SELect): Display clock frequency select |    |

| •      | 18) FBSTSEL (Frequency of BooST clock SELect): Booster clock frequency select  |    |

| -      | 19) PWRCTL (PoWeR supply ConTroL): Power supply control for LCD drive          |    |

| -      | 20) PWRON (PoWeR supply ON): Power supply ON for LCD drive                     |    |

| -      | 21) PWROFF (PoWeR supply OFF): Power supply OFF for LCD drive                  |    |

| -      | 23) BIASSET (Icd BIAS SET): LCD bias set                                       |    |

| -      | 24) DSCHG (DiSCHarGe): Discharge                                               |    |

| •      | 25) PSON (Power Save ON): Power save ON                                        |    |

| -      | 26) PSOFF (Power Save OFF): Power save OFF                                     |    |

| -      | 27) SWRST (SoftWare ReSeT): Software reset                                     |    |

| -      | 28) RDICREV (ReaD IC REVision): IC revision read                               |    |

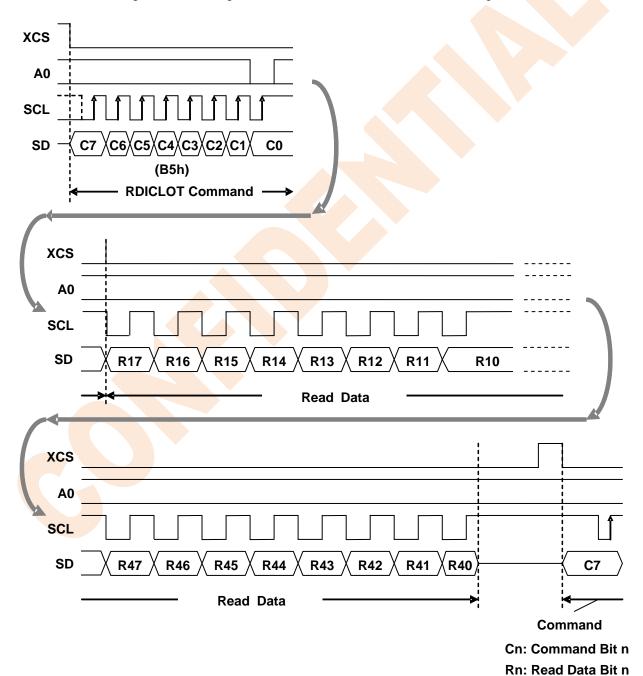

| -      | 29) RDICLOT (ReaD IC LOT number): IC lot number read                           | 68 |

| -      | 30) NOP (Non Operation)                                                        | 68 |

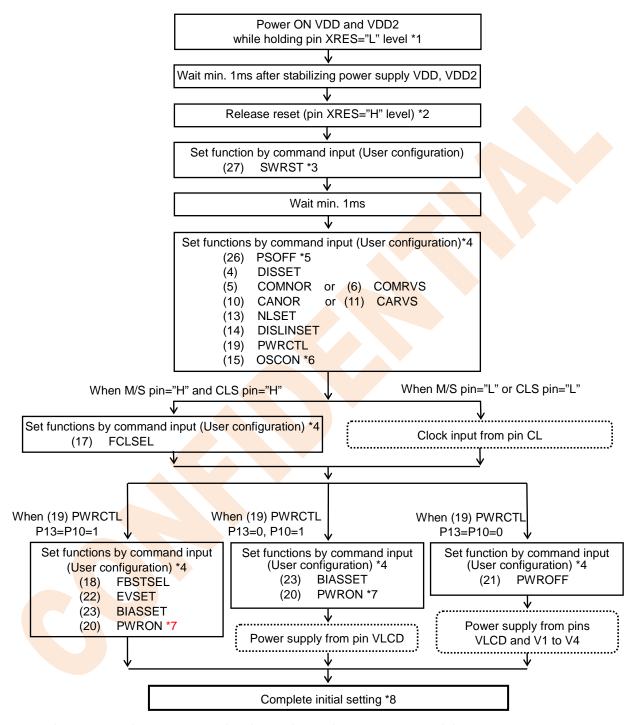

| 8. In: | struction Settings                                                             | 69 |

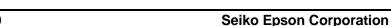

| 8.1    | Initial Setting                                                                |    |

| 8.2    | Data Display                                                                   |    |

| -      |                                                                                |    |

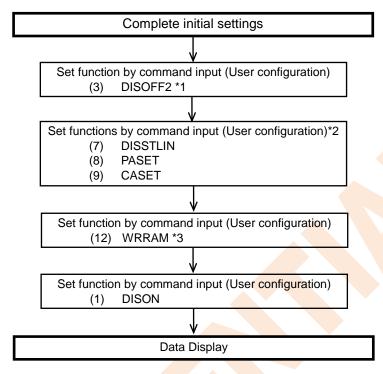

| 8.3    | Refreshing                                                                     |    |

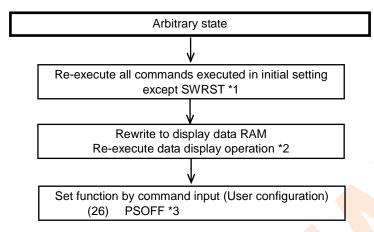

| 8.4    | Pow <mark>er Save ON / OFF</mark>                                              |    |

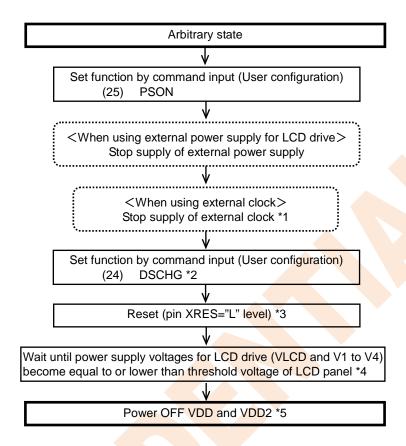

| 8.5    | Power OFF                                                                      | 74 |

| 9. Ak  | osolute Maximum Ratings                                                        | 75 |

| 10. DO | C Characteristics                                                              | 76 |

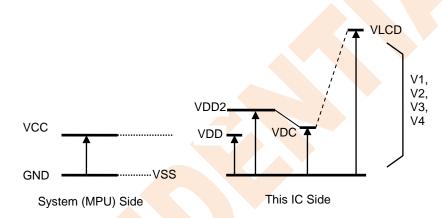

|        | Power Supply Voltage                                                           |    |

|        | Pin Characteristics                                                            |    |

|        | Oscillation Characteristics                                                    |    |

|        | Current Consumption                                                            |    |

|        | 4.1 Static Current Consumption                                                 |    |

|        | 4.2 Dynamic Current Consumption                                                |    |

|        | 0.4.2.1 Current Consumption when Display ON                                    | 79 |

| 10.4.2.2 Current Consumption when Accessing to MPU | 81 |

|----------------------------------------------------|----|

| 11. AC Characteristics                             | 82 |

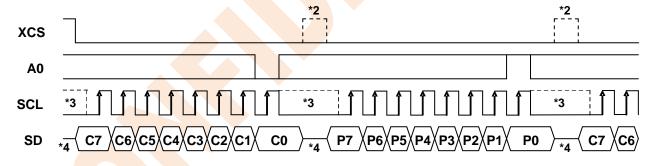

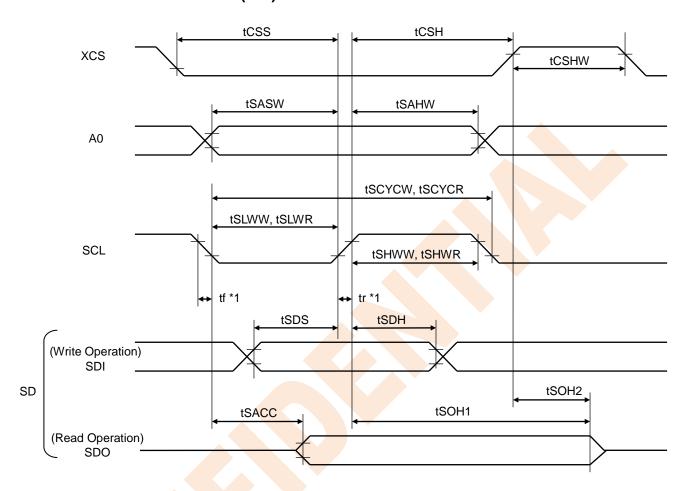

| 11.1 4-wire Serial Interface (SPI)                 |    |

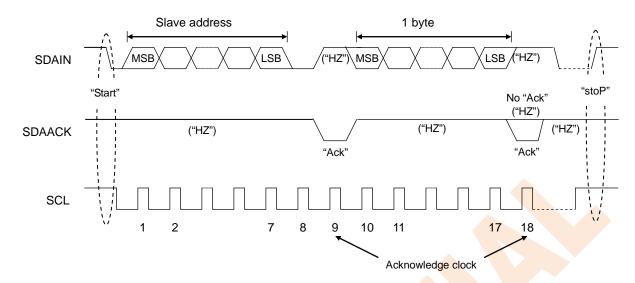

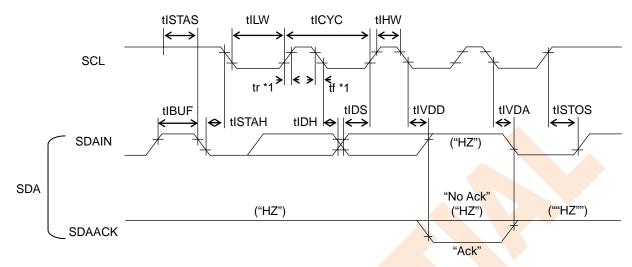

| 11.2 2-wire Serial Interface (I2C-Bus Compliant)   |    |

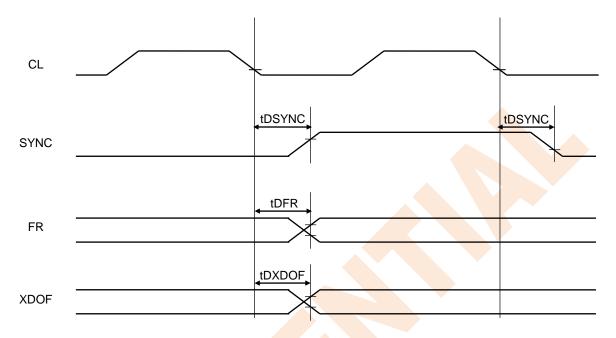

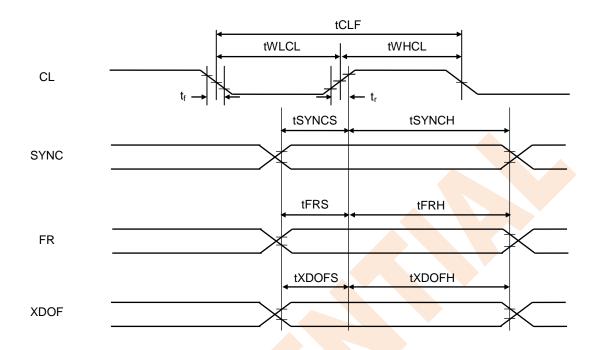

| 11.3 I/O Timing of Display Timing Signal           | 85 |

| 11.3.1 Output Timing                               | 85 |

| 11.3.2 Input Timing                                | 86 |

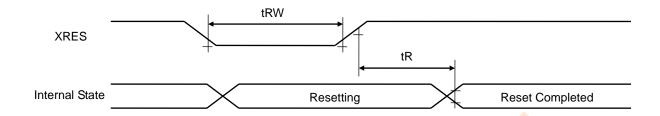

| 11.4 Reset Timing                                  | 87 |

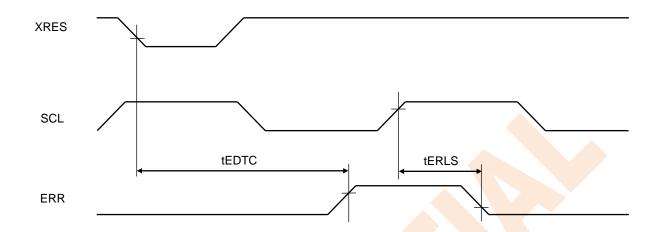

| 11.5 ERR Output Timing                             |    |

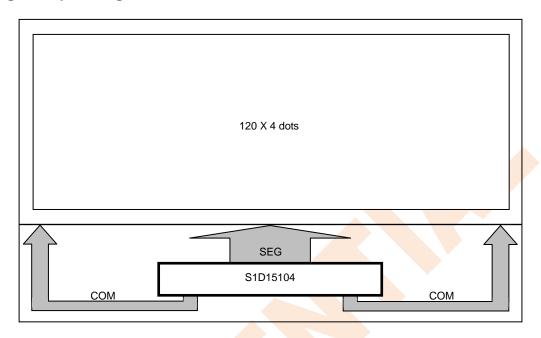

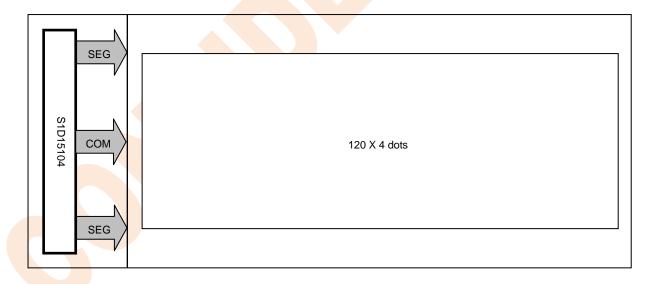

| 12. LCD Panel Connection Examples                  | 89 |

| 12.1 Single Chip Configuration                     |    |

| 12.2 2-Chip Configuration                          |    |

|                                                    |    |

| 13. Precautions                                    | 91 |

| Revision History                                   | 92 |

| · · · · · · · · · · · · · · · · · · ·              |    |

# 1. Description

The S1D15104 series (hereinafter referred to as "S1D15104") is an LCD driver designed for segment type LCD display system and can be connected directly to the bus of the microcomputer. The S1D15104 stores serial display data transmitted by the microcomputer to the built-in display data RAM, and all LCD drive signals are generated by this IC independently from the microcomputer.

The S1D15104 contains the display data RAM with a capacity of  $120 \times 4 \times 2$  bits, 120 segment output circuits and 4 common output circuits. The maximum display resolution of S1D15104 is 480 pixels and there is a one-to-one correspondence between each of the bits in the display data RAM and each of the pixels on the LCD panel. In addition, multiple chips can be cascaded as a master/slave connection to extend larger LCD displays. The S1D15104 features a built-in oscillation circuit and an LCD bias generating circuit that can be comprised of a display system with minimized number of external components.

#### 2. Features

- Serial Interface (Selectable by pin setting)

- 4-wire (SPI)

- 2-wire (I2C compliant)

- Display Data RAM

- Capacity:  $120 \times 4 \times 2 = 960 \text{ bits}$

- LCD Driver

- Segment: 120 outputs

- Common: 4 outputs

- LCD Drive Duty Configuration

- 1/4, 1/3, 1/2, 1/1(Static drive)

Applicable for +1H Dummy ON/OFF

- LCD Drive Bias Configuration

- 1/3, 1/2, 1/1(Static drive)

- Built-in Power Supply Circuit for LCD Drive

- VLCD voltage generating circuit

- Electronic volume

- Voltage regulator circuit for booster (VDC regulator)

- Booster circuit with built-in capacitor

- Bias voltages (V1, V2, V3, V4) generating circuit

- Applicable for external power supply

- Built-in Oscillation Circuit

- Adjustable frame frequency by command setting (Max. 381Hz)

- Applicable for external clock input

- A Variety of Command Functions

- Read Function for IC Revision and Lot Number (Only for 4-wire serial interface)

- Power-on Reset Function

- Extendable Display Capacity by comprising of Master/Slave Connection

- Operating Power Supply Voltages

- LCD Drive VLCD : 2.7V (\*1) to 8.0V (\*2)

- \*1: min. 4.5V (TBD) in case of 1/3 and 1/2 bias

- \*2: max. 7.0V in case of using VLCD voltage generating circuit

- Booster : VDD2 : 2.7V to 5.5V - Logic : VDD : 2.7V to 5.5V

- Shipping Form

2

- Au bump chip

- Operating Temperature Range

- $-40 \text{ to } +105^{\circ}\text{C}$

- AEC-Q100 Corresponsive

- This IC is not designed to comply with radiation- or light- protected design. Refer to the description in section "13. Precautions".

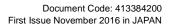

# 3. Block Diagram

Figure 3 Block Diagram of S1D15104

3

## 4. Pin Assignment

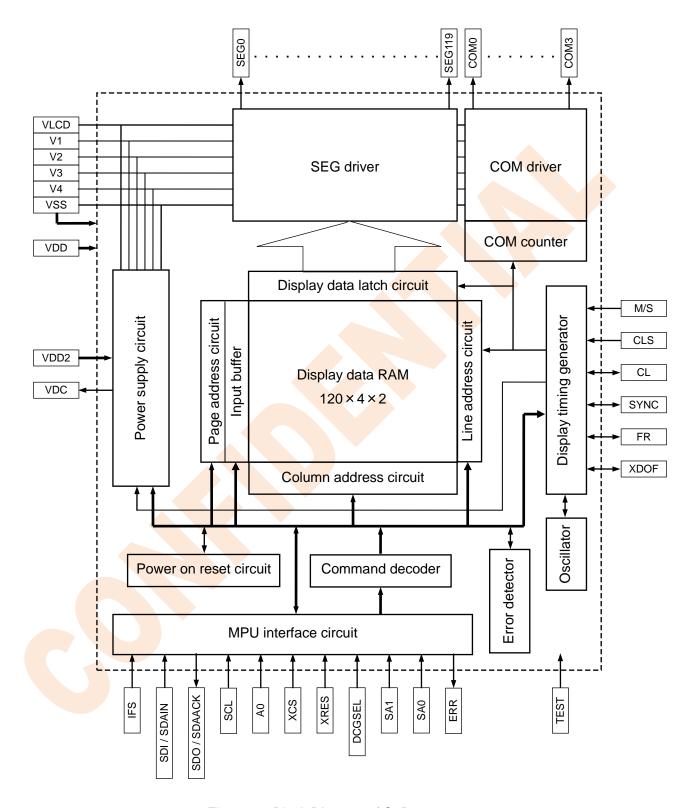

### 4.1 Chip Specifications

Figure 4.1 Bump Assignment Drawing

4

# 4.2 Bump Center Coordinates

Table 4.2 Bump Center Coordinates

| BUMP No. | Pin Name | X (μm) | Υ (μm)  |

|----------|----------|--------|---------|

| 1        | NC       | 445.0  | -5125.0 |

| 2        | NC       | 445.0  | -5075.0 |

| 3        | NC       | 445.0  | -5025.0 |

| 4        | NC       | 445.0  | -4975.0 |

| 5        | NC       | 445.0  | -4925.0 |

| 6        | NC       | 445.0  | -4875.0 |

| 7        | NC       | 445.0  | -4825.0 |

| 8        | NC       | 445.0  | -4775.0 |

| 9        | NC       | 445.0  | -4725.0 |

| 10       | NC       | 445.0  | -4675.0 |

| 11       | NC       | 445.0  | -4625.0 |

| 12       | NC       | 445.0  | -4575.0 |

| 13       | NC       | 445.0  | -4525.0 |

| 14       | NC       | 445.0  | -4475.0 |

| 15       | NC       | 445.0  | -4425.0 |

| 16       | NC       | 445.0  | -4375.0 |

| 17       | NC       | 445.0  | -4325.0 |

| 18       | NC       | 445.0  | -4275.0 |

| 19       | NC       | 445.0  | -4225.0 |

| 20       | NC       | 445.0  | -4175.0 |

| 21       | NC       | 445.0  | -4125.0 |

| 22       | NC       | 445.0  | -4075.0 |

| 23       | NC       | 445.0  | -4025.0 |

| 24       | NC       | 445.0  | -3975.0 |

| 25       | NC       | 445.0  | -3925.0 |

| 26       | NC       | 445.0  | -3875.0 |

| 27       | NC       | 445.0  | -3825.0 |

| 28       | COM0     | 445.0  | -3775.0 |

| 29       | COM1     | 445.0  | -3725.0 |

| 30       | COM2     | 445.0  | -3675.0 |

| 31       | COM3     | 445.0  | -3625.0 |

| 32       | NC       | 445.0  | -3575.0 |

| 33       | NC       | 437.0  | -3420.0 |

| 34       | V4       | 437.0  | -3344.0 |

| 35       | V4       | 437.0  | -3268.0 |

| 36       | V4       | 437.0  | -3192.0 |

| 37       | V4       | 437.0  | -3116.0 |

| 38       | V3       | 437.0  | -3040.0 |

| 39       | V3       | 437.0  | -2964.0 |

| 40       | V3       | 437.0  | -2888.0 |

| BUMP No. | Pin Name | X (μm) | Υ (μm)  |

|----------|----------|--------|---------|

| 41       | V3       | 437.0  | -2812.0 |

| 42       | NC       | 437.0  | -2736.0 |

| 43       | V2       | 437.0  | -2660.0 |

| 44       | V2       | 437.0  | -2584.0 |

| 45       | V2       | 437.0  | -2508.0 |

| 46       | V2       | 437.0  | -2432.0 |

| 47       | V1       | 437.0  | -2356.0 |

| 48       | V1       | 437.0  | -2280.0 |

| 49       | V1       | 437.0  | -2204.0 |

| 50       | V1       | 437.0  | -2128.0 |

| 51       | VLCD     | 437.0  | -2052.0 |

| 52       | VLCD     | 437.0  | -1976.0 |

| 53       | VLCD     | 437.0  | -1900.0 |

| 54       | VLCD     | 437.0  | -1824.0 |

| 55       | VLCD     | 437.0  | -1748.0 |

| 56       | VLCD     | 437.0  | -1672.0 |

| 57       | VLCD     | 437.0  | -1596.0 |

| 58       | VLCD     | 437.0  | -1520.0 |

| 59       | VLCD     | 437.0  | -1444.0 |

| 60       | VLCD     | 437.0  | -1368.0 |

| 61       | NC       | 437.0  | -1292.0 |

| 62       | VDC      | 437.0  | -1216.0 |

| 63       | VDD2     | 437.0  | -1140.0 |

| 64       | VDD2     | 437.0  | -1064.0 |

| 65       | VDD2     | 437.0  | -988.0  |

| 66       | VDD2     | 437.0  | -912.0  |

| 67       | VDD2     | 437.0  | -836.0  |

| 68       | VDD2     | 437.0  | -760.0  |

| 69       | VDD      | 437.0  | -684.0  |

| 70       | VDD      | 437.0  | -608.0  |

| 71       | VDD      | 437.0  | -532.0  |

| 72       | VDD      | 437.0  | -456.0  |

| 73       | VDD      | 437.0  | -380.0  |

| 74       | VDD      | 437.0  | -304.0  |

| 75       | IFS      | 437.0  | -228.0  |

| 76       | SA0      | 437.0  | -152.0  |

| 77       | VSS      | 437.0  | -76.0   |

| 78       | SA1      | 437.0  | 0.0     |

| 79       | VDD      | 437.0  | 76.0    |

| 80       | M/S      | 437.0  | 152.0   |

|          |          |        |         |

# 4. Pin Assignment

Table 4.2 Bump Center Coordinates (continued)

| BUMP No. | Pin Name   | X (μm) | Υ (μm) |

|----------|------------|--------|--------|

| 81       | CLS        | 437.0  | 228.0  |

| 82       | TEST1      | 437.0  | 304.0  |

| 83       | TEST2      | 437.0  | 380.0  |

| 84       | TEST3      | 437.0  | 456.0  |

| 85       | TEST4      | 437.0  | 532.0  |

| 86       | TEST5      | 437.0  | 608.0  |

| 87       | VSS        | 437.0  | 684.0  |

| 88       | VSS        | 437.0  | 760.0  |

| 89       | VSS        | 437.0  | 836.0  |

| 90       | VSS        | 437.0  | 912.0  |

| 91       | VSS        | 437.0  | 988.0  |

| 92       | VSS        | 437.0  | 1064.0 |

| 93       | TEST11     | 437.0  | 1140.0 |

| 94       | TEST12     | 437.0  | 1216.0 |

| 95       | TEST13     | 437.0  | 1292.0 |

| 96       | VSS        | 437.0  | 1368.0 |

| 97       | VSS        | 437.0  | 1444.0 |

| 98       | VSS        | 437.0  | 1520.0 |

| 99       | VSS        | 437.0  | 1596.0 |

| 100      | VSS        | 437.0  | 1672.0 |

| 101      | TEST6      | 437.0  | 1748.0 |

| 102      | TEST7      | 437.0  | 1824.0 |

| 103      | TEST8      | 437.0  | 1900.0 |

| 104      | TEST9      | 437.0  | 1976.0 |

| 105      | TEST10     | 437.0  | 2052.0 |

| 106      | DCGSEL     | 437.0  | 2128.0 |

| 107      | VDD        | 437.0  | 2204.0 |

| 108      | XRES       | 437.0  | 2280.0 |

| 109      | XCS        | 437.0  | 2356.0 |

| 110      | A0         | 437.0  | 2432.0 |

| 111      | VSS        | 437.0  | 2508.0 |

| 112      | SDI/SDAIN  | 437.0  | 2584.0 |

| 113      | SDI/SDAIN  | 437.0  | 2660.0 |

| 114      | SDO/SDAACK | 437.0  | 2736.0 |

| 115      | SDO/SDAACK | 437.0  | 2812.0 |

| 116      | SCL        | 437.0  | 2888.0 |

| 117      | SCL        | 437.0  | 2964.0 |

| 118      | ERR        | 437.0  | 3040.0 |

| 119      | CL         | 437.0  | 3116.0 |

| 120      | SYNC       | 437.0  | 3192.0 |

| BUMP No. | Pin Name | X (μm)        | Υ (μm) |

|----------|----------|---------------|--------|

| 121      | FR       | 437.0         | 3268.0 |

| 122      | XDOF     | 437.0         | 3344.0 |

| 123      | NC       | 437.0         | 3420.0 |

| 124      | NC       | 445.0         | 3575.0 |

| 125      | COM3     | 445.0         | 3625.0 |

| 126      | COM2     | 445.0         | 3675.0 |

| 127      | COM1     | 445 <u>.0</u> | 3725.0 |

| 128      | COM0     | 445.0         | 3775.0 |

| 129      | NC       | 445.0         | 3825.0 |

| 130      | NC       | 445.0         | 3875.0 |

| 131      | NC       | 445.0         | 3925.0 |

| 132      | NC       | 445.0         | 3975.0 |

| 133      | NC       | 445.0         | 4025.0 |

| 134      | NC       | 445.0         | 4075.0 |

| 135      | NC       | 445.0         | 4125.0 |

| 136      | NC       | 445.0         | 4175.0 |

| 137      | NC       | 445.0         | 4225.0 |

| 138      | NC       | 445.0         | 4275.0 |

| 139      | NC       | 445.0         | 4325.0 |

| 140      | NC       | 445.0         | 4375.0 |

| 141      | NC       | 445.0         | 4425.0 |

| 142      | NC       | 445.0         | 4475.0 |

| 143      | NC       | 445.0         | 4525.0 |

| 144      | NC       | 445.0         | 4575.0 |

| 145      | NC       | 445.0         | 4625.0 |

| 146      | NC       | 445.0         | 4675.0 |

| 147      | NC       | 445.0         | 4725.0 |

| 148      | NC       | 445.0         | 4775.0 |

| 149      | NC       | 445.0         | 4825.0 |

| 150      | NC       | 445.0         | 4875.0 |

| 151      | NC       | 445.0         | 4925.0 |

| 152      | NC       | 445.0         | 4975.0 |

| 153      | NC       | 445.0         | 5025.0 |

| 154      | NC       | 445.0         | 5075.0 |

| 155      | NC       | 445.0         | 5125.0 |

| 156      | NC       | -445.0        | 5125.0 |

| 157      | NC       | -445.0        | 5075.0 |

| 158      | NC       | -445.0        | 5025.0 |

| 159      | NC       | -445.0        | 4975.0 |

| 160      | NC       | -445.0        | 4925.0 |

Table 4.2 Bump Center Coordinates (continued)

| BUMP No. | Pin Name | X (μm) | Υ (μm) |

|----------|----------|--------|--------|

| 161      | NC       | -445.0 | 4875.0 |

| 162      | NC       | -445.0 | 4825.0 |

| 163      | NC       | -445.0 | 4775.0 |

| 164      | NC       | -445.0 | 4725.0 |

| 165      | NC       | -445.0 | 4675.0 |

| 166      | NC       | -445.0 | 4625.0 |

| 167      | NC       | -445.0 | 4575.0 |

| 168      | NC       | -445.0 | 4525.0 |

| 169      | NC       | -445.0 | 4475.0 |

| 170      | NC       | -445.0 | 4425.0 |

| 171      | NC       | -445.0 | 4375.0 |

| 172      | NC       | -445.0 | 4325.0 |

| 173      | NC       | -445.0 | 4275.0 |

| 174      | NC       | -445.0 | 4225.0 |

| 175      | NC       | -445.0 | 4175.0 |

| 176      | NC       | -445.0 | 4125.0 |

| 177      | NC       | -445.0 | 4075.0 |

| 178      | NC       | -445.0 | 4025.0 |

| 179      | NC       | -445.0 | 3975.0 |

| 180      | NC       | -445.0 | 3925.0 |

| 181      | NC       | -445.0 | 3875.0 |

| 182      | NC       | -445.0 | 3825.0 |

| 183      | NC       | -445.0 | 3775.0 |

| 184      | NC       | -445.0 | 3725.0 |

| 185      | NC       | -445.0 | 3675.0 |

| 186      | NC       | -445.0 | 3625.0 |

| 187      | NC       | -445.0 | 3575.0 |

| 188      | NC       | -445.0 | 3525.0 |

| 189      | NC       | -445.0 | 3475.0 |

| 190      | NC       | -445.0 | 3425.0 |

| 191      | NC       | -445.0 | 3375.0 |

| 192      | NC       | -445.0 | 3325.0 |

| 193      | NC       | -445.0 | 3275.0 |

| 194      | SEG0     | -445.0 | 3225.0 |

| 195      | SEG1     | -445.0 | 3175.0 |

| 196      | SEG2     | -445.0 | 3125.0 |

| 197      | SEG3     | -445.0 | 3075.0 |

| 198      | SEG4     | -445.0 | 3025.0 |

| 199      | SEG5     | -445.0 | 2975.0 |

| 200      | SEG6     | -445.0 | 2925.0 |

| BUMP No. | Pin Name | X (μm) | Υ (μm) |

|----------|----------|--------|--------|

| 201      | SEG7     | -445.0 | 2875.0 |

| 202      | SEG8     | -445.0 | 2825.0 |

| 203      | SEG9     | -445.0 | 2775.0 |

| 204      | SEG10    | -445.0 | 2725.0 |

| 205      | SEG11    | -445.0 | 2675.0 |

| 206      | SEG12    | -445.0 | 2625.0 |

| 207      | SEG13    | -445.0 | 2575.0 |

| 208      | SEG14    | -445.0 | 2525.0 |

| 209      | SEG15    | -445.0 | 2475.0 |

| 210      | SEG16    | -445.0 | 2425.0 |

| 211      | SEG17    | -445.0 | 2375.0 |

| 212      | SEG18    | -445.0 | 2325.0 |

| 213      | SEG19    | -445.0 | 2275.0 |

| 214      | SEG20    | -445.0 | 2225.0 |

| 215      | SEG21    | -445.0 | 2175.0 |

| 216      | SEG22    | -445.0 | 2125.0 |

| 217      | SEG23    | -445.0 | 2075.0 |

| 218      | SEG24    | -445.0 | 2025.0 |

| 219      | SEG25    | -445.0 | 1975.0 |

| 220      | SEG26    | -445.0 | 1925.0 |

| 221      | SEG27    | -445.0 | 1875.0 |

| 222      | SEG28    | -445.0 | 1825.0 |

| 223      | SEG29    | -445.0 | 1775.0 |

| 224      | SEG30    | -445.0 | 1725.0 |

| 225      | SEG31    | -445.0 | 1675.0 |

| 226      | SEG32    | -445.0 | 1625.0 |

| 227      | SEG33    | -445.0 | 1575.0 |

| 228      | SEG34    | -445.0 | 1525.0 |

| 229      | SEG35    | -445.0 | 1475.0 |

| 230      | SEG36    | -445.0 | 1425.0 |

| 231      | SEG37    | -445.0 | 1375.0 |

| 232      | SEG38    | -445.0 | 1325.0 |

| 233      | SEG39    | -445.0 | 1275.0 |

| 234      | SEG40    | -445.0 | 1225.0 |

| 235      | SEG41    | -445.0 | 1175.0 |

| 236      | SEG42    | -445.0 | 1125.0 |

| 237      | SEG43    | -445.0 | 1075.0 |

| 238      | SEG44    | -445.0 | 1025.0 |

| 239      | SEG45    | -445.0 | 975.0  |

| 240      | SEG46    | -445.0 | 925.0  |

|          |          |        |        |

# 4. Pin Assignment

Table 4.2 Bump Center Coordinates (continued)

| BUMP No. | Pin Name | X (μm) | Υ (μm)  |

|----------|----------|--------|---------|

| 241      | SEG47    | -445.0 | 875.0   |

| 242      | SEG48    | -445.0 | 825.0   |

| 243      | SEG49    | -445.0 | 775.0   |

| 244      | SEG50    | -445.0 | 725.0   |

| 245      | SEG51    | -445.0 | 675.0   |

| 246      | SEG52    | -445.0 | 625.0   |

| 247      | SEG53    | -445.0 | 575.0   |

| 248      | SEG54    | -445.0 | 525.0   |

| 249      | SEG55    | -445.0 | 475.0   |

| 250      | SEG56    | -445.0 | 425.0   |

| 251      | SEG57    | -445.0 | 375.0   |

| 252      | SEG58    | -445.0 | 325.0   |

| 253      | SEG59    | -445.0 | 275.0   |

| 254      | NC       | -445.0 | 225.0   |

| 255      | COM0     | -445.0 | 175.0   |

| 256      | COM1     | -445.0 | 125.0   |

| 257      | COM2     | -445.0 | 75.0    |

| 258      | COM3     | -445.0 | 25.0    |

| 259      | NC       | -445.0 | -25.0   |

| 260      | NC       | -445.0 | -75.0   |

| 261      | NC       | -445.0 | -125.0  |

| 262      | NC       | -445.0 | -175.0  |

| 263      | NC       | -445.0 | -225.0  |

| 264      | SEG60    | -445.0 | -275.0  |

| 265      | SEG61    | -445.0 | -325.0  |

| 266      | SEG62    | -445.0 | -375.0  |

| 267      | SEG63    | -445.0 | -425.0  |

| 268      | SEG64    | -445.0 | -475.0  |

| 269      | SEG65    | -445.0 | -525.0  |

| 270      | SEG66    | -445.0 | -575.0  |

| 271      | SEG67    | -445.0 | -625.0  |

| 272      | SEG68    | -445.0 | -675.0  |

| 273      | SEG69    | -445.0 | -725.0  |

| 274      | SEG70    | -445.0 | -775.0  |

| 275      | SEG71    | -445.0 | -825.0  |

| 276      | SEG72    | -445.0 | -875.0  |

| 277      | SEG73    | -445.0 | -925.0  |

| 278      | SEG74    | -445.0 | -975.0  |

| 279      | SEG75    | -445.0 | -1025.0 |

| 280      | SEG76    | -445.0 | -1075.0 |

| BUMP No. | Pin Name | X (μm) | Υ (μm)  |

|----------|----------|--------|---------|

| 281      | SEG77    | -445.0 | -1125.0 |

| 282      | SEG78    | -445.0 | -1175.0 |

| 283      | SEG79    | -445.0 | -1225.0 |

| 284      | SEG80    | -445.0 | -1275.0 |

| 285      | SEG81    | -445.0 | -1325.0 |

| 286      | SEG82    | -445.0 | -1375.0 |

| 287      | SEG83    | -445.0 | -1425.0 |

| 288      | SEG84    | -445.0 | -1475.0 |

| 289      | SEG85    | -445.0 | -1525.0 |

| 290      | SEG86    | -445.0 | -1575.0 |

| 291      | SEG87    | -445.0 | -1625.0 |

| 292      | SEG88    | -445.0 | -1675.0 |

| 293      | SEG89    | -445.0 | -1725.0 |

| 294      | SEG90    | -445.0 | -1775.0 |

| 295      | SEG91    | -445.0 | -1825.0 |

| 296      | SEG92    | -445.0 | -1875.0 |

| 297      | SEG93    | -445.0 | -1925.0 |

| 298      | SEG94    | -445.0 | -1975.0 |

| 299      | SEG95    | -445.0 | -2025.0 |

| 300      | SEG96    | -445.0 | -2075.0 |

| 301      | SEG97    | -445.0 | -2125.0 |

| 302      | SEG98    | -445.0 | -2175.0 |

| 303      | SEG99    | -445.0 | -2225.0 |

| 304      | SEG100   | -445.0 | -2275.0 |

| 305      | SEG101   | -445.0 | -2325.0 |

| 306      | SEG102   | -445.0 | -2375.0 |

| 307      | SEG103   | -445.0 | -2425.0 |

| 308      | SEG104   | -445.0 | -2475.0 |

| 309      | SEG105   | -445.0 | -2525.0 |

| 310      | SEG106   | -445.0 | -2575.0 |

| 311      | SEG107   | -445.0 | -2625.0 |

| 312      | SEG108   | -445.0 | -2675.0 |

| 313      | SEG109   | -445.0 | -2725.0 |

| 314      | SEG110   | -445.0 | -2775.0 |

| 315      | SEG111   | -445.0 | -2825.0 |

| 316      | SEG112   | -445.0 | -2875.0 |

| 317      | SEG113   | -445.0 | -2925.0 |

| 318      | SEG114   | -445.0 | -2975.0 |

| 319      | SEG115   | -445.0 | -3025.0 |

| 320      | SEG116   | -445.0 | -3075.0 |

|          |          |        |         |

Table 4.2 Bump Center Coordinates (continued)

| BUMP No. | Pin Name | X (μm)           | Υ (μm)                |

|----------|----------|------------------|-----------------------|

| 321      | SEG117   | -445.0           | -3125.0               |

| 322      | SEG118   | -445.0           | -3125.0               |

| 323      | SEG119   | -445.0           | -3225.0               |

| 324      | NC       | -445.0           | -3275.0               |

|          |          | -445.0           |                       |

| 325      | NC<br>NC | -445.0<br>-445.0 | -3325.0               |

| 326      | NC<br>NC |                  | -3375.0               |

| 327      | NC<br>NC | -445.0           | -3425.0               |

| 328      | NC<br>NC | -445.0           | -3475.0               |

| 329      | NC       | -445.0           | -3525.0               |

| 330      | NC       | -445.0           | -3575.0               |

| 331      | NC       | -445.0           | -3625.0               |

| 332      | NC       | -445.0           | -3675.0               |

| 333      | NC       | -445.0           | -3725.0               |

| 334      | NC       | -445.0           | -3775.0               |

| 335      | NC       | -445.0           | -3825.0               |

| 336      | NC       | -445.0           | -3875.0               |

| 337      | NC       | -445.0           | -3925.0               |

| 338      | NC       | -445.0           | -3975.0               |

| 339      | NC       | -445.0           | -4025. <mark>0</mark> |

| 340      | NC       | -445.0           | -4075.0               |

| 341      | NC       | -445.0           | -4125.0               |

| 342      | NC       | -445.0           | -4175.0               |

| 343      | NC       | -445.0           | -4225.0               |

| 344      | NC       | -445.0           | -4275.0               |

| 345      | NC       | -445.0           | -4325.0               |

| 346      | NC       | -445.0           | -4375.0               |

| 347      | NC       | -445.0           | -4425.0               |

| 348      | NC       | -445.0           | -4475.0               |

| 349      | NC       | -445.0           | -4525.0               |

| 350      | NC       | -445.0           | -4575.0               |

| 351      | NC       | -445.0           | -4625.0               |

| 352      | NC       | -445.0           | -4675.0               |

| 353      | NC       | -445.0           | -4725.0               |

| 354      | NC       | -445.0           | -4775.0               |

| 355      | NC       | -445.0           | -4825.0               |

| 356      | NC       | -445.0           | -4875.0               |

| 357      | NC       | -445.0           | -4925.0               |

| 358      | NC       | -445.0           | -4975.0               |

| 359      | NC       | -445.0           | -5025.0               |

| 360      | NC       | -445.0           | -5075.0               |

| 361      | NC       | -445.0           | -5125.0               |

# 5. Pin Description

#### 5.1 **Power Pins**

| Pin Name | I/O   | Description                                                                 | Pin Count |

|----------|-------|-----------------------------------------------------------------------------|-----------|

| VDD      | Power | System power supply pins. Must be supplied common voltage with MPU power    | 8         |

|          | I     | supply VCC.                                                                 |           |

| VDD2     | Power | Power supply pins for VLCD voltage generating circuit. Must be connected to | 6         |

|          | I     | VDD when supplying same voltage level as VDD or not using VLCD voltage      |           |

|          |       | generating circuit.                                                         |           |

| VSS      | Power | 0V pins connected to System GND.                                            | 13        |

|          | I     |                                                                             |           |

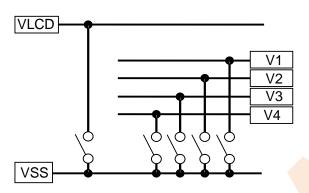

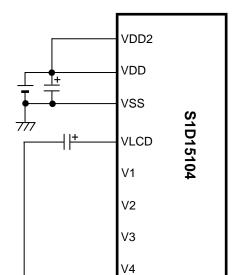

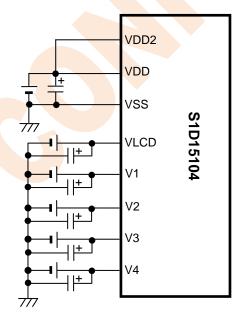

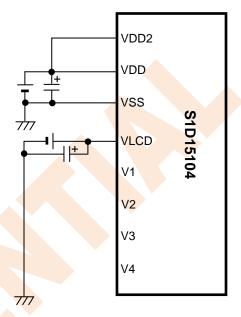

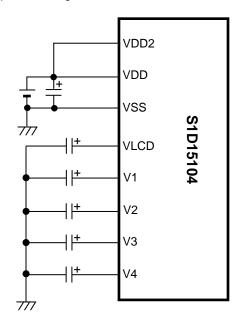

# 5.2 Power Pins for LCD Drive

| Pin Name             | I/O          |                                                              |                                                       | Description                                     |                               |                                                         | Pin Count |  |  |  |  |  |  |  |

|----------------------|--------------|--------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|-------------------------------|---------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| VDC                  | 0            | Regulator output                                             |                                                       | circuit. Must be                                | e left open.                  |                                                         | 1         |  |  |  |  |  |  |  |

| VLCD                 | Power<br>I/O | <ul><li>be connected</li><li>When not us</li></ul>           | VLCD voltage d stabilizing ca                         | pacitors betwe                                  | en VSS and V                  | rage is output. Must<br>/LCD pins.<br>be supplied VLCD  | 10        |  |  |  |  |  |  |  |

| V1<br>V2<br>V3<br>V4 | Power<br>I/O | <ul> <li>When using of bias pins setting. Because</li> </ul> |                                                       |                                                 |                               |                                                         |           |  |  |  |  |  |  |  |

|                      |              |                                                              | 1/3 Bias                                              | 1/2 Bias                                        | 1/1 Bias                      |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V1                                                           |                                                       |                                                 |                               |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V2                                                           | ()                                                    |                                                 |                               |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V3                                                           | 2/3 VLCD                                              | ("HZ")                                          | ("HZ")                        |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V4                                                           | 1/3 VLCD                                              | 1/2 VLCD                                        | ("HZ")                        |                                                         |           |  |  |  |  |  |  |  |

|                      |              | and V4 volta<br>and V3 volta                                 | ages must be si<br>ages when 1/2 I<br>must also be si | upplied from ex<br>pias setting an<br>upplied.) | xternal power of the V1 to V4 | wing V1, V2, V3<br>source. (The V2<br>voltages when 1/1 |           |  |  |  |  |  |  |  |

|                      |              |                                                              | 1/3 Bias                                              | 1/2 Bias                                        | 1/1 Bias                      |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V1                                                           | 2/3 VLCD                                              | 1/2 VLCD                                        | VLCD                          |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V2                                                           | 1/3 VLCD                                              | VSS                                             | VSS                           |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V3                                                           | 2/3 VLCD                                              | VLCD                                            | VLCD                          |                                                         |           |  |  |  |  |  |  |  |

|                      |              | V4                                                           | 1/3 VLCD                                              | 1/2 VLCD                                        | VSS                           |                                                         |           |  |  |  |  |  |  |  |

|                      |              |                                                              |                                                       |                                                 |                               |                                                         |           |  |  |  |  |  |  |  |

# 5.3 MPU Interface Pins

| Pin Name    | I/O      | Description                                                                                                                                                       | <b>Pin Count</b> |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| IFS         | I        | Interface select pin.                                                                                                                                             | 1                |

|             |          | IFS="L": 4-wire serial interface (SPI) IFS="H": 2-wire serial interface (I2C-Bus compliant)                                                                       |                  |

| SDI / SDAIN | ı        | Serial data input pins. Use for control command and display data input. The input                                                                                 | 2                |

|             |          | data is read by the rising edge of the input signal SCL.                                                                                                          |                  |

|             |          | 4-wire serial interface (IFS="L"): SDI input pins.                                                                                                                |                  |

| SDO /       | 0        | <ul> <li>2-wire serial interface (IFS="H"): SDAIN input pins.</li> <li>4-wire serial interface (IFS="L"): SDO serial data output pins. The output data</li> </ul> | 2                |

| SDAACK      | · ·      | is only applicable when reading by commands RDICREV or RDICLOT and the                                                                                            | _                |

|             |          | data is output at the falling edge of the input signal SCL. In the other                                                                                          |                  |

|             |          | conditions, this pin outputs High-impedance ("HiZ") state.  2-wire serial interface (IFS="H"): SDAACK acknowledge output pins. This pin                           |                  |

|             |          | outputs "L" level from the falling edge of the 8th bit to the falling edge of the 9th                                                                             |                  |

|             |          | bit of the input signal SCL. In the other conditions, this pin outputs                                                                                            |                  |

| 001         |          | High-impedance ("HiZ") state.                                                                                                                                     | 2                |

| SCL<br>A0   | <u> </u> | Serial clock input pins. SI input discrimination pin.                                                                                                             | 2                |

| 7.0         | •        | 4-wire serial interface (IFS="L"): SDI input discrimination pin.                                                                                                  | '                |

|             |          | A0="H": SDI input is command parameter.                                                                                                                           |                  |

|             |          | A0="L": SDI input is command.  2-wire serial interface (IFS="H"): Invalid. It is recommended to be tied to "L"                                                    |                  |

|             |          | level.                                                                                                                                                            |                  |

| XCS         | I        | Chip select pin.                                                                                                                                                  | 1                |

|             |          | 4-wire serial interface (IFS="L"): Chip select pin.  YOS "I" Active Data (Command input and output age has applied.                                               |                  |

|             |          | XCS="L": Active. Data/Command input and output can be enabled. XCS="H": Inactive. Data/Command input and output can be disabled.                                  |                  |

|             |          | 2-wire serial interface (IFS="H"): Invalid. It is recommended to be tied to "L"                                                                                   |                  |

|             |          | level.                                                                                                                                                            |                  |

| XRES        | ı        | Reset pin.                                                                                                                                                        | 1                |

|             |          | When XRES="L", this IC is initialized. This IC contains power-on reset function. When using only power-on reset function                                          |                  |

|             |          | without this reset pin, this pin must be tied to "H" level.                                                                                                       |                  |

| DCGSEL      | I        | Discharge ON/OFF select pin during execution of resetting (XRES="L"). This pin is                                                                                 | 1                |

|             |          | enabled in case of master mode (M/S="H").  DCGSEL="H": Discharge ON during execution of resetting (XRES="L").                                                     |                  |

|             |          | DCGSEL="L": Discharge OFF during execution of resetting (XRES="L").                                                                                               |                  |

|             |          | In case of slave mode (M/S="L"), this pin is disabled and discharge OFF during                                                                                    |                  |

| SA1, SA0    | 1        | execution of resetting (XRES="L"). It is recommended to be tied to "L" level.  2-wire serial interface (IFS="H"): Slave address (*1) setting pin of this IC.      | 2                |

| 3A1, 3A0    | ı        | The upper 5 bits from MSB of 7 bits address are fixed to (0,1,1,1,0). The slave                                                                                   | _                |

|             |          | address is set by connecting lower 2 bits, SA1 and SA0 (LSB), to either "H" or                                                                                    | ,                |

|             |          | "L" level.                                                                                                                                                        |                  |

|             |          | *1: The "Slave" described here is different from a "Slave" used for cascading of these ICs as a master/slave connection, is a general term of the I2C-Bus         |                  |

|             |          | interface.                                                                                                                                                        |                  |

|             |          | 4-wire serial interface (IFS="L"): Invalid. It is recommended to be tied to "L"                                                                                   |                  |

| ERR         | 0        | level.  Monitoring pin for operating status of this IC.                                                                                                           | 1                |

| LIXIX       | 9        | ERR="L": Normal operation. No error detected.                                                                                                                     | '                |

|             |          | ERR="H": Initial state or error detected.                                                                                                                         |                  |

|             |          | When ERR="H", a part of the internal registers may occur a bit error caused by an                                                                                 |                  |

|             |          | excessive external noise. All commands and all display data must be rewrite to the                                                                                |                  |

|             |          | internal registers and to the display data RAM.                                                                                                                   |                  |

|             |          | In addition, ERR="H" during initial state after resetting.                                                                                                        |                  |

# 5.4 Display Timing Pins

| Pin Name | I/O                                                                                                                 |                                                                                                                                                   |                                                                              |                             | Descr        | iption     |                                                   |           |            | Pin Count |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|--------------|------------|---------------------------------------------------|-----------|------------|-----------|--|--|--|--|--|

| M/S      | I                                                                                                                   | Master                                                                                                                                            | Master or slave operation select pin.                                        |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | ster operation              |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | M/S="L": Slave operation                                                                                                                          |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | In a master operation, the necessary timing signals using for LCD display is output.                                                              |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | Then in a slave operation, the necessary timing signals using for LCD display is input.                                                           |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | The built-in oscillation circuit and the built-in power supply circuit for LCD drive can be                                                       |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | enabled for only master operation.  The following table indicates the setting configuration by pin M/S and CLS                                    |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | THE IOI                                                                                                                                           | The following table indicates the setting configuration by pirr in/o and obs |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | Display                     | Power        |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | M/S                                                                                                                                               | CLS                                                                          | Clock                       | Supply       | CL         | SYNC                                              | FR        | XDOF       |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | Source                      | Circuit      |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | Built-in                    |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | "H"                                                                                                                                               | "H"                                                                          | Oscillation                 | Enable       | Output     | Output                                            | Output    | Output     |           |  |  |  |  |  |

|          |                                                                                                                     | ''                                                                                                                                                | ,,, n                                                                        | Circuit                     |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   | "L"<br>"H" or                                                                | External                    | Enable       | Input      | Output                                            | Output    | Output     |           |  |  |  |  |  |

|          |                                                                                                                     | "L"                                                                                                                                               | "L"                                                                          | External                    | Disable      | Input      | Input                                             | Input     | Input      |           |  |  |  |  |  |

|          |                                                                                                                     | When using this IC as a single chip, this pin must be tied to "H".                                                                                |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

| CLS      | I                                                                                                                   |                                                                                                                                                   |                                                                              | circuit select p            |              |            |                                                   |           |            | 1         |  |  |  |  |  |

|          |                                                                                                                     | When this IC is used as master operation (M/S="H"), this pin selects display clock as                                                             |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | either generated by built-in oscillation circuit or supplied from external clock input.                                                           |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          | M/S="H", CLS="H": Generated by built-in oscillation circuit.  M/S="H", CLS="L": Supplied from external clock input. |                                                                                                                                                   |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | d from                                                                                                                                            |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | When this IC is used as slave operation (M/S="L"), display clock is supplied from external clock input in both CLS settings as "H" and "L" level. |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   | -                                                                            | I clock input, o            | •            |            |                                                   | CI pin    |            |           |  |  |  |  |  |

| CL       | I/O                                                                                                                 |                                                                                                                                                   |                                                                              | •                           |              | о очер     | <del>, , , , , , , , , , , , , , , , , , , </del> | <u> </u>  |            | 1         |  |  |  |  |  |

|          |                                                                                                                     | Display clock input and output pin.  M/S="H" and CLS="H": CL is output.                                                                           |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | M/S="L" or CLS="L": CL is input.                                                                                                                  |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | In case of using this IC as a master/slave connection, each of the CL pins in master                                                              |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | and sla                                                                                                                                           | ıve chip mı                                                                  | ist be connect              | ed togethe   | r.         |                                                   | -         |            |           |  |  |  |  |  |

| SYNC     | I/O                                                                                                                 | Display                                                                                                                                           | frame sta                                                                    | rt signal input             | and output   | pin.       |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | M/                                                                                                                                                | S="H": SYI                                                                   | NC is output.               |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | NC is input.                |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | nis IC as a ma              |              |            | each of th                                        | e SYNC pi | ins in     |           |  |  |  |  |  |

| ED       | 1/0                                                                                                                 |                                                                                                                                                   |                                                                              | chip must be o              | connected    | together.  |                                                   |           |            |           |  |  |  |  |  |

| FR       | I/O                                                                                                                 |                                                                                                                                                   |                                                                              | nd output pin.              |              |            |                                                   |           |            | 1         |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   | S="H": FR                                                                    |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     | M/S="L": FR is input. In case of using this IC as a master/slave connection, each of the FR pins in master                                        |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              |                             |              |            | each of th                                        | e FK pins | ırı master |           |  |  |  |  |  |

| XDOF     | I/O                                                                                                                 |                                                                                                                                                   |                                                                              | ust be connect              | eu logelnei  | i.         |                                                   |           |            | 1         |  |  |  |  |  |

| ADOF     | 1/0                                                                                                                 | Display blanking control pin.  M/S="H": XDOF is output.                                                                                           |                                                                              |                             |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | OF is output.  OF is input. |              |            |                                                   |           |            |           |  |  |  |  |  |

|          |                                                                                                                     |                                                                                                                                                   |                                                                              | nis IC as a ma              | ster/slave o | connection | each of th                                        | e XDOF ni | ins in     |           |  |  |  |  |  |

|          |                                                                                                                     | master                                                                                                                                            | and slave                                                                    | chip must be                | connected t  | together.  | odon or th                                        | CADOI PI  |            |           |  |  |  |  |  |

| L        |                                                                                                                     |                                                                                                                                                   | J.a.                                                                         | pdot 00 t                   |              | 90 1011    |                                                   |           |            |           |  |  |  |  |  |

# 5.5 LCD Output Pins

| Pin Name | I/O | Description   F                                                                                                                                                       |                     |            |                       |                             |              |  |  |  |  |  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|-----------------------|-----------------------------|--------------|--|--|--|--|--|

| SEG0     | 0   | LCD s                                                                                                                                                                 | segment drive outp  | ut pins.   |                       |                             | 120          |  |  |  |  |  |

| to       |     |                                                                                                                                                                       |                     |            |                       | following conditions of the | (1 for each) |  |  |  |  |  |

| SEG119   |     | display data stored in display data RAM and the FR signal.                                                                                                            |                     |            |                       |                             |              |  |  |  |  |  |

|          |     | The VSS level is output when Display OFF mode1 (DISOFF1) or power saving                                                                                              |                     |            |                       |                             |              |  |  |  |  |  |

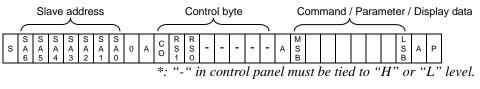

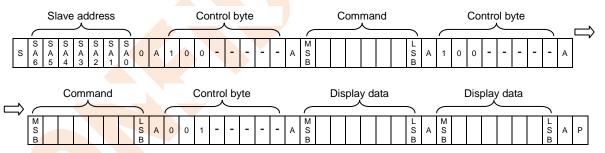

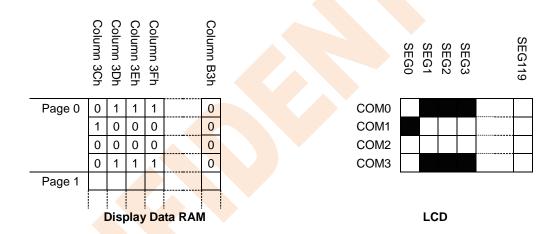

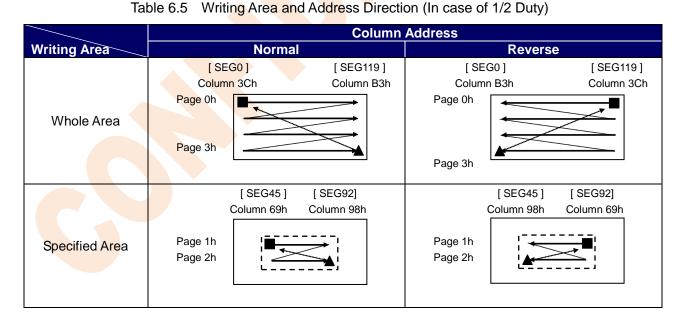

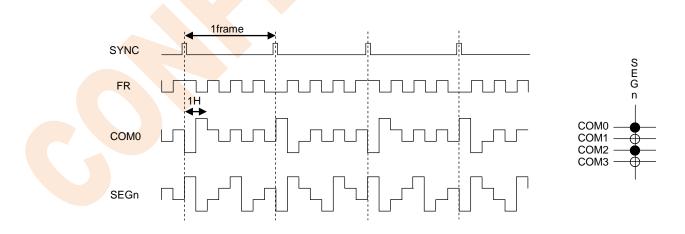

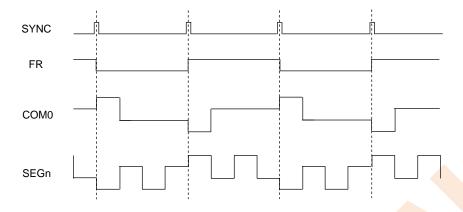

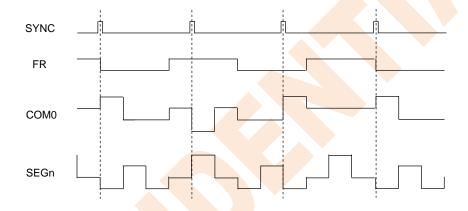

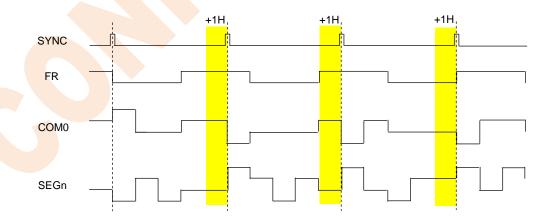

|          |     | mode.  The off state level ("0" level of PAM data in case of normal display mode or "1" level.                                                                        |                     |            |                       |                             |              |  |  |  |  |  |