www.DataSheet4U.com

# The Features of S3C6410

- -

S3C6400 vs. S3C6410 OCT 30, 2007 REV 0.2

\_\_\_\_\_.

www.DataSheet4U.com

# **IMPORTANT NOTICE**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product

#### S3C6410 32-Bit Risc Microcontroller

Copyright © 2007 Samsung Electronics Co.,Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics Co.,Ltd.

Samsung Electronics Co., Ltd. San #24 Nongseo-Dong, Giheung-Gu Yongin-City Gyeonggi-Do, Korea 449-900

TEL: (82)-(331)-209-XXXX FAX: (82)-(331)-209-XXXX

Home-Page URL: <u>Http://www.samsung.com/</u>

Printed in the Republic of Korea

# **Revision History**

| Revision No | Description of Change        | Refer to | Author(s) | Date         |

|-------------|------------------------------|----------|-----------|--------------|

| 0.1         | - Initial Release for review | -        |           | AUG 01, 2007 |

| 0.2         | -Added SYSCON & GPIO         |          |           | OCT 30, 2007 |

ww.DataSheet4U.com

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

# **1. OVERVIEW (A POINT OF DIFFERENCE)**

| -              |                                                                                                   | 1                                                                                                                            |                                                                                                                          |

|----------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|                | S3C6400                                                                                           | S3C6410 (Added IP & function)                                                                                                | S/W change                                                                                                               |

| DMC            |                                                                                                   | Deep Power Down support<br>Variable number of auto-refresh requests<br>before priority change.<br>Improved write termination | 1.bank_bits is fixed for 4<br>banks<br>2. except 1, new controls<br>are implemented in<br>reserved addresses and<br>bits |

|                | Lowest 2 bit of address bit is ignored when accessed with AHB memory channel.                     | Lowest 4 bit of address bit is ignored when accessed with AHB memory channel.                                                | Address map for<br>accessing OneNAND<br>memory contents is<br>different.                                                 |

| OneNANDC       | Maximum burst length of four is<br>supported when accessing through<br>AHB memory access channel. | Maximum burst length of eight is supported when accessing through AHB memory access channel.                                 |                                                                                                                          |

|                | OneNAND controller has a separate<br>clock domain other than AHB clock<br>domain.                 | OneNAND controller shares AHB clock domain with other memory controllers.                                                    |                                                                                                                          |

| NFCON          | 4KB Stepping Stone<br>1/4bit HW ECC<br>512B/2KB page read                                         | 8KB Stepping Stone<br>1/4/8-bit HW ECC<br>512B/2K/4KB page read                                                              | 6400 Compatible<br>Spare ECC generation (<br>bit)                                                                        |

| CFCON          | CFCON 4.0                                                                                         | CFCON 4.01<br>HREADY Bug Fix                                                                                                 | 6400 Compatible                                                                                                          |

| DMAC           | MODEM_IF DMA operation not<br>supported                                                           | Support MODEM_IF DMA (Mem-to-Mem)                                                                                            | New SFRs added                                                                                                           |

| VIC            | Interrupt source                                                                                  | Interrupt source                                                                                                             |                                                                                                                          |

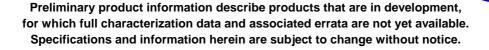

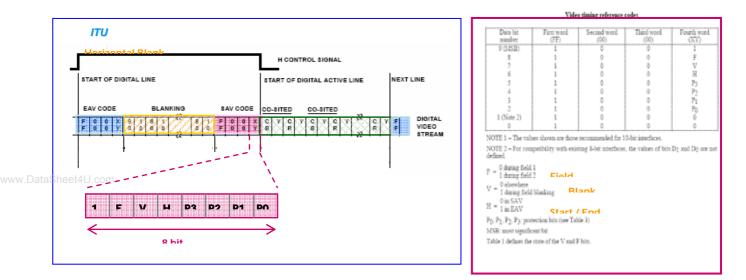

| Display<br>CON | FIMD 4.0                                                                                          | FIMD 4.2.1<br>ITU BT.601/656 interface<br>FIMC local interface sync clock addition                                           | 6400 Compatible                                                                                                          |

| 2D             | FIMG-2D 1.23                                                                                      | FIMG-2D 2.0<br>AXI Master<br>Enhanced Performance                                                                            | Not Compatible 6400                                                                                                      |

| CAMIF          | FIMC 3.0                                                                                          | FIMC 3.2<br>Preview Path Line Buffer for D1<br>Support Interlace input<br>FIMC local interface sync clock addition           |                                                                                                                          |

| MODE IF        | DMA operation not supported                                                                       | DMA operation supported                                                                                                      | New SFRs added                                                                                                           |

| USB OTG        | Power Save mode supported                                                                         | Power Save mode not supported<br>OTG block power down supported                                                              | S/W compatible                                                                                                           |

SAMSUNG ELECTRONICS

#### Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

www.DataSheet4U.com

| HSMMC   | HSMMC(Ver3.1)<br>(support SD Host Controller spec<br>Ver1.0) | HSMMC (Ver4.0)<br>(support SD Host Controller spec Ver2.0)                              | New SFRs added                                                    |

|---------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| IIC     | 1ch                                                          | 2ch                                                                                     |                                                                   |

| UART    | 4ch                                                          | 4ch (3Mbps)                                                                             |                                                                   |

| RTC com | Tick clock source is 32768Hz<br>Tick counter is 16bit        | Tick clock source<br>(32768/16384/8192/4096/2048/1024/512/256/1<br>28/64/32/16/8/4/2/1) | S/W compatible.                                                   |

| IIS     | 16bit I2S 2ea                                                | 24bit Stereo I2S 2ea + 24bit Multi-<br>Channel(up to 5.1) I2S 1ea                       | Bit length setting /<br>Multi-Channel I2S<br>transmission setting |

| TSADC   | 10bit 8channel                                               | 12bit 8channel                                                                          | S/W compatible.                                                   |

| 3D      |                                                              | New                                                                                     |                                                                   |

Note)

1. S/W change: User must change the software in S3C6410 even though user wants to use the same function of S3C6400 (refer to respective chapter in detail)

2. If user would like to use new IP or function, it is necessary to change software

3. There is no software change except above items

/

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

# 2. MEMORY MAP

## 2.1 Address region changes for newly introduced IPs in S3C6410.

## 2.1.1 S3C6400

| Data | Ado<br>Sheet4U.com | dress       | Description | Note |

|------|--------------------|-------------|-------------|------|

|      | 0x7200_0000        | 0x72FF_FFFF | Reserved    |      |

|      | 0x7E00_3000        | 0x7E00_3FFF | Reserved    |      |

|      | 0x7E00_8000        | 0x7E00_8FFF | Reserved    |      |

|      | 0x7E00_9000        | 0x7E00_9FFF | Reserved    |      |

|      | 0x7F00_D000        | 0x7F00_DFFF | Reserved    |      |

|      | 0x7F00_E000        | 0x7F00_EFFF | Reserved    |      |

|      | 0x7F00_F000        | 0x7F00_FFFF | Reserved    |      |

## 2.1.2 S3C6410

| Address     |             | Description                         | Note |

|-------------|-------------|-------------------------------------|------|

| 0x7200_0000 | 0x72FF_FFFF | 3D Graphic Accelerator              |      |

| 0x7E00_3000 | 0x7E00_3FFF | QoS control registers for AXI SPINE |      |

| 0x7E00_8000 | 0x7E00_8FFF | QoS control registers for AXI PERI  |      |

| 0x7E00_9000 | 0x7E00_9FFF | QoS control registers for AXI SFR   |      |

| 0x7F00_D000 | 0x7F00_DFFF | I2S version 4.0                     |      |

| 0x7F00_F000 | 0x7F00_FFFF | 12C                                 |      |

## 2.2 Behavior for accessing reserved address regions

## 2.2.1 S3C6400

Accesses to reserve address region returns OKAY response.

## 2.2.2 S3C6410

Accesses to reserve address region returns ERROR response.

(IP Based reserved region,)

/ww.DataSheet4U.com

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

# **3. SYSTEM CONTROLLER**

## 3.1 Difference summary

## 3.1.1 New functionality

#### .DataSheet4U.com

Added Clock Gating SFRs ( 3D, I2S\_V40, MEM0) Added Clock Source Select SFRS( I2S\_V40) Extended ARM Divider Ratio ( Max. Divider Value 8 -> 16) Added clock divider value for Camera I/F Added DMA select register for Modem I/F. Added SROMC address expand register between DMC0 and SROMC. Additional Power Domain SFRs (3D) Added Operating Mode. ( Synchronous mode) Added DEEP\_STOP Wake-up status register.

## 3.2 Register comparison

#### PLL Control Registers (Added Field)

| EPLL_CON1 | BIT     | DESCRIPTION                            | RESET VALUE |

|-----------|---------|----------------------------------------|-------------|

| RESERVED  | [30:18] | RESERVED                               | 0x0         |

| ICP       | [17:16] | EPLL ICP (Charge Pump Current Control) | 0x0         |

| KDIV      | [15:0]  | PLL K divide value                     | 0x9111      |

#### Clock source control register (Added New SFR)

| CLK_SRC2   | BI     | DESCRIPTION                                                                                                                                                                                        | RESET VALUE |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| RESERVED   | [31:4] | RESERVED                                                                                                                                                                                           | 0x0         |

| AUDIO2_SEL | [2:0]  | Control MUX <sub>AUDIO2</sub> , which is the source clock of IIS_V40<br>(000:MOUT <sub>EPLL</sub> , 001: DOUT <sub>MPLL</sub> , 010:FIN <sub>EPLL</sub> , 011:<br>IIS_V40_CDCLK, 10x: PCMCDCLK[1]) | 0x0         |

v.DataSheet4U.com

#### Clock divider control register (Modified)

| CLK_DIV0     | BIT     | DESCRIPTION                                                                                                  | RESET VALUE |

|--------------|---------|--------------------------------------------------------------------------------------------------------------|-------------|

|              | [24,20] | MFC clock divider ratio                                                                                      | 0x0         |

| MFC_RATIO    | [31:28] | $CLKMFC = CLKMFC_{IN} / (MFC_RATIO + 1)$                                                                     | UXU         |

|              | 107.041 | JPEG clock divider ratio, which must be odd value. In other words, S3C6410 supports only even divider ratio. |             |

| JPEG_RATIO   | [27:24] | $CLKJPEG = HCLKX2 / (JPEG_RATIO + 1)$                                                                        | 0x1         |

|              |         | CAM clock divider ratio                                                                                      |             |

| CAM_RATIO    | [23:20] | CLKCAM = HCLKX2 / (CAM_RATIO + 1)                                                                            | 0x0         |

|              | [10:10] | Security clock divider ratio, which must be 0x1 or 0x3.                                                      | 0×1         |

| SECUR_RATIO  | [19:18] | CLKSECUR = HCLKX2 / (SECUR_RATIO + 1)                                                                        | 0x1         |

| PCLK_RATIO   | [15:12] | PCLK clock divider ratio, which must be odd value. In other words, S3C6410 supports only even divider ratio. | 0x1         |

| _            |         | PCLK = HCLKX2 / (PCLK_RATIO + 1)                                                                             |             |

| HCLKX2 RATIO | [11:0]  | HCLKX2 clock divider ratio                                                                                   | 0x0         |

|              | [11:9]  | $HCLKX2 = HCLKX2_{IN} / (HCLKX2_RATIO + 1)$                                                                  | 0x0         |

| HCLK_RATIO   | [8]     | HCLK clock divider ratio                                                                                     | 0           |

| HOLK_KAHO    | [0]     | HCLK = HCLKX2 / (HCLK_RATIO + 1)                                                                             | 0           |

| RESERVED     | [7:5]   | RESERVED                                                                                                     | 0x0         |

|              | [4]     | DIV <sub>MPLL</sub> clock divider ratio                                                                      | 0           |

| MPLL_RATIO   | [4]     | $DOUT_{MPLL} = MOUT_{MPLL} / (MPLL_RATIO + 1)$                                                               | U           |

| ARM_RATIO    | [3:0]   | DIV <sub>ARM</sub> clock divider ratio                                                                       | 0x0         |

|              | [3.0]   | $ARMCLK = DOUT_{APLL} / (ARM_RATIO + 1)$                                                                     | UXU         |

| CLK_DIV1    | BIT     | DESCRIPTION                                                     | RESET VALUE |

|-------------|---------|-----------------------------------------------------------------|-------------|

| RESERVED    | [31:28] | RESERVED                                                        | 0x0         |

| FIMC_RATIO  | [27:24] | FIMC clock divider ratio<br>CLKFIMC = HCLKX2 / (FIMC_RATIO + 1) | 0x0         |

| UHOST_RATIO | [23:20] | USB host clock divider ratio                                    | 0x0         |

ELECTRONICS

SAMSUNG

#### Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

|              |         | $CLKUHOST = CLKUHOST_{IN} / (UHOST_RATIO + 1)$           |      |

|--------------|---------|----------------------------------------------------------|------|

|              | [10:10] | TV Scaler clock divider ratio                            | 0x0  |

| SCALER_RATIO | [19:16] | CLKSCALER = CLKSCALER <sub>IN</sub> / (SCALER_RATIO + 1) | UXU  |

|              | [15:10] | LCD clock divider ratio                                  | 0x0  |

| LCD_RATIO    | [15:12] | $CLKLCD = CLKLCD_{IN} / (LCD_RATIO + 1)$                 | UXU  |

|              | [11.0]  | MMC2 clock divider ratio                                 | 0.40 |

| MMC2_RATIO   | [11:8]  | $CLKMMC2 = CLKMMC2_{IN} / (MMC2_RATIO + 1)$              | 0x0  |

| MMC1_RATIO   | [7, 4]  | MMC1 clock divider ratio                                 | 0x0  |

|              | [7:4]   | $CLKMMC1 = CLKMMC1_{IN} / (MMC1_RATIO + 1)$              | UXU  |

| MMC0 RATIO   | [2:0]   | MMC0 clock divider ratio                                 | 0x0  |

|              | [3:0]   | $CLKMMC0 = CLKMMC0_{IN} / (MMC0_RATIO + 1)$              | UXU  |

| CLK_DIV2     | BIT     | DESCRIPTION                                                                                                  | RESET VALUE |

|--------------|---------|--------------------------------------------------------------------------------------------------------------|-------------|

| RESERVED     | [31:28] | RESERVED                                                                                                     | 0x0         |

| AUDIO2_RATIO | [27:24] | AUDIO2 clock divider ratio<br><i>CLKAUDIO2</i> = <i>CLKAUDIO2</i> <sub>IN</sub> / ( <i>AUDIO2_RATIO</i> + 1) | 0x0         |

| IRDA_RATIO   | [23:20] | IRDA clock divider ratio<br><i>CLKIRDA</i> = <i>CLKIRDA</i> <sub>IN</sub> / (IRDA_RATIO + 1)                 | 0x0         |

| UART_RATIO   | [19:16] | UART clock divider ratio<br>$CLKUART = CLKUART_{IN} / (UART_RATIO + 1)$                                      | 0x0         |

| AUDIO1_RATIO | [15:12] | AUDIO1 clock divider ratio<br>$CLKAUDIO1 = CLKAUDIO1_{IN} / (AUDIO1_RATIO + 1)$                              | 0x0         |

| AUDIO0_RATIO | [11:8]  | AUDIO0 clock divider ratio<br><i>CLKAUDIO0</i> = <i>CLKAUDIO0</i> <sub>IN</sub> / ( <i>AUDIO0_RATIO</i> + 1) | 0x0         |

| SPI1_RATIO   | [7:4]   | SPI1 clock divider ratio<br><i>CLKSPI1</i> = <i>CLKSPI1<sub>IN</sub> / (SPI1_RATIO</i> + 1)                  | 0x0         |

| SPI0_RATIO   | [3:0]   | SPI0 clock divider ratio<br>CLKSPI0 = CLKSPI0 <sub>IN</sub> / (SPI0_RATIO + 1)                               | 0x0         |

### PLL Control Registers (Added Field & Added SFRs)

| HCLK_GATE  | BIT  | DESCRIPTION                                            | RESET VALUE |

|------------|------|--------------------------------------------------------|-------------|

| HCLK_3DSE  | [31] | Gating HCLK for 3D (0: mask, 1: pass)                  | 1           |

| RESERVED   | [30] | RESERVED                                               | 1           |

| HCLK_UHOST | [29] | Gating HCLK for UHOST (0: mask, 1: pass)               | 1           |

| HCLK_SECUR | [28] | Gating HCLK for security sub-system (0: mask, 1: pass) | 1           |

| HCLK_SDMA1 | [27] | Gating HCLK for SDMA1 (0: mask, 1: pass)               | 1           |

| HCLK_SDMA0 | [26] | Gating HCLK for SDMA0 (0: mask, 1: pass)               | 1           |

10

ELECTRONICS

SAMSUNG

| _           |      |                                                                      |   |

|-------------|------|----------------------------------------------------------------------|---|

| HCLK_IROM   | [25] | Gating HCLK for IROM (0: mask, 1: pass)                              | 1 |

| HCLK_DDR1   | [24] | Gating HCLK for DDR1 (0: mask, 1: pass)                              | 1 |

| HCLK_DDR0   | [23] | Gating HCLK for DDR0 (0: mask, 1: pass)                              | 1 |

| HCLK_MEM1   | [22] | Gating HCLK for DMC1 (0: mask, 1: pass)                              | 1 |

| HCLK_MEM0   | [21] | Gating HCLK for DMC0, SROM, OneNAND, NFCON, CFCON (0: mask, 1: pass) | 1 |

| HCLK_USB    | [20] | Gating HCLK for USB OTG (0: mask, 1: pass)                           | 1 |

| HCLK_HSMMC2 | [19] | Gating HCLK for HSMMC2 (0: mask, 1: pass)                            | 1 |

| HCLK_HSMMC1 | [18] | Gating HCLK for HSMMC1 (0: mask, 1: pass)                            | 1 |

| HCLK_HSMMC0 | [17] | Gating HCLK for HSMMC0 (0: mask, 1: pass)                            | 1 |

| HCLK_MDP    | [16] | Gating HCLK for MDP (0: mask, 1: pass)                               | 1 |

| HCLK_DHOST  | [15] | Gating HCLK for direct HOST interface (0: mask, 1: pass)             | 1 |

| HCLK_IHOST  | [14] | Gating HCLK for indirect HOST interface (0: mask, 1: pass)           | 1 |

| HCLK_DMA1   | [13] | Gating HCLK for DMA1 (0: mask, 1: pass)                              | 1 |

| HCLK_DMA0   | [12] | Gating HCLK for DMA0 (0: mask, 1: pass)                              | 1 |

| HCLK_JPEG   | [11] | Gating HCLK for JPEG (0: mask, 1: pass)                              | 1 |

| HCLK_CAMIF  | [10] | Gating HCLK for camera interface (0: mask, 1: pass)                  | 1 |

| HCLK_SCALER | [9]  | Gating HCLK for scaler (0: mask, 1: pass)                            | 1 |

| HCLK_2D     | [8]  | Gating HCLK for 2D (0: mask, 1: pass)                                | 1 |

| HCLK_TV     | [7]  | Gating HCLK for TV encoder (0: mask, 1: pass)                        | 1 |

| RESERVED    | [6]  | RESERVED                                                             | 1 |

| HCLK_POST0  | [5]  | Gating HCLK for POST0 (0: mask, 1: pass)                             | 1 |

| HCLK_ROT    | [4]  | Gating HCLK for rotator (0: mask, 1: pass)                           | 1 |

| HCLK_LCD    | [3]  | Gating HCLK for LCD controller (0: mask, 1: pass)                    | 1 |

| HCLK_TZIC   | [2]  | Gating HCLK for trust interrupt controller (0: mask, 1: pass)        | 1 |

| HCLK_INTC   | [1]  | Gating HCLK for vectored interrupt controller (0: mask, 1: pass)     | 1 |

| HCLK_MFC    | [0]  | Gating HCLK for MFC (0: mask, 1: pass)                               | 1 |

| PCLK_GATE   | BIT     | DESCRIPTION                                     | RESET VALUE |

|-------------|---------|-------------------------------------------------|-------------|

| RESERVED    | [31:28] | RESERVED                                        | 0x1F        |

| PCLK_IIC1   | [27]    | Gating PCLK for IIC1 (0: mask, 1: pass)         | 1           |

| PCLK_IIS2   | [26]    | Gating PCLK for IIS2 (0: mask, 1: pass)         | 1           |

| RESERVED    | [25]    | RESERVED                                        | 1           |

| PCLK_SKEY   | [24]    | Gating PCLK for security key (0: mask, 1: pass) | 1           |

| PCLK_CHIPID | [23]    | Gating PCLK for chip ID (0: mask, 1: pass)      | 1           |

| PCLK_SPI1   | [22]    | Gating PCLK for SPI1 (0: mask, 1: pass)         | 1           |

SAMSUNG ELECTRONICS

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

| PCLK_SPI0   | [21] | Gating PCLK for SPI0 (0: mask, 1: pass)             | 1 |

|-------------|------|-----------------------------------------------------|---|

| PCLK_HSIRX  | [20] | Gating PCLK for HSI receiver (0: mask, 1: pass)     | 1 |

| PCLK_HSITX  | [19] | Gating PCLK for HSI transmitter (0: mask, 1: pass)  | 1 |

| PCLK_GPIO   | [18] | Gating PCLK for GPIO (0: mask, 1: pass)             | 1 |

| PCLK_IIC0   | [17] | Gating PCLK for IIC0 (0: mask, 1: pass)             | 1 |

| PCLK_IIS1   | [16] | Gating PCLK for IIS1 (0: mask, 1: pass)             | 1 |

| PCLK_IIS0   | [15] | Gating PCLK for IIS0 (0: mask, 1: pass)             | 1 |

| SPCLK_AC97  | [14] | Gating PCLK for AC97 (0: mask, 1: pass)             | 1 |

| PCLK_TZPC   | [13] | Gating PCLK for TZPC (0: mask, 1: pass)             | 1 |

| PCLK_TSADC  | [12] | Gating PCLK for touch screen ADC (0: mask, 1: pass) | 1 |

| PCLK_KEYPAD | [11] | Gating PCLK for Key PAD (0: mask, 1: pass)          | 1 |

| PCLK_IRDA   | [10] | Gating PCLK for IRDA (0: mask, 1: pass)             | 1 |

| PCLK_PCM1   | [9]  | Gating PCLK for PCM1 (0: mask, 1: pass)             | 1 |

| PCLK_PCM0   | [8]  | Gating PCLK for PCM0 (0: mask, 1: pass)             | 1 |

| PCLK_PWM    | [7]  | Gating PCLK for PWM (0: mask, 1: pass)              | 1 |

| PCLK_RTC    | [6]  | Gating PCLK for RTC (0: mask, 1: pass)              | 1 |

| PCLK_WDT    | [5]  | Gating PCLK for watch dog timer (0: mask, 1: pass)  | 1 |

| PCLK_UART3  | [4]  | Gating PCLK for UART3 (0: mask, 1: pass)            | 1 |

| PCLK_UART2  | [3]  | Gating PCLK for UART2 (0: mask, 1: pass)            | 1 |

| PCLK_UART1  | [2]  | Gating PCLK for UART1 (0: mask, 1: pass)            | 1 |

| PCLK_UART0  | [1]  | Gating PCLK for UART0 (0: mask, 1: pass)            | 1 |

| PCLK_MFC    | [0]  | Gating PCLK for MFC (0: mask, 1: pass)              | 1 |

| SCLK_GATE    | BIT  | DESCRIPTION                                          | RESET VALUE |

|--------------|------|------------------------------------------------------|-------------|

| RESERVED     | [31] | RESERVED                                             | 1           |

| SCLK_UHOST   | [30] | Gating special clock for USB-HOST (0: mask, 1: pass) | 1           |

| SCLK_MMC2_48 | [29] | Gating special clock for MMC2 (0: mask, 1: pass)     | 1           |

| SCLK_MMC1_48 | [28] | Gating special clock for MMC1 (0: mask, 1: pass)     | 1           |

| SCLK_MMC0_48 | [27] | Gating special clock for MMC0 (0: mask, 1: pass)     | 1           |

| SCLK_MMC2    | [26] | Gating special clock for MMC2 (0: mask, 1: pass)     | 1           |

| SCLK_MMC1    | [25] | Gating special clock for MMC1 (0: mask, 1: pass)     | 1           |

| SCLK_MMC0    | [24] | Gating special clock for MMC0 (0: mask, 1: pass)     | 1           |

| SCLK_SPI1_48 | [23] | Gating special clock for SPI (0: mask, 1: pass)      | 1           |

| SCLK_SPI0_48 | [22] | Gating special clock for SPI (0: mask, 1: pass)      | 1           |

| SCLK_SPI1    | [21] | Gating special clock for SPI (0: mask, 1: pass)      | 1           |

| SCLK_SPI0    | [20] | Gating special clock for SPI (0: mask, 1: pass)      | 1           |

| SCLK_DAC27   | [19] | Gating special clock for DAC (0: mask, 1: pass)      | 1           |

12

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

SAMSUNG

ELECTRONICS

| SCLK_TV27     | [18] | Gating special clock for TV encoder (0: mask, 1: pass)             | 1 |

|---------------|------|--------------------------------------------------------------------|---|

| SCLK_SCALER27 | [17] | Gating special clock for scaler27 (0: mask, 1: pass)               | 1 |

| SCLK_SCALER   | [16] | Gating special clock for scaler (0: mask, 1: pass)                 | 1 |

| SCLK_LCD27    | [15] | Gating special clock for LCD controller (0: mask, 1: pass)         | 1 |

| SCLK_LCD      | [14] | Gating special clock for LCD controller (0: mask, 1: pass)         | 1 |

| SCLK_FIMC     | [13] | Gating special clock for camera & LCD (0: mask, 1: pass)           | 1 |

| SCLK_POST0_27 | [12] | Gating special clock for POST0 (0: mask, 1: pass)                  | 1 |

| SCLK_AUDIO2   | [11] | Gating special clock for PCM2, IIS2, AC97 2(0: mask, 1: pass)      | 1 |

| SCLK_POST0    | [10] | Gating special clock for POST0 (0: mask, 1: pass)                  | 1 |

| SCLK_AUDIO1   | [9]  | Gating special clock for PCM1, IIS1, AC97 1(0: mask, 1: pass)      | 1 |

| SCLK_AUDIO0   | [8]  | Gating special clock for PCM0, IIS0, and AC97 0 (0: mask, 1: pass) | 1 |

| SCLK_SECUR    | [7]  | Gating special clock for security block (0: mask, 1: pass)         | 1 |

| SCLK_IRDA     | [6]  | Gating special clock for IRDA (0: mask, 1: pass)                   | 1 |

| SCLK_UART     | [5]  | Gating special clock for UART0~3 (0: mask, 1: pass)                | 1 |

| SCLK_MFC      | [3]  | Gating special clock for MFC (0: mask, 1: pass)                    | 1 |

| SCLK_CAM      | [2]  | Gating special clock for camera interface (0: mask, 1: pass)       | 1 |

| SCLK_JPEG     | [1]  | Gating special clock for JPEG (0: mask, 1: pass)                   | 1 |

| RESERVED      | [0]  | RESERVED                                                           | 1 |

| MEM0_CLK_GA<br>TE | BIT    | DESCRIPTION                                          | RESET VALUE |

|-------------------|--------|------------------------------------------------------|-------------|

| RESERVED          | [31:6] | RESERVED                                             | 0x3ff_ffff  |

| HCLK_CFCON        | [5]    | Gating special clock for CFCON (0: mask, 1: pass)    | 1           |

| HCLK_OneNAND1     | [4]    | Gating special clock for OneNAND1 (0: mask, 1: pass) | 1           |

| HCLK_OneNAND0     | [3]    | Gating special clock for OneNAND0 (0: mask, 1: pass) | 1           |

| HCLK_NFCON        | [2]    | Gating special clock for NFCON (0: mask, 1: pass)    | 1           |

| HCLK_SROM         | [1]    | Gating special clock for SROM (0: mask, 1: pass)     | 1           |

| HCLK_DMC0         | [0]    | Gating special clock for DMC0 (0: mask, 1: pass)     | 1           |

| SW_RST   | BIT     | DESCRIPTION                                      | RESET VALUE |

|----------|---------|--------------------------------------------------|-------------|

| RESERVED | [31:18] | RESERVED                                         | 0x0         |

| RESERVED | [17]    | RESERVED                                         | 0x0         |

| RESERVED | [16]    | RESERVED                                         | 0x0         |

| SWRESET  | [15:0]  | Generate software reset when the value is 0x6410 | 0x0000      |

### Software reset control register (Added Field)

## System Others register (Added SFRs)

| SYS_OTHERS             | BIT    | DESCRIPTION                                     | RESET VALUE |

|------------------------|--------|-------------------------------------------------|-------------|

| RESERVED               | [31:4] | RESERVED                                        | 0           |

| MODEM_RX1_SDM<br>A_SEL | [3]    | DMA selection for MODEM RX1 (0: SDMA0, 1: DMA0) | 0           |

| MODEM_RX0_SDM<br>A_SEL | [2]    | DMA selection for MODEM RX0 (0: SDMA0, 1: DMA0) | 0           |

| MODEM_TX1_SDM<br>A_SEL | [1]    | DMA selection for MODEM TX1 (0: SDMA0, 1: DMA0) | 0           |

| MODEM_TX0_SDM<br>A_SEL | [0]    | DMA selection for MODEM TX0 (0: SDMA0, 1: DMA0) | 0           |

#### Memory Controller Status register (Added Fields)

| MEM_SYS_<br>CFG                                                  | BI      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               | RESET VALUE |

|------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| RESERVED                                                         | [31:15] | RESERVED                                                                                                                                                                                                                                                                                                                                                                                  | 0x0000_0    |

| INDEP_CF                                                         | [14]    | Use CF interface independently.<br>0 = Use memory port 0 shared by EBI.<br>1 = Use independent CF interface.                                                                                                                                                                                                                                                                              | 0           |

| nCFG_ADDR_EX<br>PAND<br>(nCFG_SROM_A<br>DDR_EXPAND_T<br>o_DRAM0) | [13]    | Set whether DRAM control pins are used for SROMC address<br>field or not.<br>Note: Active low.<br>0 = Xm0RAS, CAS, AP, WE pins are used for SROMC<br>address [19:16].<br>1 = Xm0RAS, CAS, AP, WE pins are used for DRAM0.                                                                                                                                                                 | 0           |

| BUS_WIDTH                                                        | [12]    | Select initial state of SROMC CS0 memory bus width.<br>0 = 8-bit data width.<br>1 = 16-bit data width.<br>If NOR booting (OM[4:1] = 0101) is selected, this setting is<br>ignored and 16-bit data width is selected.<br>Even this bit is set to 0 or 1, this selects only reset value of<br>DataWidth0 of SROM_BW SFR in SROMC. Bus width of CS0<br>for SROMC follows DataWidth0 setting. | 0           |

| EBI_PRI                                                          | [11]    | Set EBI priority scheme.                                                                                                                                                                                                                                                                                                                                                                  | 0           |

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

www.DataSheet4U.com

|     |                              |        | 0 = Fixed priority scheme.                                                                                                                                                                                                                                        |      |  |  |  |

|-----|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

|     |                              |        | 1 = Circular priority scheme.                                                                                                                                                                                                                                     |      |  |  |  |

|     |                              |        | Set EBI fixed priority setting.                                                                                                                                                                                                                                   |      |  |  |  |

|     |                              |        | Highest <-> Lowest                                                                                                                                                                                                                                                |      |  |  |  |

|     |                              |        | 0,6,7 DMC0 - SROMC - OneNANDC CS0 - OneNANDC CS1 - NFCON - CFCON                                                                                                                                                                                                  |      |  |  |  |

|     |                              |        | 1 DMC0 – OneNANDC CS0 – OneNANDC CS1 – SROMC –<br>NFCON – CFCON                                                                                                                                                                                                   |      |  |  |  |

| nee | t4U.com<br>EBI_FIX_PRI       | [10:8] | 2 DMC0 - OneNANDC CS1 – NFCON – SROMC -<br>OneNANDC CS0 – CFCON                                                                                                                                                                                                   | 000  |  |  |  |

|     |                              |        | 3 DMC0 – NFCON – SROMC - OneNANDC CS0 -<br>OneNANDC CS1 – CFCON                                                                                                                                                                                                   |      |  |  |  |

|     |                              |        | 4 DMC0 – CFCON – SROMC - OneNANDC CS0 -<br>OneNANDC CS1 – NFCON                                                                                                                                                                                                   |      |  |  |  |

|     |                              |        | 5 SROMC - DMC0 - OneNANDC CS0 - OneNANDC CS1 -<br>NFCON - CFCON                                                                                                                                                                                                   |      |  |  |  |

|     | ADDR EXPAND                  |        | Set usage of Xm1DATA[31:16] pins.                                                                                                                                                                                                                                 |      |  |  |  |

|     | (CFG_SROM_AD<br>DR_EXPAND_To | [7]    | 0 = Xm1DATA[31:16] pins are used for DMC1 upper halfword data field, data[31:16].                                                                                                                                                                                 | 1    |  |  |  |

|     | _DRAM1                       |        | 1 = Xm1DATA[31:16] pins are used for SROMC upper 10-bit address field, address[25:16].                                                                                                                                                                            |      |  |  |  |

|     | ENDIAN                       | [6]    | Set endian control for SROMC, NFCON, and internal ROM.<br>0 = Little-endian memory system.<br>1 = Big-endian byte-invariant memory system.                                                                                                                        | 0    |  |  |  |

|     |                              |        | Set static memory chip selection multiplexing of memory port<br>0.                                                                                                                                                                                                |      |  |  |  |

|     |                              |        | Setting for MP0_CS_SEL[0] and MP0_CS_SEL[2] are<br>ignored. Distinguishing OneNANDC and NFCON is done by<br>XSELNAND pin value instead of MP0_CS_SEL[0] and<br>MP0_CS_SEL[2]. When XSELNAND is 0, OneNANDC is<br>selected. When XSELNAND is 1, NFCON is selected. |      |  |  |  |

|     | MP0_CS_SEL                   | [5:0]  | When NAND booting (OM[4:3] = 00) is selected, the setting values of MP0_CS_SEL[1] and MP0_CS_SEL[3] as well as XSELNAND setting are ignored and Xm0CSn[2] and Xm0CSn[3] are used as NFCON CS0 and NFCON CS1. In this case, XSELNAND should be set to 1.           | 0x00 |  |  |  |

|     |                              |        | When OneNAND booting (OM[4:1] = 0110) is selected, the setting values of MP0_CS_SEL[1] and MP0_CS_SEL[3] are ignored and Xm0CSn[2] and Xm0CSn[3] are used as OneNANDC CS0 and OneNANDC CS1. In this case, XSELNAND should be set to 0.                            |      |  |  |  |

|     |                              |        | MP0_CS_SEL                                                                                                                                                                                                                                                        |      |  |  |  |

|     |                              |        | [5]         [4]         [3]         [2]         [1]         [0]           Xm0CSn[0]         -         -         -         -         SROMC CS0                                                                                                                     |      |  |  |  |

|     |                              |        |                                                                                                                                                                                                                                                                   |      |  |  |  |

## SAMSUNG ELECTRONICS

Preliminary product information describe products that are in development, for which full characterization data and associated errata are not yet available. Specifications and information herein are subject to change without notice.

|                 |  | Xm0CSn[1]  | - | - | - | - | - | - | SROMC CS1    |

|-----------------|--|------------|---|---|---|---|---|---|--------------|

|                 |  |            | - | - | - | - | 1 | - | SROMC CS2    |

|                 |  | Xm0CSn[2]  | I | I | - | I | 0 | - | OneNANDC CS0 |

|                 |  |            | - | - | - | - | 0 | - | NFCON CS0    |

|                 |  |            | 1 | I | 1 | I | - | - | SROMC CS3    |

|                 |  | Xm0CSn[3]  | 1 | I | 0 | I | - | - | OneNANDC CS1 |

|                 |  |            | 1 | I | 0 | I | - | - | NFCON CS1    |

| DataSheet4U.com |  | Xm0CSn[4]  | 1 | 0 | - | I | - | - | SROMC CS4    |

|                 |  |            | 1 | 1 | - | I | - | - | CFCON CS0    |

|                 |  | V==000=[5] | 0 | - | - | - | - | - | SROMC CS5    |

|                 |  | Xm0CSn[5]  | 1 | - | - | - | - | - | CFCON CS1    |

#### NORMAL Configuration Register (Added Fields)

| NORMAL_CFG | BI      | DESCRIPTION                         | RESET VALUE |

|------------|---------|-------------------------------------|-------------|

| RESERVED   | [31]    | DO NOT CHANGE                       | 1           |

| IROM       | [30]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| RESERVED   | [29:17] | DO NOT CHANGE                       | 0x1FFF      |

| DOMAIN_ETM | [16]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| DOMAIN_S   | [15]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| DOMAIN_F   | [14]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| DOMAIN_P   | [13]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| DOMAIN_I   | [12]    | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| RESERVED   | [11]    | RESERVED                            | 0x1         |

| DOMAIN_G   | [10]    | 0: LP mode(OFF), 1: active mode(ON) | 0x1         |

| DOMAIN_V   | [9]     | 0: LP mode(OFF), 1: active mode(ON) | 1           |

| RESERVED   | [8:0]   | DO NOT CHANGE                       | 0x100       |

#### Others Register (Added Fields)

| OTHERS                  | BIT     | DESCRIPTION                                                                              | RESET VALUE |

|-------------------------|---------|------------------------------------------------------------------------------------------|-------------|

| RESERVED                | [31:24] | RESERVED                                                                                 | 0x0000      |

| STABLE COUNTER<br>SCALE | [23]    | Indicate OSC_STABLE, PWR_STABLE counter scale<br>0 : Exponential Scale, 1 : Linear Scale | 0           |

| RESERVED                | [22:17] | RESERVED                                                                                 | 0x0000      |

| USB_SIG_MASK            | [16]    | USB signal mask to prevent unwanted leakage.                                             | 0           |

16

ELECTRONICS

SAMSUNG

|                |        | (This bit must set before USB PHY is used.)                                                                                                                                                                                                                                                                                                                                                        |      |

|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| RESERVED       | [14]   | DO NOT CHANGE                                                                                                                                                                                                                                                                                                                                                                                      | 0    |

| CLEAR_DBGACK   | [13]   | Clear DBGACK signal when this field has 1. ARM1176<br>asserts DBGACK signal to indicate the system has<br>entered Debug state. If DBGACK is asserted, this state<br>is store in SYSCON until software clear it using this<br>field.                                                                                                                                                                | 0    |

| CLEAR_BATF_INT | [12]   | Clear interrupt caused by battery fault when this bit is set.                                                                                                                                                                                                                                                                                                                                      | 0    |

| RESERVED       | [11:8] | DO NOT CHANGE                                                                                                                                                                                                                                                                                                                                                                                      | 0x00 |

| SYNCMODE       | [7]    | SYNCMODEREQ to ARM<br>0: Asynchronous mode, 1: Synchronous mode                                                                                                                                                                                                                                                                                                                                    | 0    |

| SYNCMUXSEL     | [6]    | SYS CLOCK SELECT IN CMU<br>0: Asynchronous mode, 1: Synchronous mode                                                                                                                                                                                                                                                                                                                               | 0    |

| RESEVED        | [5:3]  | DO NOT CHANGE                                                                                                                                                                                                                                                                                                                                                                                      | 0x3  |

| SPNIDEN        | [2]    | Secure privileged non-invasive debug enable. This field<br>enables and disables non-invasive debug in the secure<br>world of ARM1176. If it is '1', non-invasive debug is<br>permitted in all non-secure mode. Otherwise, non-<br>invasive debug is not permitted in all secure privileged<br>mode. Non-invasive debug is permitted in Secure use<br>mode according to the SUNIDEN bit of ARM1176. | 1    |

| SPIDEN         | [1]    | Secure privileged invasive debug enable. This field<br>enables and disables invasive debug in the secure<br>world of ARM1176. If it is '1', invasive debug is<br>permitted in all secure mode. Otherwise, invasive<br>debus is not permitted in any secure privileged mode.<br>Invasive debug is permitted in Secure use mode<br>according to the SUNIDEN bit of ARM1176.                          | 1    |

| CP15DISABLE    | [0]    | Disables write asses to some system control processor registers of ARM1176. (0: enable, 1: disable)                                                                                                                                                                                                                                                                                                | 0    |

#### Reset Status register (Added Fields)

| RST_STAT             | BIT    | DESCRIPTION                                                                                     | RESET VALUE |

|----------------------|--------|-------------------------------------------------------------------------------------------------|-------------|

| RESERVED             | [31:7] | RESERVED                                                                                        | 0x0000_000  |

| DEEP_STOP_WAKEU<br>P | [6]    | Reset by DEEP_STOP mode wake-up                                                                 | 0           |

| SW_RESET             | [5]    | Software reset by SWRESET                                                                       | 0           |

| RESERVED             | [4]    | RESERVED                                                                                        | 0           |

| SLEEP_WAKEUP         | [3]    | Reset by SLEEP mode wake-up                                                                     | 0           |

| WDT_RESET            | [2]    | Watch dog timer reset by WDTRST                                                                 | 0           |

| WARM_RESET           | [1]    | Warm reset by XnWRESET. This field is not set when the wakeup source of SLEEP mode is XnWRESET. | 0           |

SAMSUNG

ELECTRONICS

| HW_RESET   [0]   External reset by XnRESET   1 | IIW RESET |

|------------------------------------------------|-----------|

|------------------------------------------------|-----------|

ww.DataSheet4U.com

# **4.MEMORY SUBSYSTEM**

## 4.1 Behavior for accessing reserved address regions

## 4.1.1 S3C6400

Accesses to reserve address region returns OKAY response.

## 4.1.2 S3C6410

Accesses to reserve address region returns ERROR response.

(IP Based reserved region,)

## 4.2 Clock domain for OneNAND controller

## 4.2.1 S3C6400

OneNAND controller has a separate clock domain other than AHB clock domain.

## 4.2.2 S3C6410

OneNAND controller shares AHB clock domain with other memory controllers.

2

# **5. DRAM CONTROLLER**

## 5.1 Difference summary

## 5.1.1 New programmable options

#### v.DataSheet4U.com

DPD support

Variable number of auto-refresh requests before priority change.

## 5.1.2 New functionality

Improved pipeline stages

Improved write termination

Auto self refresh entry

## 5.2 Register comparison

## 5.2.1 DRAM Controller Status Register (MODIFIED)

| Register  | Address    | R/W | Description                            | Reset Value |

|-----------|------------|-----|----------------------------------------|-------------|

| POMEMSTAT | 0x9E000000 | R   | 16-bit DRAM controller status register | 0xAB0       |

| P1MEMSTAT | 0x9E001000 | R   | 32-bit DRAM controller status register | 0xAB4       |

#### S3C6400

| PnMEMSTAT             | Bit     | Description                                                                             | Initial State |

|-----------------------|---------|-----------------------------------------------------------------------------------------|---------------|

| Reserved              | [31:14] | Read undefined.                                                                         |               |

| Memory banks          | [13:12] | The maximum number of banks that DRAM controller supports on each chip.<br>00 = 4 banks | 00            |

| Exclusive<br>monitors | [11:10] | 10]The number of exclusive access monitor resources<br>10 = 2 monitors                  |               |

| Reserved              | [9]     | Read always zero.                                                                       | 0             |

| Memory chips              | [8:7] | The maximum number of different chip selects that DRAM<br>controller can supports:<br>11 = 4 chips<br>However, S3C6400X uses only two chip select signals per DRAM<br>controller. | 11      |

|---------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Memory type               | [6:4] | The type of SDRAM that DRAM controller supports:<br>100 = Support SDR SDRAM (normal or mobile) and DDR SDRAM<br>(normal or mobile)                                                | 100     |

| eet4U.com<br>Memory width | [3:2] | The width of the external memory $00 = 16$ -bit $01 = 32$ -bit $10 = 64$ -bit $11 =$ reserved                                                                                     | 00 / 01 |

| Controller status         | [1:0] | The status of the DRAM controller00 = Config.01 = Ready10 = Paused11 = Low-Power                                                                                                  | 00      |

#### S3C6410

| PnMEMSTAT             | Bit     | Description                                                                                                                                                                                                                                                                  | Initial State |

|-----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Reserved              | [31:14] | Read undefined.                                                                                                                                                                                                                                                              |               |

| Memory banks          | [13:12] | The maximum number of banks that DRAM controller supports on each chip.<br>00 = 4 banks                                                                                                                                                                                      | 00            |

| Exclusive<br>monitors | [11:10] | The number of exclusive access monitor resources<br>10 = 2 monitors                                                                                                                                                                                                          | 10            |

| Reserved              | [9]     | Read always zero.                                                                                                                                                                                                                                                            | 0             |

| Memory chips          | [8:7]   | The maximum number of different chip selects that DRAM controller can supports:<br>00 = 1chip, 01 = 2 chips, 10 = 3 chips, 11 = 4 chips                                                                                                                                      | 11            |

| Memory type           | [6:4]   | The type of SDRAM that DRAM controller supports:<br>000 = SDR SDRAM, 001 = DDR SDRAM<br>011 = Mobile DDR SDRAM, 010 = eDRAM<br>1xx = Reserved.<br>If Mobile DDR SDRAM or SDR SDRAM or an eDRAM is<br>supported, the cas_half_cycle bit at address offset 0x14 is<br>ignored. | 000/001       |

| Memory width          | [3:2]   | The width of the external memory00 = 16-bit01 = 32-bit10 = 64-bit11 = reserved                                                                                                                                                                                               | 00 / 01       |

| Controller status     | [1:0]   | The status of the DRAM controller00 = Config.01 = Ready10 = Paused11 = Low-Power                                                                                                                                                                                             | 00            |

## 5.2.2 Direct Command Register

| Register     | Address    | R/W | Description                                    | Reset Value |

|--------------|------------|-----|------------------------------------------------|-------------|

| P0DIRECTCMD  | 0x9E000008 | W   | 16-bit DRAM controller direct command register |             |

| P1 DIRECTCMD | 0x9E001008 | W   | 32-bit DRAM controller direct command register |             |

#### r0p0\_AP

| PnDIRECTCMD         | Bit     | Description                                                                            | Initial State |

|---------------------|---------|----------------------------------------------------------------------------------------|---------------|

| Reserved            | [31:22] | Undefined. Write as Zero                                                               |               |

| Chip number         | [21:20] | Bits mapped to external memory chip address bits.                                      |               |

|                     |         | Determine the command required                                                         |               |

|                     |         | 00 = Prechargeall                                                                      |               |

| Memory<br>command   | [19:18] | 01 = Autorefresh                                                                       |               |

| command             |         | 10 = MRS or EMRS                                                                       |               |

|                     |         | 11 = NOP.                                                                              |               |

| Bank address        | [17:16] | Bits mapped to external memory bank address bits when command is MRS or EMRS access.   |               |

| Reserved            | [15:14] | Undefined. Write as Zero                                                               |               |

| Address_13_to_<br>0 | [13:0]  | Bits mapped to external memory address bits [13:0] when command is MRS or EMRS access. |               |

#### S3C6410

| PnDIRECTCMD                   | Bit     | Description                                                                                                                           | Initial State |

|-------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Reserved                      | [31:23] | Undefined. Write as Zero                                                                                                              |               |

| Extended<br>Memory<br>command | [22]    | Extended memory command, see note after the table<br>If this bit is set and Memory command is Prechargeall, direct<br>command is DPD. |               |

| Chip number                   | [21:20] | Bits mapped to external memory chip address bits.                                                                                     |               |

| Memory<br>command             | [19:18] | Determine the command required<br>00 = Prechargeall<br>01 = Autorefresh<br>10 = MRS or EMRS<br>11 = NOP.                              |               |

| Bank address                  | [17:16] | Bits mapped to external memory bank address bits when command is MRS or EMRS access.                                                  |               |

| Reserved            | [15:14] | Undefined. Write as Zero                                                               |  |

|---------------------|---------|----------------------------------------------------------------------------------------|--|

| Address_13_to_<br>0 | [13:0]  | Bits mapped to external memory address bits [13:0] when command is MRS or EMRS access. |  |

## 5.2.3 Memory Configuration 2 Register (MODIFIED)

| DataShe | et4U.co <b>Register</b> | Address    | R/W | Description                                   | Reset Value |

|---------|-------------------------|------------|-----|-----------------------------------------------|-------------|

|         | P0MEMCFG2               | 0x9E00004C | R/W | 16-bit DRAM controller configuration register | 0x0B00      |

|         | P1MEMCFG2 0x9E00104C    |            | R/W | 32-bit DRAM controller configuration register | 0x0B40      |

#### r0p0\_AP

| PnMEMCFG2    | Bit     | Description                                                                                           | Initial State |  |

|--------------|---------|-------------------------------------------------------------------------------------------------------|---------------|--|

| Reserved     | [31:13] | Read undefined. Write as Zero.                                                                        |               |  |

|              |         | Encodes the delay used when reading from the pad interface to allow for de-skew of incoming read data |               |  |

| Road dolov   | [10:11] | 00 = Read delay 0 cycle (usually for SDR SDRAM)                                                       | 01            |  |

| Read delay   | [12:11] | 01 = Read delay 1 cycle (usually for DDR SDRAM and mobile DDR SDRAM)                                  | UT            |  |

|              |         | 10, 11 = Read delay 2 cycle                                                                           |               |  |

|              |         | The type of SDRAM that is attached to DRAM controller:<br>000 = SDR SDRAM                             |               |  |

|              | [10:8]  | 001 = DDR SDRAM                                                                                       | 011           |  |

| Memory type  |         | 011 = mobile DDR SDRAM                                                                                |               |  |

|              |         | 010 = Embedded SDRAM                                                                                  |               |  |

|              |         | 1xx = reserved                                                                                        |               |  |

| Memory width | [7:6]   | The width of the external memory                                                                      | 00 / 01       |  |

|              | [7.0]   | 00 = 16-bit 01 = 32-bit 10 = 64-bit 11 = 128-bit                                                      | 00701         |  |

|              |         | Encodes the number of bit of the AXI address that comprise the bank address.                          |               |  |

| Develo hite  | [[.4]   | 00 = 2 bits                                                                                           | 00            |  |

| Bank bits    | [5:4]   | 01 = 1 bit                                                                                            | 00            |  |

|              |         | 10 = 0 bit                                                                                            |               |  |

|              |         | 11 = reserved                                                                                         |               |  |

| Reserved     | [3]     | Read as Zero. Write as Zero.                                                                          | 0             |  |

| DQM init     | [2]     | State of DQM when memory reset is de-asserted.                                                        | 1             |  |

| Clock config | [1:0] | The clock scheme supports:<br>00 = AXI clock and memory clock are asynchronous.<br>01 = AXI clock and memory clock are synchronous, and AXI clock<br>is the same frequency or slower than memory clock.<br>S3C6400X supports synchronous configuration. If this value is set<br>to asynchronous, S3C6400X should endure performance<br>degradation.<br>10~11 = reserved | 00 |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

vw.DataSheet4U.com

#### r2p0\_AP

| PnMEMCFG2    | Bit     | Description                                                                                                  | Initial State |

|--------------|---------|--------------------------------------------------------------------------------------------------------------|---------------|

| Reserved     | [31:13] | Read undefined. Write as Zero.                                                                               |               |

|              |         | Encodes the delay used when reading from the pad interface to allow for de-skew of incoming read data        |               |

| Dood dolow   | [10,14] | 00 = Read delay 0 cycle (usually for SDR SDRAM)                                                              | 01            |

| Read delay   | [12:11] | 01 = Read delay 1 cycle (usually for DDR SDRAM and mobile DDR SDRAM)                                         | UT            |

|              |         | 10, 11 = Read delay 2 cycle                                                                                  |               |

|              |         | The type of SDRAM that is attached to DRAM controller:<br>000 = SDR SDRAM                                    |               |

|              | [10:8]  | 001 = DDR SDRAM                                                                                              | 011           |

| Memory type  |         | 011 = mobile DDR SDRAM                                                                                       |               |

|              |         | 010 = Embedded SDRAM                                                                                         |               |

|              |         | 1xx = reserved                                                                                               |               |

| Manager      | [7.0]   | The width of the external memory                                                                             | 00/01         |

| Memory width | [7:6]   | 00 = 16-bit 01 = 32-bit 10 = 64-bit 11 = 128-bit                                                             | 00 / 01       |

| Reserved     | [5:4]   | Read undefined. Write as Zero. <sup>1</sup>                                                                  | 00            |

| Cke Init     | [3]     | Sets the level for the cke outputs after reset.                                                              | 0             |

| DQM init     | [2]     | State of DQM when memory reset is de-asserted.                                                               | 1             |

| A_gt_m_sync  | [1]     | Requires to be set HIGH when running the aclk and mclk synchronously but with aclk running faster than mclk. | 00            |

| sync         | [0]     | Set high when aclk and mclk are synchronous.                                                                 |               |

<sup>1</sup> bank\_bits is not programmable in S3C6410

## 5.2.4 Memory Configuration 3 Register (NEW)

| Register  | Address    | R/W | Description                                   | Reset Value |

|-----------|------------|-----|-----------------------------------------------|-------------|

| P0MEMCFG3 | 0x9E000050 | R/W | 16-bit DRAM controller configuration register | 0x0B00      |

| P1MEMCFG3 | 0x9E001050 | R/W | 32-bit DRAM controller configuration register | 0x0B40      |

#### r2p0\_AP

| PnMEMCFG3     | Bit     | Description                                                                      | Initial State |

|---------------|---------|----------------------------------------------------------------------------------|---------------|

| sr_enable     | [31]    | Auto self-entry enable. Only if configured else read is undefined write as zero. | 0             |

| Reserved      | [30:12] | Read undefined. Write as Zero.                                                   |               |

| Prescale      | [11:3]  | Prescalar counter value.                                                         |               |

| max_outs_refs | [2:0]   | Maximum number of outstanding refresh commands.                                  |               |

# **6. SROM CONTROLLER**

## 6.1 Difference summary

There in no change

ww.DataSheet4U.com

# 7. ONENAND CONTROLLER

## 7.1 Address regions

## 7.1.1 S3C6400

| v.DataShee | dev_id        | <b>D</b>        | # of   | Page | MAP      |              | ME          | M_ADDR  | Field |       |              |

|------------|---------------|-----------------|--------|------|----------|--------------|-------------|---------|-------|-------|--------------|

|            | size<br>field | Density         | Blocks | Size | location | Reserve<br>d | DFS_DB<br>S | FBA     | FPA   | FSA   | Reserve<br>d |

|            | 0000          | 128Mb           | 256    | 1KB  | [23:22]  | [21:17]      | N/A         | [16:9]  | [8:3] | [2]   | [1:0]        |

|            | 0001          | 256Mb           | 512    | 1KB  | [23:22]  | [21:18]      | N/A         | [17:9]  | [8:3] | [2]   | [1:0]        |

|            | 0010          | 512Mb           | 512    | 2KB  | [23:22]  | [21:19]      | N/A         | [18:10] | [9:4] | [3:2] | [1:0]        |

| ·          | 0011          | 1Gb<br>Dual Die | 1024   | 2KB  | [23:22]  | [21:20]      | [19]        | [18:10] | [9:4] | [3:2] | [1:0]        |

|            | 0011          | 1Gb             | 1024   | 2KB  | [23:22]  | [21]         | N/A         | [19:10] | [9:4] | [3:2] | [1:0]        |

| ·          | 0100          | 2Gb<br>Dual Die | 2048   | 2KB  | [23:22]  | [21]         | [20]        | [19:10] | [9:4] | [3:2] | [1:0]        |

|            | 0100          | 2Gb             | 2048   | 2KB  | [23:22]  | N/A          | N/A         | [20:10] | [9:4] | [3:2] | [1:0]        |

| ·          | 0101          | 4Gb<br>Dual Die | 4096   | 2KB  | [23:22]  | N/A          | [21]        | [20:10] | [9:4] | [3:2] | [1:0]        |

|            | 0101          | 4Gb             | 4096   | 2KB  | [23:22]  | N/A          | N/A         | [21:10] | [9:4] | [3:2] | [1:0]        |

## 7.1.2 S3C6410