# S6BP201A

ASSP 42V, 1A, Synchronous Buck-boost DC/DC Converter IC Data Sheet (Preliminary)

**Notice to Readers:** This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

### Notice On Data Sheet Designations

Cypress Semiconductor Corp. issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Cypress data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Cypress Semiconductor Corp. is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Cypress Semiconductor Corp. therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Cypress Semiconductor Corp. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Cypress Semiconductor Corp. reserves the right to change or discontinue work on this proposed product without notice."

#### Preliminary

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Cypress places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### **Full Production (No Designation on Document)**

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or VIO range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Cypress Semiconductor Corp. applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Cypress product(s) described herein. Cypress Semiconductor Corp. deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local sales office.

# S6BP201A

## ASSP 42V, 1A, Synchronous Buck-boost DC/DC Converter IC

Data Sheet (Preliminary)

### 1. Description

S6BP201A is a 1ch Buck-boost DC/DC converter IC with four built-in switching FETs. This IC is able to supply up to 1.0A of load current within the very wide range from 2.5V to 42V in the input voltage. This IC has an operation mode that is automatically changed to PFM operation during low load, which can achieve super-high efficiency with a very low quiescent current 20  $\mu$ A. It is possible to provide stable output voltage from an automotive cold cranking and load dump, up to 42V, conditions within 1 ms transition time. As a result, this IC is suitable for power supply solutions of automotive and Industrial applications.

This IC has the SYNC function, which is capable of selecting the SYNC\_IN that is able to inputs an external clock signal. When an external clock signal in the range from 200 kHz to 400 kHz is inputted, the FETs perform the switching operation with synchronizing signal from an external clock. When an external clock signal is not inputted, the FETs perform the switching operation from an internal clock. The internal clock signal in the range from 200 kHz to 2.1 MHz can be set by an external resistor.

Since external voltage setting resistors and phase compensation capacitors are not required with this IC, it can reduce the number of parts and a part mounting area.

This IC has five protection functions, input under voltage lockout (input UVLO), output under voltage protection (output UVP), output over voltage protection (output OVP), output over current protection (output OCP), and thermal shutdown (TSD).

Moreover, this IC has the power good (PG) function that indicates the state of the output voltage(VOUT pin). When the output voltage reaches the PG voltage, the PG signal is outputted.

The VOUT output voltage of this product is selectable from the product lineup (refer to the "4. Product Lineup").

This document states the current technical specifications regarding the Cypress product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications.

#### Features 2.

- Wide input voltage range : 2.5V to 42V

- Selectable output voltage (factory settable): 5.000V/5.050V/5.075V/5.100V/5.125V/5.150V/5.200V

- Wide operating frequency range

- External synchronized clock range

- : 200 kHz to 2.1 MHz : 200 kHz to 400 kHz

- SYNC function - SYNC IN : External clock input (Not inputting an external clock, this IC operates by an internal clock)

- Super-high efficiency by PFM operation (When setting MODE pin to a low level)

- Automatic PWM/PFM switching operation and fixed PWM operation are selectable by MODE pin

: 20 µA

- Built-in switching FET

- Synchronous current mode architecture

- Shutdown current : Lower than 1 µA

- Quiescent current

- Power Good Monitor

- Output voltage monitoring by window comparator

- Power-on reset time : 14 ms

- Soft start time without load dependence : 0.9 ms (When switching frequency = 2.1 MHz)

- Enhanced protection functions

- Input under voltage lockout

- Output under voltage protection : 95.5% : 104.5%

- Output over voltage protection

- Output over current protection

- Thermal shutdown

- Small TSSOP16 package (exposed PAD) : 5 mm × 6.4 mm

#### **Applications** 3.

- Body Control Module (BCM)

- Gateway module

- Automotive applications

- Industrial applications

## **Table of Contents**

| 1.  | Description                                | 3  |

|-----|--------------------------------------------|----|

| 2.  | Features                                   | 4  |

| 3.  | Applications                               | 4  |

| 4.  | Product Lineup                             | 6  |

| 5.  | Pin Assignment                             | 7  |

| 6.  | Pin Descriptions                           | 7  |

| 7.  | Block Diagram                              | 8  |

| 8.  | Absolute Maximum Ratings                   | 9  |

| 9.  | Recommended Operating Conditions           | 10 |

| 10. | Electrical Characteristics                 | 11 |

| 11. | Functional Description                     | 13 |

|     | 11.1 Protection Function                   | 13 |

|     | 11.2 Protection Function Table             | 14 |

| 12. | Application Circuit Example and Parts list | 15 |

| 13. | Application Note                           | 16 |

|     | 13.1 Setting the Operation Conditions      | 16 |

| 14. | Usage Precaution                           | 19 |

| 15. | RoHS Compliance Information                | 19 |

| 16. | Ordering Information                       | 19 |

| 17. | Package Dimensions                         | 20 |

| 18. | Major Changes                              | 21 |

## Figures

| Figure 5-1 Pin Assignment                         | 7  |

|---------------------------------------------------|----|

| Figure 7-1 Block Diagram                          | 8  |

| Figure 12-1 Application Circuit Example           | 15 |

| Figure 13-1 Fosc vs RRT Measured Characteristic   | 17 |

| Figure 13-2 I <sub>VOUT</sub> vs V <sub>VIN</sub> | 18 |

| -                                                 |    |

## Tables

| Table 6-1 Pin Descriptions                    | 7    |

|-----------------------------------------------|------|

| Table 11-1 Protection Function Table          | . 14 |

| Table 12-1 Parts List                         | . 15 |

| Table 13-1 Operation State of DC/DC Convertor | . 16 |

## 4. Product Lineup

The VOUT output voltage of this product is set at the factory shipment. To order a product, select an item from the product lineup blow.

| Dert Number(#4)   | Order | VOUT                  | SYNC     |                  | • Threshold<br>%] |                 | Threshold<br>6]  | Power-on         |  |

|-------------------|-------|-----------------------|----------|------------------|-------------------|-----------------|------------------|------------------|--|

| Part Number(*1)   | Code  | Output<br>Voltage [V] | Function | Falling<br>(Typ) | Rising<br>(Typ)   | Rising<br>(Typ) | Falling<br>(Typ) | Reset<br>Time[s] |  |

| S6BP201A1AST2B000 | 1A    | 5.000                 |          | -                |                   |                 |                  |                  |  |

| S6BP201A2AST2B000 | 2A    | 5.050                 |          |                  |                   |                 |                  |                  |  |

| S6BP201A3AST2B000 | 3A    | 5.075                 |          |                  |                   |                 |                  |                  |  |

| S6BP201A4AST2B000 | 4A    | 5.100                 | SYNC_IN  | 95.5             | 96.5              | 104.5           | 103.5            | 14.0m            |  |

| S6BP201A5AST2B000 | 5A    | 5.125                 |          |                  |                   |                 |                  |                  |  |

| S6BP201A6AST2B000 | 6A    | 5.150                 |          |                  |                   |                 |                  |                  |  |

| S6BP201A7AST2B000 | 7A    | 5.200                 |          |                  |                   |                 |                  |                  |  |

\*1: Commercial sample (CS)

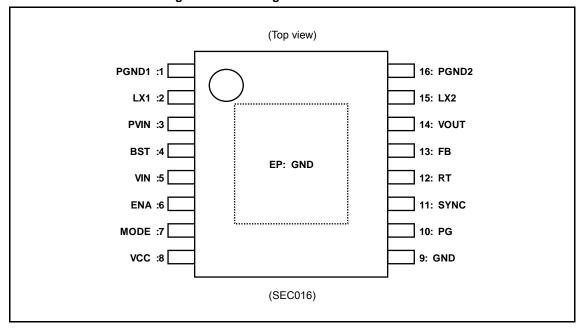

## 5. Pin Assignment

Figure 5-1 Pin Assignment

## 6. Pin Descriptions

#### **Table 6-1 Pin Descriptions**

| Pin No. | Pin Name | I/O | Description                                                                |                                                         |

|---------|----------|-----|----------------------------------------------------------------------------|---------------------------------------------------------|

| 1       | PGND1    | -   | GND pin for built-in switching FET                                         |                                                         |

| 2       | LX1      | 0   | Inductor connection pin                                                    |                                                         |

| 3       | PVIN     | I   | Power supply pin for PWM controller and switching FETs                     |                                                         |

| 4       | BST      | I   | BST(Boost) capacitor connection pin                                        |                                                         |

| 5       | VIN      | I   | Power supply pin                                                           |                                                         |

| 6       | ENA      | I   | DC/DC converter enable pin                                                 |                                                         |

| 7       | MODE     | 1   | PWM/PFM operation control pin                                              |                                                         |

| 7       | MODE     | I   | For the MODE pin setting, refer to "13.1 Setting the Operation Conditions" |                                                         |

| 8       | VCC      | 0   | LDO output pin of Internal reference voltage                               |                                                         |

| 0       | VCC      | 0   | VCC capacitor connection pin                                               |                                                         |

| 9       | GND      | -   | GND pin                                                                    |                                                         |

|         |          |     | Open drain output pin for power good                                       |                                                         |

| 10      | PG       | PG  | 0                                                                          | When being used, connect PG pin to VCC pin or VOUT pin. |

|         |          |     | When not being used, leave PG pin open.                                    |                                                         |

| 11      | SYNC     | 1   | External clock input pin                                                   |                                                         |

| 11      | STNC     | I   | For the SYNC pin setting, refer to "13.1 Setting the Operation Conditions" |                                                         |

| 12      | RT       | 0   | Timing resistor connection pin for internal clock (switching frequency)    |                                                         |

| 12      | RI.      | 0   | For the resistance, refer to "13.1 Setting the Operation Conditions"       |                                                         |

| 13      | FB       | I   | Output voltage feedback pin                                                |                                                         |

| 14      | VOUT     | 0   | DC/DC converter output pin                                                 |                                                         |

| 15      | LX2      | 0   | Inductor connection output pin.                                            |                                                         |

| 16      | PGND2    | -   | GND pin for built-in switching FET                                         |                                                         |

| EP      | GND      | -   | GND pin                                                                    |                                                         |

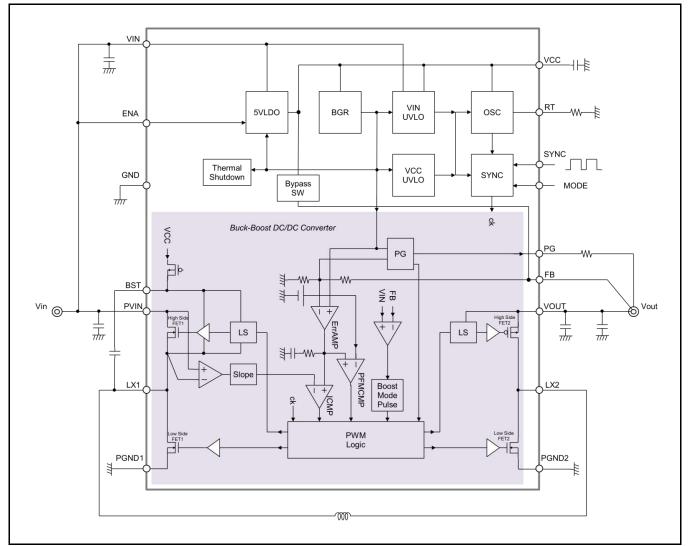

## 7. Block Diagram

Figure 7-1 Block Diagram

### 8. Absolute Maximum Ratings

| Denemater                 | Cumula al           | Condition              | Rat  | ting             | l lució |

|---------------------------|---------------------|------------------------|------|------------------|---------|

| Parameter                 | Symbol              | Condition              | Min  | Max              | Unit    |

|                           | V <sub>VIN</sub>    | VIN pin                | -0.3 | +48.0            | V       |

| Power supply voltage (*1) | V <sub>PVIN</sub>   | PVIN pin               | -0.3 | +48.0            | V       |

|                           | V <sub>VCC</sub>    | VCC pin                | -0.3 | +6.9             | V       |

|                           | V <sub>BST</sub>    | BST pin                | -0.3 | +48.0            | V       |

|                           | V <sub>LX1</sub>    | LX1 pin                | -2.0 | +48.0            | V       |

|                           | V <sub>LX2</sub>    | LX2 pin                | -2.0 | +6.9             | V       |

|                           | V <sub>FB</sub>     | FB pin                 | -0.3 | V <sub>VCC</sub> | V       |

| Terminal voltage (*1)     | V <sub>RT</sub>     | RT pin                 | -0.3 | V <sub>VCC</sub> | V       |

|                           | V <sub>MODE</sub>   | MODE pin               | -0.3 | V <sub>VCC</sub> | V       |

|                           | V <sub>SYNC</sub>   | SYNC pin               | -0.3 | V <sub>VCC</sub> | V       |

|                           | V <sub>ENA</sub>    | ENA pin                | -0.3 | +48.0            | V       |

|                           | V <sub>PG</sub>     | PG pin                 | -0.3 | +6.9             | V       |

|                           | V <sub>BST-LX</sub> | Between BST–LX1 pins   | -0.3 | +6.9             | V       |

| Difference voltage (*1)   | V                   | Between GND–PGND1 pins | 0.2  | +0.3             | V       |

|                           | $V_{GND}$           | Between GND–PGND2 pins | -0.3 | +0.5             | v       |

| PG output current         | I <sub>PG</sub>     | PG pin                 | -3   | 0                | mA      |

| Power dissipation (*1)    | PD                  | Ta ≤ ±25°C             | 0    | 3324 (*2)        | mW      |

| Storage temperature       | T <sub>STG</sub>    | -                      | -55  | +150             | °C      |

\*1: When PGND1 = PGND2 = GND = 0V

\*2: When the product is mounted on 76.2 mm × 114.3 mm, four-layer FR-4 board

#### Warning:

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

## 9. Recommended Operating Conditions

| Devementer                    | Sumbol                     |                           | Condition         |       | Unit        |       |      |  |

|-------------------------------|----------------------------|---------------------------|-------------------|-------|-------------|-------|------|--|

| Parameter                     | Symbol                     |                           | Condition         |       | Min Typ Max |       | Unit |  |

| Power supply veltage (*1)     | V                          | VIN                       | At start-up       | 5.0   | 12.0        | 42.0  | V    |  |

| Power supply voltage (*1)     | $V_{VIN}$                  | pin                       | After start-up    | 2.5   | 12.0        | 42.0  | V    |  |

|                               | V <sub>BST</sub>           | BST pin                   |                   | 0.0   | -           | 47.5  | V    |  |

|                               | V <sub>LX1</sub>           | LX1 pin                   |                   | -1.0  | +12.0       | +42.0 | V    |  |

|                               | $V_{LX2}$                  | LX2 pin                   |                   | -1.0  | I           | +5.5  | V    |  |

| Terminal valtage (*1)         | V <sub>FB</sub>            | FB pin                    |                   | 0.0   | -           | 5.5   | V    |  |

| Terminal voltage (*1)         | V <sub>MODE</sub> MODE pin |                           | 0.0               | -     | 5.5         | V     |      |  |

|                               | V <sub>SYNC</sub>          | IC SYNC pin               |                   | 0.0   | -           | 5.5   | V    |  |

|                               | V <sub>ENA</sub>           | ENA pin                   |                   | 0.0   | 12.0        | 42.0  | V    |  |

|                               | V <sub>PG</sub>            | PG pin                    |                   | 0.0   | -           | 5.5   | V    |  |

|                               | V <sub>BST-LX1</sub>       | Between BST-LX1 pins      |                   | 0.0   | -           | 5.5   | V    |  |

| Difference voltage (*1)       | V <sub>GND</sub>           |                           | n GND-PGND1 pins, | -0.05 | 0.00        | +0.05 | v    |  |

|                               | 0115                       | Between GND-PGND2 pins    |                   |       |             |       |      |  |

| PG output current             | I <sub>PG</sub>            | PG pin (                  | sink current)     | 0     | -           | 1     | mA   |  |

| BST capacitance               | C <sub>BST</sub>           | Between BST-LX1 pins      |                   | 0.068 | 0.100       | 0.470 | μF   |  |

| VCC capacitance               | C <sub>VCC</sub>           | Between VCC-GND pins      |                   | 2.2   | 4.7         | 10.0  | μF   |  |

| Timing resistance             | R <sub>RT</sub>            | Betweer                   | n RT-GND pins     | 22    | -           | 270   | kΩ   |  |

|                               |                            | When using internal clock |                   |       |             |       |      |  |

| Operating ambient Temperature | Та                         |                           | -                 | -40   | +25         | +125  | °C   |  |

\*1: When PGND1 = PGND2 = GND = 0V

#### Warning:

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

## **10. Electrical Characteristics**

#### VIN = PVIN = 12V, ENA = 5V

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

|              | Deveryor                   |                        | Condition                                                   | Value   |       |                   |      |

|--------------|----------------------------|------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

| Parameter    |                            | Symbol                 | Condition                                                   | Min     | Тур   | Max               | Unit |

|              |                            |                        | $I_{VOUT}$ = 0A, When $V_{VOUT}$ = 5.000 (*1)               | 4.925   | 5.000 | 5.075             | V    |

|              |                            |                        | $I_{VOUT}$ = 0A, When $V_{VOUT}$ = 5.050 (*1)               | 4.975   | 5.050 | 5.125             | V    |

|              |                            |                        | $I_{VOUT}$ = 0A, When $V_{VOUT}$ = 5.075 (*1)               | 4.999   | 5.075 | 5.151             | V    |

|              | VOUT output voltage        | V <sub>VOUT</sub>      | I <sub>VOUT</sub> = 0A, When V <sub>VOUT</sub> = 5.100 (*1) | 5.024   | 5.100 | 5.176             | V    |

|              |                            |                        | I <sub>VOUT</sub> = 0A, When V <sub>VOUT</sub> = 5.125 (*1) | 5.048   | 5.125 | 5.201             | V    |

|              |                            |                        | $I_{VOUT}$ = 0A, When $V_{VOUT}$ = 5.150 (*1)               | 5.073   | 5.150 | 5.227             | V    |

|              |                            |                        | I <sub>VOUT</sub> = 0A, When V <sub>VOUT</sub> = 5.200 (*1) | 5.122   | 5.200 | 5.278             | V    |

| Buck-boost   | FB input resistance        | R <sub>FB</sub>        | EN = 0V, Ta = +25°C                                         | 3.84    | 4.80  | 5.76              | MΩ   |

| DC/DC        |                            | R <sub>HSIDEFET1</sub> | LX1 = -30 mA (Between PVIN-LX1)                             | -       | 150   | -                 | mΩ   |

| converter    | Switching FET              | R <sub>LSIDEFET1</sub> | LX1 = 30 mA (Between LX1-PGND1)                             | -       | 150   | -                 | mΩ   |

| Block        | on-resistance              | R <sub>HSIDEFET2</sub> | LX2 = -30 mA (Between VOUT-LX2)                             | -       | 150   | -                 | mΩ   |

|              |                            | R <sub>LSIDEFET2</sub> | LX2 = 30 mA (Between LX2-PGND2)                             | -       | 150   | -                 | mΩ   |

|              | Switching FET              | 1 .                    |                                                             |         |       | _                 |      |

|              | leakage current            | I <sub>LEAK</sub>      | -                                                           | -       | -     | 5                 | μA   |

|              | Soft-start time            | T <sub>SS</sub>        | R <sub>RT</sub> = 22 kΩ                                     | 0.855   | 0.9   | 0.945             | ms   |

|              |                            | I <sub>VOUT</sub>      | PVIN ≥ 7.5V, Ta = 25°C                                      | -       | -     | 1.0(*2)           | Α    |

|              | VOUT output current        |                        | PVIN = 4.5V, Ta = 25°C                                      | -       | -     | 1.0(*2)           | Α    |

|              | Current limit              | I <sub>LIMT</sub>      | PVIN = 12V, L = 2.2µH                                       | 1.0(*2) | -     | -                 | Α    |

| 5V LDO block | VCC output voltage         | V <sub>VCC</sub>       | VIN = 12V                                                   | 4.9     | 5.0   | 5.1               | V    |

| VIN UVLO     | VIN UVLO falling threshold | VUVLOVINHL             | VIN input voltage when falling                              | 2.30    | 2.40  | 2.50              | V    |

| block        | VIN UVLO rising threshold  | VUVLOVINLH             | VIN input voltage when rising                               | 4.55    | 4.75  | 4.95              | V    |

| VCC UVLO     | VCC UVLO falling threshold | VUVLOVCCHL             | VCC input voltage when falling                              | 2.30    | 2.40  | 2.50              | V    |

| block        | VCC UVLO rising threshold  | VUVLOVCCLH             | VCC input voltage when rising                               | 4.55    | 4.75  | 4.95              | V    |

|              |                            | V <sub>ENA</sub>       | Enable voltage range                                        | 1.10    | -     | V <sub>VIN</sub>  | V    |

| ENA pin      | Enable condition           | V <sub>DSB</sub>       | Disable voltage range                                       | 0.0     | -     | 0.2               | V    |

|              | ENA input current          | I <sub>ENA</sub>       | V <sub>ENA</sub> = 12V                                      | -       | 1     | 3                 | μA   |

|              |                            | N/                     | Automatic PWM/PFM switching                                 | 0.0     |       | 0.4               | V    |

|              | MODE input voltage         | V <sub>MODE_L</sub>    | operation                                                   | 0.0     | -     | 0.4               | V    |

| MODE pin     |                            | V <sub>MODE_H</sub>    | Fixed PWM operation                                         | 2.0     | -     | V <sub>VOUT</sub> | V    |

|              | MODE Input current         | I <sub>MODE</sub>      | MODE = 5.0V                                                 | -       | 5     | 10                | μA   |

| OSC block    | Switching froguency        | E                      | R <sub>RT</sub> = 22 kΩ                                     | 2.0     | 2.1   | 2.2               | MHz  |

| OSC block    | Switching frequency        | Fosc                   | R <sub>RT</sub> = 270 kΩ                                    | 180     | 200   | 220               | kHz  |

|              | SVNC input threshold       | V <sub>SYNC_L</sub>    | -                                                           | 0.0     | -     | 0.4               | V    |

| SVNC black   | SYNC input threshold       | V <sub>SYNC_H</sub>    | -                                                           | 2.0     | -     | V <sub>VOUT</sub> | V    |

| SYNC block   | SYNC input frequency       | V <sub>SYNC_L</sub>    | -                                                           | 200     | -     | 400               | kHz  |

| (SYNC_IN)    | SYNC input duty ratio      | V <sub>SYNC_H</sub>    | -                                                           | +20     | +50   | +80               | %    |

|              | SYNC leakage current       | ILKSYNC                | V <sub>SYNC</sub> = 5.0V                                    | -       | 5     | 10                | μA   |

\*1: Refer to "4. Product Lineup"

\*2: The specification is guaranteed by design, not tested in production.

#### VIN = PVIN = 12V, ENA = 5V

| ( | Unless si       | pecified otherwise.       | these are the | electrical ch | aracteristics | under the r | ecommended | operatin | a environment.) | ) |

|---|-----------------|---------------------------|---------------|---------------|---------------|-------------|------------|----------|-----------------|---|

|   | • · · · • • • • | p o o o a . o a . o o o , |               |               |               |             |            |          | g o             | / |

| Parameter                     |                            | Symphol             | Symbol Condition                         |       | Value  |        |      |

|-------------------------------|----------------------------|---------------------|------------------------------------------|-------|--------|--------|------|

|                               |                            | Symbol Condition    |                                          | Min   | Тур    | Max    | Unit |

|                               | VOUT UVP falling threshold | PGUVPHL             | Falling threshold for VOUT output        | 94.0  | 95.5   | 97.0   | %    |

|                               |                            |                     | voltage setting (*1)                     |       |        |        |      |

|                               | VOUT UVP rising threshold  | P <sub>GUVPLH</sub> | Rising threshold for VOUT output         | 95.0  | 96.5   | 98.0   | %    |

|                               |                            | GOVI EIT            | voltage setting (*1)                     |       |        |        |      |

|                               | VOUT OVP rising threshold  | PGOVPLH             | Rising threshold for VOUT output         | 103.0 | 104.5  | 106.0  | %    |

| PG block                      |                            | GOVPLH              | voltage setting (*1)                     | 100.0 | 101.0  | 100.0  | ,,,  |

| (UVP, OVP)                    | VOUT OVP falling threshold | $P_{GOVPHL}$        | Falling threshold for VOUT output        | 102.0 | 103.5  | 105.0  | %    |

| $(\mathbf{UVF},\mathbf{UVF})$ |                            |                     | voltage setting (*1)                     | 102.0 | 100.0  | 100.0  | 70   |

|                               | Leak current               | I <sub>LKPG</sub>   | $V_{PWRGD}$ = 5.0V, $V_{ENA}$ = 0V       | 0     | -      | 1      | μA   |

|                               | Low level output voltage   | V <sub>OLPG</sub>   | I <sub>PGSINK</sub> = 1 mA               | 0.025 | 0.05   | 0.15   | V    |

|                               | Delay time                 | т                   | At nower obutdown                        |       | 7(*0)  | 10/*0) |      |

|                               | at abnormal detection      | T <sub>PPG</sub>    | At power shutdown                        | -     | 7(*2)  | 12(*2) | μs   |

|                               | Power-on reset time (*1)   | T <sub>RPG</sub>    | At power good                            | 9.1   | 14.0   | 18.9   | ms   |

| Thermal                       |                            | -                   |                                          |       | 165    |        | °C   |

| shutdown                      | Shutdown temperature       | T <sub>TSDH</sub>   | _                                        | -     | (*2)   | _      | C    |

| block (TSD)                   |                            | T <sub>TSDL</sub>   | Hysteresis                               | -     | 10(*2) | -      | °C   |

|                               | Shutdown current           | I <sub>VINSDN</sub> | VIN input current, V <sub>ENA</sub> = 0V | -     | 1      | 5      | μA   |

| Supply ourset                 |                            |                     | VIN input current, $V_{ENA}$ = 12V,      |       |        |        |      |

| Supply current                | Quiescent current          |                     | I <sub>VOUT</sub> = 0A,                  | -     | 20     | 40     | μA   |

|                               |                            |                     | MODE/SYNC/PG Pins = OPEN                 |       |        |        |      |

\*1: Refer to "4. Product Lineup"

$\ensuremath{^{\ast}2}\xspace$  The specification is guaranteed by design, not tested in production.

## 11. Functional Description

### **11.1 Protection Function**

#### Input Under Voltage Lockout (Input UVLO)

The input UVLO is the function that prevents a malfunction of this IC from the following status, and protects poststage devices.

- Transitional state at start-up

- Momentary drop of power supply voltage

To prevent such a malfunction, this protection monitors the VIN input voltage and VCC voltage. When either VIN or VCC voltage falls to the UVLO falling threshold, 2.4V (Typ), or lower, the IC stops the VOUT voltage output and becomes UVLO status. When both VIN and VCC voltages reach the UVLO rising threshold, 4.75V (Typ), or higher, the IC is released from the UVLO state and returns to the normal operation.

#### **Output Under Voltage Protection (Output UVP)**

The output UVP is the function that monitors the voltage drop of the VOUT pin and notifies by the PG pin.

When the output voltage falls to the UVP falling threshold ( $P_{GUVPHL}$ ) for the output voltage setting or lower, the PG voltage is fixed to the low level. The IC becomes the UVP status, but the switching operation is maintained under the UVP status.

When the output voltage once again reaches the UVP rising threshold ( $P_{GUVPLH}$ ) for the output voltage setting or higher, the IC is released from the UVP state and the PG voltage is fixed to the high level.

#### **Output Over Voltage Protection (Output OVP)**

The output OVP is the function that monitors the voltage rise of the VOUT pin and stops the switching operations, which protects poststate devices from overvoltage. Also, the VOUT state is notified by the PG pin.

When the output voltage rises to the OVP falling threshold ( $P_{GOVPLH}$ ) for the output voltage setting or higher, the PG voltage is fixed to the low level. The IC becomes the OVP status, and the switching operations of the high-side FETs are stopped. When the output voltage once again falls to the OVP falling threshold ( $P_{GOVPHL}$ ) for the output voltage setting or lower, the IC is released from the OVP state and resumes the switching operations. The PG voltage is fixed to the high level again.

#### **Output Over Current Protection (Output OCP)**

The output OCP is the function that limits the excessive current load and protects poststage devices.

#### Thermal Shutdown (TSD)

The TSD is the function that protects the IC from heat-destruction. When the junction temperature reaches +165°C (Typ), the high-side and low-side switching FET are turned off and the IC becomes the TSD status. When the junction temperature once again falls to +155°C (Typ) or lower, the IC is released from the TSD state and restarts the power supply.

## **11.2** Protection Function Table

The following table shows the state of each pin when each protection function operates.

| Function                                        | ENA Pin<br>Setting | PG Pin<br>Output | DC/DC<br>Converter<br>Operation | Remarks                                                                                                                                                                                                            |

|-------------------------------------------------|--------------------|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shutdown operation                              | L                  | Hi-Z(*1)         | Shutdown                        | It is recommended to connect PG pin to<br>VCC pin or VOUT pin via a pull-up<br>resistor.<br>When setting ENA pin to a low level, both<br>VCC pin and VOUT pin voltage drop to<br>0V. Therefore, PG pin outputs 0V. |

| Nominal operation                               | Н                  | Hi-Z(*1)         | Switching                       | -                                                                                                                                                                                                                  |

| Input under voltage protection<br>(Input UVLO)  | Н                  | L                | Shutdown                        | After releasing UVLO state, this IC is automatically reset with soft start.                                                                                                                                        |

| Output under voltage protection<br>(Output UVP) | Н                  | L                | Switching                       | -                                                                                                                                                                                                                  |

| Output over voltage protection<br>(Output OVP)  | Н                  | L                | Shutdown                        | -                                                                                                                                                                                                                  |

| Output over current protection<br>(Output OCP)  | Н                  | L                | Switching                       | OCP operates to drop the output voltage.                                                                                                                                                                           |

| Thermal shutdown<br>(TSD)                       | Н                  | L                | Shutdown                        | After releasing TSD state, this IC is automatically reset with soft start.                                                                                                                                         |

| Table 11-1 Protection Function Table | Table 11-1 | Protection | Function | Table |

|--------------------------------------|------------|------------|----------|-------|

|--------------------------------------|------------|------------|----------|-------|

\*1: PG pin is formed as an open drain structure. The internal MOSFET is in the OFF state.

## 12. Application Circuit Example and Parts list

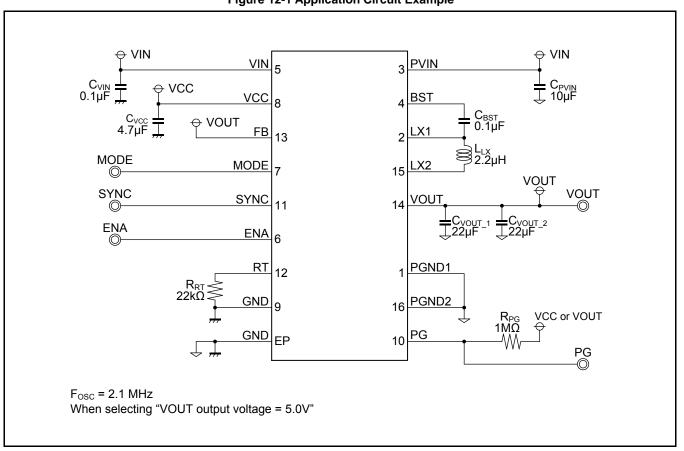

### Figure 12-1 Application Circuit Example

| Symbol                                 | Item              | Value  | Part Number          | Vendor | Package Size<br>(W×L×H[mm]) | Remarks                                  |

|----------------------------------------|-------------------|--------|----------------------|--------|-----------------------------|------------------------------------------|

| C <sub>VIN</sub> ,<br>C <sub>BST</sub> | Ceramic capacitor | 0.1 µF | CGA2B3X7R1H104K050BB | TDK    | 1.0×0.5×0.5                 | X7R, Rated Voltage: 50 Vdc               |

| C <sub>PVIN</sub>                      | Ceramic capacitor | 10 µF  | CGA9N3X7R1H106K230KB | TDK    | 5.7×5.0×2.3                 | X7R, Rated Voltage: 50 Vdc               |

| C <sub>VCC</sub>                       | Ceramic capacitor | 4.7 µF | CGA4J3X7R1C475K125AB | TDK    | 2.0×1.25×1.25               | X7R, Rated Voltage: 16 Vdc               |

| $C_{VOUT_1}, C_{VOUT_2}$               | Ceramic capacitor | 22 µF  | CGA6P1X7R1C226M250AC | TDK    | 3.2×2.5×2.5                 | X7R, Rated Voltage: 16 Vdc               |

| $L_{LX}$                               | Inductor          | 2.2 µH | CLF7045T-2R2N-D      | TDK    | 7.2×6.9×4.5                 | DCR: 14.6 mΩ, I <sub>DC_MAX</sub> : 5.5A |

| R <sub>RT</sub>                        | Resistor          | 22 kΩ  | RK73H1JTTD2202F      | KOA    | 0.8×1.6×0.45                | -                                        |

KOA

0.8×1.6×0.45

RK73H1JTTD1004F

TDK: TDK Corporation KOA: KOA Corporation

Resistor

1 MΩ

$R_{PG}$

#### Table 12-1 Parts List

\_

## 13. Application Note

### **13.1 Setting the Operation Conditions**

#### **Operation State of DC/DC Convertor**

The operation stage of DC/CD converter is set by both MODE pin and SYNC pin.

| MODE   | SYNC Pin                  | Operation State of DC/DC Convertor                                        |  |

|--------|---------------------------|---------------------------------------------------------------------------|--|

| Pin    | (Signal Input)            |                                                                           |  |

|        | L (*3)                    | Automatic PWM/PFM switching operation from an internal clock              |  |

| L (*3) | External clock input (*5) | Fixed PWM operation with synchronizing signal from an external clock (*2) |  |

|        | H (*4)                    | Prohibition of use (*1)                                                   |  |

| H (*4) | L (*3)                    | Fixed PWM operation from an internal clock                                |  |

|        | External clock input (*5) | Fixed PWM operation with synchronizing signal from an external clock (*2) |  |

|        | H (*4)                    | Prohibition of use (*1)                                                   |  |

#### Table 13-1 Operation State of DC/DC Convertor

$\overline{1}$ : When setting SYNC pin to a high level, the quiescent current ( $I_{VINQ}$ ) is increased.

\*2: Set the timing resistance ( $R_{RT}$ ) to 330 k $\Omega$ .

\*3: Apply the GND1 or GND2 voltage.

\*4: Apply the VOUT voltage.

\*5: Apply the VOUT voltage at a high level. Apply the GND1 or GND2 voltage at a low level

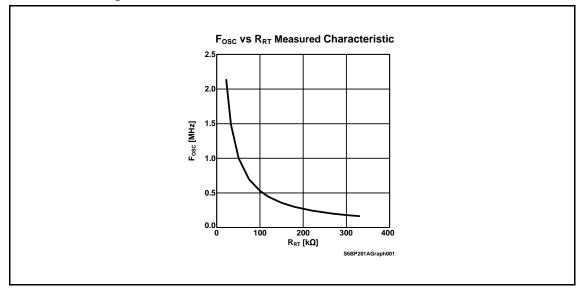

#### Setting of Switching Frequency (Internal Clock)

The switching frequency (internal clock) can be set by RT resistor, which value is the timing resistance ( $R_{RT}$ ), connected to RT pin. Set the timing resistance in a range within the following graph.

Figure 13-1 Fosc vs R<sub>RT</sub> Measured Characteristic

The reference value can be calculated by the following formula.

$$\begin{split} F_{OSC} \ [\text{Hz}] &\approx \frac{1}{\text{R}_{\text{RT}} \times 21.7 \times 10^{-12}} \\ F_{OSC} &: \text{Switching frequency [Hz]} \\ \text{R}_{\text{RT}} &: \text{Timing resistance } [\Omega] \end{split}$$

#### Setting of Soft-start Time

The Soft-start time is determined by the timing resistance ( $R_{RT}$ ), the value of the resistor connected to RT pin.

$$T_{\rm SS} [s] = \frac{1}{F_{\rm OSC}} \times 2 \times 1024$$

$\begin{array}{ll} T_{SS} & : \mbox{ Soft-start time [s]} \\ F_{OSC} & : \mbox{ Switching frequency [Hz]} \end{array}$

### Consideration of VOUT Maximum Output Current

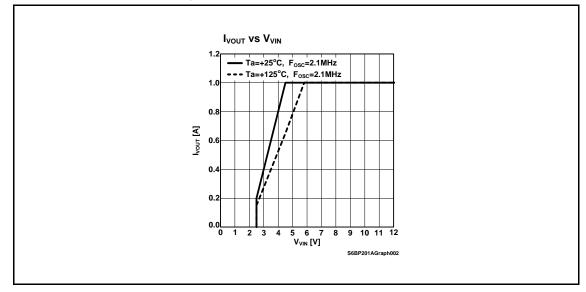

Make sure the VOUT maximum output current in a range within the following graph.

Figure 13-2 I<sub>VOUT</sub> vs V<sub>VIN</sub>

### 14. Usage Precaution

Printed circuit board ground lines should be set up with consideration for common impedance.

#### Take appropriate measures against static electricity.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial body and ground.

#### Do not apply negative voltages.

The use of negative voltages below -0.3V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

## 15. RoHS Compliance Information

This product has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

### 16. Ordering Information

| Order<br>Code | Part Number (*1)       | Package                                 |  |  |

|---------------|------------------------|-----------------------------------------|--|--|

| 1A            | S6BP201A1AST2B000      |                                         |  |  |

| 4A            | S6BP201A4AST2B000      | Plastic TSSOP16 (0.65 mm pitch), 16-pin |  |  |

| 7A            | S6BP201A7AST2B000      | (SEC016)                                |  |  |

| ES            | S6BP201AESET21000 (*2) |                                         |  |  |

\*1: Please contact our sales division for the part numbers (refer to "4. Product Lineup") not mentioned in this table.

\*2: This part number is used for the engineering sample (ES). Please contact our sales division for the order code (refer to "4. Product Lineup").

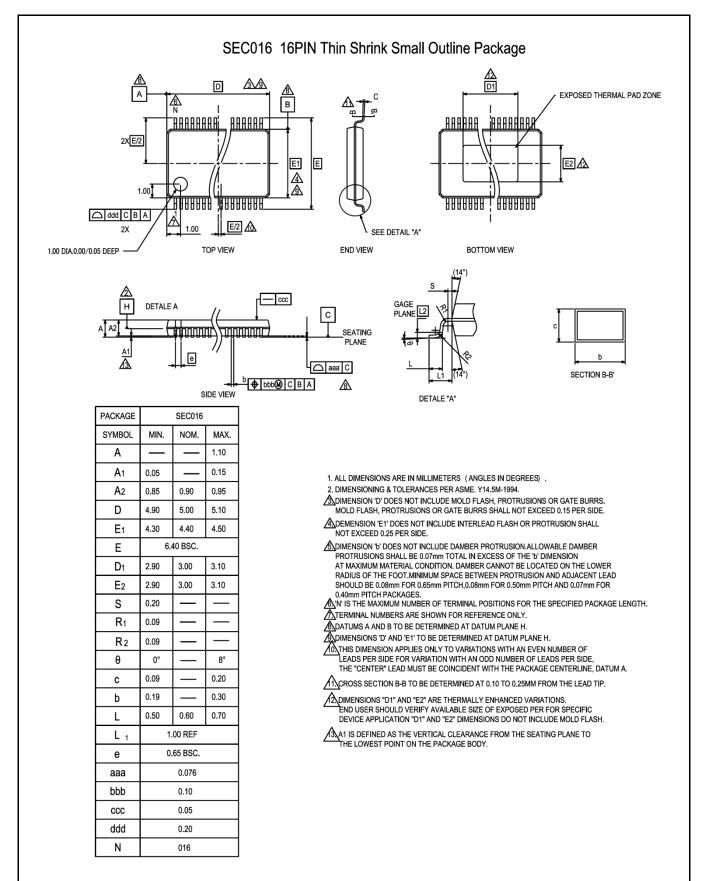

## 17. Package Dimensions

## 18. Major Changes

| Page            | Section         | Change Results                                                      |  |  |

|-----------------|-----------------|---------------------------------------------------------------------|--|--|

| Preliminary 0.1 |                 |                                                                     |  |  |

| -               | -               | Initial release                                                     |  |  |

| Preliminary 0.2 |                 |                                                                     |  |  |

| 12              | 10. Electrical  | "/TSD)" was added in the table of "10. Electrical Characteristics"  |  |  |

|                 | Characteristics | "(TSD)" was added in the table of "10. Electrical Characteristics". |  |  |

#### Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Cypress will not be liable to you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country, the prior authorization by the respective government entity will be required for export of those products.

#### Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Cypress product under development by Cypress. Cypress reserves the right to change or discontinue work on any product without notice. The information in this document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose, merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Cypress assumes no liability for any damages of any kind arising out of the use of the information in this document.

Copyright © 2015 Cypress Semiconductor Corp. All rights reserved. Cypress, the Cypress logo, Spansion<sup>®</sup>, the Spansion logo, MirrorBit<sup>®</sup>, MirrorBit<sup>®</sup> Eclipse<sup>TM</sup>, ORNAND<sup>TM</sup>, Easy DesignSim<sup>TM</sup>, Traveo<sup>TM</sup> and combinations thereof, are trademarks and registered trademarks of Cypress Semiconductor Corp. in the United States and other countries. Bluetooth is a trademark of Bluetooth SIG. Other names used are for informational purposes only and may be trademarks of their respective owners.