#### RF AMPLIFIER FOR DIGITAL SERVO SYSTEM

#### **DESCRIPTION**

SA9618A can be used for ALPC and signal conversion between CD optical pickup and decoding chip.

This IC incorporates an interconnection to general CD optical pickup photodiode, bias voltage VREF generation circuit, RF amplifier and ALPC circuit.(This IC is adaptive for CD-A/V,CD-R,CD-R/W,CD-ROM).

#### **FEATURES**

- \* RF amplitude automatic adjustment circuit .(It is adaptive for CD-A/V,CD-R,CD-R/W,CD-ROM)

- \* Low power consumption.(35mW ~ 3.5V)

- \* ALPC circuit

- \* Operating voltage range: 2.8V 7.0V

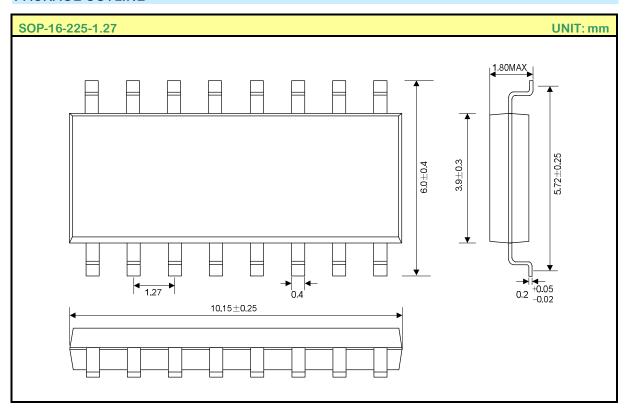

#### **ORDERING INFORMATION**

| Device  | Package         |

|---------|-----------------|

| SA9618A | SOP-16-225-1.27 |

#### **APPLICATIONS**

- \* CD Players

- \* VCD Players

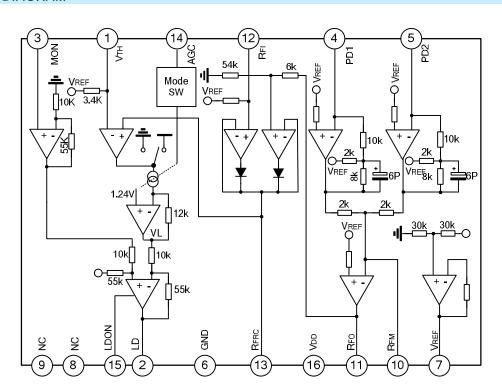

#### **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS (Tamb=25°C)

| Characteristics       | Symbol | Rating     | Unit |

|-----------------------|--------|------------|------|

| Supply Voltage        | VDD    | -0.5 ~ +12 | V    |

| Operating Temperature | Topr   | -20 ~ +75  | °C   |

| Power Dissipation     | PD     | 370        | mW   |

## DC ELECTRICAL CHARACTERISTICS

| Characteristics                     | Symbol | Test Condition | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------|----------------|------|------|------|------|

| Supply voltage                      | VDD    |                | 2.8  | 5.0  | 7.0  | >    |

| Bias Output Of Photoelectric Signal | VREF   |                |      | 2.5  | 1    | ٧    |

| Current Consumption                 | IDD    | VDD=5V         |      | 12   |      | mA   |

#### **AC ELECTRICAL CHARACTERISTICS**

| Characteristics            | Symbol | Test Conditions | Min. | Тур. | Max. | Unit     |

|----------------------------|--------|-----------------|------|------|------|----------|

| Diode Control Input        | MON    |                 |      | 0.17 |      | V        |

| Photoelectric Input 1(A+C) | PD1    | DA11            | 0    |      | 0.60 | <b>V</b> |

|                            |        | KSS213          | 0    |      | 0.15 | V        |

| Photoelectric Input 2(B+D) | PD2    | DA11            | 0    |      | 0.60 | ٧        |

|                            |        | KSS213          | 0    |      | 0.15 | V        |

| Gain Of RF Signal          | GAIN   | 1MHZ, 300mVpp   |      | 15   | -    | dB       |

Note 1: The resistance between Pin RFM and Pin RFO is 5.5K.

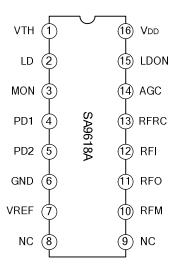

#### **PIN CONFIGURATION**

#### PIN DESCRIPTION

| Pin No. | Symbol | Description                                                                            |  |  |  |  |

|---------|--------|----------------------------------------------------------------------------------------|--|--|--|--|

| 1       | VTH    | eference level variable pin for RF level control.                                      |  |  |  |  |

| 2       | LD     | APC circuit output pin.                                                                |  |  |  |  |

| 3       | MON    | Diode control input pin.                                                               |  |  |  |  |

| 4       | PD1    | Photoelectric input1 (A+C) pin.                                                        |  |  |  |  |

| 5       | PD2    | Photoelectric input2 (B+D) pin.                                                        |  |  |  |  |

| 6       | GND    | GND                                                                                    |  |  |  |  |

| 7       | VREF   | Bias output pin of OEIC.                                                               |  |  |  |  |

| 8       | NC     | RF level control ON/OFF switching pin                                                  |  |  |  |  |

| 9       | NC     | Gain select pin for RF signal.                                                         |  |  |  |  |

| 10      | RFM    | RF level control output pin                                                            |  |  |  |  |

| 11      | RFO    | RF amplifier inverted side output pin. RF amplifier gain is determined by the resistor |  |  |  |  |

| 11      | KFO    | connected between RFO pin and RFM pin.                                                 |  |  |  |  |

| 12      | RFI    | RF amplifier input pin.                                                                |  |  |  |  |

| 13      | RFRC   | External time-constant pin for RF level control.                                       |  |  |  |  |

| 14      | AGC    | The automatic switching pin for optical power.                                         |  |  |  |  |

| 15      | LDON   | ALPC circuit ON/OFF switching pin.                                                     |  |  |  |  |

| 16      | VDD    | VDD pin.                                                                               |  |  |  |  |

NOTE: LDON pin is low active in SA9618A, but it must be connected to an external resistor of  $150k\Omega$ .

#### **FUNCTION DESCRIPTIONS**

SA9618A can be divided into three parts: Reference voltage generation circuit; RF signal processing circuit incorporating two RF Amplifiers and an RF adder; Automatic switching APC circuit incorporating optical power switching circuit, RF demodulation circuit and automatic optical power control circuit.

Reference voltage is half of VDD. It is not only the common level for amplifier in circuit, but also the bias voltage of OEIC.

The feedback resistor of each RF Amplifier is  $58k\Omega$ . And the gain of RF amplifier is the ratio of the  $58k\Omega$ equivalent resistance and external resistor connected between PD1 pin and PD2 pin. When the resistance value is 33k, the gain of RF Amplifier is 1.76.

The output of each RF Amplifier is added by RF adder. The gain of RF adder can be adjusted by varying the resistor connected between RFM pin and RFO pin. When the resistance value is 5.5k, the gain of RF summing amplifier is 2.75.

The output of Peak value of RF demodulation circuit comes from the output of RF adder. The DC voltage formed by external RC filter of RFRC pin, and it is related to the level of input of PD1 pin and PD2 pin. The DC voltage will increase as the level of the input becomes higher.

Optical Power switching circuit is controlled by AGC pin. It has three modes: connected to GND, open, connected to supply voltage. The optical power can be adjusted by varying the voltage of VL. There are five VL values, and it is as follows.

**REV:1.1** 2006.07.14 Http: www.silan.com.cn Page 3 of 6

| AGC  | The level of input | Value of VL | Strength of optical power |

|------|--------------------|-------------|---------------------------|

| VCC  | *                  | 1.25V       | middle                    |

| OPEN | large RFRC>VTH     | 0.9V        | weaker                    |

| OPEN | small RFRC>VTH     | 1.6V        | stronger                  |

| GND  | large RFRC>VTH     | 0.7         | weakest                   |

| GND  | small RFRC>VTH     | 1.8         | strongest                 |

Pin LDON controls APC circuit. In SA9618A, APC is set to ON by connecting the LDON pin to GND; and set to OFF by connecting it to VDD, and SA9618A should be connected to an external resistance of  $150 k\Omega$  between LDON pin and external MCU.

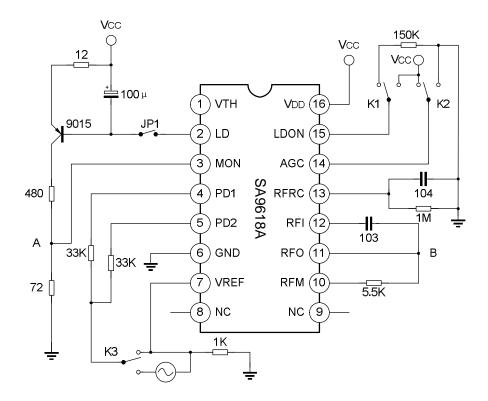

#### **TEST CIRCUITS**

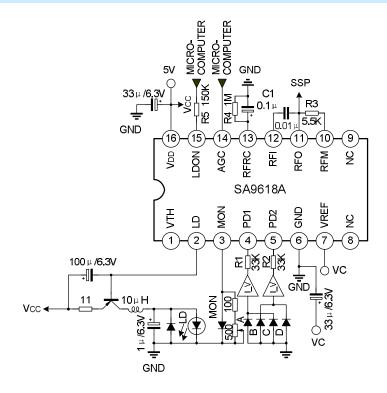

## **TYPICAL APPLICATION CIRCUIT**

## **PACKAGE OUTLINE**

# Attach

# **Revision History**

| Data       | REV | Description                              | Page |

|------------|-----|------------------------------------------|------|

| 2006.01.23 | 1.0 | Original                                 |      |

| 2006.07.14 | 1.1 | Modify the "TYPICAL APPLICATION CIRCUIT" |      |