# **SAA7160**

## PCI Express based audio and video bridge

Rev. 01 — 25 February 2008

**Product data sheet**

### 1. General description

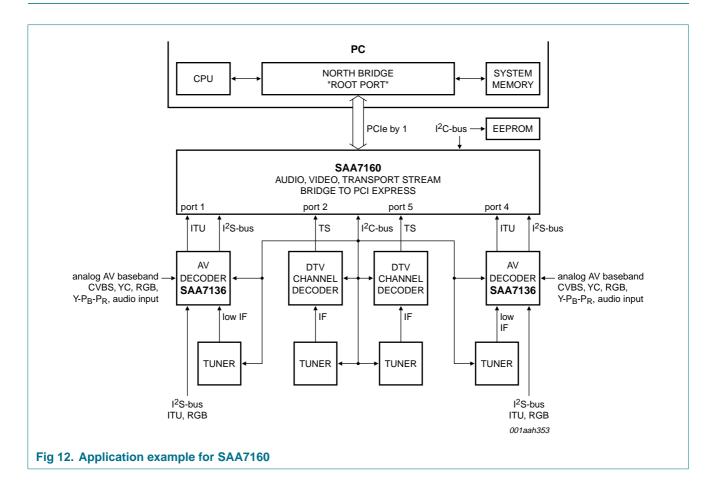

The SAA7160E and the SAA7160ET are PCI Express based audio and video capture bridges. Both devices provide ports for capturing video streams, transport streams, program streams and audio streams with audio functionality like I<sup>2</sup>S-bus inputs. The bridges provide audio and video capture function as required for PCI Express applications like Microsoft 'multimedia center'.

The target is to cover a range of performance applications like personal video recording and PC TV cards.

The SAA7160E and the SAA7160ET are highly integrated circuits for TV insertion inside PC systems. Additional high-speed programming ports enable high integrated system solutions for multimedia applications.

#### 2. Features

#### 2.1 PCI Express interface SAA7160E and SAA7160ET

- Compliant to PCI Express Base Specification 1.0a

- Native PCI Express

- ◆ 64-bit address support

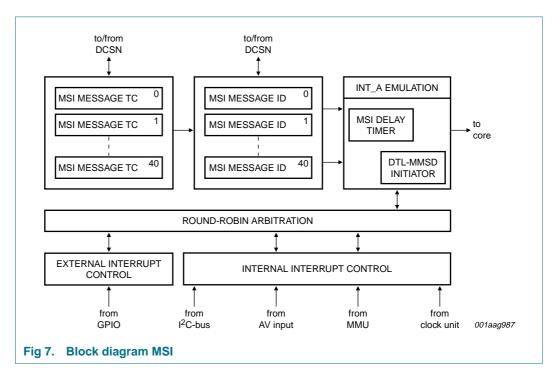

- MSI and INT\_A message support

- The PCI Express circuit supports isochronous data traffic intended for uninterrupted transfer of streaming data like video streaming

- x1 PCI Express endpoint device (2.5 Gbit/s)

- Low jitter and bit error rate

- Type 0 configuration space header

- Single BAR; configurable address range of 17 bits, 18 bits, 19 bits or 20 bits dependent on application requirements

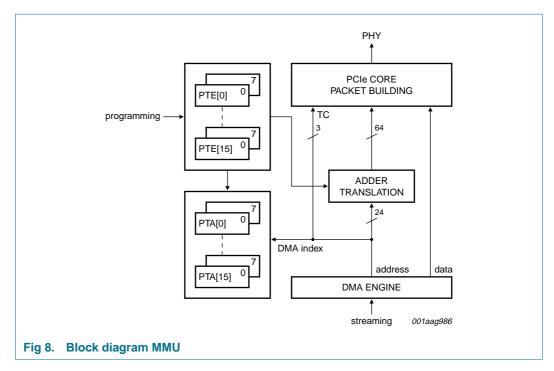

- DMA write support

- 12 DMA write channels for AV streaming

- Managing up to 8 software buffers per DMA channel

- ◆ Buffer size of 2 MB extendable to 4 MB (e.g. HDTV)

- Round-robin arbitration between DMAs

Support overflow recovery if PCI Express bandwidth is not granted in the required amount

#### PCI Express based audio and video bridge

- DMA read support

- Autonomous address translation on PCI Express bus

- ◆ One DMA read channel for reading from page table(s) in system memory

- PCI Express capabilities

- ◆ 128 B write packet size and 64 B read packet size

- MSI support

- INT\_A emulation

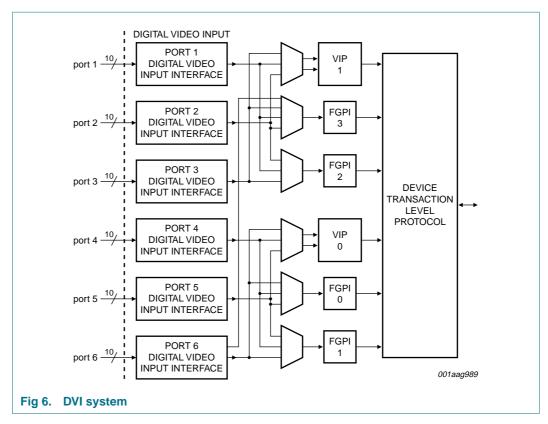

#### 2.2 Digital interfaces SAA7160E

- Digital video input ports of 60 pins usable for maximum clock rates up to 75 MHz

- Six independent standard TV (ITU-R BT.656) 8-bit or 10-bit wide input streams (27 MHz)

or

Two standard TV 20-bit wide input streams

or

Four TS or PS 8-bit wide input streams (13.5 MHz to 54 MHz) and two independent standard TV (ITU-R BT.656) 8-bit or 10-bit wide input streams

or

One HDTV 20-bit wide input stream (75 MHz)

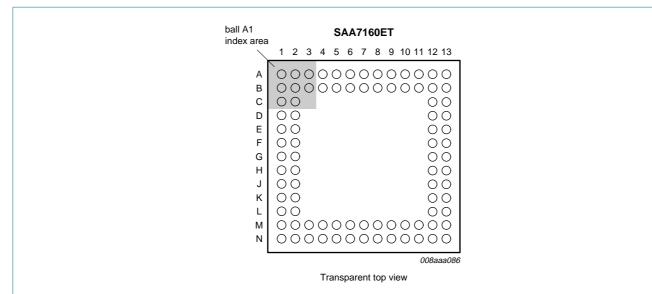

#### 2.3 Digital interfaces SAA7160ET

- Digital video input ports of 20 pins usable for maximum clock rates up to 75 MHz

- Two independent standard TV (ITU-R BT.656) 8-bit or 10-bit wide input streams (27 MHz)

or

- Two TS or PS 8-bit wide input streams (13.5 MHz to 54 MHz)

- One TS or PS 8-bit wide input stream (13.5 MHz to 54 MHz) and one independent standard TV (ITU-R BT.656) 8-bit or 10-bit wide input stream

- One HDTV 20-bit wide input stream (75 MHz)

#### 2.4 Digital peripheral audio interfaces SAA7160E and SAA7160ET

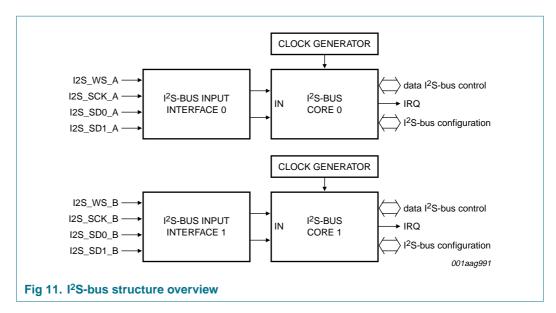

■ Two independent I<sup>2</sup>S-bus input channels supporting 32 kHz, 44.1 kHz or 48 kHz

### 2.5 Peripheral programming ports SAA7160E

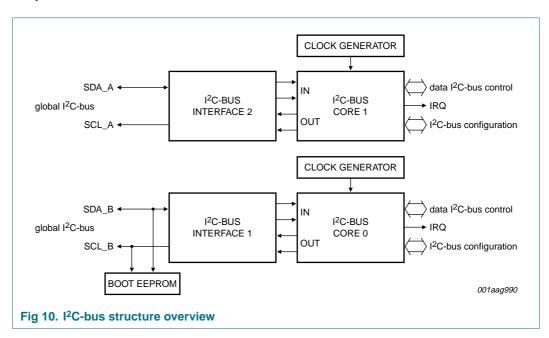

- Two I<sup>2</sup>C-bus interfaces

- ◆ I<sup>2</sup>C-bus master port to program other peripheral devices

- ◆ Support register access with 100 kHz and 400 kHz bit rate

- ◆ I<sup>2</sup>C-bus slave port, usable to support a programming interface for application systems

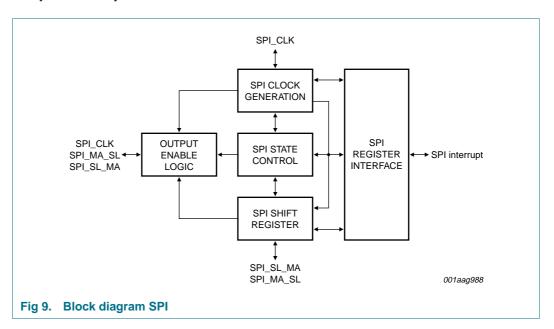

- One SPI master interface for controlling external peripherals

- PHI; this is an 16-bit wide interface for fast access to microcontroller

- Supports 8-bit data and 16-bit address interface

SAA7160\_1 © NXP B.V. 2008. All rights reserved.

#### PCI Express based audio and video bridge

28 GPIO pins for general I/O purposes, e.g. usable for interrupt input and chip select functions

### 2.6 Peripheral programming ports SAA7160ET

- Two I<sup>2</sup>C-bus interfaces

- ◆ I<sup>2</sup>C-bus master port to program other peripheral devices

- ◆ Support register access with 100 kHz and 400 kHz bit rate

- ◆ I<sup>2</sup>C-bus slave port, usable to support a programming interface for application systems

- One SPI master interface for controlling external peripherals

- 13 GPIO pins for general I/O purposes, e.g. usable for interrupt input and chip select functions

#### 2.7 General features SAA7160E and SAA7160ET

■ Boundary scan test circuit according to 'IEEE Std. 1149.1'

## 3. Ordering information

#### Table 1. Ordering information

| Type number | Package |                                                                                                    |          |

|-------------|---------|----------------------------------------------------------------------------------------------------|----------|

|             | Name    | Description                                                                                        | Version  |

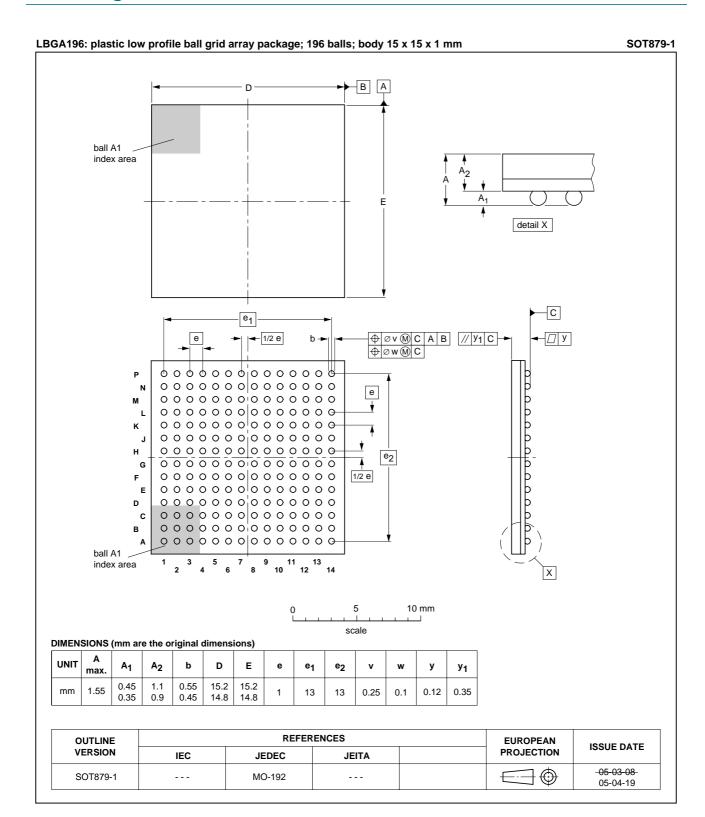

| SAA7160E    | LBGA196 | plastic low profile ball grid array package; 196 balls; body $15 \times 15 \times 1$ mm            | SOT879-1 |

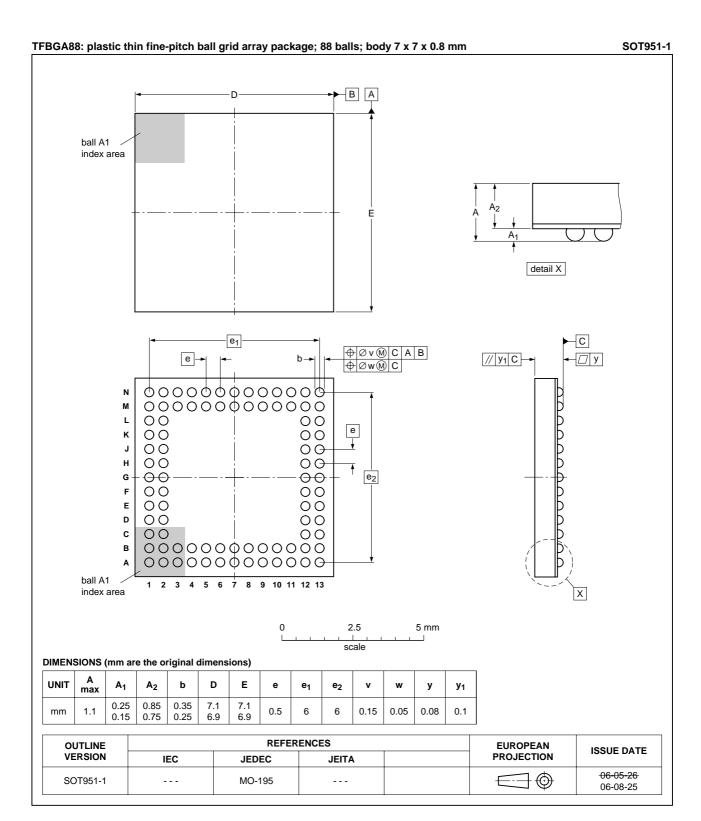

| SAA7160ET   | TFBGA88 | plastic thin fine-pitch ball grid array package; 88 balls; body $7 \times 7 \times 0.8 \text{ mm}$ | SOT951-1 |

#### PCI Express based audio and video bridge

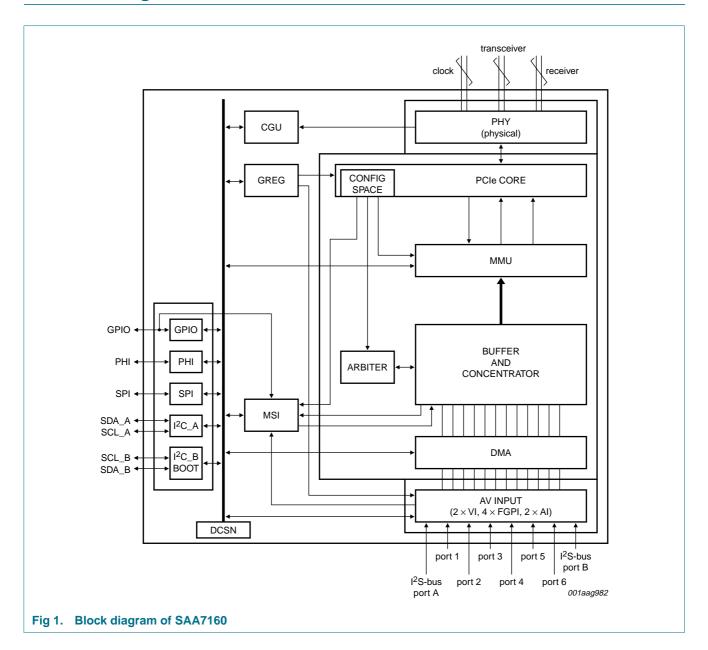

## 4. Block diagram

#### PCI Express based audio and video bridge

## 5. Pinning information

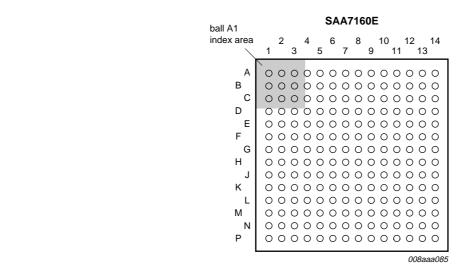

#### 5.1 SAA7160E package LBGA196

#### 5.1.1 Pinning

Transparent top view

Fig 2. Pin configuration for LBGA196

|   | 1         | 2             | 3         | 4               | 5                               | 6                               | 7                                | 8                           | 9                            | 10                                | 11            | 12        | 13            | 14        |

|---|-----------|---------------|-----------|-----------------|---------------------------------|---------------------------------|----------------------------------|-----------------------------|------------------------------|-----------------------------------|---------------|-----------|---------------|-----------|

| Α | P1_4      | P1_5          | P1_6      | P1_7            | P1_CLK                          | P5_3                            | P4_CLK                           | P4_4                        | P5_CLK                       | P5_HS                             | P4_1          | P4_0      | P6_VS<br>_SOP | P6_HS     |

| В | P1_1      | P1_2          | P1_3      | P1_HS           | P5_2                            | P4_HS                           | P4_7                             | P4_5                        | P5_7                         | P4_6                              | P4_VS<br>_SOP | P4_2      | P6_VAL        | P6_CLK    |

| С | P2_HS     | P2_VS<br>_SOP | P1_0      | P1_VS<br>_SOP   | P5_5                            | P5_6                            | P5_0                             | P5_4                        | P5_1                         | P5_VS<br>_SOP                     | P4_3          | P6_0      | P6_1          | P6_2      |

| D | P2_CLK    | P2_7          | P2_6      | PHI_7           | PHI_8                           | PHI_RDY_0                       | PHI_RDN                          | PHI_WRN                     | GPIO_17                      | GPIO_16                           | PHI_RDY_1     | P6_3      | P6_4          | P6_5      |

| Е | P2_5      | P2_4          | P2_3      | PHI_14          | PHI_12                          | V <sub>DDDI1</sub><br>(1V25)    | V <sub>DDDE3</sub><br>(3V3)      | V <sub>DDDE3</sub><br>(3V3) | PHI_15                       | PHI_13                            | PHI_6         | P5_VAL    | P6_6          | P6_7      |

| F | P2_2      | P2_1          | P2_0      | PHI_4           | V <sub>DDDI1</sub><br>(1V25)    | V <sub>SS</sub>                 | V <sub>SS</sub>                  | V <sub>SS</sub>             | V <sub>SS</sub>              | PHI_10                            | PHI_11        | P4_VAL    | P2_VAL        | P1_VAL    |

| G | I2S_SCK_B | 12S_SD1_B     | I2S_WS_B  | PHI_5           | V <sub>DDDE1</sub><br>(3V3)     | V <sub>SS</sub>                 | V <sub>SS</sub>                  | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>DDDE2</sub><br>(3V3)       | PHI_9         | I2S_SD1_A | I2S_WS_A      | I2S_SD0_A |

| Н | P3_VAL    | P3_VS<br>_SOP | I2S_SD0_B | PHI_3           | V <sub>DDDE1</sub><br>(3V3)     | V <sub>SS</sub>                 | V <sub>SS</sub>                  | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>DDDI2</sub><br>(1V25)      | PHI_ALE       | PHI_RDY_3 | P1_2_VS       | I2S_SCK_A |

| J | P3_HS     | P3_CLK        | P3_7      | PHI_1           | PHI_2                           | V <sub>SS</sub>                 | V <sub>SS</sub>                  | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>DDDI(1V25)</sub> /<br>TEST | PHI_RDY_2     | P1_2_HS   | P4_5_VS       | P1_2_FRE  |

| K | P3_6      | P3_5          | P3_4      | PHI_0           | V <sub>DDD(PCI0)</sub><br>(1V0) | V <sub>DDD(PCI1)</sub><br>(1V0) | V <sub>DDD(PCI0)</sub><br>(1V25) | V <sub>DDDE2</sub><br>(3V3) | V <sub>DDDI2</sub><br>(1V25) | GPIO_6                            | TEST1         | P4_5_HS   | GPIO_3        | P4_5_FRE  |

| L | P3_3      | P3_2          | P3_1      | GPIO_0          | V <sub>DDA(PCI0)</sub><br>(3V3) | V <sub>DDA(PCI1)</sub><br>(3V3) | V <sub>DDD(PCI1)</sub><br>(1V25) | GPIO_29                     | GPIO_26                      | GPIO_21                           | GPIO_10       | GPIO_13   | GPIO_5        | GPIO_2    |

| М | P3_0      | SCL_B         | TMS       | TRSTN           | GPIO_1                          | PCI_PVT                         | PCI_RESN                         | BOOT_1                      | SPI_SL_MA                    | GPIO_28                           | GPIO_18       | GPIO_14   | GPIO_9        | GPIO_4    |

| N | SCL_A     | SDA_B         | TDO       | V <sub>SS</sub> | V <sub>SS</sub>                 | PCI_REF<br>CLKP                 | PCI_REF<br>CLKN                  | BOOT_0                      | SPI_MA_SL                    | GPIO_23                           | GPIO_20       | GPIO_15   | GPIO_11       | GPIO_7    |

| Р | SDA_A     | TCK           | TDI       | PCI_PER<br>_P0  | PCI_PER<br>_N0                  | PCI_PET<br>_P0                  | PCI_PET<br>_N0                   | V <sub>SS</sub>             | SPI_CLK                      | GPIO_27                           | GPIO_22       | GPIO_19   | GPIO_12       | GPIO_8    |

|   |           |               |           |                 |                                 |                                 |                                  |                             |                              |                                   |               |           |               | 008aaa087 |

Fig 3. Pin configuration (LBGA196 top view) for SAA7160E

### PCI Express based audio and video bridge

## 5.1.2 Pin description

Table 2. Description of functional pins

| Symbol    | Pin | Type <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL_A     | N1  | Ю                   | I <sup>2</sup> C-bus clock of first I <sup>2</sup> C-bus interface                                                                                                                                                                                                                                                                                                                          |

| SDA_A     | P1  | Ю                   | I <sup>2</sup> C-bus data of first I <sup>2</sup> C-bus interface                                                                                                                                                                                                                                                                                                                           |

| I2S_SD0_A | G14 | Ю                   | I <sup>2</sup> S-bus port A: digital audio input signal for                                                                                                                                                                                                                                                                                                                                 |

|           |     |                     | <ul> <li>I2S_SD serial data line of Inter IC Sound bus serial interconnect format</li> </ul>                                                                                                                                                                                                                                                                                                |

| I2S_WS_A  | G13 | Ю                   | I <sup>2</sup> S-bus port A: digital audio input signal for                                                                                                                                                                                                                                                                                                                                 |

|           |     |                     | <ul> <li>I2S_WS word select line of Inter IC Sound bus serial interconnect format</li> </ul>                                                                                                                                                                                                                                                                                                |

| I2S_SCK_A | H14 | I                   | I <sup>2</sup> S-bus port A: digital audio input signal for                                                                                                                                                                                                                                                                                                                                 |

|           |     |                     | <ul> <li>I2S_SCK bit clock of Inter IC Sound bus serial interconnect format</li> </ul>                                                                                                                                                                                                                                                                                                      |

| I2S_SD1_A | G12 | I                   | I <sup>2</sup> S-bus port A: digital audio input signal for                                                                                                                                                                                                                                                                                                                                 |

|           |     |                     | <ul> <li>I2S_SD serial data line of Inter IC Sound bus serial interconnect format</li> </ul>                                                                                                                                                                                                                                                                                                |

| P1_0      | C3  | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 0</li> <li>STV YUV[9:0] bit 2</li> <li>HDTV Y[9:0] bit 2</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 0</li> <li>program stream data of PS1[7:0] bit 0</li> </ul> </li> </ol> |

| P1_1      | B1  | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 1</li> <li>STV YUV[9:0] bit 3</li> <li>HDTV Y[9:0] bit 3</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 1</li> <li>program stream data of PS1[7:0] bit 1</li> </ul> </li> </ol> |

| P1_2      | B2  | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 2</li> <li>STV YUV[9:0] bit 4</li> <li>HDTV Y[9:0] bit 4</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 2</li> <li>program stream data of PS1[7:0] bit 2</li> </ul> </li> </ol> |

| P1_3      | B3  | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 3</li> <li>STV YUV[9:0] bit 5</li> <li>HDTV Y[9:0] bit 5</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 3</li> <li>program stream data of PS1[7:0] bit 3</li> </ul> </li> </ol> |

**SAA7160 NXP Semiconductors**

Table 2. Description of functional pins ... continued

| Table 2. | Description of functional pinscontinued |                     |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------|-----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol   | Pin                                     | Type <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| P1_4     | A1                                      | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV Y[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 4</li> <li>program stream data of PS1[7:0] bit 4</li> </ul> </li> </ol> |  |  |  |

| P1_5     | A2                                      | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV Y[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 5</li> <li>program stream data of PS1[7:0] bit 5</li> </ul> </li> </ol> |  |  |  |

| P1_6     | A3                                      | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV Y[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 6</li> <li>program stream data of PS1[7:0] bit 6</li> </ul> </li> </ol> |  |  |  |

| P1_7     | A4                                      | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV Y[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS1[7:0] bit 7</li> <li>program stream data of PS1[7:0] bit 7</li> </ul> </li> </ol> |  |  |  |

| P1_CLK   | A5                                      | ID                  | <ol> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream clock of TS1</li> <li>program stream clock of PS1</li> </ul> </li> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for         <ul> <li>clock signal of parallel video data</li> </ul> </li> </ol>                                                                                     |  |  |  |

| P1_HS    | B4                                      | ID                  | <ul> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> <li>horizontal synchronization reference in 8-bit STV mode</li> <li>parallel video data mode STV YUV[9:0] bit 0</li> <li>parallel video data mode HDTV Y[9:0] bit 0</li> </ul>                                                                                                                                            |  |  |  |

| P1_2_HS  | J12                                     | ID                  | horizontal synchronization reference for HD stream from video port 1 and port 2                                                                                                                                                                                                                                                                                                             |  |  |  |

| P1_2_VS  | H13                                     | ID                  | vertical synchronization reference for HD stream from video port 1 and port 2                                                                                                                                                                                                                                                                                                               |  |  |  |

| P1_2_FR  | ≣ J14                                   | ID                  | field indication reference for HD stream from video port 1 and port 2                                                                                                                                                                                                                                                                                                                       |  |  |  |

Table 2.

Description of functional pins ...continued

| Symbol    | Pin | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1_VS_SOP | C4  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> <li>parallel video data mode STV YUV[9:0] bit 1</li> <li>parallel video data mode HDTV Y[9:0] bit 1</li> <li>vertical synchronization reference in 8-bit STV mode</li> </ol>                                                                                                                                               |

|           |     |         | <ul> <li>2. digital input signal 'start of package' of FGPI_2 or FGPI_3 for parallel</li> <li>program stream data of PS1</li> <li>transport stream data of TS1</li> </ul>                                                                                                                                                                                                                    |

| P1_VAL    | F14 | ID      | digital input control signal 'valid data' of FGPI_2 or FGPI_3 for parallel  transport stream data of TS1  program stream data of PS1  If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.                                                                                                                                                                      |

| P2_0      | F3  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 0</li> <li>STV YUV[9:0] bit 2</li> <li>HDTV UV[9:0] bit 2</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 0</li> <li>program stream data of PS2[7:0] bit 0</li> </ul> </li> </ol> |

| P2_1      | F2  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 1</li> <li>STV YUV[9:0] bit 3</li> <li>HDTV UV[9:0] bit 3</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 1</li> <li>program stream data of PS2[7:0] bit 1</li> </ul> </li> </ol> |

| P2_2      | F1  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 2</li> <li>STV YUV[9:0] bit 4</li> <li>HDTV UV[9:0] bit 4</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 2</li> <li>program stream data of PS2[7:0] bit 2</li> </ul> </li> </ol> |

| P2_3      | E3  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 3</li> <li>STV YUV[9:0] bit 5</li> <li>HDTV UV[9:0] bit 5</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 3</li> <li>program stream data of PS2[7:0] bit 3</li> </ul> </li> </ol> |

Table 2.

Description of functional pins ...continued

| Table 2. | Description of functional pinscontinued |         |                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------|-----------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol   | Pin                                     | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| P2_4     | E2                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV UV[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 4</li> <li>program stream data of PS2[7:0] bit 4</li> </ul> </li> </ol> |  |  |  |  |

| P2_5     | E1                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV UV[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 5</li> <li>program stream data of PS2[7:0] bit 5</li> </ul> </li> </ol> |  |  |  |  |

| P2_6     | D3                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV UV[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 6</li> <li>program stream data of PS2[7:0] bit 6</li> </ul> </li> </ol> |  |  |  |  |

| P2_7     | D2                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV UV[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS2[7:0] bit 7</li> <li>program stream data of PS2[7:0] bit 7</li> </ul> </li> </ol> |  |  |  |  |

| P2_CLK   | D1                                      | ID      | <ol> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream clock of TS2</li> <li>program stream clock of PS2</li> </ul> </li> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for clock signal of parallel video data</li> </ol>                                                                                                                   |  |  |  |  |

| P2_HS    | C1                                      | ID      | <ul> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> <li>horizontal synchronization of digital video port</li> <li>parallel video data mode STV YUV[9:0] bit 0</li> <li>parallel video data mode HDTV UV[9:0] bit 0</li> </ul>                                                                                                                                                  |  |  |  |  |

Table 2.

Description of functional pins ...continued

| Symbol    | Pin | Type[1] | Description                                                                                       |

|-----------|-----|---------|---------------------------------------------------------------------------------------------------|

| P2_VS_SOP | C2  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> </ol>                           |

|           |     |         | <ul> <li>parallel video data mode STV YUV[9:0] bit 1</li> </ul>                                   |

|           |     |         | <ul> <li>parallel video data mode HDTV UV[9:0] bit 1</li> </ul>                                   |

|           |     |         | <ul> <li>vertical synchronization reference in 8-bit STV mode</li> </ul>                          |

|           |     |         | <ol><li>digital input signal 'start of package' of FGPI_2 or FGPI_3 for parallel</li></ol>        |

|           |     |         | <ul> <li>transport stream data of TS2</li> </ul>                                                  |

|           |     |         | <ul> <li>program stream data of PS2</li> </ul>                                                    |

| P2_VAL    | F13 | ID      | digital input control signal 'valid data' of FGPI_2 or FGPI_3 for parallel                        |

|           |     |         | transport stream data of TS2                                                                      |

|           |     |         | <ul> <li>program stream data of PS2</li> </ul>                                                    |

|           |     |         | If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.                 |

| P3_0      | M1  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes</li> </ol> |

|           |     |         | <ul><li>STV YUV[7:0] bit 0</li></ul>                                                              |

|           |     |         | <ul><li>STV YUV[9:0] bit 2</li></ul>                                                              |

|           |     |         | <ul><li>HDTV UV[9:0] bit 2</li></ul>                                                              |

|           |     |         | <ol><li>digital input signal of FGPI_2 or FGPI_3 for parallel</li></ol>                           |

|           |     |         | <ul> <li>transport stream data of TS3[7:0] bit 0</li> </ul>                                       |

|           |     |         | <ul><li>program stream data of PS3[7:0] bit 0</li></ul>                                           |

| P3_1      | L3  | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes</li> </ol> |

|           |     |         | <ul><li>STV YUV[7:0] bit 1</li></ul>                                                              |

|           |     |         | <ul><li>STV YUV[9:0] bit 3</li></ul>                                                              |

|           |     |         | <ul><li>HDTV UV[9:0] bit 3</li></ul>                                                              |

|           |     |         | <ol><li>digital input signal of FGPI_2 or FGPI_3 for parallel</li></ol>                           |

|           |     |         | <ul> <li>transport stream data of TS3[7:0] bit 1</li> </ul>                                       |

|           |     |         | <ul> <li>program stream data of PS3[7:0] bit 1</li> </ul>                                         |

| P3_2      | L2  | ID      | 1. digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes                  |

|           |     |         | <ul><li>STV YUV[7:0] bit 2</li></ul>                                                              |

|           |     |         | <ul><li>STV YUV[9:0] bit 4</li></ul>                                                              |

|           |     |         | <ul><li>HDTV UV[9:0] bit 4</li></ul>                                                              |

|           |     |         | <ol><li>digital input signal of FGPI_2 or FGPI_3 for parallel</li></ol>                           |

|           |     |         | <ul> <li>transport stream data of TS3[7:0] bit 2</li> </ul>                                       |

|           |     |         | <ul><li>program stream data of PS3[7:0] bit 2</li></ul>                                           |

| P3_3      | L1  | ID      | 1. digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes                  |

|           |     |         | - STV YUV[7:0] bit 3                                                                              |

|           |     |         | - STV YUV[9:0] bit 5                                                                              |

|           |     |         | - HDTV UV[9:0] bit 5                                                                              |

|           |     |         | 2. digital input signal of FGPI_2 or FGPI_3 for parallel                                          |

|           |     |         | - transport stream data of TS3[7:0] bit 3                                                         |

|           |     |         | <ul><li>program stream data of PS3[7:0] bit 3</li></ul>                                           |

Table 2.

Description of functional pins ...continued

| Table 2. | Description of functional pinscontinued |         |                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------|-----------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol   | Pin                                     | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| P3_4     | КЗ                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV UV[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS3[7:0] bit 4</li> <li>program stream data of PS3[7:0] bit 4</li> </ul> </li> </ol> |  |  |  |  |

| P3_5     | K2                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV UV[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS3[7:0] bit 5</li> <li>program stream data of PS3[7:0] bit 5</li> </ul> </li> </ol> |  |  |  |  |

| P3_6     | K1                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV UV[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS3[7:0] bit 6</li> <li>program stream data of PS3[7:0] bit 6</li> </ul> </li> </ol> |  |  |  |  |

| P3_7     | J3                                      | ID      | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV UV[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream data of TS3[7:0] bit 7</li> <li>program stream data of PS3[7:0] bit 7</li> </ul> </li> </ol> |  |  |  |  |

| P3_CLK   | J2                                      | ID      | <ol> <li>digital input signal of FGPI_2 or FGPI_3 for parallel         <ul> <li>transport stream clock of TS3</li> <li>program stream clock of PS3</li> </ul> </li> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for         <ul> <li>clock signal of parallel video data</li> </ul> </li> </ol>                                                                                      |  |  |  |  |

| P3_HS    | J1                                      | ID      | <ul> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> <li>parallel video data mode STV YUV[9:0] bit 0</li> <li>parallel video data mode HDTV UV[9:0] bit 0</li> <li>horizontal synchronization reference in 8-bit STV mode</li> </ul>                                                                                                                                            |  |  |  |  |

Table 2.

Description of functional pins ...continued

| Symbol    | Pin | Type <sup>[1]</sup> | Description                                                                                |

|-----------|-----|---------------------|--------------------------------------------------------------------------------------------|

| P3_VS_SOP | H2  | ID                  | <ol> <li>digital input signal of VIP_1, FGPI_2 or FGPI_3 for</li> </ol>                    |

|           |     |                     | <ul> <li>parallel video data mode STV YUV[9:0] bit 1</li> </ul>                            |

|           |     |                     | <ul> <li>parallel video data mode HDTV UV[9:0] bit 1</li> </ul>                            |

|           |     |                     | <ul> <li>vertical synchronization reference in 8-bit STV mode</li> </ul>                   |

|           |     |                     | <ol><li>digital input signal 'start of package' of FGPI_2 or FGPI_3 for parallel</li></ol> |

|           |     |                     | <ul> <li>transport stream data of TS3</li> </ul>                                           |

|           |     |                     | <ul> <li>program stream data of PS3</li> </ul>                                             |

| P3_VAL    | H1  | ID                  | digital input control signal 'valid data' of FGPI_2 or FGPI_3 for parallel                 |

|           |     |                     | <ul> <li>transport stream data of TS3</li> </ul>                                           |

|           |     |                     | <ul> <li>program stream data of PS3</li> </ul>                                             |

|           |     |                     | If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.          |

| P4_0      | A12 | ID                  | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes           |

|           |     |                     | <ul><li>STV YUV[7:0] bit 0</li></ul>                                                       |

|           |     |                     | - STV YUV[9:0] bit 2                                                                       |

|           |     |                     | <ul><li>HDTV Y[9:0] bit 2</li></ul>                                                        |

|           |     |                     | <ol><li>digital input signal of FGPI_0 or FGPI_1 for parallel</li></ol>                    |

|           |     |                     | <ul> <li>transport stream data of TS4[7:0] bit 0</li> </ul>                                |

|           |     |                     | <ul> <li>program stream data of PS4[7:0] bit 0</li> </ul>                                  |

| P4_1      | A11 | ID                  | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes           |

|           |     |                     | <ul><li>STV YUV[7:0] bit 1</li></ul>                                                       |

|           |     |                     | - STV YUV[9:0] bit 3                                                                       |

|           |     |                     | <ul><li>HDTV Y[9:0] bit 3</li></ul>                                                        |

|           |     |                     | <ol><li>digital input signal of FGPI_0 or FGPI_1 for parallel</li></ol>                    |

|           |     |                     | <ul> <li>transport stream data of TS4[7:0] bit 1</li> </ul>                                |

|           |     |                     | <ul> <li>program stream data of PS4[7:0] bit 1</li> </ul>                                  |

| P4_2      | B12 | ID                  | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes           |

|           |     |                     | <ul><li>STV YUV[7:0] bit 2</li></ul>                                                       |

|           |     |                     | - STV YUV[9:0] bit 4                                                                       |

|           |     |                     | <ul><li>HDTV Y[9:0] bit 4</li></ul>                                                        |

|           |     |                     | <ol><li>digital input signal of FGPI_0 or FGPI_1 for parallel</li></ol>                    |

|           |     |                     | <ul> <li>transport stream data of TS4[7:0] bit 2</li> </ul>                                |

|           |     |                     | <ul><li>program stream data of PS4[7:0] bit 2</li></ul>                                    |

| P4_3      | C11 | ID                  | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes           |

|           |     |                     | - STV YUV[7:0] bit 3                                                                       |

|           |     |                     | - STV YUV[9:0] bit 5                                                                       |

|           |     |                     | - HDTV Y[9:0] bit 5                                                                        |

|           |     |                     | 2. digital input signal of FGPI_0 or FGPI_1 for parallel                                   |

|           |     |                     | <ul> <li>transport stream data of TS4[7:0] bit 3</li> </ul>                                |

|           |     |                     |                                                                                            |

Table 2.

Description of functional pins ...continued

| Table 2. | Description of functional pinscontinued |                     |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------|-----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol   | Pin                                     | Type <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| P4_4     | A8                                      | ID                  | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV Y[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS4[7:0] bit 4</li> <li>program stream data of PS4[7:0] bit 4</li> </ul> </li> </ol> |  |  |  |

| P4_5     | B8                                      | ID                  | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV Y[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS4[7:0] bit 5</li> <li>program stream data of PS4[7:0] bit 5</li> </ul> </li> </ol> |  |  |  |

| P4_6     | B10                                     | ID                  | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV Y[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS4[7:0] bit 6</li> <li>program stream data of PS4[7:0] bit 6</li> </ul> </li> </ol> |  |  |  |

| P4_7     | В7                                      | ID                  | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV Y[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS4[7:0] bit 7</li> <li>program stream data of PS4[7:0] bit 7</li> </ul> </li> </ol> |  |  |  |

| P4_CLK   | A7                                      | ID                  | <ol> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream clock of TS4</li> <li>program stream clock of PS4</li> </ul> </li> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for         <ul> <li>clock signal of parallel video data</li> </ul> </li> </ol>                                                                                     |  |  |  |

| P4_HS    | В6                                      | ID                  | <ul> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for</li> <li>horizontal synchronization reference in 8-bit STV mode</li> <li>parallel video data mode STV YUV[9:0] bit 0</li> <li>parallel video data mode HDTV Y[9:0] bit 0</li> </ul>                                                                                                                                            |  |  |  |

| P4_5_HS  | K12                                     | ID                  | horizontal synchronization reference for HD stream from video port 4 and port 5                                                                                                                                                                                                                                                                                                             |  |  |  |

| P4_5_VS  | J13                                     | ID                  | vertical synchronization reference for HD stream from video port 4 and port 5                                                                                                                                                                                                                                                                                                               |  |  |  |

| P4_5_FRE | E K14                                   | ID                  | field indication reference for HD stream from video port 4 and port 5                                                                                                                                                                                                                                                                                                                       |  |  |  |

**SAA7160 NXP Semiconductors**

Table 2. **Description of functional pins** ...continued

| Symbol    | Pin                                     | Type[1] | Description                                                                                                                  |

|-----------|-----------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| P4_VS_SOP | B11                                     | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for</li> <li>parallel video data mode STV YUV[9:0] bit 1</li> </ol> |

|           |                                         |         | <ul> <li>parallel video data mode HDTV Y[9:0] bit 1</li> </ul>                                                               |

|           |                                         |         | <ul> <li>vertical synchronization reference in 8-bit STV mode</li> </ul>                                                     |

|           |                                         |         | 2. digital input signal 'start of package' of FGPI_0 or FGPI_1 for parallel                                                  |

|           |                                         |         | <ul> <li>transport stream data of TS4</li> </ul>                                                                             |

|           |                                         |         | <ul> <li>program stream data of PS4</li> </ul>                                                                               |

| P4_VAL    | F12                                     | ID      | digital input control signal 'valid data' of FGPI_0 or FGPI_1 for parallel                                                   |

|           |                                         |         | <ul> <li>transport stream data of TS4</li> </ul>                                                                             |

|           |                                         |         | <ul> <li>program stream data of PS4</li> </ul>                                                                               |

|           |                                         |         | If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.                                            |

| P5_0      | C7                                      | ID      | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes                                             |

|           |                                         |         | <ul><li>STV YUV[7:0] bit 0</li></ul>                                                                                         |

|           |                                         |         | <ul><li>STV YUV[9:0] bit 2</li></ul>                                                                                         |

|           |                                         |         | <ul><li>HDTV UV[9:0] bit 2</li></ul>                                                                                         |

|           |                                         |         | <ol><li>digital input signal of FGPI_0 or FGPI_1 for parallel</li></ol>                                                      |

|           |                                         |         | <ul> <li>transport stream data of TS5[7:0] bit 0</li> </ul>                                                                  |

|           |                                         |         | <ul><li>program stream data of PS5[7:0] bit 0</li></ul>                                                                      |

| P5_1      | C9                                      | ID      | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes                                             |

|           |                                         |         | <ul><li>STV YUV[7:0] bit 1</li></ul>                                                                                         |

|           |                                         |         | <ul><li>STV YUV[9:0] bit 3</li></ul>                                                                                         |

|           |                                         |         | <ul><li>HDTV UV[9:0] bit 3</li></ul>                                                                                         |

|           |                                         |         | <ol><li>digital input signal of FGPI_0 or FGPI_1 for parallel</li></ol>                                                      |

|           |                                         |         | <ul> <li>transport stream data of TS5[7:0] bit 1</li> </ul>                                                                  |

|           |                                         |         | <ul><li>program stream data of PS5[7:0] bit 1</li></ul>                                                                      |

| P5_2      | B5                                      | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes</li> </ol>                            |

|           |                                         |         | <ul><li>STV YUV[7:0] bit 2</li></ul>                                                                                         |

|           |                                         |         | - STV YUV[9:0] bit 4                                                                                                         |

|           |                                         |         | - HDTV UV[9:0] bit 4                                                                                                         |

|           |                                         |         | 2. digital input signal of FGPI_0 or FGPI_1 for parallel                                                                     |

|           |                                         |         | - transport stream data of TS5[7:0] bit 2                                                                                    |

| D         | • • • • • • • • • • • • • • • • • • • • |         | - program stream data of PS5[7:0] bit 2                                                                                      |

| P5_3      | A6                                      | ID      | 1. digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes                                             |

|           |                                         |         | <ul><li>STV YUV[7:0] bit 3</li><li>STV YUV[9:0] bit 5</li></ul>                                                              |

|           |                                         |         | - STV TOV[9:0] bit 5 - HDTV UV[9:0] bit 5                                                                                    |

|           |                                         |         | 2. digital input signal of FGPI_0 or FGPI_1 for parallel                                                                     |

|           |                                         |         | - transport stream data of TS5[7:0] bit 3                                                                                    |

|           |                                         |         | - program stream data of PS5[7:0] bit 3  - program stream data of PS5[7:0] bit 3                                             |

|           |                                         |         | program stream data or i oopioj bit o                                                                                        |

Table 2.

Description of functional pins ...continued

| Table 2. | Description of functional pinscontinued |         |                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|----------|-----------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol   | Pin                                     | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| P5_4     | C8                                      | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV UV[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS5[7:0] bit 4</li> <li>program stream data of PS5[7:0] bit 4</li> </ul> </li> </ol> |  |  |  |  |

| P5_5     | C5                                      | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV UV[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS5[7:0] bit 5</li> <li>program stream data of PS5[7:0] bit 5</li> </ul> </li> </ol> |  |  |  |  |

| P5_6     | C6                                      | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV UV[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS5[7:0] bit 6</li> <li>program stream data of PS5[7:0] bit 6</li> </ul> </li> </ol> |  |  |  |  |

| P5_7     | В9                                      | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV UV[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS5[7:0] bit 7</li> <li>program stream data of PS5[7:0] bit 7</li> </ul> </li> </ol> |  |  |  |  |

| P5_CLK   | А9                                      | ID      | <ol> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream clock for port TS5</li> <li>program stream clock for port PS5</li> </ul> </li> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for         <ul> <li>clock signal of parallel video data</li> </ul> </li> </ol>                                                                          |  |  |  |  |

| P5_HS    | A10                                     | ID      | digital input signal of VIP_0, FGPI_0 or FGPI_1 for  • horizontal synchronization reference in 8-bit STV mode  • parallel video data mode STV YUV[9:0] bit 0  • parallel video data mode HDTV UV[9:0] bit 0                                                                                                                                                                                  |  |  |  |  |

Table 2.

Description of functional pins ...continued

| Symbol   |    | Pin | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5_VS_S0 | OP | C10 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for         <ul> <li>parallel video data mode STV YUV[9:0] bit 1</li> <li>parallel video data mode HDTV UV[9:0] bit 1</li> <li>vertical synchronization reference in 8-bit STV mode</li> </ul> </li> <li>digital input signal 'start of package' of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS5</li> <li>program stream data of PS5</li> </ul> </li> </ol> |

| P5_VAL   |    | E12 | ID      | digital input control signal 'valid data' of FGPI_0 or FGPI_1 for parallel  transport stream data of TS5  program stream data of PS5  If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.                                                                                                                                                                                                                             |

| P6_0     |    | C12 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 0</li> <li>STV YUV[9:0] bit 2</li> <li>HDTV UV[9:0] bit 2</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 0</li> <li>program stream data of PS6[7:0] bit 0</li> </ul> </li> </ol>                                                        |

| P6_1     |    | C13 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 1</li> <li>STV YUV[9:0] bit 3</li> <li>HDTV UV[9:0] bit 3</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 1</li> <li>program stream data of PS6[7:0] bit 1</li> </ul> </li> </ol>                                                        |

| P6_2     |    | C14 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 2</li> <li>STV YUV[9:0] bit 4</li> <li>HDTV UV[9:0] bit 4</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 2</li> <li>program stream data of PS6[7:0] bit 2</li> </ul> </li> </ol>                                                        |

| P6_3     |    | D12 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 3</li> <li>STV YUV[9:0] bit 5</li> <li>HDTV UV[9:0] bit 5</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 3</li> <li>program stream data of PS6[7:0] bit 3</li> </ul> </li> </ol>                                                        |

Table 2.

Description of functional pins ...continued

| Symbol | Pin | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6_4   | D13 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 4</li> <li>STV YUV[9:0] bit 6</li> <li>HDTV UV[9:0] bit 6</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 4</li> <li>program stream data of PS6[7:0] bit 4</li> </ul> </li> </ol> |

| P6_5   | D14 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 5</li> <li>STV YUV[9:0] bit 7</li> <li>HDTV UV[9:0] bit 7</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 5</li> <li>program stream data of PS6[7:0] bit 5</li> </ul> </li> </ol> |

| P6_6   | E13 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 6</li> <li>STV YUV[9:0] bit 8</li> <li>HDTV UV[9:0] bit 8</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 6</li> <li>program stream data of PS6[7:0] bit 6</li> </ul> </li> </ol> |

| P6_7   | E14 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for parallel video data modes         <ul> <li>STV YUV[7:0] bit 7</li> <li>STV YUV[9:0] bit 9</li> <li>HDTV UV[9:0] bit 9</li> </ul> </li> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6[7:0] bit 7</li> <li>program stream data of PS6[7:0] bit 7</li> </ul> </li> </ol> |

| P6_CLK | B14 | ID      | <ol> <li>digital input signal of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream clock of TS6</li> <li>program stream clock of PS6</li> </ul> </li> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for         <ul> <li>clock signal for parallel video data modes</li> </ul> </li> </ol>                                                                               |

| P6_HS  | A14 | ID      | digital input signal of VIP_0, FGPI_0 or FGPI_1 for  • parallel video data mode STV YUV[9:0] bit 0  • parallel video data mode HDTV UV[9:0] bit 0  • horizontal synchronization reference in 8-bit STV mode                                                                                                                                                                                  |

Table 2.

Description of functional pins ...continued

| Symbol   |    | Pin | Type[1] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6_VS_S0 | ϽP | A13 | ID      | <ol> <li>digital input signal of VIP_0, FGPI_0 or FGPI_1 for         <ul> <li>parallel video data mode STV YUV[9:0] bit 1</li> <li>parallel video data mode HDTV UV[9:0] bit 1</li> <li>vertical synchronization reference in 8-bit STV mode</li> </ul> </li> <li>digital input signal 'start of package' of FGPI_0 or FGPI_1 for parallel         <ul> <li>transport stream data of TS6</li> <li>program stream data of PS6</li> </ul> </li> </ol> |

| P6_VAL   |    | B13 | ID      | digital input control signal 'valid data' of FGPI_0 or FGPI_1 for parallel  transport stream data of TS6  program stream data of PS6  If this pin is unused it is necessary to connect the pin to 3.3 V supply voltage.                                                                                                                                                                                                                             |

| GPIO_0   |    | L4  | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 0</li> <li>external interrupt 0; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_1   |    | M5  | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 1</li> <li>external interrupt 1; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_2   |    | L14 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 2</li> <li>external interrupt 2; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_3   |    | K13 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 3</li> <li>external interrupt 3; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_4   |    | M14 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 4</li> <li>external interrupt 4; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_5   |    | L13 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 5</li> <li>external interrupt 5; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_6   |    | K10 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 6</li> <li>external interrupt 6; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_7   |    | N14 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 7</li> <li>external interrupt 7; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |

| GPIO_8   |    | P14 | IOU     | <ul> <li>GPIO: programming control port signal for</li> <li>general purpose input/output port 8</li> <li>external interrupt 8; interrupt edge sensitive with programmable edge polarity</li> </ul>                                                                                                                                                                                                                                                  |