## **SIEMENS**

# Data / Address Buffer SAB 82C215 of Siemens PC-AT<sup>TM</sup> Chipset

#### **Advance Information**

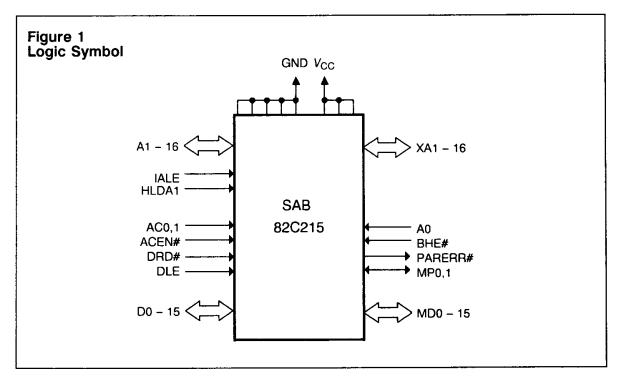

- Address buffer and latch for local CPUand X-address bus interface

- Data buffer and latch for local CPU data bus / memory data bus interface

- Bus conversion logic for 16-bit to 8-bit transfers

- Parity generation / detection logic for memory data bus

- CMOS implementation for high speed and low power requirements

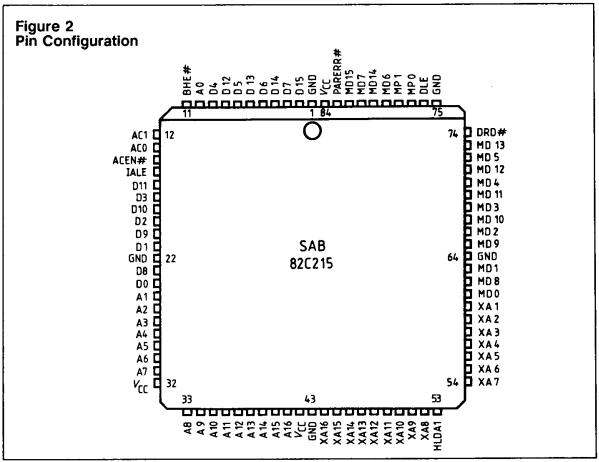

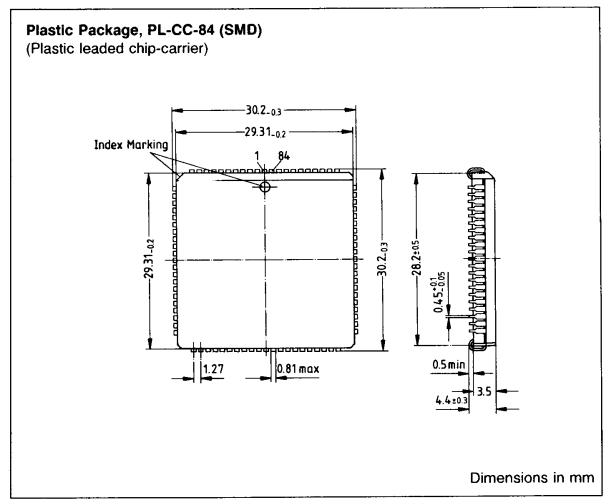

- 84-pin plastic leaded chip carrier package (PL-CC-84)

1 2.90

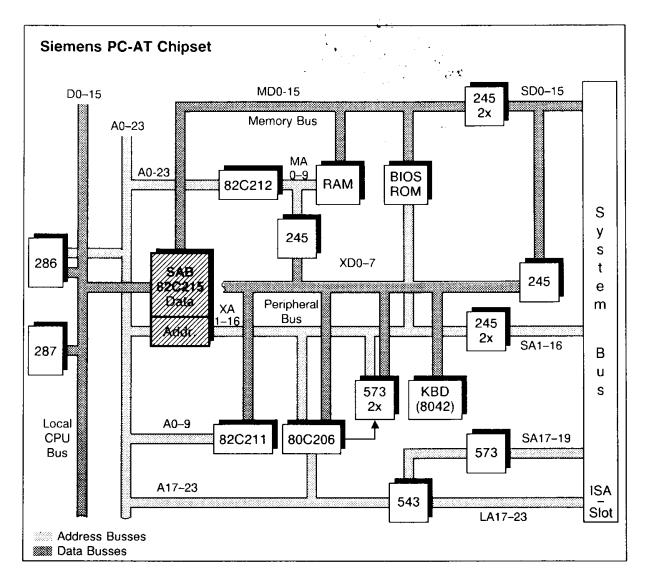

As a member of the Siemens PC-AT Chipset the SAB 82C215 provides address buffer / latch, data bus buffer / latch, data bus path conversion logic and parity logic.

The SAB 82C215 data / address buffer, the SAB 82C211 system controller, the SAB 82C212 memory controller and the SAB 82C206 integrated peripheral controller provide a highly integrated high performance system solution for PC-AT compatible systems.

The SAB 82C215 is fabricated in Siemens ACMOS technology and packaged in a 84-pin plastic leaded chip carrier package (PL-CC-84).

## **Ordering Information**

| Туре            | Ordering code | Package        | Description                                                   |

|-----------------|---------------|----------------|---------------------------------------------------------------|

| SAB 82C215-12-N | Q67120-P297   | PL-CC-84 (SMD) | Data / Address Buffer<br>of Siemens PC-AT<br>Chipset (12 MHz) |

| SAB 82C215-16-N | Q67120-P298   | PL-CC-84 (SMD) | Data / Address Buffer of Siemens PC-AT Chipset (16 MHz)       |

## Pin Definitions and Functions

| Symbol       | Pin                  | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                      |

|--------------|----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Late | ch / Buffers         |                         |                                                                                                                                                                                                                               |

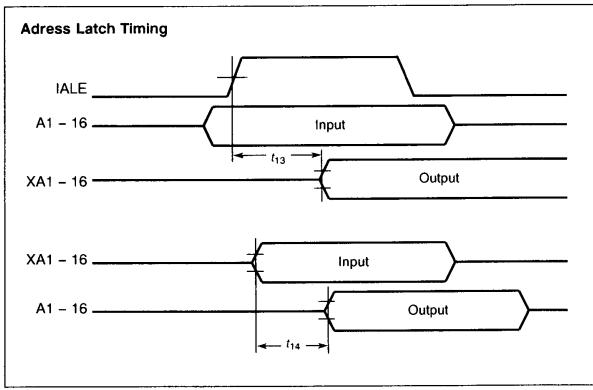

| IALE         | 15                   | I                       | Address Latch Enable IALE is the strobe input line of the address latch. It is used to latch the CPU addresses onto the X-address lines.                                                                                      |

| A1 – A16     | 25 – 31<br>33 – 411) | I/O                     | CPU Address Lines 1 – 16  During CPU cycles (HLDA1 = 0) A1 – A16 are the inputs to the internal address latch of the SAB 82C215. During DMA cycles (HLDA1 = 1) A1 – A16 are outputs. The address latch is controlled by IALE. |

| XA1 – XA16   | 60 - 54<br>52 - 441) | I/O                     | XBUS Address Lines 1 – 16 During CPU cycles (HLDA1 = 0) XA1 – 16 are the outputs of the address latch. During DMA cycles (HLDA1 = 1) XA1 – 16 are inputs.                                                                     |

| HLDA1        | 53                   |                         | Hold Acknowledge HLDA1 indicates the type of cycle currently executing. CPU cycles are executed with HLDA1 = 0. During DMA cycles HLDA1 = 1. HLDA1 controls the direction of the address and data bus transfers.              |

#### Data Buffers / Latch

| D0 – D15 | 24, 23<br>21 - 16<br>9 - 21) | I/O | CPU Data Bus Lines 0 – 15  D0 – D15 represent the local CPU data bus lines.  The data bus buffers are controlled by HLDA1 and DRD#.                                                                                     |

|----------|------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

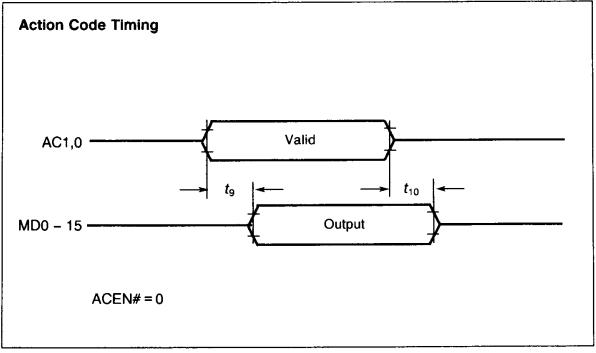

| AC0,1    | 13, 12                       |     | Action Code Line 0, 1 The two action code lines control the data path during CPU and DMA cycles. AC0,1 are qualified (enabled) by the ACEN# signal. At the Siemens PC-AT chipset AC0,1 are generated by the SAB 82C211. |

<sup>1)</sup> For detailed pin numbers see also pin configuration (figure 2).

## Pin Definitions and Functions (cont'd)

Input (I)

Pin

Symbol

|              |                                 | Output (O) |                                                                                                                                                                                              |

|--------------|---------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Buffers | / Latch                         |            |                                                                                                                                                                                              |

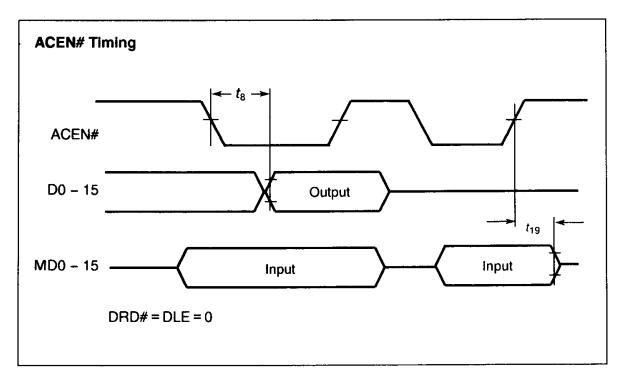

| ACEN#        | 14                              |            | Action Code Enable#  ACEN# = 0 validates the action code signals  AC0,1.                                                                                                                     |

| MD0 – MD15   | 61 – 63<br>65 – 73<br>79 – 821) | I/O        | Memory Data Bus 0 - 15 MD0 - MD15 are the memory data bus lines. They are controlled by HLDA1, DRD#, AC1,0 and ACEN#.                                                                        |

| DRD#         | 74                              | I          | Data Read#  DRD# controls the direction of the data bus buffer path. DRD# = 1 sets the data path from local CPU bus to memory bus. DRD# = 0 sets the data path from memory to local CPU bus. |

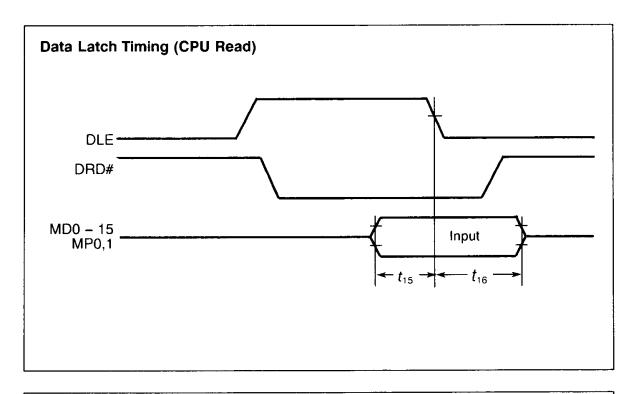

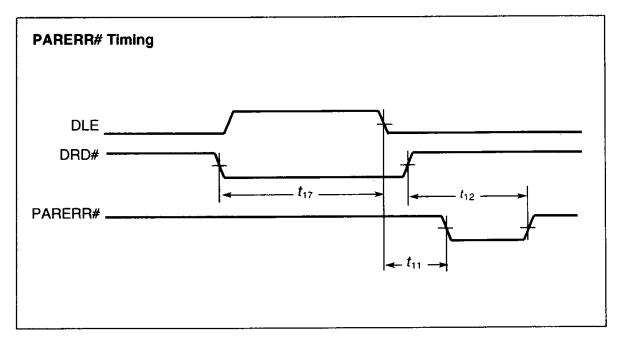

| DLE          | 76                              | 1          | Data Latch Enable  DLE controls the data bus latch. Memory bus data is stored in the latch with the high-to-low transition of DLE.                                                           |

**Function**

## Parity Generator / Checker

| A0       | 10     | 1   | Address Line 0 A0 is used to enable the low byte parity checking.                                                                                                                                                                                                  |

|----------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BHE#     | 11     | I   | Byte High Enable# BHE# is used to enable the high byte parity checking.                                                                                                                                                                                            |

| MP1, MP0 | 78, 77 | I/O | Memory Parity Bit 1,0 MP1 and MP0 are the parity bits for the high and low order bytes of the system DRAM's. These lines are inputs during memory read operations for parity error detection and are outputs during memory write operations for parity generation. |

| PARERR#  | 83     | 0   | Parity Error# PARERR# = 0 indicates that a parity error has been detected during a system memory read operation. At the Siemens PC-AT chipset PARERR# is checked by the SAB 82C211 system controller.                                                              |

<sup>1)</sup> For detailed pin numbers see also pin configuration (figure 2).

## Pin Definitions and Functions (cont'd)

| Symbol    | Pin | Input (I)<br>Output (O) | Function |

|-----------|-----|-------------------------|----------|

| Power Sup | ply |                         |          |

| V <sub>CC</sub> | 32, 42,<br>84           | - | Power Supply (+5 V) |

|-----------------|-------------------------|---|---------------------|

| GND             | 1, 22,<br>43, 64,<br>75 | - | Ground (0 V)        |

#### **Functional Description**

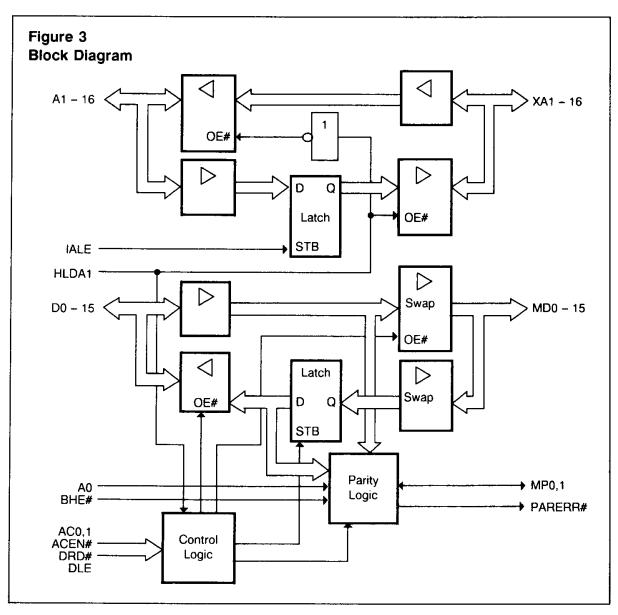

The SAB 82C215 data / address buffer for the SIEMENS PC-AT chipset provides the following functional units:

- Address buffer and latch

- Data buffer and latch

- Data bus conversion logic

- Parity generation / detection logic

#### Address Buffer and Latch

For local CPU cycles (HLDA1 = 0) the SAB 82C215 provides the address buffering and latching between the CPU address lines A1 – A16 and the peripheral bus address lines XA1 – XA16. A1 – A16 can be latched by the address latch enable signal IALE. The latch is transparent with IALE = high.

During DMA cycles (HLDA1 = 1) the peripheral address bus XA1 – XA16 is routed to the A1 – A16 address bus lines. The address latch is not available during DMA cycles.

#### **Data Buffer and Latch**

The SAB 82C215 provides the buffering between the CPU data bus D0 – D15 and the memory data bus MD0 – MD15 for local cycles (on-board memory read / write cycles) or AT-bus cycles (on-board peripherals or AT-slot read / write cycles).

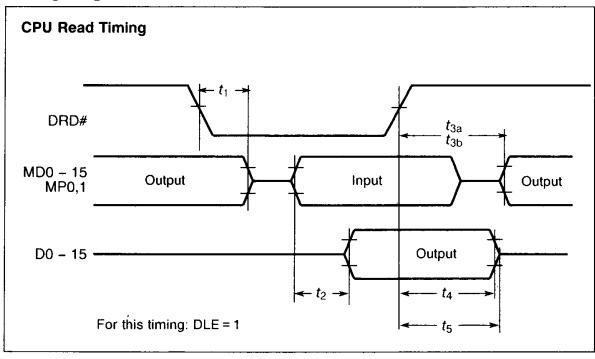

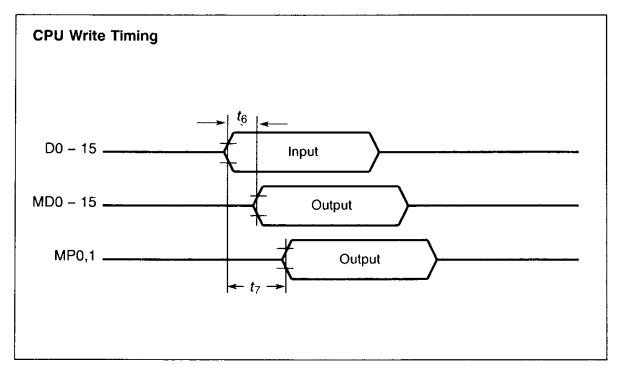

DRD# is the direction control signal for the data buffer. For local write cycles DRD# is at high level and sets the data path from the CPU data bus to the memory data bus. For local read cycles DRD# = 0 sets the data path from MD-bus to D-bus. DLE controls the data latch. DLE = 1 makes the latch transparent. During local cycles the action code enable signal is inactive (ACEN# = 1).

During AT-bus cycles DLE is inactive (low), and instead of DLE the ACEN# signal is used to strobe the data into the data latch. With ACEN# = 0 the data latch is transparent and data is stored with the low-to-high transition of ACEN#.

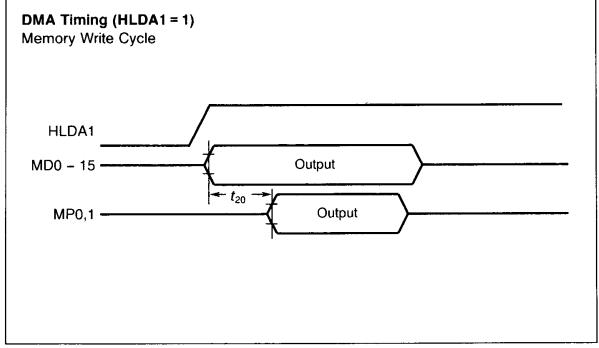

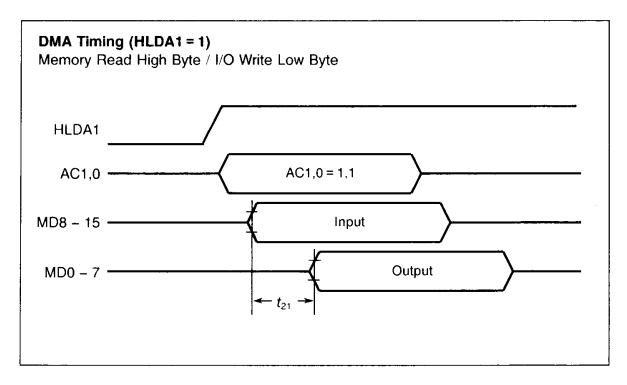

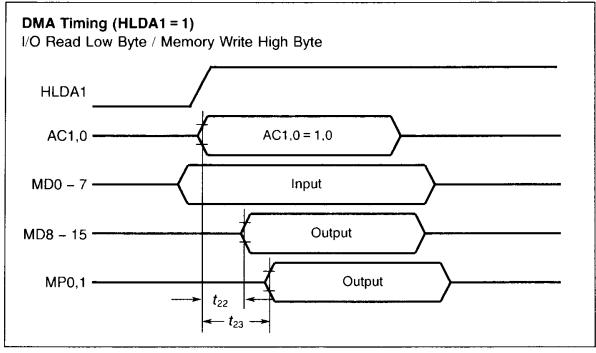

During DMA cycles the D-bus of the SAB 82C215 is switched off. During DMA memory write operations (AC1,0 = 0,0 and 1,0), the MD-bus lines are connected to the parity generator. If data bus conversion is required during DMA cycles (AC1,0 = 1,0 and 1,1), the corresponding data path is set between MD0 - 7 and MD8 - 15.

#### **Data Bus Conversion Logic**

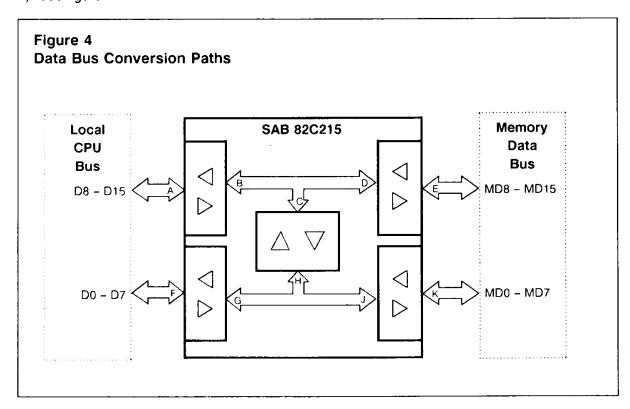

The SAB 82C215 provides data bus conversion when the 16-bit CPU reads from or writes to 8-bit devices. It also provides data bus conversion for DMA cycles. Table 1 lists the possible cases of the data paths for CPU and DMA cycles. The action code signals AC1, 0, which are qualified by ACEN#, control the different data path configurations.

Table 1: Action Code Functions

| AC1 | AC0 | HLDA1 | Operation                                                                  | Data path 1)           |

|-----|-----|-------|----------------------------------------------------------------------------|------------------------|

| 0   | 0   | 0     | 16-bit Write                                                               | A-B-D-E and<br>F-G-J-K |

|     |     |       | 8-bit Low Write                                                            | F-G-J-K                |

| 0   | 1   | 0     | 16-bit Read                                                                | E-D-B-A and<br>K-J-G-F |

|     |     |       | 8-bit Low Read                                                             | K-J-G-F                |

| 1   | 0   | 0     | 8-bit High Write to MD-bus low                                             | A-B-C-H-J-K            |

| 1   | 1   | 0     | 8-bit Read MD-bus Low to D-bus high                                        | K-J-H-C-B-A            |

| 0   | 0   | 1     | MD-bus tristated:<br>16-bit/8-bit (low byte) DMA read / write at<br>MD-bus | _                      |

| 0   | 1   | 1     | reserved                                                                   | _                      |

| 1   | 0   | 1     | High memory Write to MD8 – 15 from MD0 – 7                                 | K-J-H-C-D-E            |

| 1   | 1   | 1     | High memory Read from MD8 – 15 to MD0 – 7                                  | E-D-C-H-J-K            |

## 1) see figure 4

#### Parity Generation / Detection Logic

For local memory write cycles the SAB 82C215 generates an even parity bit (MP0, MP1) for each of the two data bytes MD0 – 7 and MD8 – 15. The parity bit is set if the corresponding data byte has an even number of 1's. During local memory read cycles the SAB 82C215 checks the data bytes for even parity. If a parity error is detected, the PARERR# output becomes active (low). PARERR# is activated by the falling edge of DLE and deactivated by the rising edge of DRD#. For DMA cycles (HLDA1 = 1) the parity checker is disabled. During parity checking A0 and BHE# select the data bytes to be checked.

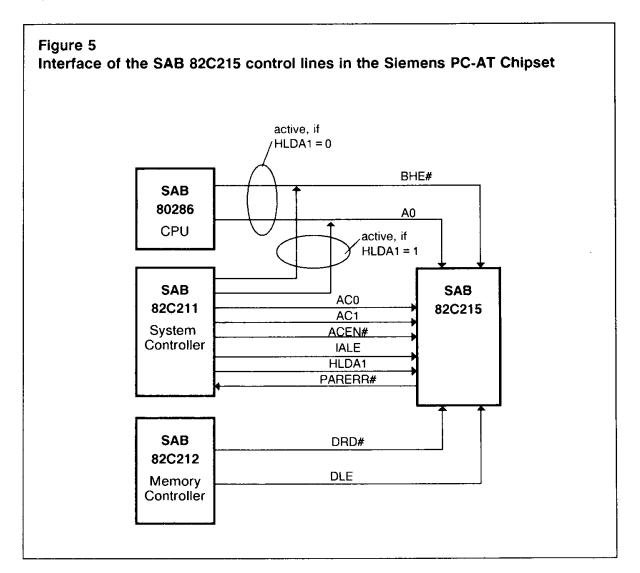

#### SAB 82C215 control lines interface

The SAB 82C215 has several control lines. In a PC-AT design using the Siemens PC-AT chipset the interface of the SAB 82C215 control lines is shown in the next figure.

## **Absolute Maximum Ratings**

| Ambient temperature under bias                                         | °C  |

|------------------------------------------------------------------------|-----|

| Storage temperature 65 to +150                                         | °C  |

| Supply voltage 0.5 to +7.5                                             | 5 V |

| Voltage on any pin with respect to ground 0.5 to V <sub>CC</sub> + 0.5 | 5 V |

| Power dissipation                                                      | W   |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **DC Characteristics**

$T_A = 0$  to 70 °C;  $V_{CC} = +5 \text{ V} \pm 5 \text{ %}$ ; GND = 0 V

| Parameter                       | Symbol            | Limit | values                   | Unit | Test                                                               |  |

|---------------------------------|-------------------|-------|--------------------------|------|--------------------------------------------------------------------|--|

|                                 |                   | min.  | max.                     |      | condition                                                          |  |

| Input low voltage               | V <sub>IL</sub>   | - 0.5 | 0.8                      | V    | -                                                                  |  |

| Input high voltage              | V <sub>IH</sub>   | 2.0   | V <sub>CC</sub><br>+ 0.5 | ٧    | -                                                                  |  |

| Output low voltage              | V <sub>OL</sub>   | _     | 0.45                     | V    | MD0 – 15: $I_{OL}$ = 8 mA<br>other outputs:<br>$I_{OL}$ = 4 mA     |  |

| Output high voltage             | V <sub>OH</sub>   | 2.4   | -                        | V    | MD0 - 15: $I_{OH}$ = - 8 mA<br>other outputs:<br>$I_{OH}$ = - 4 mA |  |

| Input leakage current           | $I_{ m IL}$       | _     | ± 10                     | μА   | 0 V < V <sub>IN</sub> < V <sub>CC</sub>                            |  |

| Output tristate leakage current | I <sub>OZ</sub>   | _     | ± 10                     | μА   | 0.45 V < V <sub>OUT</sub> < V <sub>CC</sub>                        |  |

| Power supply current            | $I_{\rm CC}$      | _     | 80                       | mA   | @16 MHz                                                            |  |

| Standby power supply current    | I <sub>CCSB</sub> | -     | 1.0                      | mA   | _                                                                  |  |

**AC Characteristics**

$T_A = 0$  to 70 °C;  $V_{CC} = +5 \text{ V} \pm 5 \text{ %}$ ; GND = 0 V

| Parameter                                                                     | Symbol                | Limit v | /alues   | Unit     | Test condition |  |

|-------------------------------------------------------------------------------|-----------------------|---------|----------|----------|----------------|--|

|                                                                               |                       | min.    | max.     |          |                |  |

| MD-bus tristated after DRD# active                                            | <i>t</i> <sub>1</sub> | 7.5     | 24       | ns       | -              |  |

| MD-bus valid to D-bus valid                                                   | $t_2$                 | 8       | 18.5     | ns       | _              |  |

| MD-bus being driven after DRD# inactive                                       | t <sub>3a</sub>       | 7.5     | 28       | ns       | -              |  |

| MP0, MP1 being driven after DRD# inactive                                     | t <sub>3b</sub>       | 6       | 23       | ns       | -              |  |

| D-bus invalid after DRD# inactive                                             | t <sub>4</sub>        | 4       | 13       | ns       | -              |  |

| D-bus tristated after DRD# inactive                                           | t <sub>5</sub>        | 6       | 15       | ns       |                |  |

| D-bus valid to MD-bus valid                                                   | t <sub>6</sub>        | 11      | 19       | ns       | -              |  |

| D-bus valid to MP1, MP0 valid                                                 | <i>t</i> <sub>7</sub> | 11      | 20       | ns       | -              |  |

| ACEN# active to D-bus valid                                                   | t <sub>8</sub>        | 16      | 27       | ns       | _              |  |

| Action code valid to MD-bus valid                                             | $t_9$                 | 10      | 19       | ns       | _              |  |

| Action code invalid to MD-bus invalid                                         | t <sub>10</sub>       | 11      | 20       | ns       | _              |  |

| DLE inactive to PARERR# enabled                                               | t <sub>11</sub>       | 17      | 30       | ns       | -              |  |

| DRD# inactive to PARERR# disabled                                             | t <sub>12</sub>       | 17      | 28       | ns       |                |  |

| IALE active to XA-bus valid                                                   | t <sub>13</sub>       | 11      | 19       | ns       | _              |  |

| XA-bus valid to A-bus validSAB 82C215-12<br>SAB 82C215-15                     | t <sub>14</sub>       | 7<br>7  | 19<br>16 | ns<br>ns | -              |  |

| MD, MP setup time to DLE trailing edge                                        | t <sub>15</sub>       | 0       | _        | ns       | _              |  |

| MD, MP hold time from DLE trailing edge                                       | t <sub>16</sub>       | 6       | _        | ns       | ] -            |  |

| DRD# setup time to DLE trailing edge                                          | t <sub>17</sub>       | 12      | _        | ns       | _              |  |

| MD-bus hold time from ACEN# trailing edge                                     | t <sub>19</sub>       | 7.5     | -        | ns       | _              |  |

| MD-bus valid to MP valid during DMA memory write cycle                        | t <sub>20</sub>       | 14      | 24       | ns       | -              |  |

| MD-bus high byte valid to MD low byte valid during DMA high memory read cycle | t <sub>21</sub>       | 10      | 19       | ns       | _              |  |

| Action code valid to MD high byte valid during DMA high memory write cycle    | t <sub>22</sub>       | 9       | 18       | ns       | _              |  |

| Action code valid to MP valid during DMA high memory write cycle              | t <sub>23</sub>       | 17      | 28       | ns       | _              |  |

## **Timing Diagrams**

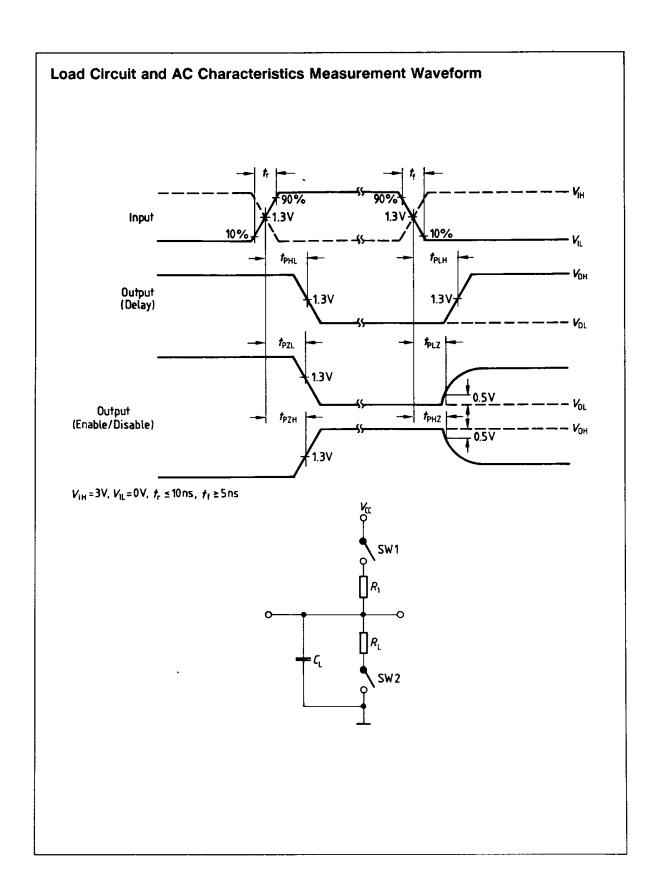

## **Load Circuit Measurement Conditions**

| Parameter                 | Output Type                             | Symbol           | C <sub>L</sub> (pF) | $R_1$ (k $\Omega$ ) | $R_L(k\Omega)$ | SW <sub>1</sub> | SW <sub>2</sub> |

|---------------------------|-----------------------------------------|------------------|---------------------|---------------------|----------------|-----------------|-----------------|

| Propagation<br>Delay Time | Totem Pole<br>Tristate<br>Bidirectional | t <sub>PLH</sub> | 50<br>50            | <b>-</b><br>-       | 1.0<br>1.0     | OFF<br>OFF      | ON<br>ON        |

| Propagation<br>Delay Time | Open Drain or<br>Open Collector         | t <sub>PLH</sub> | 50<br>50            | 0.5<br>0.5          | -              | ON<br>ON        | OFF<br>OFF      |

| Disable Time              | Tristate<br>Bidirectional               | t <sub>PLZ</sub> | 5<br>5              | 0.5<br>0.5          | 1.0<br>1.0     | ON<br>OFF       | ON              |

| Enable Time               | Tristate<br>Bidirectional               | t <sub>PZL</sub> | 50<br>50            | 0.5<br>0.5          | 1.0<br>1.0     | ON<br>OFF       | ON<br>ON        |

## **Package Outlines**

Electronic Designs Inc. makes no warranty for the use of the products described in this volume. These specifications are subject to change and are based on design goals and are not guaranteed. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Electronic Designs Inc. reserves the right to make any changes in specifications at any time and without notice. Information contained in this volume supersedes data previously published on these parts by EDI. (Revision 1-89) CAGE 66301

Life Support Policy

Electronic Designs Products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of EDI. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support of sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to affect its safety or effectiveness.

Additional copies of this Databook, as well as other EDI literature, may be ordered from:

Publications Department Electronic Designs Incorporated 42 South Street Hopkinton MA 01748, USA 508-435-2341

Fax: 508-435-6302

Copyright@1990 Electronic Designs Inc.