# SIEMENS

# CMOS Programmable SAB 82C59A-2 Interrupt Controller

## **Preliminary**

- Compatible with NMOS and CMOS 8085A, SAB 8086/8088, SAB 80186/80188, SAB 80286 and 80386 processor families

- Eight-level priority controller

- Expandable to 64 levels

- Programmable interrupt modes

- Individual request mask capability

- · Fully static design

- Low standby power dissipation

- Compatible with the industry standard NMOS SAB 8259A-2

| n Configuration |                 |                      | Pin Names |                             |

|-----------------|-----------------|----------------------|-----------|-----------------------------|

| تدرا            |                 | 28 □ V <sub>CC</sub> | D7-D0     | Data Bus (bidirectional)    |

| ₩R 🗒 2          |                 | 27 A0                | RD        | Read Input                  |

| 170 □ 3         |                 | 26 TINTA             | WR        | Write Input                 |

| 07 🗖 4          |                 | 25   IR7             | A0        | Command Select Address      |

| D6 🗆 S          |                 | 24   IR6             |           | Chip Select                 |

| D5              |                 | 23                   | CAS2-CAS0 | Cascade Lines               |

| 03 [ 8          | SAB<br>82C59A-2 | 21   IR3             | SP/EN     | Slave Program/Enable Buffer |

| D2              |                 | 20   IR2             | INT       | Interrupt Output            |

| 01 🗖 10         |                 | 19 🗀 IR1             | INTA      | Interrupt Acknowledge Input |

| 00 🗖 11         |                 | 18 🗀 IR0             | IR0-IR7   | Interrupt Request Inputs    |

| CAS 0 🗖 12      |                 | 17 🗀 INT             |           | Interrupt nequest inputs    |

| CA\$1 ☐ 13      |                 | 16 SP/EN             |           |                             |

| GND 🗀 14        |                 | 15 🗀 CAS2            |           |                             |

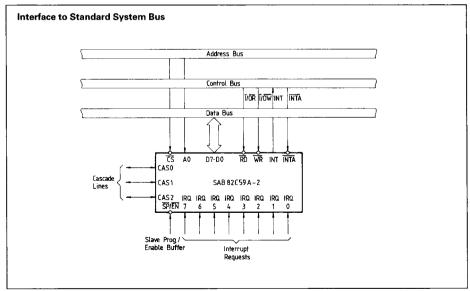

The SAB 82C59A-2 Programmable Interrupt Controller is a high-performance CMOS version of the NMOS SAB 8259A-2. The SAB 82C59A-2 is fabricated in Siemens ACMOS technology and compatible with the industry standard 8259A. The SAB 82C59A-2 handles up to 8 vectored interrupts to the CPU. It is designed to minimize the

software and real-time overhead in handling multilevel priority interrupts. It offers several modes, permitting optimization for a variety of system requirements. Packaged in a 28-pin plastic dualin-line package, the SAB 82C59A-2 as a static CMOS circuit insures low operating power.

## **Pin Definitions and Functions**

| Symbol          | Pin        | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <del>CS</del>   | 1          | I                       | CHIP SELECT A low on this pin enables RD and WR communication between the CPU and the SAB 82C59A-2. INTA functions are independent of CS.                                                                                                                                                                                                                        |

| WR              | 2          | I                       | WRITE A low on this pin, when $\overline{\text{CS}}$ is low, enables the SAB 82C59A-2 to accept command words from the CPU.                                                                                                                                                                                                                                      |

| RD              | 3          | 1                       | READ A low on this pin, when $\overline{\text{CS}}$ is low, enables the SAB 82C59A-2 to release status onto the data bus for the CPU.                                                                                                                                                                                                                            |

| D7-D0           | 4-11       | 1/0                     | BIDIRECTIONAL DATA BUS<br>Control, status, and interrupt vector information is transferred<br>via this bus.                                                                                                                                                                                                                                                      |

| CAS0-CAS2       | 12, 13, 15 | I/O                     | CASCADE LINES The CAS lines form a private SAB 82C59A-2 bus to control a multiple SAB 82C59A-2 structure. These pins are outputs for a master SAB 82C59A-2 and inputs for a slave SAB 82C59A-2.                                                                                                                                                                  |

| SP/EN 4U.com    | 16         | 1/0                     | SLAVE PROGRAM/ENABLE BUFFER This is a dual-function pin. When in buffered mode it can be used as an output to control buffer transceivers ( $\overline{EN}$ ). When not in buffered mode it is used as an input to designate a master ( $\overline{SP}=1$ ) or slave ( $\overline{SP}=0$ ).                                                                      |

| INT             | 17         | 0                       | INTERRUPT This pin goes high whenever a valid interrupt request is asserted. It is used to interrupt the CPU and is, therefore, connected to the CPU's interrupt pin.                                                                                                                                                                                            |

| IRO-IR7         | 18-25      | I                       | INTERRUPT REQUESTS These are asynchronous inputs. An interrupt request can be generated by raising an IR input (low to high) and holding it high until it is acknowledged (edge-triggered mode), or just by a high level on an IR input (level-triggered mode).                                                                                                  |

| ĪNTĀ            | 26         | 1                       | INTERRUPT ACKNOWLEDGE This pin is used to enable SAB 82C59A-2 interrupt vector data onto the data bus. This is done by a sequence of interrupt acknowledge pulses issued by the CPU.                                                                                                                                                                             |

| A0              | 27         | - 1                     | A0 ADDRESS LINE This pin acts in conjunction with the $\overline{\text{CS}}$ , $\overline{\text{WR}}$ and $\overline{\text{RD}}$ pins. It is used by the SAB 82C59A-2 to distinguish between various command words written by the CPU and the status the CPU wishes to read. It is typically connected to the CPU A0 address line (A1 for SAB 8086/80186/80286). |

| V <sub>cc</sub> | 28         | _                       | POWER SUPPLY (+5V)                                                                                                                                                                                                                                                                                                                                               |

| GND             | 14         | _                       | GROUND (0 V)                                                                                                                                                                                                                                                                                                                                                     |

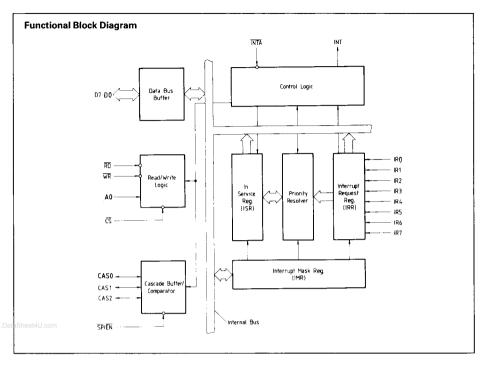

## **Functional Description**

#### General

The SAB 82C59A-2 is a device specifically designed for use in real-time, interrupt-driven microcomputer systems. It manages eight levels of requests and has built-in features for expandability to other SAB 82C59A-2 devices (up to 64 levels). It is programmed by the system's software as an I/O peripheral. A selection of priority modes is available to the programmer so that the manner in which the requests are processed by the SAB 82C59A-2 can be configured to match his system requirements. The priority modes can be changed or reconfigured dynamically at any time during the main program. This means that the complete interrupt structure can be defined as required, based on the total system environment.

## Interrupt Request Register (IRR) and In-Service Register (ISR)

The interrupts at the IR input lines are handled by two cascaded registers: the Interrupt Request Register (IRR) and the In-Service Register (ISR). The IRR is used to store all the interrupt levels which are requesting service, and the ISR is used to store all the interrupt levels which are being serviced.

#### **Priority Resolver**

This logic block determines the priorities of the bits set in the IRR. The highest priority is selected and strobed into the corresponding bit of the ISR during an INTA pulse.

#### Interrupt Mask Register (IMR)

The IMR stores the bits which mask the interrupt lines. The IMR operation is based on the IRR. Masking of a higher priority input will not affect the interrupt request lines of lower priority.

#### INT (Interrupt)

This output goes directly to the CPU interrupt input. The  $V_{\rm OH}$  level on this line is designed to be fully compatible with the SAB 8085A/8086/8088/80186/80188/80286 and 80386.

#### INTA (Interrupt Acknowledge)

INTA pulses will cause the SAB 82C59A-2 to release vectoring information onto the data bus. The format of this data depends on the system mode (μPM) of the SAB 82C59A-2.

#### **Data Bus Buffer**

This tristate, bidirectional 8-bit buffer is used to interface the SAB 82C59A-2 to the system data bus. Control words and status information are transferred through the data bus buffer.

#### Read/Write Control Logic

The function of this block is to accept output commands from the CPU. It contains the Initialization Command Word (ICW) registers and Operation Command Word (OCW) registers which store the various control formats for device operation. This function block also allows the status of the SAB 82C59A-2 to be transferred onto the data bus.

#### CS (Chip Select)

A low on this input enables the SAB 82C59A-2. No reading or writing of the chip will occur unless the device has been selected.

#### WR (Write)

A low on this input enables the CPU to write control words (ICWs and OCWs) to the SAB 82C59A-2.

#### RD (Read)

A low on this input enables the SAB 82C59A-2 to send the status of the Interrupt Request Register (IRR), the In-Service Register (ISR), the Interrupt Mask Register (IMR), or the interrupt level onto the data bus.

#### A0

This input signal is used in conjunction with WR and RD signals to write commands into the various command registers, as well as to read the various status registers of the chip. This line can be tied directly to one of the address lines.

#### The Cascade Buffer/Comparator

This function block stores and compares the IDs of all SAB 82C59A-2 devices used in the system. The associated three I/O pins (CAS0-2) are outputs when the SAB 82C59A-2 is used as a master and are inputs when the SAB 82C59A-2 is used as a slave. As a master, the SAB 82C59A-2 is used as a slave. As a master, the SAB 82C59A-2 sends the ID of the interrupting slave device onto the CAS0-2 lines. The slave thus selected will send its preprogrammed subroutine address onto the data bus during the next one or two consecutive INTA pulses.

#### Interrupt Sequence

The powerful features of the SAB 82C59A-2 in a microcomputer system are its programmability and the interrupt routine addressing capability. The latter allows direct or indirect jumping to the specific interrupt routine requested without any polling of the interrupting devices. The normal sequence of events during an interrupt depends on the type of CPU being used.

In an SAB 8085A system the events occur as follows:

- One or more of the interrupt request lines (IR7-0) are raised high, setting the corresponding IRR bit(s).

- 2. The SAB 82C59A-2 evaluates these requests, and sends an INT to the CPU, if appropriate.

- 3. The CPU acknowledges the INT and responds with an INTA pulse.

- 4. Upon receiving an INTA from the CPU group, the highest priority ISR bit is set, and the corresponding IRR bit is reset. The SAB 82C59A-2 will also release a "call" instruction code (11001101) onto the 8-bit data bus through its D7-0 pins.

- 5. This "call" instruction will initiate two more INTA pulses to be sent to the SAB 82C59A-2 from the CPU group.

- 6. These two INTA pulses allow the SAB 82C59A-2 to release its preprogrammed subroutine address onto the data bus. The lower 8-bit address is released at the first INTA pulse and the higher 8-bit address is released at the second INTA pulse.

7. This completes the 3-byte "call" instruction released by the SAB 82C59A-2. In the AEOI (automatic end of interrupt) mode the ISR bit is reset at the end of the third INTA pulse. Otherwise, the ISR bit remains set until an appropriate EOI command is issued at the end of the interrupt sequence.

The events occurring in an SAB 8086/8088/80186/80188/80286 or 80386 system are the same until step 4.

- 4. Upon receiving an INTA from the CPU group, the highest priority ISR bit is set and the corresponding IRR bit is reset. The SAB 82C59A-2 does not drive the data bus during this cycle.

- The CPU will initiate a second INTA pulse.

During this pulse, the SAB 82C59A-2 releases an 8-bit pointer onto the data bus where it is read by the CPU.

- 6. This completes the interrupt cycle. In the AEOI mode, the ISR bit is reset at the end of the second INTA pulse. Otherwise, the ISR bit remains set until an appropriate EOI command is issued at the end of the interrupt subroutine.

If no interrupt request is present at step 4 of either sequence (i.e. the request duration was too short), the SAB 82C59A-2 will issue an interrupt level 7. Both, the vectoring bytes and the CAS lines will look as if an interrupt level 7 was requested.

## Absolute Maximum Ratings 1)

Ambient temperature under bias

0 to 70°C

Storage temperature

-65 to +150°C

Voltage on any pin with respect to ground Supply voltage with respect to ground

-0.5 to  $V_{cc} + 0.5$  V -0.5 to 7.0 V

Power dissipation

1 W

### **DC Characteristics**

$T_A = 0$  to 70°C;  $V_{CC} = 5 \text{ V} \pm 10\%$ ; GND = 0V

| Symbol           | D                         | Limit                       | values               |      | Test condition                                                                                                 |  |

|------------------|---------------------------|-----------------------------|----------------------|------|----------------------------------------------------------------------------------------------------------------|--|

|                  | Parameter                 | min.                        | max.                 | Unit |                                                                                                                |  |

| V <sub>IL</sub>  | Input low voltage         | -0.5                        | 0.8                  | ٧    | _                                                                                                              |  |

| V <sub>IH</sub>  | Input high voltage        | 2.2                         | V <sub>cc</sub> +0.5 | V    | _                                                                                                              |  |

| V <sub>OL</sub>  | Output low voltage        | _                           | 0.4                  | V    | $I_{\rm OL}=2.5~{\rm mA}$                                                                                      |  |

| V <sub>OH</sub>  | Output high voltage       | 3.0<br>V <sub>CC</sub> -0.4 | _                    | V    | $I_{OH} = -2.5 \text{ mA}$<br>$I_{OH} = -100 \mu\text{A}$                                                      |  |

| I <sub>LI</sub>  | Interrupt leakage current | _                           | ±1                   | μΑ   | $0  \mathrm{V} < V_{\mathrm{IN}} < V_{\mathrm{CC}}$                                                            |  |

| I <sub>LOL</sub> | Output leakage current    |                             | ±10                  | μА   | $0  \mathrm{V} < V_{\mathrm{OUT}} < V_{\mathrm{CC}}$                                                           |  |

| I <sub>LIR</sub> | IR input leakage current  | -                           | -300<br>+10          | μА   | $V_{IN} = 0 \text{ V}$ $V_{IN} = V_{CC}$                                                                       |  |

| $I_{\rm CC}$     | Operating supply current  | _                           | 5                    | mA   | 2)                                                                                                             |  |

| Iccs             | Standby supply current    | _                           | 10                   | μΑ   | $V_{\rm CC} = 5.5$ V, outputs<br>unloaded,<br>$V_{\rm IN} = V_{\rm CC}$ or GND<br>All IR inputs = $V_{\rm CC}$ |  |

## Capacitance

$T_A = 25^{\circ}C; V_{CC} = GND = 0 V$

| Symbol I         | B                  | Li   | Limit values |      | Test condition                                               |  |

|------------------|--------------------|------|--------------|------|--------------------------------------------------------------|--|

|                  | Parameter          | min. | max.         | Unit | rest condition                                               |  |

| C <sub>IN</sub>  | Input capacitance  | -    | 5            | pF   | 4 1 8411-                                                    |  |

| C <sub>IO</sub>  | I/O capacitance    | -    | 20           | pF   | f <sub>C</sub> = 1 MHz<br>Unmeasured pins<br>returned to GND |  |

| C <sub>OUT</sub> | Output capacitance | -    | 15           | pF   |                                                              |  |

<sup>1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2)</sup> Repeated data input with 8086-2 timings.

## **AC Characteristics**

$T_{\rm A} = 0 \text{ to } 70^{\circ}{\rm C}; \ V_{\rm CC} = 5 \,{\rm V} \pm 10\%; \ {\rm GND} = 0 \,{\rm V}$

#### **Timing Requirements**

| Symbol               | Parameter                                                                  | Limit values |      | 11.3 |                |

|----------------------|----------------------------------------------------------------------------|--------------|------|------|----------------|

| Symbol               | rarameter                                                                  | min.         | max. | Unit | Test condition |

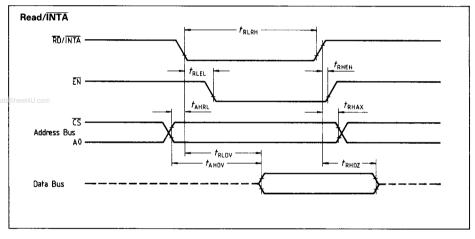

| t <sub>AHRL</sub>    | A0/CS setup to RD/INTA↓                                                    | 0            | _    | ns   | _              |

| t <sub>RHAX</sub>    | A0/ <del>CS</del> hold after <del>RD</del> / <del>INTA</del> ↑             | 0            | _    | ns   | _              |

| t <sub>RLRH</sub>    | RD pulse width                                                             | 160          | _    | ns   | _              |

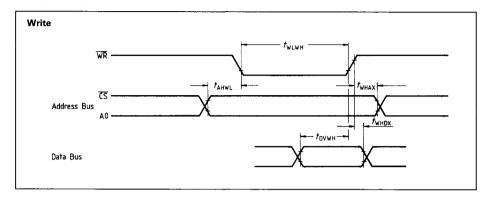

| t <sub>AHWL</sub>    | A0/ <del>CS</del> setup to <del>WR</del> ↓                                 | 0            | _    | ns   | _              |

| t <sub>WHAX</sub>    | A0/ <del>CS</del> hold after <del>WR</del> ↑                               | 0            | _    | ns   | _              |

| t <sub>WLWH</sub>    | WR pulse width                                                             | 190          | _    | ns   | _              |

| t <sub>DVWH</sub>    | Data setup to WR↑                                                          | 160          | _    | ns   | _              |

| t <sub>WHDX</sub>    | Data hold after WR↑                                                        | 0            |      | ns   | _              |

| t <sub>JLJH</sub> 1) | Interrupt request width (low)                                              | 100          | -    | ns   | _              |

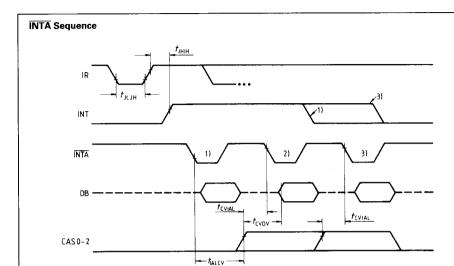

| t <sub>CVIAL</sub>   | Cascade setup to second or third INTA↓ (slave only)                        | 40           | -    | ns   | -              |

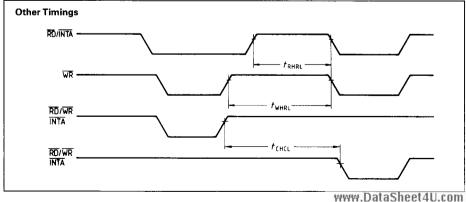

| t <sub>RHRL</sub>    | End of RD to next RD End of INTA to next INTA within an INTA sequence only | 160          | _    | ns   | -              |

| t <sub>WHRL</sub>    | End of WR to next WR                                                       | 190          | _    | ns   | _              |

| Cheet (2) .com       | End of command to next command (not same command type)                     | 180          | -    | ns   | _              |

|                      | End of INTA sequence to next INTA sequence                                 | 400          | -    | ns   | -              |

#### **Timing Responses**

| Symbol             | Parameter                                   | Limit values |      | 11-24 | 7                            |

|--------------------|---------------------------------------------|--------------|------|-------|------------------------------|

| Symbol             | rarameter                                   | min.         | max. | Unit  | Test condition <sup>3)</sup> |

| $t_{RLDV}$         | Data valid from RD/INTA↓                    |              | 120  | ns    | 1                            |

| t <sub>RHDZ</sub>  | Data float after RD/INTA↑                   | 10           | 85   | ns    | 2                            |

| t <sub>JHIH</sub>  | Interrupt output delay                      | -            | 300  | ns    | 1                            |

| t <sub>IALCV</sub> | Cascade valid from first INTA (master only) | _            | 360  | ns    | 1                            |

| t <sub>RLEL</sub>  | Enable active from RD↓<br>or INTA↓          | _            | 100  | ns    | 1                            |

| t <sub>RHEH</sub>  | Enable inactive from RD↑ or INTA↑           | -            | 150  | ns    | 1                            |

| $t_{AHDV}$         | Data valid from stable address              |              | 200  | ns    | 1                            |

| $t_{\text{CVDV}}$  | Cascade valid to valid data                 | -            | 200  | ns    | 1                            |

<sup>1)</sup> This is the low time required to clear the input latch in the edge-triggered mode.

$<sup>^{2}</sup>$ ) Worst-case timing for  $t_{\mathrm{CHCL}}$  in an actual microprocessor system is typically much greater than 400 ns.

<sup>3)</sup> See diagrams on next page.

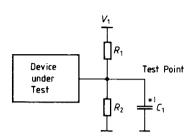

## **AC Testing**

## Load Circuit

\*) Includes Stray and Jig Capacitance

#### **Test Condition Definition**

| Test Condition | V <sub>1</sub> | R <sub>1</sub>  | R <sub>2</sub> | C <sub>1</sub>  |

|----------------|----------------|-----------------|----------------|-----------------|

| 1              | 1.7 V<br>4.5 V | 523 Ω<br>1.8 kΩ | Open<br>1.8 kΩ | 100 pF<br>30 pF |

| 2              | 4.5 V          | 1.0 KS2         | 1.0 KS2        | 30 pr           |

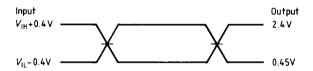

#### I/O Waveform

AC testing: All input signals must switch between  $V_{\rm IL}-0.4\,{\rm V}$  and  $V_{\rm IH}+0.4\,{\rm V}$ . Input rise and fall times must be  $\leq$ 15 ns. All timing measurements are made at 2.4 V and 0.45 V.

## **Waveforms**

Interrupt output must remain high at least until leading edge of first INTA.

## **Ordering Information**

| Туре           | Ordering code | Description                                                  |

|----------------|---------------|--------------------------------------------------------------|

| SAB 82C59A-2-P | Q67120-P238   | Programmable interrupt controller,<br>8 MHz, plastic package |

<sup>1)</sup> Cycle 1 in SAB 8086/8088/80186/80188/80286 and 80386 systems, the data bus is not active.

<sup>&</sup>lt;sup>2</sup>) Cycle 2.

<sup>3)</sup> Cycle 3 in SAB 8085 systems only.