#### INTERNAL USE CONFIDENTIAL, SUBJECT TO CHANGE

# High Efficiency, Synchronous 3A Buck Charger for 1 cell Li-ion Battery with NVDC Power Path Management

#### 1 DESCRIPTION

The SC89601A is a 1.5MHz highly integrated switch-mode buck charger for 1 cell Li-ion battery applications and NVDC system power path management, which separate the system load and charge current, also the system can power up with deep depletion battery. System can get the power from VBUS, VBAT or both. It supports 3.9-13.5V input voltage, up to 3A charging current and provide battery charge management functions including trickle charge, constant current charge, constant voltage charge, charge termination ,auto recharge and charging status indication.

The SC89601A supports flexible charge current option, the user can program the current and all others charger spec by I2C interface.

The SC89601A supports USB OTG with up to 1.4A output with PFM/PWM mode. Meanwhile, the SC89601A supports USB Input BC1.2, non-standard adapters.

The SC89601A supports input current and voltage limit, input under voltage and over voltage protections, internal cycle by cycle current limit, battery short circuit protection, and output over voltage protection. It also offers charging safety timer and over temperature protection to ensure safety under different abnormal conditions.

The SC89601A integrated all MOSFETs, current sensing, loop compensation and I2C interface.

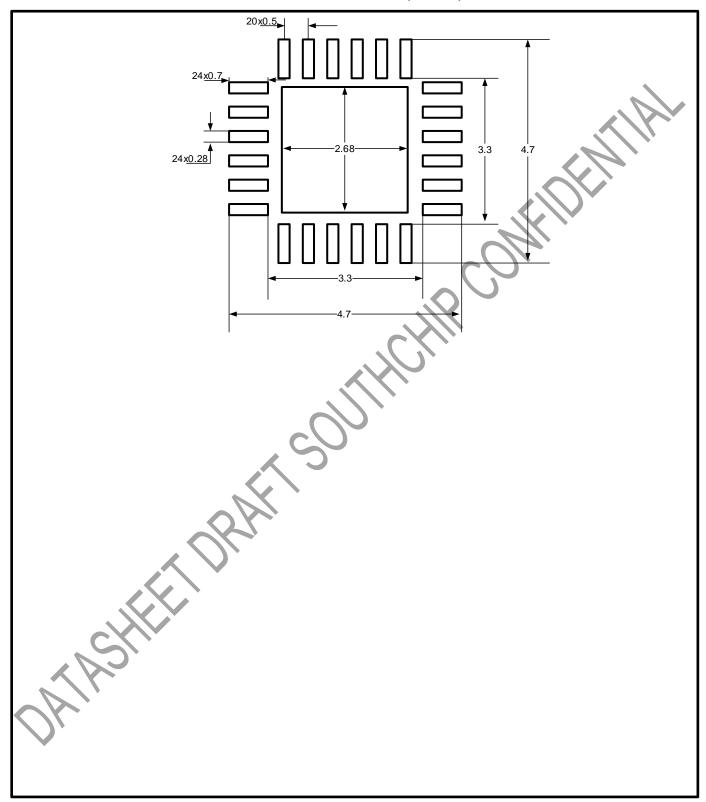

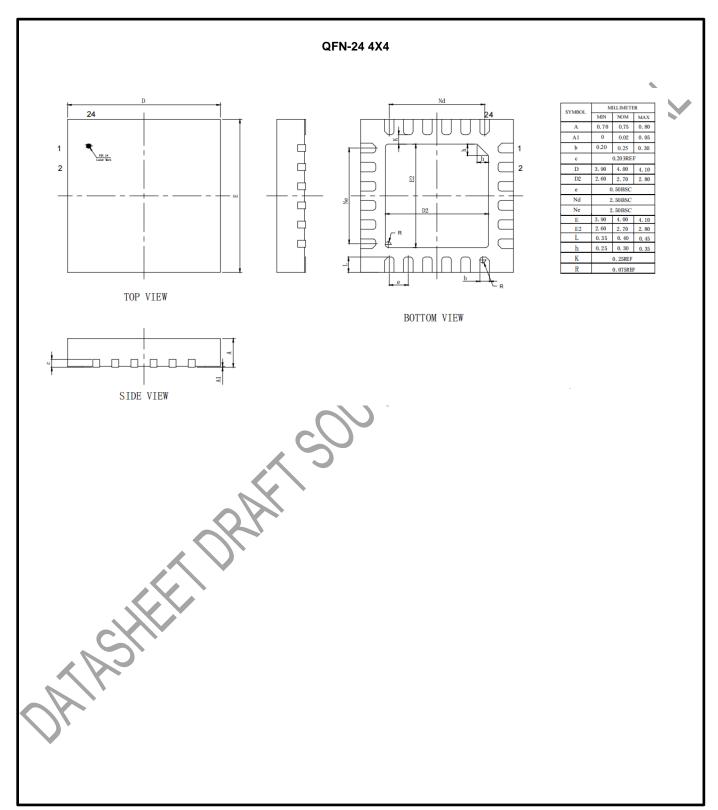

The SC89601A is available in QFN(24)-4\*4 package.

## 3 APPLICATIONS

- Smart Phones

- Portable Internet Devices and Accessory

#### 2 FEATURES

- Integrated Synchronous Buck Charger

- Integrated NVDC Power Path Management

- Charging Management (Trickle Charge / Constant/ Current Charge / Constant Voltage Charge / Charge Termination)

- Integrated I2C Interface

- I2C Programmable Constant Charge Current, ±5%

@1.5A-3A Accuracy

- I2C Programmable Constant Voltage, ±0.5% Accuracy

- I2C Programmable Charge Safety Timer

- Support OTG Discharging Function and I2C Programmable Output Voltage: 3.9V~5.4V with up 1.4A Current

- Charge Status Indication

- NTC for Battery Protection (Support JEITA Standard)

- Input Under Voltage and Over Voltage Protection

- Internal Cycle by Cycle Over Current Protection

- OTG OCP/OVP/VBAT\_LOW Protection

- Battery Over Voltage and Short Protection

- Battery Discharging Over Current and Under voltage Protection

- Thermal Regulation and Shutdown

- QFN(24)-4\*4 Footprint

#### 4 DEVICE INFORMATION

| Part Number  | Package     | Dimension |

|--------------|-------------|-----------|

| SC89601AQDLR | QFN(24)-4*4 | 4mm x 4mm |

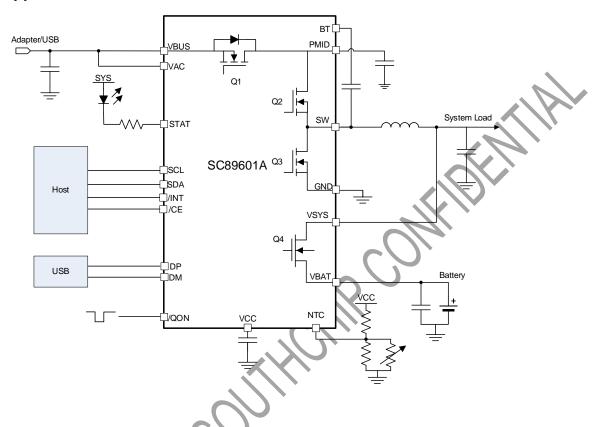

## 5 Typical Application Circuit

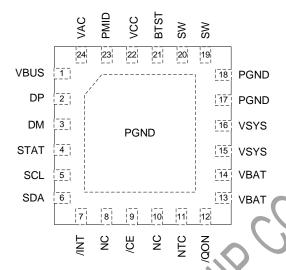

## 6 Terminal Configurations and Functions

QFN(24) 4x4 (TOP View)

|          | I/O  |   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC89601A | NAME |   |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1        | VBUS | 1 | Power supply pin. Place a 1µF ceramic capacitor from VBUS to GND close to the IC.                                                                                                                                                                                                                                                                                                                |

| 2        | DP   | Ю | Positive line of the USB data line pair. DP/DM based USB host/charging port detection. The detection includes data contact detection (DCD), primary and secondary detection in BC1.2.                                                                                                                                                                                                            |

| 3        | DM   | Ю | Negative line of the USB data line pair. DP/DM based USB host/charging port detection. The detection includes data contact detection (DCD), primary and secondary detection in BC1.2.                                                                                                                                                                                                            |

| 4        | STAT |   | Open-drain charge status output. Connect the STAT pin to a logic rail via 10-kΩ resistor. The STAT pin indicates charger status. Collect a current limit resister and a LED from a rail to this pin.  Charge in progress: LOW  Charge complete or charger in SLEEP mode: HIGH  Charge suspend (fault response): 1-Hz, 50% duty cycle Pulses  This pin can be disabled via STAT DIS register bit. |

| 5        | SCL  | 1 | I2C interface clock. Connect SCL to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                     |

| 6        | SDA  | Ю | I2C interface data. Connect SDA to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                      |

| 7        | /INT | 0 | Open-drain interrupt Output. Connect the INT to a logic rail through $10\text{-k}\Omega$ resistor. The /INT pin sends an active low, 256- $\mu$ s pulse to host to report charger device status and fault.                                                                                                                                                                                       |

| 8        | NC   |   | Not Connected                                                                                                                                                                                                                                                                                                                                                                                    |

| 9        | /CE  | I | Charger enable pin. Low to enable battery charging.                                                                                                                                                                                                                                                                                                                                              |

| 10       | NC   |   | Not Connected                                                                                                                                                                                                                                                                                                                                                                                    |

| 11       | NTC  | Ю | Connect to the Negative Temperature Coefficient (NTC) thermistor inside the battery cells to sense the battery cells temperature for protection. When NTC is not used, connect a $10K\Omega$ resistor to GND.                                                                                                                                                                                    |

| 12       | /QON | I | BATFET enable control input. When BATFET is in ship mode, a logic low of t <sub>SHIPMODE</sub> duration turns on BATFET to exit shipping mode.                                                                                                                                                                                                                                                   |

| 13,14    | VBAT | 0 | Battery connection point to the positive terminal of the battery pack. Connect a $10\mu F$ ceramic capacitor close to the VBAT pin.                                                                                                                                                                                                                                                              |

## SOUTHCHIP SEMICONDUCTOR

| 15,16 | VSYS | 0   | Converter output connection point. Connect a 20 µF capacitor close to the VSYS pin.                                                                                                                                                      |

|-------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17,18 | PGND | ı   | Power ground pin.                                                                                                                                                                                                                        |

| 19,20 | SW   | 0   | Switching node output. Connected to output inductor. Connect the 47nF bootstrap capacitor from SW to BTST.                                                                                                                               |

| 21    | BTST | Ю   | PWM high side driver positive supply. Internally, the BTST pin is connected to the cathode of the boost-strap diode. Connect the 47nF bootstrap capacitor from SW to BTST.                                                               |

| 22    | vcc  | 0   | HSFET and LSFET driver and internal supply output. Internally, VCC is connected to the anode of the boost-strap diode. Connect a 4.7-µF (10-V rating) ceramic capacitor from VCC to GND. The capacitor should be placed close to the IC. |

| 23    | PMID | 0   | Connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Put 10 µF ceramic capacitor on PMID to GND.                                                                                                        |

| 24    | VAC  | - 1 | Connected to VBUS.                                                                                                                                                                                                                       |

|       |      |     |                                                                                                                                                                                                                                          |

## 7 Specification

## 7.1 Absolute Maximum Rating

Over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                                           | Min.     | Max. | Unit |

|------------------------|-----------------------------------------------------------|----------|------|------|

|                        | VBUS, VAC                                                 | -0.3     | 22   | V    |

|                        | PMID                                                      | -0.3     | 22   | V    |

| Voltage <sup>(2)</sup> | BTST                                                      | -0.3     | 22   | V    |

| Voltage                | SW <sup>(3)</sup>                                         | -2(10ns) | 16   | V    |

|                        | BTST to SW                                                | -0.3     | 6    | V    |

|                        | DP,DM,VCC,NTC,/CE,VBAT,VSYS,SDA,SCL,/INT,/QON , QON, STAT | -0.3     | 6    | V    |

| TJ                     | Operating junction temperature                            | -40      | 150  | °C   |

| T <sub>stg</sub>       | Storage temperature                                       | -65      | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

#### 7.2 Thermal Information

| THERMAL RESISTA       | QFN (4mmX4mm)                          | Unit |      |

|-----------------------|----------------------------------------|------|------|

| $\theta_{JA}$         | Junction to ambient thermal resistance | 34   | °C/W |

| $\theta_{	extsf{JC}}$ | Junction to case resistance            | 25   | °C/W |

<sup>(1)</sup> Measured on JESD51-7, 4-layer PCB.

#### 7.3 ESD Ratings

|                                 |                                |          | Min. | Max. | Unit |

|---------------------------------|--------------------------------|----------|------|------|------|

| V <sub>ESD</sub> <sup>(1)</sup> | Human-body Model (HBM) (2)     | All pins | -2   | +2   | kV   |

| VESD                            | Charged-device Model (CDM) (3) |          | -750 | 750  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

## 7.4 Recommended Operation Conditions

|                  |                     | MIN | TYP | MAX   | UNIT |

|------------------|---------------------|-----|-----|-------|------|

| V <sub>BUS</sub> | VBUS voltage range  | 3.9 |     | 13.5  | V    |

| V <sub>BAT</sub> | VBAT voltage range  |     | 4.2 | 4.848 | V    |

| I <sub>IN</sub>  | Input current limit |     |     | 3.25  | А    |

<sup>(2)</sup> All voltages are with respect to network ground terminal.

<sup>(3)</sup> VBUS, PMID, BTST, SW should be tied together to test the SW abs voltage,

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### SOUTHCHIP SEMICONDUCTOR

INTERNAL USE CONFIDENTIAL, SUBJECT TO CHANGE

| Icc              | Constant current charge current |     |    | 3   | А  |

|------------------|---------------------------------|-----|----|-----|----|

| I <sub>DIS</sub> | Discharging current             |     | 10 |     | А  |

| L                | Inductance                      |     | 1  |     | μH |

| T <sub>A</sub>   | Operating ambient temperature   | -40 |    | 85  | °C |

| TJ               | Operating junction temperature  | -40 |    | 125 | °C |

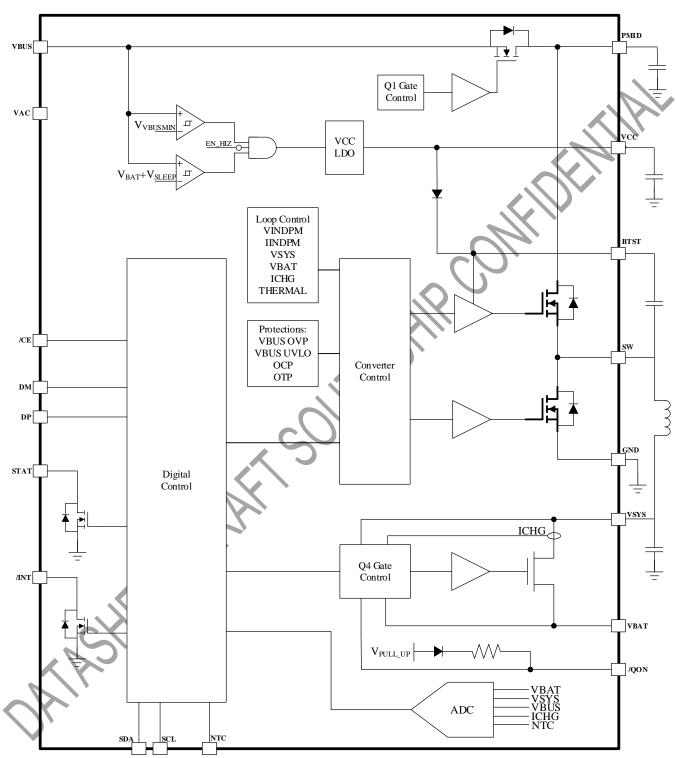

## 8 Function Block Diagram

## 9 Electrical Characteristics

$T_{J}\text{=-}40^{\circ}\text{C}$  to 125  $^{\circ}\text{C}~$  and  $V_{AC\_UVLO}\text{<}~V_{BUS}\text{<}~V_{VAC\_OVP},$  unless otherwise noted.

| PARAMETER                                       |                                                                 | TEST CONDITIONS                                                                                                                    | MIN  | TYP  | MAX  | UNIT       |

|-------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|

| SUPPLY VOLT                                     | AGE                                                             |                                                                                                                                    |      |      |      |            |

| V <sub>BUS</sub>                                | Operating input V <sub>BUS</sub> voltage                        |                                                                                                                                    | 3.9  |      | 13.5 | V          |

| V                                               | V for active ISC no bettony                                     | Rising edge                                                                                                                        |      | 3.3  | 3.7  | V          |

| $V_{VAC\_UVLO}$ $V_{BUS}$ for active I2C, no ba | V <sub>BUS</sub> for active 12C, no battery                     | Hysteresis                                                                                                                         |      | 300  | -\1  | mV         |

| V                                               | \/ \/ threehold                                                 | Falling edge                                                                                                                       | 20   | 100  | 210  | mV         |

| $V_{SLEEP}$                                     | V <sub>BUS</sub> -V <sub>BAT</sub> threshold                    | Rising edge                                                                                                                        | 120  | 220  | 370  | mV         |

|                                                 |                                                                 | 5.8V , Rising edge                                                                                                                 | 5.4  | 5.8  | 6.1  | V          |

|                                                 |                                                                 | Hysteresis                                                                                                                         | 4    | 300  |      | mV         |

|                                                 |                                                                 | 6.4V, Rising edge                                                                                                                  | 6.1  | 6.4  | 6.75 | V          |

| V                                               | V Over Veltage threehold                                        | Hysteresis                                                                                                                         |      | 300  |      | mV         |

| $V_{VAC\_OVP}$                                  | V <sub>BUS</sub> Over Voltage threshold                         | 10.5V, Rising edge                                                                                                                 | 10   | 10.5 | 11.1 | V          |

|                                                 |                                                                 | Hysteresis                                                                                                                         |      | 300  |      | mV         |

|                                                 |                                                                 | 14.2V, Rising edge                                                                                                                 | 13.5 | 14.2 | 14.9 | V          |

|                                                 |                                                                 | Hysteresis                                                                                                                         |      | 300  |      | mV         |

|                                                 | DATE ( 100 MOUNT                                                | Rising edge                                                                                                                        | 2.25 |      |      | V          |

| $V_{VBAT\_UVLO}$                                | BAT for active I2C, no VBUS                                     | Hysteresis                                                                                                                         |      | 240  |      | mV         |

| $V_{VBAT\_DPL}$                                 | Battery Depletion threshold                                     | Rising edge                                                                                                                        | 2.5  | 2.6  | 2.75 | V          |

|                                                 |                                                                 | Hysteresis                                                                                                                         |      | 200  |      | mV         |

| V                                               | Bad adapter detection                                           | Falling edge                                                                                                                       | 3.6  | 3.7  | 3.8  | V          |

| $V_{VBUSMIN}$                                   | threshold                                                       | Hysteresis                                                                                                                         |      | 200  |      | mV         |

| I <sub>BADSRC</sub>                             | Bad adapter detection sink current from V <sub>BUS</sub> to GND |                                                                                                                                    |      | 30   |      | mA         |

| 1                                               | Battery discharge current in Buck mode                          | $V_{BAT}$ = 4.5 V, HIZ mode, no $V_{BUS}$ , BATFET_DIS Enable, $T_{J} \le 85^{\circ}C$                                             |      | 15   | 25   | μ <b>A</b> |

| I <sub>BAT</sub>                                |                                                                 | $V_{BAT}$ = 4.5 V, HIZ mode, no $V_{BUS}$ , BATFET_DIS Disable ,T <sub>J</sub> $\leq$ 85°C                                         |      | 22   | 35   | μ <b>A</b> |

|                                                 | Input supply current in buck<br>mode when HIZ mode is           | V <sub>BUS</sub> =5V, HIZ mode and BATFET _DIS Disable, no battery                                                                 |      |      | 70   | μ <b>A</b> |

| I <sub>VBUS_HIZ</sub>                           | enabled                                                         | V <sub>BUS</sub> =12V,HIZ mode and BATFET _DIS Disable, no battery                                                                 |      |      | 70   | μΑ         |

| DI.                                             |                                                                 | $V_{\text{BUS}}$ > $V_{\text{VAC\_UVLO}}$ , $V_{\text{BUS}}$ > $V_{\text{BAT}}$ , Converter not switching                          |      | 1.5  | 3    | mA         |

| lvbus                                           | Input supply current in buck mode                               | $V_{BUS}$ > $V_{VAC\_UVLO}$ , $V_{BUS}$ > $V_{BAT}$ , Converter switching, $V_{BAT}$ =3.8 $V$ , $I_{SYS}$ =0 $A$ , disable charger |      | 3    |      | mA         |

| I <sub>BOOST</sub>                              | Battery discharge current in boost mode                         | V <sub>BAT</sub> =4.2V,boost mode, I <sub>VBUS</sub> =0A, converter switching                                                      |      |      | 3    | mA         |

| POWER PATH                                      |                                                                 | 1                                                                                                                                  |      |      |      | 1          |

#### $I_{\text{SYS}} = 0A, V_{\text{BAT}} < V_{\text{SYSMIN}}, I_{\text{SYS}} = 0A,$ $V_{\text{SYSMIN}}$ +1 ٧ **BATFET Disable** 80mV Typical system regulation $V_{\text{SYS}}$ voltage $I_{SYS}=0A, V_{BAT}>V_{SYSMIN}, I_{SYS}=0A,$ $V_{BAT}+50$ ٧ **BATFET Disable** mV Maximum DC system voltage $I_{SYS}$ =0A, $V_{BAT}$ > $V_{SYSMIN}$ , $I_{SYS}$ =0A, 44 4.51 4.45 V $V_{SYS\_MAX}$ BATFET Disable, V<sub>BAT</sub><=4.4V output Reverse blocking MOSFET on R<sub>DSON\_Q1</sub> V<sub>CC</sub>=5V 38 $m\Omega$ resistance High side switching MOSFET $R_{\text{DSON}\_\text{Q2}}$ V<sub>CC</sub>=5V 50 $m\Omega$ on resistance Low side switching MOSFET R<sub>DSON Q3</sub> V<sub>CC</sub>=5V $\boldsymbol{m}\Omega$ on resistance $V_{\text{SYS}}$ to $V_{\text{BAT}}$ MOSFET on V<sub>VBAT</sub>=4.2V 20 $R_{\text{DSON}_{Q4}}$ $\boldsymbol{m}\Omega$ resistance Supplement mode Q4 forward $V_{\text{FWD}}$ 50 mV voltage **CHARGER MANAGEMENT** Regulation Charge Voltage 3.84 4.848 V $V_{\text{BATREG\_RANGE}}$ Charge Voltage Step 16 m۷ $V_{\mathsf{BATREG\_STEP}}$ V<sub>BATREG</sub>=4.208V 4.18 4.208 4.23 ٧ Charge Voltage accuracy 4.36 4.384 4.4 V $V_{\mathsf{BATREG\_ACC}}$ $V_{BATREG}=4.432V$ ٧ 4.4 4.432 4.45 Constant charging current 0 3 Α ICC\_RANGE range Constant charging current step 60 mΑ I<sub>CC\_STEP</sub> 216 240 264 mΑ $I_{CC} = 240 \text{mA}$ , $V_{BAT} = 3.1 \text{V}$ or 3.8 V $I_{CC}$ =720mA, $V_{BAT}$ =3.1V or 3.8V 684 720 756 mΑ Constant charging current $I_{CC} = 2040 \text{mA}$ , $V_{BAT} = 3.1 \text{V}$ or 3.8 V1938 2040 2142 mΑ $I_{\text{CC\_ACC}}$ accuracy $I_{CC}$ =3000mA, $V_{BAT}$ =3.1V or 3.8V 2850 3000 3150 mA Rising edge 2.9 3 3.1 V Trickle charge to CC Charge battery voltage threshold Hysteresis 200 m۷ 60 960 Trickle charge current range mΑ 60 Trickle charge current step mΑ

Trickle charge current accuracy

$I_{TC} = 120 \text{mA}$

$I_{TC\_STEP}$

$I_{TC\_ACC}$

mΑ

150

90

120

#### $I_{TC} = 420 \text{mA}$ 390 420 450 mΑ Termination current range 30 930 mΑ I<sub>TERM\_RANGE</sub> Termination current step 60 mΑ I<sub>TERM\_STEP</sub> I<sub>TERM</sub> =120mA 90 120 150 mA Termination current accuracy I<sub>TERM\_ACC</sub> $I_{TERM} = 420 \text{mA}$ 420 450 mΑ 390 2.15 Falling edge 1.85 2 Battery short voltage $V_{\text{BAT SHORT}}$ Hysteresis 200 m۷ **5**0 Battery short charge current $V_{BAT} = 1V$ 35 65 mΑ I<sub>SHORT</sub> V<sub>BAT</sub> falling edge,100mV 80 140 100 m۷ Recharge threshold below $V_{RECHG}$ $V_{BAT\_REG}$ V<sub>BAT</sub> falling edge, 200mV 170 200 250 $\mathsf{mV}$ System discharge load current $V_{SYS}=4.2V$ 30 mΑ I<sub>SYSLOAD</sub> Deglitch time for charge 200 300 250 ms $t_{\mathsf{TERM\_DGL}}$ termination Deglitch time for recharge 200 250 300 ms t<sub>RECH\_DGL</sub> System over-current deglitch time to turn off Q4 50 100 150 us tsysocp\_dgl System over-voltage deglitch tsysovp dgl time to turn off DCDC 1 us Battery over-voltage deglitch time to disable charger 1 us t<sub>BATOVP DGL</sub> INPUT VOLTAGE AND CURRENT REGULATION Input voltage regulation limit 3.9 5 ٧ $V_{INDPM\_RANGE}$ range Input voltage regulation limit 100 mV $V_{\text{INDPM\_STEP}}$ Input voltage regulation limit V<sub>INDPM</sub>=4.8V 4.6 4.8 4.944 ٧ $V_{INDPM\_ACC}$ accuracy Input current regulation limit INDPM\_RANGE 100 3250 mΑ Input current regulation limit 50 $\mathsf{m}\mathsf{A}$ I<sub>INDPM\_STEP</sub> step $V_{\text{BUS}}$ =5V, $I_{\text{INDPM}}$ =500 mA 410 500 mΑ Input current regulation limit $V_{BUS}$ =5V, $I_{INDPM}$ =900 mA 750 900 mΑ $I_{\text{INDPM\_ACC}}$ accuracy $V_{\text{BUS}}$ =5V, $I_{\text{INDPM}}$ =1500 mA 1300 1500 mA

|                              |                                                     | V <sub>BUS</sub> =5V,I <sub>INDPM</sub> =2400 mA                         | 2200  |       | 2400  | mA  |

|------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------|-------|-------|-------|-----|

| I <sub>IN_START</sub>        | Input current limit during system start-up sequence |                                                                          |       | 200   |       | mA  |

| PROTECTION                   |                                                     |                                                                          | •     |       |       |     |

|                              | Pattery over voltage threshold                      | Rising                                                                   | 102   | 104   | 105   | %   |

| $V_{BAT\_OVP}$               | Battery over voltage threshold                      | Hysteresis                                                               |       | 2     |       | %   |

| I <sub>BAT_OCP</sub>         | Battery discharge over current threshold            |                                                                          | 10    |       | 1/2.  | А   |

| PWM                          |                                                     |                                                                          |       |       |       |     |

| f <sub>sw</sub>              | PWM switching frequency                             | V <sub>BUS</sub> = 9V, V <sub>BAT</sub> =4V, I <sub>CC=</sub> 3A         | 1320  | 1500  | 1680  | KHz |

| D <sub>MAX</sub>             | Maximum PWM duty cycle(Buck)                        |                                                                          |       | 97    |       | %   |

| JEITA (BUCK I                | MODE)                                               |                                                                          | ~(    |       |       |     |

| M                            | NTC cold temp (0°C) threshold,                      | Rising                                                                   | 72.4  | 73.3  | 74.2  | %   |

| V <sub>COLD</sub>            | as percentage of VCC                                | Falling                                                                  | 71.5  | 72    | 72.5  | %   |

| 1/                           | NTC cool temp threshold, ration                     | Rising                                                                   | 67.75 | 68.25 | 68.75 | %   |

| $V_{\text{COOL}}$            | as percentage of VCC                                | Falling                                                                  | 66.45 | 66.95 | 67.45 | %   |

| V                            | NTC warm temp threshold , as                        | Falling                                                                  | 44.25 | 44.75 | 45.25 | %   |

| $V_{WARM}$                   | percentage of VCC                                   | Rising                                                                   | 45.3  | 45.8  | 48.3  | %   |

| V <sub>HOT</sub>             | NTC hot temp (60°C) threshold,                      | Falling                                                                  | 33.7  | 34.2  | 34.7  | %   |

| <b>V</b> HOT                 | as percentage of VCC                                | Rising                                                                   | 34.8  | 35.3  | 35.8  | %   |

| NTC (BOOST I                 | MODE)                                               | ( )                                                                      |       |       |       |     |

|                              | NTC cold temp (-25°C)                               | Rising                                                                   | 79.5  | 80    | 80.5  | %   |

| $V_{\text{BCOLD}}$           | threshold, as percentage of VCC                     | Falling                                                                  | 78.5  | 79    | 79.5  | %   |

| M                            | NTC hot temp (60°C) threshold,                      | Falling                                                                  | 29.7  | 31.2  | 32    | %   |

| V <sub>внот</sub>            | as percentage of VCC                                | Rising                                                                   | 33.9  | 34.4  | 34.9  | %   |

| BOOST MODE                   | OPERATION                                           |                                                                          |       |       |       |     |

| $V_{\text{OTG\_REG\_RANGE}}$ | Boost mode regulation voltage range                 |                                                                          | 3.9   |       | 5.4   | V   |

| V <sub>OTG_REG_STEP</sub>    | Boost mode regulation voltage step                  |                                                                          |       | 100   |       | mV  |

| v                            | Boost mode regulation voltage                       | V <sub>OTG_REG</sub> =5V, V <sub>BAT</sub> =3.8V, I <sub>BUS</sub> =0A   | 4.85  | 5     | 5.15  | V   |

| $V_{\text{OTG\_REG\_ACC}}$   | accuracy                                            | V <sub>OTG_REG</sub> =5.2V, V <sub>BAT</sub> =3.8V, I <sub>BUS</sub> =0A | 5.04  | 5.2   | 5.36  | V   |

| 11/                          |                                                     | V <sub>VBAT</sub> falling,2.8V                                           | 2.7   | 2.8   | 2.9   | V   |

| V                            | Battery voltage exiting boost                       | Hysteresis                                                               |       | 200   |       | mV  |

| V <sub>VBATLOW_</sub> OTG    | mode                                                | V <sub>VBAT</sub> falling,2.5V                                           | 2.4   | 2.5   | 2.6   | V   |

|                              |                                                     | Hysteresis                                                               |       | 300   |       | mV  |

| loro                         | OTG mode output current limit                       | I <sub>OTG</sub> = 1.2A                                                  | 1.2   | 1.4   | 1.6   | Α   |

| $I_{OTG}$                    | O 10 mode output current millt                      | I <sub>OTG</sub> = 0.5A                                                  | 0.5   | 0.6   | 0.72  | Α   |

## INTERNAL USE CONFIDENTIAL, SUBJECT TO CHANGE

| $V_{\text{OTG\_OVP}}$     | OTG overvoltage threshold                          | Rising                                      |     | 5.8 |     | V   |

|---------------------------|----------------------------------------------------|---------------------------------------------|-----|-----|-----|-----|

| VCC LDO                   |                                                    |                                             |     |     |     |     |

| V <sub>VCC</sub>          | V <sub>CC</sub> LDO output voltage                 | V <sub>BUS</sub> =5V,I <sub>VCC</sub> =40mA |     | 4.5 |     | V   |

| I <sub>VCC</sub>          | V <sub>CC</sub> current limiter                    | VBUS=5V, $V_{VCC} = 3.8V$ , Charger disable | 50  |     |     | m   |

| LOGIC IO                  | •                                                  |                                             |     |     |     | 1   |

| V <sub>ILO</sub>          | Input low threshold                                |                                             |     |     | 0.4 | V   |

| V <sub>IHO</sub>          | Input high threshold                               |                                             | 0.9 |     |     | V   |

| /QON TIMING               | •                                                  |                                             |     |     | 1/4 |     |

| t <sub>shipmode</sub>     | /QON low time to turn on BATFET and exit ship mode |                                             | 0.9 |     | 1.3 | S   |

| t <sub>SHIPMODE_DGL</sub> | Enter ship mode delay                              |                                             | 10  | W.  | 15  | s   |

| t <sub>RESET</sub>        | /QON low time to reset BATFET                      |                                             | 8   | 1   | 12  | S   |

| t <sub>RESET_LAST</sub>   | BATFET off time during full system reset           |                                             | 250 |     | 400 | m   |

| DIGITAL CLO               | CK AND WATCHDOG TIMER                              |                                             |     |     |     |     |

| t <sub>WDT</sub>          | Watchdog timer                                     |                                             | 20  | 40  | 60  | S   |

| f <sub>SCL</sub>          | SCL Clock frequency                                |                                             |     |     | 400 | Kŀ  |

| SAFETY TIME               | R                                                  |                                             |     |     |     |     |

| t <sub>TC</sub>           | Safety timer for Trickle charge                    |                                             | 2   | 4   | 6   | hou |

| t <sub>cc/cv</sub>        | Safety timer for CC and CV                         | 12 hours                                    | 6   | 12  | 18  | hou |

| VBUS Power                | up                                                 | C                                           |     |     |     |     |

| t <sub>VAC_OVP</sub>      | V <sub>BUS</sub> OVP reaction time                 |                                             |     | 150 |     | n   |

| t <sub>BADSRC</sub>       | Bad adapter detection duration                     |                                             | 15  | 30  | 45  | m   |

| THERMAL RE                | GULATION and SHUTDOWN                              |                                             |     |     |     |     |

| $T_REG$                   | Thermal regulation temperature                     | Range                                       | 60  |     | 120 | °(  |

| REG                       | The marrogardien temperature                       | Step                                        |     | 20  |     | °(  |

|                           | Thermal shutdown temperature                       |                                             |     | 150 |     | °(  |

| $T_{SD}$                  |                                                    |                                             |     | 30  |     | °(  |

## 10 Feature Description

#### 10.1 Power-On-Reset(POR)

The SC89601A powers internal bias circuits from the higher voltage of VBUS and VBAT. When VBUS rises above  $V_{VBUS\_UVLO}$  or VBAT rises above  $V_{VBAT\_UVLO}$ , the sleep comparator, battery depletion comparator and BATFET driver are active. I2C interface is ready for communication and all the registers are reset to default value. The host can access all the registers after POR.

# 10.2 Device Power Up from Battery without Input Source

If only battery is present and the voltage is above depletion threshold , the BATFET turns on and connects battery to system. The VCC LDO stays off to minimize the quiescent current. The low  $R_{\mbox{\scriptsize DSON}}$  of BATFET and the low quiescent current on BAT minimize the conduction loss and maximize the battery run time.

The device always monitors the discharge current through BATFET (Supplement Mode). When the system is overloaded or shorted ( $I_{BAT} > I_{BATFET\_OCP}$ ), the device turns off BATFET immediately and set BATFET\_DIS bit to indicate BATFET is disabled until the input source plugs in again or one of the methods described in BATFET Enable (Exit Shipping Mode) is applied to re-enable BATFET.

#### 10.3 Power Up from Input Source

When an input source is plugged in, the device checks the input source voltage to turn on VCC LDO and all the bias circuits. It detects and sets the input current limit before the buck converter is started. The power up sequence from input source is as listed:

- 1. Power up VCC LDO

- 2. Poor Source Qualification

- 3. Input Source Type Detection is based on DP/DM to set default input current limit (IINDPM) register or input source type

- 4. Input Voltage Limit Threshold Setting (VINDPM threshold)

- 5. Converter Power-up

#### 10.3.1 Power Up VCC LDO Regulation

The VCC LDO supplies internal bias circuits as well as the HSFET and LSFET gate drive. The VCC also provides bias rail to NTC external resistors. The pull-up rail of STAT can be

connected to VCC as well. The VCC is enabled when all the below conditions are valid:

- V<sub>BUS</sub> above V<sub>VBUSMIN</sub> , above V<sub>BAT</sub> + V<sub>SLEEP</sub> in buck mode

- V<sub>BUS</sub> below V<sub>BAT</sub> + V<sub>SLEEP</sub> in boost mode

- Above conditions are satisfied during 220ms delay

If any one of the above conditions is not valid, the device is in high impedance mode (HIZ) with VCC LDO off. The device draws less than I<sub>VBUS\_HIZ</sub> from VBUS during HIZ state. The battery powers up the system when the device is in HIZ mode.

By setting EN\_HIZ bit to 1 with adapter, the device enters high impedance state (HIZ). In HIZ mode, the system is powered from battery even with good adapter present. The device is in the low input quiescent current state with Q1 RBFET, VCC LDO and the bias circuits off.

#### 10.3.2 Poor Source Qualification

After VCC LDO powers up, the device confirms the current capability of the input source. The input source must meet both of the following requirements in order to start the buck converter:

- VAC voltage below V<sub>VAC\_OV</sub>

- VBUS voltage above V<sub>VBUSMIN</sub> when pulling I<sub>BADSRC</sub> (typical 30 mA)

Once the input source passes all the conditions above, the status register bit VBUS\_GD is set high and the /INT pin is pulsed to signal to the host. If the device fails the poor source detection, it repeats poor source qualification every 2 seconds.

#### 10.3.3 Input Source Type Detection

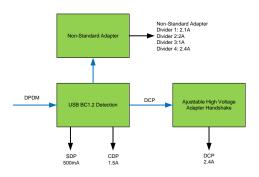

After the VBUS\_GD bit is set and VCC LDO is powered, the device runs input source detection through DP/DM. The SC89601A follows the USB Battery Charging Specification 1.2 (BC1.2) to detect input source (SDP/CDP/DCP) and non-standard adapter through USB DP/DM lines.

After input source type detection is completed, an INT pulse is asserted to the host. in addition, the following registers and pin are changed:

- 1. Input Current Limit (IINDPM) register is changed to set current limit

- 2. PG\_STAT bit is set

- 3. VBUS\_STAT bit is updated to indicate USB or other input source

The host can over-write IINDPM register to change the input current limit if needed. The charger input current is always limited by the IINDPM register.

The SC89601A contains a DP/DM based input source detection to set the input current limit at VBUS plug-in. The DP/DM detection includes standard USB BC1.2 and non-standard adapter. When input source is plugged in, the device starts standard USB BC1.2 detection. The USB BC1.2 is capable to identify Standard Downstream Port (SDP), Charging Downstream Port(CDP) and Dedicated Charging Port (DCP). When the Data Contact Detection (DCD) timer expires, the nonstandard adapter detection is applied to set the input current limit. The non-standard detection is used to distinguish vendor specific adapters based on their unique dividers on the DP/DM pins. If an adapter is detected as DCP, the input current limit is set at 2.4 A. If an adapter is detected as unknown, the input current limit is set at 0.5 A.

Figure 1 USB DP/DM Detection

| rigare roop by Abin Detection |                     |  |  |  |

|-------------------------------|---------------------|--|--|--|

| D+/D- DETECTION               | INPUT CURRENT LIMIT |  |  |  |

| USB SDP                       | 500mA               |  |  |  |

| USB CDP                       | 1.5A                |  |  |  |

| USB DCP                       | 2.4A                |  |  |  |

| Divider 1                     | 2.1A                |  |  |  |

| Divider 2                     | 2A                  |  |  |  |

| Divider 3                     | 1A                  |  |  |  |

| Divider 4                     | 2.4A                |  |  |  |

| Unknown Adapter               | 500mA               |  |  |  |

Table1 Input current limit setting from DP/DM Detection

After the input source detection, DP and DM return to HI-Z.

#### 10.3.4 Input Voltage Limit Threshold Setting

The SC89601A supports wide range of input voltage limit. and provides three methods to set Input Voltage Limit (VINDPM) threshold to facilitate autonomous detection.

1. Absolute VINDPM (FORCE VINDPM=1)

By setting FORCE\_VINDPM bit to 1, the VINDPM threshold setting algorithm is disabled. Register VINDPM is writable and allows host to set the absolute threshold of VINDPM function.

2. Relative VINDPM based on VINDPM\_OS registers (FORCE\_VINDPM=0)

When FORCE\_VINDPM bit is 0 (default), the VINDPM threshold setting algorithm is enabled. The VINDPM register is read only and the charger controls the register by using VINDPM Threshold setting algorithm(VBUS-VINDPM\_OS).

| FORCE_ | VINDPM REGULATION VOLTAGE  |

|--------|----------------------------|

| VINDPM |                            |

| 0      | VBUS-VINDPM_OS             |

| 1      | Register VINDPM(0x0D[6:0]) |

**Table2 VINDPM Function**

#### 10.3.5 Converter Power-Up

After the input current limit is set, the converter is enabled and the HSFET and LSFET start switching. If battery charging is disabled, BATFET turns off. Otherwise, BATFET stays on to charge the battery.

The SC89601A provides soft-start when system rail is ramped up. When the system rail is below 2.2 V, the input current is limited to is to the lower of 200 mA or IINDPM register setting. After the system rises above 2.2 V, the device limits input current to the value set by IINDPM register.

As a battery charger, the device deploys a highly efficient 1.5 MHz step-down switching regulator. The fixed frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current and temperature, simplifying output filter design.

The SC89601A switches to PFM control at light load or when battery is below minimum system voltage setting or charging is disabled.

#### 10.4 Boost Mode Operation From Battery

The SC89601A supports boost converter operation to deliver

#### SOUTHCHIP SEMICONDUCTOR

power from the battery to other portable devices through USB port. The boost mode output current rating meets the USB On-The-Go 500 mA output requirement. The maximum output current is up to 1.4 A. The boost operation can be enabled if the conditions are valid:

- 1. VBAT above  $V_{\text{VBATLOW\_OTG}}$

- 2. VBUS less than VBAT + VSLEEP

- 3. Boost mode operation is enabled

- 4. Battery is not in BCOLD and BHOT.

- 5. Above conditions are satisfied during 30ms delay.

During boost mode, the status register VBUS\_STAT bits is set to 111, the VBUS output is I2C programmed (default) and the output current can reach up to 1.4 A, selected through I2C (BOOST\_LIM bit). The boost output is maintained when BAT is above VVBATLOW OTG threshold.

When OTG is enabled, the device starts up with PFM and later transits to PWM to minimize the overshoot. The PFM\_DIS bit can be used to prevent PFM operation in either buck or boost configuration.

#### 10.5 Host Mode and Default Mode

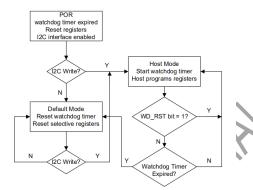

The SC89601A is a host controlled charger, but it can operate in default mode without host management. In default mode, the device can be used as an autonomous charger with no host or while host is in sleep mode.

When the charger is in default mode, WATCHDOG\_FAULT bit is HIGH. When the charger is in host mode, WATCHDOG\_FAULT bit is LOW.

After power-on-reset, the device starts in default mode with watchdog timer expired, or default mode. All the registers are in the default settings. in default mode, the device keeps charging the battery with default 10-hour fast charging safety timer. At the end of the 10-hour, the charging is stopped and the buck converter continues to operate to supply system load.

Writing a 1 to the WD\_RST bit transitions the charger from default mode to host mode. All the device parameters can be programmed by the host. To keep the device in host mode, the host has to reset the watchdog timer by writing 1 to WD\_RST bit before the watchdog timer expires (WATCHDOG\_FAULT bit is set), or disable watchdog timer by setting WATCHDOG bits = 00.

When the watchdog timer expires (WATCHDOG\_FAULT bit = 1), the device returns to default mode and all registers are reset to default values except IINDPM, VINDPM, BATFET\_RST\_EN, BATFET\_DLY, and BATFET\_DIS bits.

Figure 2 Watch dog

#### 10.6 NVDC Power Path Management

The SC89601A accommodates a wide range of input sources from USB, wall adapter, to car charger. The device provides automatic power path selection to supply the system (VSYS) from input source (VBUS), battery (VBAT), or both.

#### 10.6.1 Battery Charging Management

The SC89601A charges 1-cell Li-lon battery with up to 3.0-A charge current for high capacity tablet battery. The 11-m $\Omega$  BATFET improves charging efficiency and minimize the voltage drop during discharging.

#### 10.6.1.1 Autonomous Charging Cycle

With battery charging is enabled (CHG\_CONFIG bit = 1 and /CE pin is LOW), the device autonomously completes a charging cycle without host involvement. The host can always control the charging operations and optimize the charging parameters by writing to the corresponding registers through I2C.

| Charging Parameters         | Default Value            |  |  |  |

|-----------------------------|--------------------------|--|--|--|

| Charging Voltage            | 4.208V                   |  |  |  |

| CC Current                  | 2.040A                   |  |  |  |

| TC Current                  | 120mA                    |  |  |  |

| Termination Current         | 270mA                    |  |  |  |

| Battery Temperature Profile | JEITA                    |  |  |  |

| Safety Timer                | TC:4hours, CC/CV:12hours |  |  |  |

**Table 3 Charging Parameter Default Setting**

A new charge cycle starts when the following conditions are valid:

- Converter starts

- Battery charging is enabled(CHG\_CONFIG bit =1, Icc is not 0A and /CE is low)

- No NTC COLD or HOT fault

- No safety timer fault

- BATFET is not forced to turn off(BATFET\_DIS bit=0)

The charger device automatically terminates the charging cycle when the charging current is below termination threshold, battery voltage is above recharge threshold, and device not is in DPM mode or thermal regulation. When a fully charged battery is discharged below recharge threshold (selectable through VRECHG bit), the device automatically starts a new charging cycle. After the charge is done, toggle CE pin or CHG\_CONFIG bit can initiate a new charging cycle. Adapter removal and re plug will also start a new charging cycle.

The STAT output indicates the charging status: charging (LOW), charging complete or charge disable (HIGH) or charging fault (Blinking). The STAT output can be disabled by setting EN\_ICHG\_MON bits = 11. in addition, the status register (CHRG\_STAT) indicates the different charging phases: 00-charging disable, 01-precharge, 10-fast charge (constant current) and constant voltage mode, 11-charging done. Once a charging cycle is completed, an INT is asserted to notify the host.

| STAT status  | IC working status                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------|

| Low          | Normal charging (TC/CC/CV/Recharge)                                                                                        |

| High         | End of charging (EOC, topoff timer maybe running), charge disable, sleep mode, Boost Mode                                  |

| 1Hz Blinking | Charge suspend(VBUS OVP, NTC COLD/HOT, Safety timer out, system over voltage, VBAT OVP).  Boost Mode suspend(NTC/COLD/HOT) |

**Table 4 STAT Pin status**

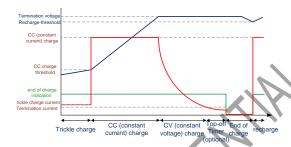

#### 10.6.1.2 Battery Charging Profile

The SC89601A charges the battery in six phases: battery short, TC,CC,CV,EOC and Recharge. At the beginning of a charging cycle, the device checks the battery voltage and regulates current and voltage accordingly.

| $V_{VBAT}$ | Charging current   | Default value | CHRG_STAT |

|------------|--------------------|---------------|-----------|

| <2.2V      | I <sub>SHORT</sub> | 50mA          | 01        |

| 2.2V to 3V | I <sub>TC</sub>    | 120mA         | 01        |

| >3V        | Icc                | 2.040A        | 10        |

**Table5 Charging Current Setting**

If the charger device is in DPM regulation or thermal regulation during charging, the actual charging current will be

less than the programmed value. in this case, termination is temporarily disabled and the charging safety timer is doubled.

Figure 3 Battery Charging Profile

#### 10.6.1.3 End of Charge

The SC89601A terminates a charge cycle when the battery voltage is above recharge threshold, and the current is below termination current. After the charging cycle is completed, the BATFET turns off. The converter keeps running to power the system, and BATFET can turn on again to engage Supplement Mode.

When termination occurs, the status register CHRG\_STAT is set to 11, and an INT pulse is asserted to the host. Termination is temporarily disabled when the charger device is in input current, voltage or thermal regulation. Termination can be disabled by writing 0 to EN\_TERM bit prior to charge termination.

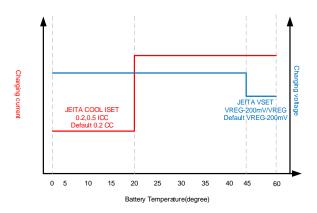

#### 10.6.1.4 NTC in Buck mode

The SC89601A monitors the battery cells' temperature through NTC pin. It monitors the NTC voltage. Once it detects the temperature is below 0°C or higher than 60°C, the IC transitions to shutdown mode. Below shows the NTC operation summary. NTC function can be also disabled through shorting the pin to ground.

| V <sub>NTC</sub>                                          | Temperature     | Operation           |

|-----------------------------------------------------------|-----------------|---------------------|

| V <sub>NTC</sub> > V <sub>COLD</sub>                      | T < 0°C         | Stop charging       |

| V <sub>COLD</sub> >V <sub>NTC</sub> > V <sub>COOL</sub>   | 0°C < T < 10°C  | 0.2*I <sub>CC</sub> |

| V <sub>COOL</sub> >V <sub>NTC</sub> > V <sub>WARM</sub>   | 10°C < T < 45°C | Normal charging     |

| V <sub>WARM</sub> > V <sub>NTC</sub> > V <sub>HOT</sub>   | 45°C < T < 60°C | CV/4.1V             |

| V <sub>HOT</sub> > V <sub>NTC</sub> > V <sub>DISNTC</sub> | T > 60°C        | Stop charging       |

| V <sub>DISNTC</sub> > V <sub>NTC</sub> >=0                |                 | Disable NTC         |

**Table6 NTC Function**

Figure 4 NTC function

#### 10.6.1.5 NTC in Boost mode

For battery protection during boost mode, the SC89601A monitors the battery temperature to be within the  $V_{\text{BCOLD}}$  to  $V_{\text{BHOT}}$  thresholds. When temperature is outside of the temperature thresholds, the boost mode is suspended. In additional, VBUS\_STAT bits are set to 000 and NTC\_FAULT is reported. Once temperature returns within thresholds, the boost mode is recovered and NTC\_FAULT is cleared.

#### 10.6.1.6 Safety Timer

The SC89601A has built-in safety timer to prevent extended charging cycle due to abnormal battery conditions. The safety timer is 4 hours when the battery is below  $V_{TC}$  threshold and 12 hours when the battery is higher than  $V_{TC}$  threshold.

The user can program CC/CV charge safety timer through I2C (CHG\_TIMER bits). When safety timer expires, the fault register CHRG\_FAULT bits are set to 11 and an INT is asserted to the host. The safety timer feature can be disabled through I2C by setting EN\_TIMER bit.

During input voltage, current, JEITA cool/warm or thermal regulation, the safety timer will double as the setting value.-The timer double function can be disable by writing 0 to TMR2X\_EN bit.

During the fault(BAT\_FAULT,NTC\_FAULT), timer is suspended. Once the fault goes away, timer resumes. If user stops the current charging cycle, and start again, timer gets reset (toggle CE pin or CHRG\_CONFIG bit).

#### 10.6.2 NVDC Architecture

The SC89601A deploys Narrow VDC architecture (NVDC) with BATFET separating system from battery. The minimum system voltage is set by  $V_{\text{SYS\_MIM}}$  bits. Even with a fully depleted battery, the system is regulated above the minimum system voltage.

When the battery is below minimum system voltage setting, the BATFET operates in linear mode (LDO mode), and the system is typically 180 mV above the minimum system voltage setting. As the battery voltage rises above the minimum system voltage, BATFET is fully on and the voltage difference between the system and battery is the  $V_{DS}$  of BATFET.

When the battery charging is disabled and above minimum system voltage setting or charging is terminated, the system is always regulated at typically 50mV above battery voltage. The status register VSYS\_STAT bit goes high when the system is in minimum system voltage regulation.

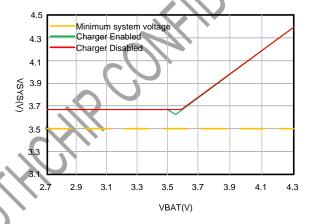

Figure 5 System Voltage vs Battery Voltage

#### 10.6.3 Dynamic Power Management

To meet maximum current limit in USB spec and avoid over loading the adapter, the device features Dynamic Power management (DPM), which continuously monitors the input current and input voltage. When input source is over-loaded, either the current exceeds the input current limit (IIDPM) or the voltage falls below the input voltage limit (VINDPM). The device then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit.

When the charge current is reduced to zero, but the input source is still overloaded, the system voltage starts to drop. Once the system voltage falls below the battery voltage, the device automatically enters the supplement mode where the BATFET turns on and battery starts discharging so that the system is supported from both the input source and battery.

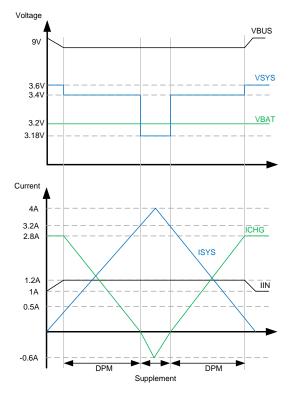

During DPM mode, the status register bits VDPM\_STAT (VINDPM) or IDPM\_STAT (IINDPM) goes high. Below figure shows the DPM response with 9-V/1.2-A adapter, 3.2-V battery, 2.8-A charge current and 3.5-V minimum system voltage setting.

Figure 6 DPM Response

#### 10.6.4 Supplement Mode

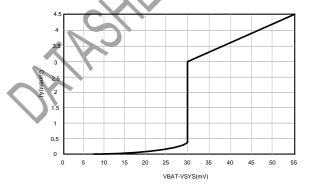

When the system voltage falls below the battery voltage, the BATFET turns on and the BATFET gate is regulated the gate drive of BATFET so that the minimum BATFET V<sub>DS</sub> stays at 30 mV when the current is low. This prevents oscillation from entering and exiting the supplement mode.

As the discharge current increases, the BATFET gate is regulated with a higher voltage to reduce  $R_{\rm DSON}$  until the BATFET is in full conduction. At this point onwards, the BATFET  $V_{\rm DS}$  linearly increases with discharge current. BATFET turns off to exit supplement mode when the battery is below battery depletion threshold.

Figure 7 BATFET V-I Curve

#### 10.7 Shipping Mode and /QON Pin

#### 10.7.1 BATFET Disable Mode(Shipping Mode)

To extend battery life and minimize power when system is powered off during system idle, shipping, or storage, the device can turn off BATFET so that the system voltage is zero to minimize the battery leakage current. When the host set BATFET\_DIS bit, the charger can turn off BATFET immediately or delay by tsm\_DLY as configured by BATFET\_DLY bit.

#### 10.7.2 BATFET Enable(Exit Shipping Mode)

When the BATFET is disabled (in shipping mode) and indicated by setting BATFET\_DIS, one of the following events can enable BATFET to restore system power:

- 1. Plug in adapter

- 2. Clear BATFET\_DIS bit

- 3. Set REG\_RST bit to reset all registers including BATFET\_DIS bit to be default 0

- 4. A logic high to low transition on /QON pin with tshipmode deglitch time to enable BATFET to exit shipping mode

#### 10.7.3 BATFET Full System Reset

The BATFET functions as a load switch between battery and system when input source is not plugged—in. By changing the state of BATFET from on to off, systems connected to SYS can be effectively forced to have a power-on-reset. The /QON pin supports push-button interface to reset system power without host by changing the state of BATFET.

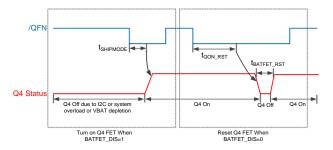

When the /QON pin is driven to logic low for  $t_{QON\_RST}$  while input source is not plugged in and BATFET is enabled (BATFET\_DIS = 0), the BATFET is turned off for  $t_{BATFET\_RST}$  and then it is re-enabled to reset system power. This function can be disabled by setting BATFET\_RST\_EN bit to 0.

#### 10.7.4 /QON Pin Operation

The /QON pin incorporates two functions to control BATFET.

- 1. BATFET Enable: A /QON logic transition from high to low with longer than t<sub>SHIPMODE</sub> deglitch turns on BATFET and exit shipping mode.

- 2. BATFET Reset: When /QON is driven to logic low by at least tQON\_RST while adapter is not plugged in (and BATFET\_DIS = 0), the BATFET is turned off for tBATFET\_RST. The BATFET is re-enabled after tBATFET\_RST duration. This function allows systems connected to SYS to have power-on-reset. This function can be disabled by setting

BATFET\_RST\_EN bit to 0.

Figure 8 /QON Timing

#### 10.8 Power Good Indicator

The PG\_STAT bit goes HIGH to indicate a good input source when:

- VBUS above V<sub>VBUS\_UVLO</sub> below V<sub>VAC\_OVP</sub>

- VBUS above VBAT+V<sub>SLEEP</sub> (not in sleep)

- VBUS above V<sub>VBUSMin</sub> (typical 3.8 V) when I<sub>BADSRC</sub> (typical 30 mA) current is applied (not a poor source)

- Completed input Source Type Detection

#### 10.9 /INT

The SC89601A also has an alert mechanism that can output an interrupt signal via INT to notify the system of the operation by outputting a 256µs low-state INT pulse. All of the below events can trigger an INT output:

- USB/adapter source identified

- Good input source detected as described in power good indicator

- Input Removed

- Charge Complete

- VINDPM/IINDPM event detected(can be masked)

- Watchdog timer out, Safety timer out, Boost fault (VBUS overload hiccup mode, VBUS OVP, VBAT

VVBATLOW\_OTG), VBAT OVP, NTC COLD/HOT(Buck and Boost mode), Thermal shutdown, VBUS OVP, VBUS

When a fault occurs, the charger device sends out INT and keeps the fault state in REG until the host reads the fault register. The INT signal can be masked when the corresponding control bit is set. When a fault/status change occurs, the charger device sends out an INT pulse and keeps the state in REGOC until the host reads the registers. To read the current status, the host has to read REGOC two times consecutively. The first read reports the pre-existing register

status and the second read reports the current register status.

#### 10.10 Protections

#### 10.10.1 Voltage and Current Monitoring in Buck Mode

#### 10.10.1.1 Input Over voltage (ACOVP)

If VBUS voltage exceeds 14.2V, the device stops switching immediately. During input over voltage event (ACOV), the fault register CHRG\_FAULT bits are set to 01. An INT pulse is asserted to the host. The device will automatically resume normal operation once the input voltage drops back below the OVP threshold.

#### 10.10.1.2 System Over voltage Protection(SYSOVP)

The charger device clamps the system voltage during load transient so that the components connect to system would not be damaged due to high voltage. SYSOVP threshold is 350 mV above minimum system regulation voltage when the system is regulated at V<sub>SYS\_MIN</sub> and above battery regulation voltage when battery charging is terminated. Upon SYSOVP, converter stops switching immediately to clamp the overshoot. The charger provides 30 mA discharge current to bring down the system voltage.

#### 10.10.2 Voltage and Current Monitoring in Boost Mode

#### 10.10.2.1 VBUS Soft Start

When the boost function is enabled, the device soft-starts boost mode to avoid inrush current.

#### 10.10.2.2 VBUS Over Load Protection

The device monitors boost output voltage and other conditions to provide output short circuit and over voltage protection. The Boost build in accurate constant current regulation to allow OTG to adaptive to various types of load. If short circuit is detected on VBUS, the Boost turns off and retry with hiccup function until the host to clear the OTG CFG.

#### 10.10.2.3 VBUS Over Voltage Protection

When the VBUS voltage rises above regulation target and exceeds  $V_{\text{OTG\_OVP}}$ , the device enters over voltage protection which stops switching, clears OTG\_CONFIG bit and exits boost mode. At Boost over voltage duration, the fault register bit (BOOST\_FAULT) is set high to indicate fault in boost operation. An INT is also asserted to the host.

#### SOUTHCHIP SEMICONDUCTOR

#### 10.10.3 Thermal Regulation and Thermal Shutdown

#### 10.10.3.1 Thermal Protection in Buck Mode

The SC89601A monitors the internal junction temperature T<sub>J</sub> to avoid overheat the chip and limits the IC surface temperature in buck mode. When the internal junction temperature exceeds thermal regulation limit, the device lowers down the charge current. During thermal regulation, the actual charging current is usually below the programmed battery charging current. Therefore, termination is disabled, the safety timer runs at half the clock rate, and the status register THERM\_STAT bit goes high.

Additionally, the device has thermal shutdown to turn off the converter and BATFET when IC surface temperature exceeds T<sub>SHUT</sub>. The fault register CHRG\_FAULT is set to 1 and an INT is asserted to the host. The BATFET and converter is enabled to recover when IC temperature is T<sub>SHUT\_HYS</sub> below T<sub>SHUT</sub>.

#### 10.10.3.2 Thermal Protection in Boost Mode

The device monitors the internal junction temperature to provide thermal shutdown during boost mode. When IC junction temperature exceeds  $T_{SHUT}$ , the boost mode is disabled by setting OTG\_CONFIG bit low and BATFET is turned off. When IC junction temperature is below  $T_{SHUT}$ - $T_{SHUT\_HYS}$ , the BATFET is enabled automatically to allow system to restart and the host can re-enable OTG\_CONFIG bit to recover.

#### 10.10.4 Battery Protection

#### 10.10.4.1 Battery Over voltage Protection(VBATOVP)

The battery overvoltage limit is clamped at 4% above the battery regulation voltage. When battery over voltage occurs, the charger device immediately disables charging. The fault register BAT\_FAULT bit goes high and an INT is asserted to the host.

### 10.10.4.2 Battery Over discharge Protection

When battery is discharged below  $V_{BAT\_DPL}$ , the BATFET is turned off to protect battery from over discharge. To recover from over-discharge latch-off, an input source plug-in is required at VBUS. The battery is charged with  $I_{SHORT}$  (typically 50 mA) current when the VBAT <  $V_{SHORT}$ .

#### 10.10.4.3 System Over current Protection

When the system is shorted or significantly overloaded (IBAT > IBATOCP) and the current exceeds BATFET over current limit, the BATFET latches off. Section BATFET Enable (Exit Shipping Mode) can reset the latch-off condition and turn on

BATFET.

### 10.11 I2C Interface

#### 10.11.1 I2C Interface

The IC features I2C interface, so the MCU or controller can control the IC flexibly. The 7-bit I2C address of the chip is 0x6B. The SDA and SCL pins are open drain and must be connected to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The I2C interface supports both standard mode (up to 100kbits) and fast mode (up to 400k bits with 5 k $\Omega$  pull up resistor at SCL pin and SDA pin respectively).

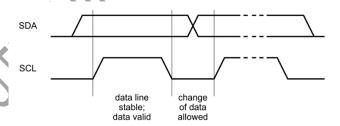

#### 10.11.2 Data Validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure9 Bit transfer on the I2C bus

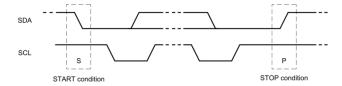

#### 10.11.3 START and STOP Conditions

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

Figure 10 START and STOP conditions

#### SOUTHCHIP SEMICONDUCTOR

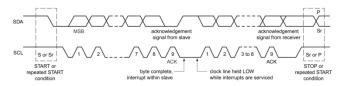

#### 10.11.4 Byte Format

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. Data is transferred with the Most Significant Bit (MSB) first. If a slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

Figure 11 Data transfer on the I2C bus

## 10.11.5 Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. During data is transferred, the master can either be the transmitter or the receiver. No matter what it is, the master generates all clock pulses, including the acknowledge ninth clock pulse.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse.

When SDA remains HIGH during this ninth clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

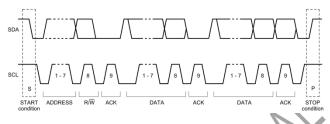

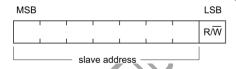

## 10.11.6 The slave address and R/W bit

Data transfers follow the format shown in below. After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W) — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

Figure 12 complete data transfer

Figure 13 The first byte after the START procedure

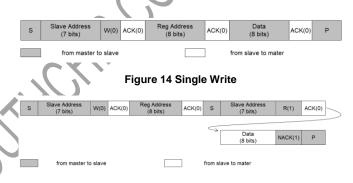

#### 10.11.7 Single Read and Write

Figure 15 Single Read

If the register address is not defined, the charger IC send back NACK and go back to the idle state.

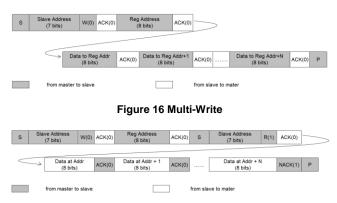

#### 10.11.8 Multi-Read and Multi-Write

The IC supports multi-read and multi-write for continuous registers.

Figure 17 Multi-Read

## 11 Application information (TBD)

### INTERNAL USE CONFIDENTIAL, SUBJECT TO CHANGE

## 12 Register Map

| Addr       | Register        | Туре | Default value<br>@POR | Bit 7            | Bit 6           | Bit 5          | Bit 4                | Bit 3       | Bit 2                | Bit 1                | Bit 0                    |

|------------|-----------------|------|-----------------------|------------------|-----------------|----------------|----------------------|-------------|----------------------|----------------------|--------------------------|

| <u>00H</u> | INPUT CONTROL   | R/W  | 0X001000              | EN_HIZ           | RESERVED        |                |                      |             | IIN_DPM              |                      |                          |

| <u>01H</u> | DPDM CONTROL1   | R/W  | XXXXXXX1              |                  | RESERVED        |                |                      | RESERVED    |                      | RESERVED             | VINDPM_OS                |

| <u>02H</u> | DPDM CONTROL2   | R/W  | XXXXXX0X              | RESERVED         | RESERVED        | RESERVED       | RESERVED             | RESERVED    | RESERVED             | FORCE_DPDM           | RESERVED                 |

| <u>03H</u> | SYSTEM CONTROL1 | R/W  | X0011010              | RESERVED         | WD_RST          | OTG_CFG        | CHG_CFG              |             | V <sub>SYS_MIN</sub> |                      | V <sub>BAT_OTG_LOW</sub> |

| <u>04H</u> | ICC             | R/W  | XX100010              | RESERVED         | RESERVED        |                |                      | Ula.        | lcc                  |                      |                          |

| <u>05H</u> | ITC & ITERM     | R/W  | 00010100              |                  | ŀ               | тс             |                      | (           |                      | I <sub>TERM</sub>    |                          |

| <u>06H</u> | VBAT_REG        | R/W  | 01011110              |                  |                 |                | V <sub>BAT_REG</sub> | U           |                      | V <sub>BAT_LOW</sub> | V <sub>RECHG</sub>       |

| <u>07H</u> | SYSTEM CONTROL2 | R/W  | 10011101              | EN_TERM          | STAT_DIS        |                | Two                  | EN_TIMER    | Т                    | CHG                  | JEITA_ISET               |

| <u>08H</u> | TREG            | R/W  | XXXXXX11              | RESERVED         | RESERVED        | RESERVED       | RESERVED             | RESERVED    | RESERVED             | -                    | ΓREG                     |

| <u>09H</u> | SYSTEM CONTROL3 | R/W  | X10001XX              | RESERVED         | TMR2X_EN        | BATFET_DI<br>S | JEITA_ISET_WA<br>RM  | BATFET_DLY  | BATFET_RST_E<br>N    | RESERVED             | RESERVED                 |

| <u>0AH</u> | BOOST CONTROL   | R/W  | 10110011              |                  | V <sub>B</sub>  | DOST           |                      | PFM_OTG_DIS |                      | Івооѕт               |                          |

| <u>0BH</u> | STAT1           | R    | XXXXXXX               |                  | VBUS_STAT       | . 1/1          | CHR                  | G_STAT      | PG_STAT              | RESERVED             | VSYS_STAT                |

| <u>och</u> | STAT2           | R    | xxxxxxx               | WD_FAULT         | BOOST_FAUL<br>T | CHR            | G_FAULT              | BAT_FAULT   |                      | NTC_FAULT            |                          |

| <u>odh</u> | VINDPM          | R/W  | 00010010              | FORCE_VIND<br>PM | ~ (             | 2              |                      | VINDPM      |                      |                      |                          |

| <u>0EH</u> | STAT3           | R    | xxxxxxx               | THERMAL_ST<br>AT | RESERVED        | RESERVED       | RESERVED             | RESERVED    | RESERVED             | RESERVED             | RESERVED                 |

| <u>11H</u> | STAT4           | R    | XXXXXXXX              | VBUS_GD          | RESERVED        | RESERVED       | RESERVED             | RESERVED    | RESERVED             | RESERVED             | RESERVED                 |

| <u>13H</u> | STAT5           | R    | XXXXXXXX              | VINDPM_STAT      | IINDPM_STAT     | RESERVED       | RESERVED             | RESERVED    | RESERVED             | RESERVED             | RESERVED                 |

| <u>14H</u> | PN              | R    | 0X101XXX              | REG_RST          | RESERVED        |                | PART NUMBER          | 3           | RESERVED             | RESERVED             | RESERVED                 |

## REG 00H(Back to map)

|   | Mode | Bit Name | Default<br>value<br>@POR | Reset by<br>REG_RST | Reset by<br>WTD | Description      | Notes                                                                                                                                                               |

|---|------|----------|--------------------------|---------------------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      |          |                          |                     |                 | Enable HI-Z Mode | Reset to default value                                                                                                                                              |