# **AUDIO SYSTEM CONTROL MCU WITH ANALOG RADIO FUNCTION**

### **DESCRIPTION**

SC9307P is a SOC based on Silan's 8-bit MCU SC65PX for analog radio DFR control with low power dissipation. Built-in LCD driver which can drive 34 configurable I/O ports and three 8-bit counters, two of which can be combined to achieve 16 timing length; Built-in real time clock ensures the system uninterrupted counting when it is in sleep state; 11 interrupt sources, including four external interrupts, enabling the system to respond quickly to internal and external events. Multimode optional serial communication circuits greatly increase the system's scalability. Built-in 3.2MHz RC oscillator with external 75KHz oscillator can achieve the perfect balance between power and speed. In high speed application, it can extend external high frequency crystal through PC.4/5 pin, maximum up to 6MHz.

# **APPLICATIONS**

\* Clock movement

# FEATURES (Note)

\* Memory384-byte data memory8K-byte program memory (OTP)

\* I/O configuration 34 general-purpose I/O, 18 of which can be connected to pull-up resistor, open-drain output available.

www.DataSheet#L8-bit timer/counter T0/T1/T2

Timing time can be set by program

External events counting

Arbitrary clock frequency output

T0/T1 can be used as 16-bit counter

\* UART serial communication [port2-line asynchronous communication

Communicate rate slectable

\* A/D converter

4-channels with 8-bit conversion precision

External reference voltage selectable

Battery voltage monitor

\* Clock source

External clock source: 75KHz oscillator

Built-in RC oscillator: 3.2MHz;

Extension oscillator: 2~6MHz(VDD>2.4V@4MHz)

\* RTC

Year/month/day display

Provide BCD code data directly

Leap year auto adjust

Timing alarm

\* Local oscillator frequency counting circuit

Local oscillator:

FM frequency range: 30MHz~150MHz AM frequency range: 0.5MHz~30MHz Counter: 16-bit, gate time 1/4/8ms

\* Built-in voltage reference

VREF=1.23V ± 5%

\* Interrupt source

5 external interrupts, maskable 6 internal interrupts, maskable

Operating voltage range: 3.0~3.6V

# **ORDERING INFORMATION**

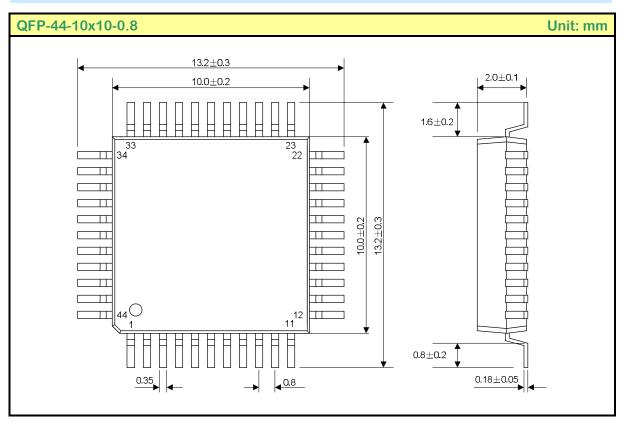

| Part No. | Package          | Marking | Material | Packing |

|----------|------------------|---------|----------|---------|

| SC9307P  | QFP-44-10×10-0.8 | SC9307P | Pb-free  | Tray    |

# **RESOURCE ALLOCATION**

| Part No. | Timer | ADC channel | KBI | UART | GPIO | External interrupt |

|----------|-------|-------------|-----|------|------|--------------------|

| SC9307P  | 3     | 4           | 3   | 1    | 34   | 4                  |

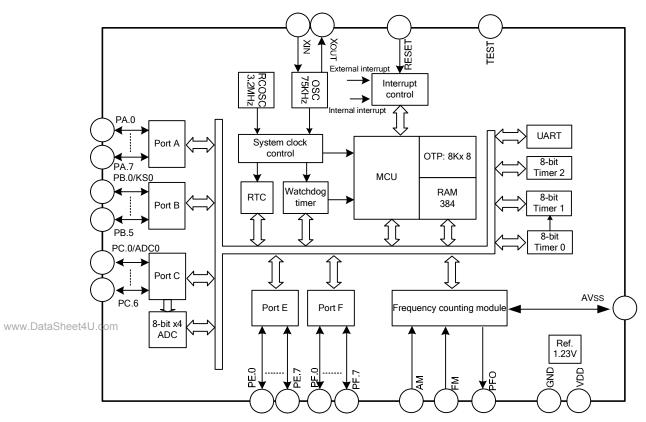

# **BLOCK DIAGRAM**

Note: Pin VPP can be diplexed as RESET, when program the OTP memory, this pin is connected to 12V.

# **ABSOLUTE MAXIMUM RATINGS**

| Characteristics               | Symbol           | Ratings                   | Unit |

|-------------------------------|------------------|---------------------------|------|

| Supply Voltage                | $V_{DD}$         | -0.3~5.5                  | V    |

| Input Voltage (All I/O Pins)  | V <sub>I1</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    |

| Input Voltage (RESET)         | V <sub>I1</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    |

| Output Voltage                | Vo               | -0.3~V <sub>DD</sub> +0.3 | V    |

| Output High Level Current     | Іон              | -15                       | mA   |

| Output Low Level Current      | loL              | 30                        | mA   |

| Operating Ambient Temperature | T <sub>amb</sub> | -20~+75                   | °C   |

| Storage Temperature           | Tstg             | -40~+125                  | °C   |

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, Tamb=25 °C,VDD=3.3V)

| Characteristics |                                               | Symbol           | Test conditions                                 | Min. | Тур.  | Max. | Unit |  |  |

|-----------------|-----------------------------------------------|------------------|-------------------------------------------------|------|-------|------|------|--|--|

|                 | Operating Voltage                             | VDD              |                                                 | 3.0  | 3.3   | 3.6  | V    |  |  |

|                 |                                               | IQ1              | OSC 75KHz stop, CPU Clk stop                    |      |       | 1    | μΑ   |  |  |

|                 | Quiescent Current                             | lQ2              | OSC=75KHz,CPU Clk=75KHz Sleep<br>(Note 1)       |      | 5.5   |      | μΑ   |  |  |

|                 | Operating Current                             | IDD              | OSC=75KHz,CPU Clk=3.2MHz, all the modules start |      | 1.7   | 3.0  | mA   |  |  |

|                 | Innert I Ent Maltana                          | VIH1             | PA/B/C 2.4                                      |      | -     |      | .,   |  |  |

|                 | Input High Voltage                            | VIH2             | PE/F                                            | 2.0  | -     |      | V    |  |  |

|                 | Input Low Voltage                             | VIL1             | PA/B/C                                          |      | -     | 1.0  | V    |  |  |

| www.DataS       |                                               | VIL2             | PE/F                                            |      | -     | 1.0  |      |  |  |

|                 | Output High Voltage                           | VOH1             | VDD=3V,PA/B/C,IOH=-1mA                          | 2.8  |       |      | V    |  |  |

|                 |                                               | Voh2             | VDD=3V,PE/F,IOH=-1mA 2.5                        |      |       |      | V    |  |  |

|                 | Output Low Voltage                            | VOL1             | V <sub>DD</sub> =3V,PA/B/C,IOH=1mA              |      |       | 0.2  | V    |  |  |

|                 | Output Low Voltage                            | VOL2             | VDD=3V,PE/F,IOH=1mA                             |      |       | 0.2  |      |  |  |

|                 | Input High Leakage Current                    | ILIH             | VIN=VDD, all input pins                         |      |       | 1    |      |  |  |

|                 | Input Low Leakage Current                     | ILIL             | VIN=0V,all input pins                           |      |       | 1    | μΑ   |  |  |

|                 | 75KHz Crystal Oscillator<br>Feedback Resistor | Rosc             | VDD =3.0V,XIN=VDD, XOUT=0V                      | 3000 | 6000  | 9000 | ΚΩ   |  |  |

|                 |                                               | RL1              | VIN(FM/AM)=VDD 10.5                             |      | 10.5  |      | 140  |  |  |

|                 | Pull-Down Resistor                            | RL2              | VDD=3.0V,Test = VDD                             |      | 83 KΩ |      | K12  |  |  |

|                 | Dull Ha Daniete a                             | R <sub>H</sub> 1 | V <sub>DD</sub> =3.0V,V <sub>IN</sub> =0,PA/B/C |      | 25    |      |      |  |  |

|                 | Pull-Up Resistor                              | R <sub>H2</sub>  | VDD=3.0V,Vreset = 0                             |      | 67    |      | ΚΩ   |  |  |

Note1: Only 75KHz crystal oscillator and RTC are working.

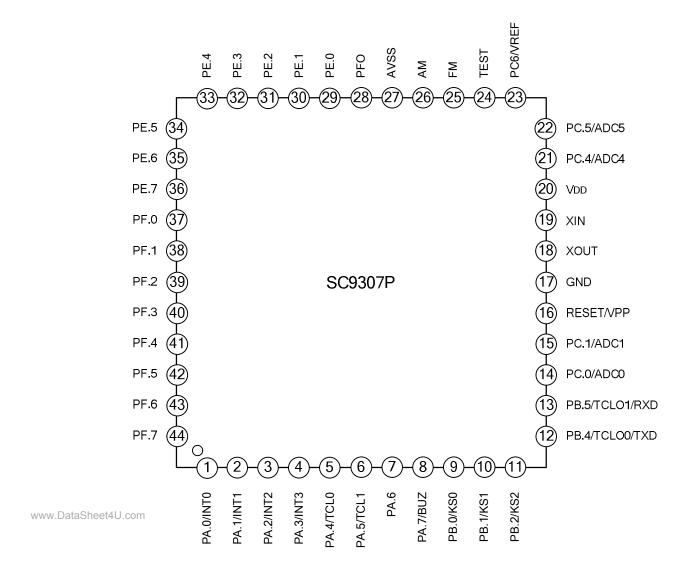

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin No.              | Pin Name | Diplex pin | I/O      | Pin Descriptions                                              |

|----------------------|----------|------------|----------|---------------------------------------------------------------|

| 1                    | PA.0     | INT0       |          |                                                               |

| 2                    | PA.1     | INT1       |          |                                                               |

| 3                    | PA.2     | INT2       |          |                                                               |

| 4                    | PA.3     | INT3       |          |                                                               |

| 5                    | PA.4     | TCL0       |          |                                                               |

| 6                    | PA.5     | TCL1       |          | General input / output;                                       |

| 7                    | PA.6     | _          | I/O      | 8bit read/write;                                              |

| 8                    | PA.7     | BUZ        |          | Configurable bit operation.                                   |

| 9                    | PB.0     | KS0        |          |                                                               |

| 10                   | PB.1     | KS1        |          |                                                               |

| 11                   | PB.2     | KS2        |          |                                                               |

| 12                   | PB.4     | TCLO0      |          |                                                               |

| 13                   | PB.5     | TCLO1      |          |                                                               |

| 14                   | PC.0     | ADC0       | I/O      | General input / output;                                       |

| 15                   | PC.1     | ADC1       | AD input | Configurable bit operation.                                   |

| 16                   | RESET    | VPP        |          | System reset pin                                              |

| 17                   | GND      | _          | _        | Digital ground                                                |

| 18                   | Xout     | _          | 0        | Low frequency oscillator output                               |

| 19                   | XIN      | _          | I        | Low frequency oscillator input                                |

| 20                   | Vdd      | _          | _        | Digital power supply                                          |

| 21                   | PC.4     | ADC4       | I/O      | General input / output; Configurable bit operation.           |

| 22                   | PC.5     | ADC5       | AD input | PC4/5 can also be used as high speed crystal interface;       |

| Sheet4 <b>23</b> com | PC.6     | VREF       | I/O      | General input / output; ADC reference input                   |

| 24                   | TEST     | _          | _        | Test enable pin, internal pull-down resistor                  |

| 25                   | FM       | _          | I        | FM signal input                                               |

| 26                   | AM       | _          | I        | AM signal input                                               |

| 27                   | AVSS     | _          | _        | Analog ground                                                 |

| 28                   | PFO      | _          | 0        | Programmable frequency output, can be used for buzzer driving |

| 29~36                | PE.0~7   | _          | I/O      | General input / output                                        |

| 37~44                | PF.0~7   | PE.0~7     | I/O      | General input / output                                        |

www.DataS

## **DIPLEX PIN DESCRIPTION**

| Pin no. | Diplex pin | I/O | Description                                                     |  |

|---------|------------|-----|-----------------------------------------------------------------|--|

| 12      | TXD        | 0   | Serial communication data output                                |  |

| 13      | RXD        | 1   | Serial communication data input                                 |  |

| 1-4     | INT0-INT3  | 1   | External interrupt input                                        |  |

| 5       | TCL0       | 1   | External counting pulse/clock input of timer 0                  |  |

| 6       | TCL1       | 1   | External counting pulse/clock input of timer 1                  |  |

| 8       | BUZ        | 0   | Buzzer signal output                                            |  |

| 9~11    | KS0-KS2    | 1   | Key scan input, can generate interrupt                          |  |

| 12      | TCLO0      | 0   | Frequency division output of timer 0                            |  |

| 13      | TCLO1      | 0   | Frequency division output of timer 1                            |  |

| 16      | VPP        | -   | High voltage pin, when download OTP, connects to 12V voltage    |  |

| 21      | XIN4M      | 1   | High frequency crystal input <adc channel="" forbids=""></adc>  |  |

| 22      | XOUT4M     | 0   | High frequency crystal output <adc channel="" forbids=""></adc> |  |

| 23      | VREF       | 1   | ADC external reference voltage input                            |  |

### **FUNCTION DESCRIPTION**

SC9307P has embedded SC65PX core and 8K-byte OTP program memory, the data memory is 384-byte. Built-in RC oscillator generates 3.2MHz clock frequency, and after 1/2,1/4 frequency divided, It can also be used as system main clock together with external 75KHz oscillator or extended high speed clock by PC4/5 to implement applications in different modes, thus to reduce the power dissipation. The built-in counting circuit can be used for local oscillator signal counting and RC oscillator frequency measuring. In addition, it has three 8-bit counters T0/T1/T2. T0/T1 can be used separately or used together as a 16-bit counter. The built-in RTC module www.DataSprovides\_powerful calendar/alarm functions, and BUZ signals with 4 different frequencies. PA/B/C/E/F can provide max. 34 I/O ports, where PA/B has pull-up configuration and selectable open-drain output function, PC can be shared as ADC analog pin, 16 PE/F ports are all used as general I/O without pull-up resistor or open-drain function. Compared to port PA, PB and PC, driving ability of port PE and PF are a little weak.

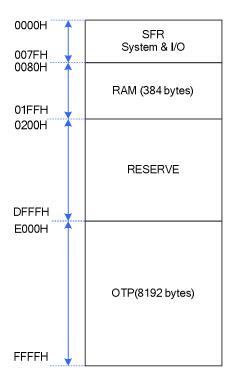

# **MCU Address Space**

MCU uses 16-bit address bus, the maximum addressing space is 64K-Byte (0000H~FFFFH). The address assignment of memory space is as follows:

SFR: Special function registers. This block includes system control & status register and the mapping of ports and display data block.

# **Register Mapping Table**

0000H~007FH is assigned to I/O and some function registers. Where 0000H~000FH is assigned to the core.

Function registers and I/O ports configuration of used address space is as follows:

| Module                | Register                                                                           | I/O | Address | Function descriptions                                                                      |  |  |  |

|-----------------------|------------------------------------------------------------------------------------|-----|---------|--------------------------------------------------------------------------------------------|--|--|--|

| Used Address Spac     | е                                                                                  |     |         |                                                                                            |  |  |  |

| Sheet4U.com           | IRQIP                                                                              | W/R | 00H     | Maskable interrupt enable register                                                         |  |  |  |

|                       | IRQDP                                                                              | W/R | 01H     | Maskable interrupt source register                                                         |  |  |  |

| Interment Control     | NMIIP                                                                              | W/R | 02H     | Non-maskable interrupt enable register                                                     |  |  |  |

| Interrupt Control     | NMIDP                                                                              | W/R | 03H     | Non-maskable interrupt source register                                                     |  |  |  |

|                       | INTCON                                                                             | W/R | 47H     | Interrupt control register                                                                 |  |  |  |

|                       | NMI is not used in the circuit, reserved. Forbid it by SEN instruction of program. |     |         |                                                                                            |  |  |  |

|                       | WDTCON                                                                             | W/R | 04H     | Watchdog timer setting and enable register                                                 |  |  |  |

| Watchdog Timer        | WDT CLR0                                                                           | W   | 09H     | Watchdog clear register (write 53H, ACH to                                                 |  |  |  |

|                       | WDT CLR1                                                                           | W   | 0AH     | 09H,0AH to clear WDT)                                                                      |  |  |  |

| MOLL control          | MCU_SLP                                                                            | W   | 06H     | MCU sleep control register                                                                 |  |  |  |

| MCU control           | MCU_STATUS                                                                         | R   | 07H     | MCU status register                                                                        |  |  |  |

| Bit Operation Control | BITCTRL                                                                            | W/R | 08H     | Bit operation address space selection register(refer to 《SC65PX instructions》 for details) |  |  |  |

| System Control        | SYSCON                                                                             | W/R | 45H     | System function control register                                                           |  |  |  |

| Clock Control         | CLKCON                                                                             | W/R | 46H     | System clock control register                                                              |  |  |  |

| Module                   | Register   | I/O  | Address | Function descriptions                             |

|--------------------------|------------|------|---------|---------------------------------------------------|

| Block Signal             | CLKSEL     | W/R  | 4BH     | Block signal selection control register           |

| Selection Control        | 02.1022    | •••• | 1511    | Disort orginal colocitor control register         |

|                          | RTC_CS     | W/R  | 30H     | RTC control register                              |

|                          | YEARH      | W/R  | 31H     | MSB of year data(BCD: 00~99)                      |

|                          | SECOND     | W/R  | 32H     | Second data(BCD: 00~59)                           |

|                          | MIN        | W/R  | 33H     | Minute data(BCD: 00~59)                           |

|                          | HOUR       | W/R  | 34H     | Hour data(BCD: 00~23)                             |

|                          | DAY        | W/R  | 35H     | Day data(BCD: 01~31)                              |

| RTC Data and             | WEEK       | W/R  | 36H     | Week data(BCD: 0~6)                               |

| Control                  | MON        | W/R  | 37H     | Month data(BCD: 01~12)                            |

|                          | YEARL      | W/R  | 38H     | LSB of year data(BCD: 00~99)                      |

|                          | MIN_ALARM  | W/R  | 39H     | Minute alarm setting                              |

|                          | HOUR_ALARM | W/R  | 3AH     | Hour alarm setting                                |

|                          | DAY_ALARM  | W/R  | 3BH     | Day alarm setting                                 |

|                          | WEEK_ALARM | W/R  | 3CH     | Week alarm time setting                           |

|                          | CKO_CS     | W    | 3DH     | BUZ signal control                                |

| TIMEDO                   | T2CON      | W/R  | 48H     | Control register                                  |

| TIMER2                   | T2REF      | W/R  | 49H     | Preassign register                                |

| TIMEDO                   | T0CON      | W/R  | 4CH     | Control register                                  |

| TIMER0                   | T0REF      | W/R  | 4DH     | Preassign register                                |

| TIMER1                   | T1CON      | W/R  | 4EH     | Control register                                  |

| TIVIERI                  | T1REF      | W/R  | 4FH     | Preassign register                                |

|                          | UART_BUF   | W/R  | 62H     | Transmitting/receiving data buffer                |

|                          | SCON       | W/R  | 63H     | UART control register                             |

| UART                     | BRCON      | W/R  | 64H     | Baud rate control register                        |

| Sheet4U.com              | BRTIMER    | W/R  | 65H     | Baud rate counting initial value setting register |

| Analog/Digital           | ADDATA     | R    | 50H     | Conversion result of 8-bit storage                |

| Converter                | ADCON      | W/R  | 51H     | Analog/digital control and status                 |

| Local oscillator amplify | PLLCON     | W/R  | 52H     | Local oscillator input control register           |

|                          | IFMOD      | W/R  | 55H     | Frequency counting mode control register          |

| Frequency counter        | IFCNT0     | W/R  | 56H     | Low 8-bit of frequency counting data              |

|                          | IFCNT1     | W/R  | 57H     | High 8-bit of frequency counting data             |

|                          | TRISA      | W/R  | 59H     | Direction control register of port A              |

|                          | PORTA      | W/R  | 5DH     | Data temporary storage register of port A         |

| Port and Direction       | TRISB      | W/R  | 5AH     | Direction control register of port B              |

| Control (strong          | PORTB      | W/R  | 5EH     | Data temporary storage register of port B         |

| driving)                 | TRISC      | W/R  | 5BH     | Direction control register of port C              |

|                          | PORTC      | W/R  | 5FH     | Data temporary storage register of port C         |

|                          | APCON      | W/R  | 5CH     | Port and A/D input diplex selection control       |

www.DataS

| Module             | Register | I/O | Address | Function descriptions                     |  |  |

|--------------------|----------|-----|---------|-------------------------------------------|--|--|

| Pull-up            | PUA      | W/R | 60H     | I/O port pull-up mode selection register  |  |  |

| Configuration      | PUB      | W/R | 61H     | I/O port pull-up mode selection register  |  |  |

|                    | PORTE    | W/R | 68H     | Data temporary storage register of port E |  |  |

| Dont and Discotion | PORTF    | W/R | 69H     | Data temporary storage register of port F |  |  |

| Port and Direction | PECFGL   | W   | 6BH     | PE0~3 pin configuration register          |  |  |

| Control (weak      | PECFGH   | W   | 6CH     | PE4~7 pin configuration register          |  |  |

| driving)           | PFCFGL   | W   | 6DH     | PF0~3 pin configuration register          |  |  |

|                    | PFCFGH   | W   | 6EH     | PF4~7 pin configuration register          |  |  |

| 6F-7FH Unused      |          |     |         |                                           |  |  |

#### Interrupt control

SC65PX supports two kinds of interrupts: Non-maskable interrupt NMI; maskable interrupt IRQ. Where PRI of non-maskable interrupt NMI is higher than maskable interrupt IRQ. However, this circuit does not implement NMI interrupt.

#### 1. Maskable interrupts

SC9307P has 11 maskable interrupts in total without PRI; Setting IRQIP register to determine if the interrupt is enable. All the maskable interrupts use the same entry address FFF8H.

## 2. Non-maskable interrupts(reserved)

Non-maskable interrupt NMI is active high. Entry address is FFFCH/FFFDH. This circuit does not implement NMI function. There is no need to set NMIIP and NMIDP registers.

# 3. External interrupts

SC9307P has 4 IO input interrupts: ExtInt0~3 input by PA0~3 pins; one scan interrupt KSINT sharing one interrupt source with ExtInt2, IRQDP.6. ExtInt3 and IF interrupt IRQIFC share one interrupt source, IRQDP.7. In addition, RTC and Timer2 share one interrupt source.

www.DataSheet4U.com

### **Watchdog Timer**

Watchdog timer adopts independent counter. Watchdog (WDT) is mainly used for program monitor. After counting overflows, it generates reset signal to avoid endless loop or other error execution status. The longest overflow time is 873.6ms with 75KHz crystal oscillator.

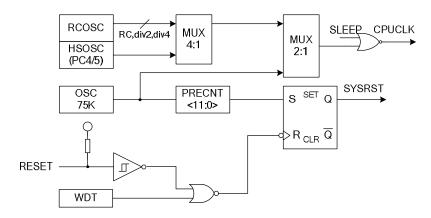

# Operating mode control

SC9307P work in three modes: normal mode, sleep mode, and data hold mode. Normal mode can be divided into high-speed mode and low-speed mode. The difference is the different system clock sources. The high speed mode system clock comes from internal RC oscillator or high speed oscillator extended by PC4/5, while the low speed mode system clock comes from external low speed oscillator.

After power on, CPU clock is provided by internal RC oscillator which needs to turn on internal reference module. Select clock frequency or switch to the external low speed clock (75KHz) by setting system control register and clock control register.

The MCU enters sleep mode by setting SLEEP flag of MCU sleep control register MCU\_SLP as 1. After the MCU enters sleep mode, external 75KHz oscillator still works, and CPU clock will be turned off. But it can still response to internal timer interrupt or external IO interrupt. The circuit enters sleep mode which can reduce the

system standby power dissipation (with 75KHz crystal oscillator, when RTC enables at 3V operating voltage, typical power dissipation current is less than  $5\mu$ A). Reset, internal or external interrupt can wake up CPU and make it enter work in full speed.

When system clock comes from external low speed oscillator, if this oscillator is closed by program, the circuit will enter data hold mode. In this mode, RAM data is saved. The dissipation current is reduced to less than 1uA. External IO interrupt or reset can make the oscillator work again.

**Note:** The clock should be switch to 75KHz before entering the sleep mode. Turn off the power reference circuit and other relative circuits to reduce the power dissipation.

#### **Clock and Reset**

SC9307P supports many selectable operating clocks. The clock source can be external 75KHz crystal oscillator, and can also be the clock generated by internal RC oscillator. When high precision and high speed is needed, it can extend high frequency external oscillator through PC4/5. The structure is as follows:

The system reset occurs when: internal watchdog counting overflows; external Reset pin input low level. The circuit jumps to the start address of the program from reset address FFFAH and begins working normally.

If only fast response to internal and external events is needed without high precision, RC oscillator can be adopted as CPU clock to make the system process the events quickly. RC oscillator will vary following the voltage and temperature, so PC4/PC5 must be used to extend high-speed oscillator to satisfy the system requirements under the conditions that need high-precision timing or asynchronous communication, etc..

RC oscillator begins to work after reset, and used as CPU clock.

# Real time Clock (RTC)

RTC module can provide powerful timing function. When it starts, it will work separately from CPU. It can provide minute, hour and year/month/day, etc. in BCD formats. Minute, hour, week, day alarm can be set, and the alarm function can be triggered by interrupt or inquiring the alarm flag by software. At the same time, it will generate 0.5s real time clock signal, which can trigger interrupt. This interrupt shares one channel with alarm interrupt. It is used together with INTCON register. At the same time, it provides 4 BUZ signals to driver the buzzer.

## Timer T0/T1/T2

SC9307P includes three 8-bit timers Timer0, Timer1 and Timer2. Where, T0 and T1 timers can be used together as a 16-bit timer. When T0 or T1 are used separately, their functions are as follows:

- > 8-bit programmable timing, generate interrupt after setting the time interval

- Arbitrary frequency output

- External clock frequency division

T0/T1/T2 has one control register and one pre-assignment register.

#### **UART**

SC9307P has built-in full duplex async communication interface with three modes: 8bit variable baud rate, 9bit fixed baud rate or variable baud rate communication.

- Pin Tx diplex with PB4, pin RX diplex with PB5

- > Baud rate presetting register can adjust baud rate freely

- > Transmitting and receiving interrupt cooperation dual buffer can guarantee the high speed communication stable and reduce the CPU load.

#### 8-bit ADC

8-bit AD converter is mainly used for keyboard scan and electronic volume display. It has 4 input channels (PC0/1/4/5). Select a channel and input switch level by program and the result is stored in an 8-bit register. Conversion clock has 4 selectable clock sources. Input internal reference voltage through channel 6 of ADC to detect the battery voltage (together with internal standard voltage). PC4/5 can also be used to extend high frequency oscillator pin, if it is not connected to oscillator, ADC input channel is not effected. One AD conversion needs 12 clock cycles, and the typical conversion time of ADC is 160µs with 75KHz oscillator.

# Frequency counting module

This module mainly includes local oscillator signal amplifier and gate control counting. FM or AM local oscillator signal is counted by a 16-bit counter after amplified. This counter gate control time can be selected as 1/4/8ms, so the local oscillator frequency can be got easily according to the counter value and gate time.

#### I/O Port

www.DataSiSC9307Pnhas 5 groups of I/O ports: PA, PB, PC, PE, PF. PA has 8 pins, where 4 pins are used for external interrupt input. PB has 5 pins, where 3 pins are used for key input interrupt. PC has 5 pins, where 4 pins are shared with ADC input channel. PC.6 is used for ADC external reference voltage input. PE/PF are general I/O, 16 pins in total. So there are max. 34 pins can be used as IO pins.

There are three registers for ports PA/B. Data register PORTx latches the output data, direction register TRISx controls the dataflow direction (set 1 to be output). PUA register and TRISA register can implement input pull-up or output open-drain of port A. PB has only 5 pins, port PC of PUB register is controlled by 3 registers, TRISC realizes direction selection, PORTC stores output data, APCON realizes the switch of analog channel and digital channel.

Register PORTx is readable/writable. When PORTx is set as output, read the last writing data of this register; when it is set as input, read the pin state.

Usage of port PE/F is different from PA/B/C. Just take port PE as an example, lower 4-bit of register PECFGL is used for controlling PE.3~0 ports. When PECFGL.3 is set as 1, PE.3 acts as output and when PECFGL.3 is set as 0, PE.3 acts as input. Lower 4-bit of register PECFGH is used for controlling PE.7~4 ports. When PECFGH.3 is set as 1, PE.7 acts as output and when PECFGH.3 is set as 0, PE.7 acts as input.

Usage and function of PF are same as PE, used as output after reset. Control mode of PFCFGL, PFCFGH are same as PECFGL, PECFGH.

# **PACKAGE OUTLINE**

# **HANDLING MOS DEVICES:**

Electrostatic charges can exist in many things. All of our MOS devices are internally protected against electrostatic discharge but they can be damaged if the following precautions are not taken:

- Persons at a work bench should be earthed via a wrist strap.

- Equipment cases should be earthed.

- All tools used during assembly, including soldering tools and solder baths, must be earthed.

- MOS devices should be packed for dispatch in antistatic/conductive containers.

#### Disclaimer:

- Silan reserves the right to make changes to the information herein for the improvement of the design and performance without further notice!

- All semiconductor products malfunction or fail with some probability under special conditions. When using Silan products

in system design or complete machine manufacturing, it is the responsibility of the buyer to comply with the safety

standards strictly and take essential measures to avoid situations in which a malfunction or failure of such Silan products

could cause loss of body injury or damage to property.

- Silan will supply the best possible product for customers!