## MP3 DECODER WITH CD INTERFACE

## **DESCRIPTION**

SC9820P is a sing-chip Mp3 decoder. It can be used in CD player, DISC-MAN and such systems which need MP3 decoder. And this chip provides smaller package, lower power dissipation and higher cost performance ratio.

### **FEATURES**

- \* Provide ECC and EDC functions for CD-ROM data error correcting.

- \* ISO/IEC 11172-3 L3 L2 L1 decode

- \* ISO/IEC 13818-3 L3 L2 L! decode

- \* Support all MP3 bit rates and free formats under SO/IEC 11172-3 L3 L2 L1 specifications.

- \* Support all MP3 bit rates and free formats under SO/IEC 13818-3 L3 L2 L1 specifications.

- \* Support 48K/44.1K/32K MP3 standard sampling rate, 24K/22.05K/16K and 12K/11.025/8K low sampling rate

- \* Support single/double/stereo/union stereo

- \* Serial host interface

- \* Support CD-DA straight through mode

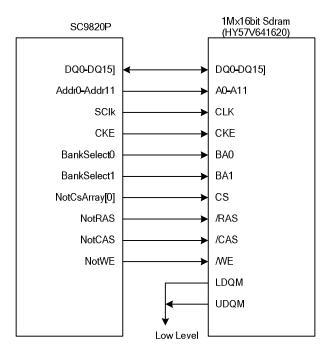

- \* Support SDRAM/DRAM interface

- \* Only one external 16.9344MHz crystal oscillator

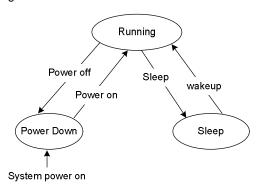

- \* Power supply managing: normal mode, brownout mode and dormancy mode

- \* Various playing functions: skip forward/backward in track, skip forward/backward between tracks, pause, play and so on.

- \* Support the file systems in ISO9660, Joliet UDF formats

- \* Support 1M/4M/8M/16Mx16 SDRAM, 1M/4M x16 DRAM

## **ORDERING INFORMATION**

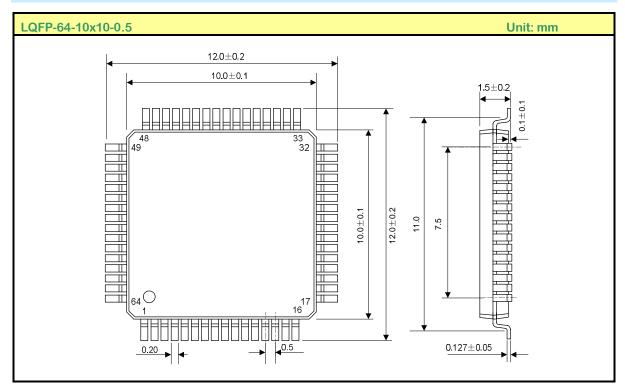

| Device  | Package           |

|---------|-------------------|

| SC9820P | LQFP-64-10X10-0.5 |

### **APPLICATIONS**

- \* Desk-top audio

- \* Portable CD/Mp3 player

- \* Car audio

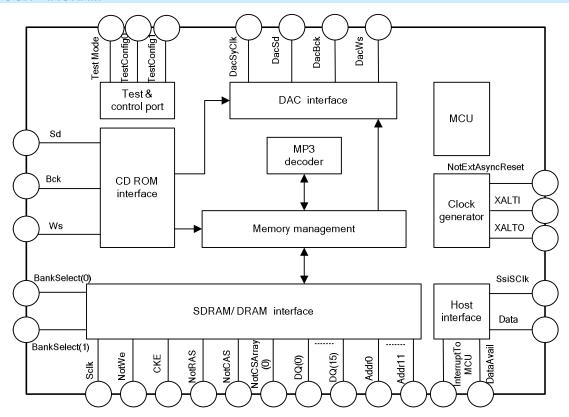

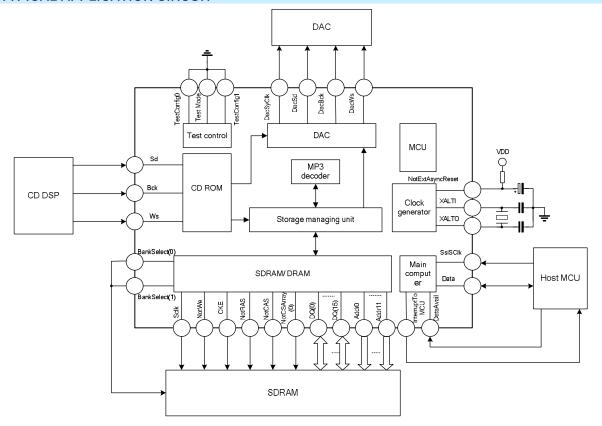

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol | Rating            | Unit |

|---------------------|--------|-------------------|------|

| Kernel Voltage      | VCCInt | 1.4 ~ 2.3         | V    |

| Port Voltage        | Vccio  | 2.9 ~ 4.2         | V    |

| Input Voltage       | VIN    | -0.3 ~Vccio + 0.3 | ٧    |

| Ambient Temperature | Tamb   | -40~90            | °C   |

| Storage Temperature | Tstg   | -60~150           | °C   |

## ELECTRICAL CHARACTERISTICS (VCCINT=1.8V, VCCIO=3.3V, Tamb=25°C)

| Parameter                | Symbol | Test Conditions              | Min. | Тур.    | Max. | Unit |

|--------------------------|--------|------------------------------|------|---------|------|------|

| Kernel Operating Voltage | VCCInt | Normal working               | 1.6  | 1.8     | 2.0  | V    |

| Port Operating Voltage   | VCCIO  | Normal working               | 3.1  | 3.3     | 3.9  | V    |

|                          | IDDInt | Kernel VDD1.8 supply current |      | 5.3     |      | μA   |

| Quiescent Current        | Iddio  | Port VDD3.3 supply current   |      | 0       |      | μA   |

|                          | ICCInt | Kernel VDD1.8 supply current | 10.1 |         | 11.9 | mA   |

| Operating Current        | Iccio  | Port VDD3.3 supply current   | 1.3  |         | 2.5  | mA   |

| Operating Frequency      | McIk   |                              |      | 16.9344 |      | MHz  |

| High Level Input Voltage | ViH    |                              | 2.1  |         |      | V    |

| tinued |  |

|--------|--|

|        |  |

|        |  |

| Parameter                          | Symbol | Test                   | Conditions | Min. | Тур. | Max. | Unit     |

|------------------------------------|--------|------------------------|------------|------|------|------|----------|

| Low Level Input Voltage            | VIL    |                        |            |      |      | 0.6  | V        |

| High Level Input Current           | lін    | Type a <sup>note</sup> | VIN=VDD    | 0    |      |      | μΑ       |

| Low Level Input Current            | lıL    | Type a <sup>note</sup> | VIN=VSS    | 0    |      |      | μΑ       |

| High Level Output                  | \/a    | IOH=1mA                |            | -    | 3.29 |      | \ /      |

| Voltage                            | Vон    | IOH=2mA                |            | -    | 3.28 |      | V        |

| 1 - 1 - 1 0 (- 1)/-1(              | \      | IoL=1mA                |            | 1    | 0.02 |      |          |

| Low Level Output Voltage           | Vol    | IOL=2mA                |            | 1    | 0.04 |      | <b>V</b> |

| Three State Output leakage current | loz    | VOUT=VSS or VDD        |            | 0    |      |      | μΑ       |

| Output Short Circuit               | 1      | VDD=3.3V, Vo           | D=VDD      |      | 47   |      |          |

| Current                            | los    | VDD=3.3V, V0           | D=VSS      |      | 35   |      | mA       |

Note: Type a: Common input port; Type b: Input port with pull-up resistor

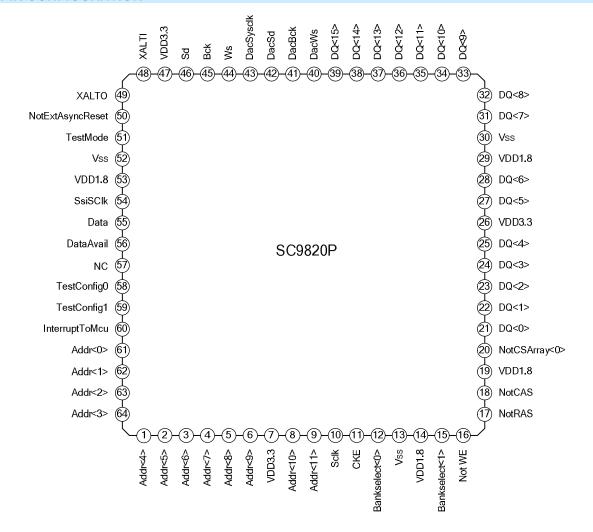

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN DESCR | AIF TION      | 1   |                                                             |  |  |

|-----------|---------------|-----|-------------------------------------------------------------|--|--|

| Pin No.   | Pin name      | I/O | Pin description                                             |  |  |

| 1         | Addr<4>       | 0   | SDRAM/DRAM address pin 4                                    |  |  |

| 2         | Addr<5>       | 0   | SDRAM/DRAM address pin 5                                    |  |  |

| 3         | Addr<6>       | 0   | SDRAM/DRAM address pin 6                                    |  |  |

| 4         | Addr<7>       | 0   | SDRAM/DRAM address pin 7                                    |  |  |

| 5         | Addr<8>       | 0   | SDRAM/DRAM address pin 8                                    |  |  |

| 6         | Addr<9>       | 0   | SDRAM/DRAM address pin 9                                    |  |  |

| 7         | VDD3.3        | ı   | Port supply voltage (3.3V)                                  |  |  |

| 8         | Addr<10>      | 0   | SDRAM/DRAM address pin 10                                   |  |  |

| 9         | Addr<11>      | 0   | SDRAM/DRAM address pin 11                                   |  |  |

| 10        | SCIk          | 0   | 16.9344M SDRAM/DRAM clock output pin                        |  |  |

| 11        | CKE           | 0   | SDRAM/DRAM clock enable output pin                          |  |  |

| 12        | BankSelect<0> | 0   | SDRAM/DRAM block selecting output pin 0                     |  |  |

| 13        | Vss           | ı   | Ground                                                      |  |  |

| 14        | VDD1.8        | ı   | Kernel supply voltage (1.8V)                                |  |  |

| 15        | BankSelect<1> | 0   | SDRAM/DRAM block selecting output pin 1                     |  |  |

| 16        | NotWE         | 0   | SDRAM/DRAM write enable output pin which is a low active.   |  |  |

| 17        | NotRAS        | 0   | SDRAM/DRAM row address strobe pin which is a low active.    |  |  |

| 18        | NotCAS        | 0   | SDRAM/DRAM column address strobe pin which is a low active. |  |  |

| 19        | VDD1.8        | ı   | OTP download voltage.                                       |  |  |

| 20        | NotCSArray<0> | 0   | SDRAM/DRAM chip selection output 0 which is a low active.   |  |  |

| 21        | DQ<0>         | I/O | SDRAM/DRAM data pin 0 with internal pull-up resistor.       |  |  |

| 22        | DQ<1>         | I/O | SDRAM/DRAM data pin 1 with internal pull-up resistor.       |  |  |

| 23        | DQ<2>         | I/O | SDRAM/DRAM data pin 2 with internal pull-up resistor.       |  |  |

| 24        | DQ<3>         | I/O | SDRAM/DRAM data pin 3 with internal pull-up resistor.       |  |  |

| 25        | DQ<4>         | I/O | SDRAM/DRAM data pin 4 with internal pull-up resistor.       |  |  |

| 26        | VDD3.3        | ı   | Port supply voltage (3.3V)                                  |  |  |

| 27        | DQ<5>         | I/O | SDRAM/DRAM data pin 5 with internal pull-up resistor.       |  |  |

| 28        | DQ<6>         | I/O | SDRAM/DRAM data pin 6 with internal pull-up resistor.       |  |  |

| 29        | VDD1.8        | ı   | Kernel supply voltage(1.8V)                                 |  |  |

| 30        | VSS           | ı   | Ground                                                      |  |  |

| 31        | DQ<7>         | I/O | SDRAM/DRAM data pin 7 with internal pull-up resistor.       |  |  |

| 32        | DQ<8>         | I/O | SDRAM/DRAM data pin 8 with internal pull-up resistor.       |  |  |

| 33        | DQ<9>         | I/O | SDRAM/DRAM data pin 9 with internal pull-up resistor.       |  |  |

| 34        | DQ<10>        | I/O | SDRAM/DRAM data pin 10 with internal pull-up resistor.      |  |  |

| 35        | DQ<11>        | I/O | SDRAM/DRAM data pin 11 with internal pull-up resistor.      |  |  |

| 36        | DQ<12>        | I/O | SDRAM/DRAM data pin 12 with internal pull-up resistor.      |  |  |

| 37        | DQ<13>        | I/O | SDRAM/DRAM data pin 13 with internal pull-up resistor.      |  |  |

| 38        | DQ<14>        | I/O | SDRAM/DRAM data pin 14 with internal pull-up resistor.      |  |  |

| 39        | DQ<15>        | I/O | SDRAM/DRAM data pin 15 with internal pull-up resistor.      |  |  |

(Continued)

| (Continued) |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.     | Pin name         | I/O | Pin description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

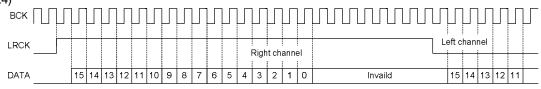

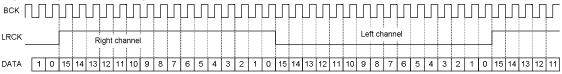

| 40          | DacWs            | 0   | Word selection clock pin output to DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 41          | DacBck           | 0   | Bit clock pin output to DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 42          | DacSd            | 0   | Data pin output to DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 43          | DacSysClk        | 0   | System clock output to DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 44          | Ws               | I   | Word selection clock pin output to CD-DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 45          | Bck              | I   | Bit clock pin output to CD-DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 46          | Sd               | ı   | Data pin output to CD-DSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 47          | VDD3.3           | ı   | Port supply voltage (3.3V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 48          | XALTI            | ı   | Oscillator input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 49          | XALTO            | 0   | Oscillator output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 50          | NotExtAsyncReset | ı   | System reset pin which is a low active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 51          | TestMode         | ı   | Test mode pin which is a high active and connected to ground when it is not in test mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 52          | Vss              | ı   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 53          | VDD1.8           | ı   | Kernel supply voltage (1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 54          | SsiSClk          | ı   | MCU clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 55          | Data             | I/O | MCU data pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 56          | DataAvail        | ı   | MCU telecommunication control pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 57          | NC               |     | Null                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 58          | TestConfig0      | ı   | Test mode configuration ( low level when normal use)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 59          | TestConfig1      | I   | Test mode configuration ( low level when normal use)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 60          | InterruptToMcu   | 0   | Interrupt pin which is a high active and output to MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 61          | Addr<0>          | 0   | SDRAM/DRAM address pin 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 62          | Addr<1>          | 0   | SDRAM/DRAM address pin 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 63          | Addr<2>          | 0   | SDRAM/DRAM address pin 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 64          | Addr<3>          | 0   | SDRAM/DRAM address pin 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | 1                |     | process of the control of the contro |

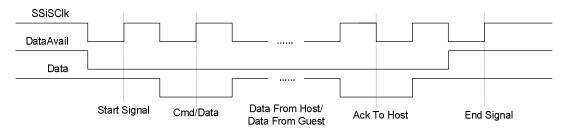

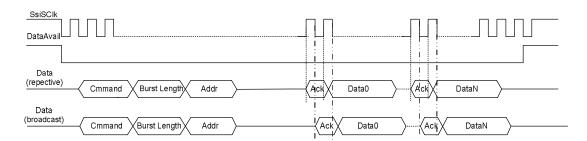

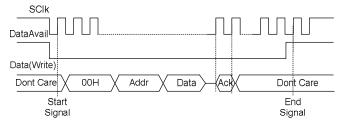

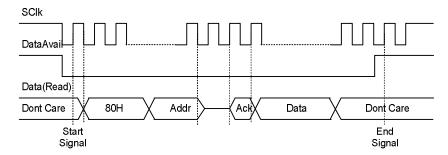

## **FUNCTION DESCRIPTION**

## 1. Register function

Register description (The register address of SC9820P is 8 bits)

| -3 ,                | togister description (The register address of edecater is a site) |            |                |                                                    |  |  |  |  |

|---------------------|-------------------------------------------------------------------|------------|----------------|----------------------------------------------------|--|--|--|--|

| Symbol              | Address                                                           | Read/write | Initialization | Description                                        |  |  |  |  |

| SC9820P play state  | registers                                                         |            |                |                                                    |  |  |  |  |

| TotalTimeMin[5:0]   | 0x61                                                              | R          | 0x00           | Total time's minutes of current playing music:0-59 |  |  |  |  |

| TotalTimeSec[5:0]   | 0x62                                                              | R          | 0x00           | Total time's seconds of current playing music:0-59 |  |  |  |  |

| CurrentTimeMin[5:0] | 0x63                                                              | R          | 0x00           | Played time's minutes of current music:0-59        |  |  |  |  |

| CurrentTimeSec[5:0] | 0x64                                                              | R          | 0x00           | Played time's seconds of current music: 0-59       |  |  |  |  |

| (Continued)         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol Address Read | /write Initialization | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | R 0x03                | bit[3:0]: Sampling rate of current playing music  0x0: 44.1KHz 0x1: 48KHz 0x2: 32KHz 0x4: 22.05KHz 0x6: 16Khz 0x0C: 11.025KHz 0x0D: 12KHz 0x0E: 8KHz Reserve the rest; When the music format is Layer III: Bit [7:4]: The bit rate of current playing music, together with sampling rate to decide current bit rate. This chip provides variable bit rate and free bit rate (*1). When the sampling rate is 44.1, 48, 32KHz, the other sampling rate is: 0x0: Free schema 0x1: 32kbps 8kbps 0x2: 40kbps 16kbps 0x3: 48kbps 24kbps 0x4: 56kbps 32 kbps 0x5: 64 kbps 40 kbps 0x6: 80 kbps 48 kbps 0x7: 96 kbps 56 kbps 0x8: 112 kbps 64 kbps 0x9: 128 kbps 80 kbps 0x0A: 160 kbps 96 kbps 0x0C: 224 kbps 128 kbps 0x0C: 224 kbps 128 kbps 0x0C: 320 kbps 160 kbps 0x0F: Forbid When the music format is Layer I: 0x0: Free mode 0x1: 32kbps 0x2: 64kbps 0x3: 96kbps 0x4: 128kbps 0x5: 160 kbps |

| (Continued)      |         | T          |                |                                             |

|------------------|---------|------------|----------------|---------------------------------------------|

| Symbol           | Address | Read/write | Initialization | Description                                 |

|                  |         |            |                | 0x6: 192 kbps                               |

|                  |         |            |                | 0x7: 224 kbps                               |

|                  |         |            |                | 0x8: 256 kbps                               |

|                  |         |            |                | 0x9: 288 kbps                               |

|                  |         |            |                | 0x0A:320 kbps                               |

|                  |         |            |                | 0x0B:352 kbps                               |

|                  |         |            |                | 0x0C:384 kbps                               |

|                  |         |            |                | 0x0D:416 kbps                               |

|                  |         |            |                | 0x0E:448 kbps                               |

|                  |         |            |                | 0x0F:Forbid                                 |

|                  |         |            |                | When the music format is Layer II:          |

|                  |         |            |                | 0x0: Free mode                              |

|                  |         |            |                | 0x1: 32kbps                                 |

| FrameInform[7:0] | 0x65    | R          | 0x03           | 0x2: 48kbps                                 |

|                  |         |            |                | 0x3: 56kbps                                 |

|                  |         |            |                | 0x4: 64kbps                                 |

|                  |         |            |                | 0x5: 80 kbps                                |

|                  |         |            |                | 0x6: 96 kbps                                |

|                  |         |            |                | 0x7: 112 kbps                               |

|                  |         |            |                | 0x8: 128 kbps                               |

|                  |         |            |                | 0x9: 160 kbps                               |

|                  |         |            |                | 0x0A:192 kbps                               |

|                  |         |            |                | 0x0B:224 kbps                               |

|                  |         |            |                | 0x0C:256 kbps                               |

|                  |         |            |                | 0x0D:320 kbps                               |

|                  |         |            |                | 0x0E:384 kbps                               |

|                  |         |            |                | 0x0F:Forbid                                 |

|                  |         |            |                | SC9820PC02 operating mode:                  |

|                  |         |            |                | Bit0: HostMemoryOpEnable                    |

|                  |         |            |                | 0b0: inhibit Host operate external Sdram    |

|                  |         |            |                | 0b1: enable Host operate external Sdram     |

|                  |         |            |                | Bit1: Mute                                  |

|                  |         |            |                | 0b0: the current play is in the normal mode |

| StereoMode[0]    | 0x66    | R          | 0x00           | 0b1: the current play is in the mute mode   |

|                  |         |            |                | Bit2: Pause                                 |

|                  |         |            |                | 0b0: the current play is in the normal mode |

|                  |         |            |                | 0b1: the current play is in the pause mode  |

|                  |         |            |                | Bit3: Sleep                                 |

|                  |         |            |                | 0b0: the current play is in the normal mode |

|                  |         |            |                | 0b1: the current play is in the sleep mode  |

| (Continued)    |         |            |                |                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|---------|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

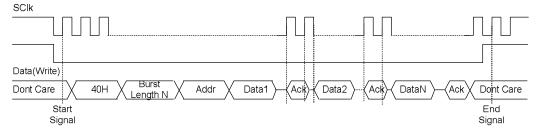

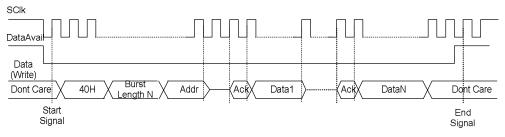

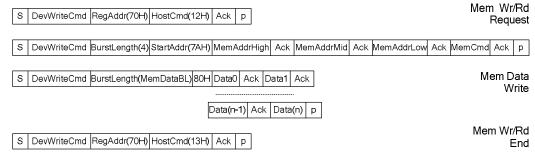

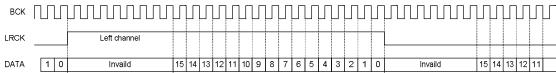

| Symbol         | Address | Read/write | Initialization | Description                                                                                                                                                                                                                                                                                                                                                                                                  |