# **Signetics**

# SCB68175 Bus Controller

Preliminary Specification

#### **Microprocessor Products**

#### DESCRIPTION

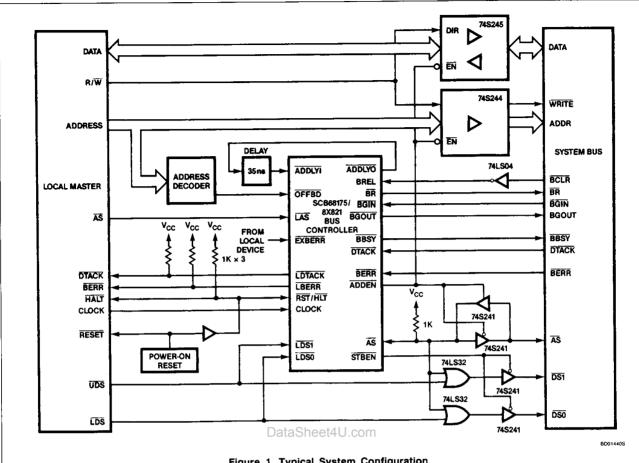

The Signetics SCB68175/8X821 Bus Controller is a high-speed bus requester and timing generator designed to interface a local master (typically, a microprocessor or DMA controller) to the VMEbus or VERSAbus<sup>TM</sup>. The requester is fully asynchronous and controls all the sequencing required for acquisition and use of the bus, including both strobe and buffer timing. To permit fixed or variable length bus access, both release-whendone (RWD) and release-on-request (ROR) modes are supported by the SCB68175/8X821. In addition, an early bus-busy release increases system throughput by allowing bus arbitration to be performed concurrently with the final bus cycle of the local master. A bus error/retry circuit is also included in the SCB68175/8X821. This circuit allows the local master to rerun a cycle that was terminated by a bus error. Interface and control signals for a typical configuration are shown in Figure 1.

The SCB68175/8X821 Bus Controller is designed primarily for implementing a simple and efficient interface to the VMEbus. For more information regarding the protocol definitions, proper use, and application of this device, refer to the VMEbus Specification Manual.

#### **FEATURES**

- Asynchronous bus controller for VMEbus and VERSAbus systems

- Provides transparent system interface to local master

- Supports both release-on-request (ROR) and release-when-done (RWD) operations

- Early bus-busy release for optimal bus usage

- Error/entry sequencing

- Dual port capability using 74LS764 DRAM controller

- High speed bipolar technology

- Single +5V supply

- 24-pin slimline DIP package

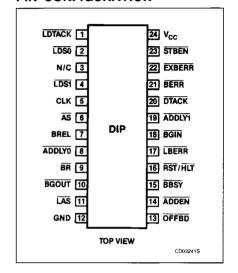

#### PIN CONFIGURATION

DataSheet4U.com

DataShe

VERSAbus is a registered trademark of Motorola, Inc. January 1986

2-426

DataSheet/III com

## Bus Controller

#### SCB68175

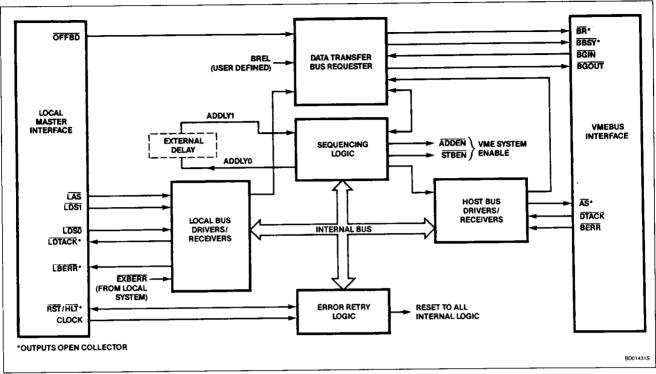

#### **BLOCK DIAGRAM**

et4U.com

DataSheet4U.com

DataShe

January 1986

2-427

DataSheet4U.com

#### **ORDERING CODE**

| PACKAGES    | $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$ |

|-------------|-------------------------------------------------------------|

| Ceramic DIP | SCB68175C2I24                                               |

| Plastic DIP | SCB68175C2N24                                               |

#### PIN DESCRIPTION

| MNEMONIC        | PIN NO. | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDTACK          | 1       | 0    | Local Data Transfer Acknowledge: Active low, open collector. LDTACK is the acknowledge signal to the local master.                                                                                                                                                                                                                                              |

| LDS0            | 2       | 1    | Local Data Strobe 0: Active low (hysteresis) input lower data strobe of the local master.                                                                                                                                                                                                                                                                       |

| LDS1            | 4       | 1    | Local Data Strobe 1: Active low (hysteresis) input upper data strobe of the local master.                                                                                                                                                                                                                                                                       |

| CLK             | 5       | 1    | Clock: CLK is the clock input to the retry circuitry.                                                                                                                                                                                                                                                                                                           |

| AS              | 6       | 1/0  | Address Strobe: Active low, open collector. $\overline{AS}$ is the address strobe of the system bus. As an output, $\overline{AS}$ is asserted to indicate a valid address on the system bus. As an input (hysteresis), $\overline{AS}$ is monitored during the bus acquisition phase to determine when the current master has relinquished control of the bus. |

| BREL            | 7       | 1    | Bus Release: Active high input used to get the SCB68175/8X821 to release the system bus.                                                                                                                                                                                                                                                                        |

| ADDLYO          | 8       | 0    | Address Delay Out: Active low, totem pole. ADDLYO is the output to an external delay line.                                                                                                                                                                                                                                                                      |

| BR              | 9       | 0    | <b>Bus Request:</b> Active low, open collector. The bus request output to the system bus; asserted when the SCB68175/8X821 is not the current master and LAS and OFFBD are asserted.                                                                                                                                                                            |

| BGOUT           | 10      | 0    | Bus Grant Out: Active low, totem pole. BGOUT is the daisy-chain output.                                                                                                                                                                                                                                                                                         |

| LAS             | 11      | 1    | <b>Local Address Strobe:</b> Active low $\overline{LAS}$ is the (hysteresis) input address strobe signal from the local master. If $\overline{OFFBD}$ and $\overline{LAS}$ are asserted low, the SCB68175/8X821 will initiate a bus cycle requesting the bus, if necessary.                                                                                     |

| GND             | 12      | 1    | Ground DataSheet4U.com                                                                                                                                                                                                                                                                                                                                          |

| OFFBD           | 13      | I    | Off Board: OFFBD is an active low select input driven by an address decoder to request access to the system bus. If LAS and OFFBD are asserted low, the SCB68175/8X821 will initiate a bus cycle requesting the bus, if necessary.                                                                                                                              |

| ADDEN           | 14      | 0    | <b>Address Enable:</b> Active low, totem pole. ADDEN is an enable signal to the address and data bus drivers/receivers.                                                                                                                                                                                                                                         |

| BBSY            | 15      | 0    | <b>Bus Busy:</b> Active low, open collector. BBSY output is driven low when the local master has been granted the system bus.                                                                                                                                                                                                                                   |

| RST/HLT         | 16      | 1/0  | Reset/Halt: Active low, open collector. (Hysteresis) input resets the SCB68175/8X821. As an output, it is asserted along with TBERR to initiate a rerun cycle upon receiving either BERR for a bus cycle, or EXBERR for a local cycle.                                                                                                                          |

| LBERR           | 17      | 1/0  | Local Bus Error: Active low, open collector. LBERR is the bus error signal to the local master.                                                                                                                                                                                                                                                                 |

| BGIN            | 18      | 1    | Bus Grant In: Active low. BGIN is the daisy-chain input.                                                                                                                                                                                                                                                                                                        |

| ADDLYI          | 19      | 1    | Address Delay In: Active low. Input from the external delay line.                                                                                                                                                                                                                                                                                               |

| DTACK           | 20      | l    | Data Transfer Acknowledge: Active low. DTACK is the (hysteresis) input data transfer acknowledge signal of the system bus. During the bus acquisition phase, DTACK is monitored to determine when the current master has relinquished control of the bus.                                                                                                       |

| BERR            | 21      | I    | <b>Bus Error:</b> Active low. BERR is the (hysteresis) input bus error signal of the system bus. During the bus acquisition phase, BERR is monitored to determine when the current master has relinquished control of the bus.                                                                                                                                  |

| EXBERR          | 22      | 1    | <b>External Bus Error:</b> Active low. EXBERR is a (hysteresis) input bus error signal from a local device.                                                                                                                                                                                                                                                     |

| STBEN           | 23      | 0    | Strobe Enable: Active low, totem pole. STBEN is an enable signal to the system bus data strobe drivers.                                                                                                                                                                                                                                                         |

| V <sub>CC</sub> | 24      | 1    | Supply Voltage: +5V power supply.                                                                                                                                                                                                                                                                                                                               |

January 1986

2-428

et4U.com

DataShe

Bus Controller SCB68175

Figure 1. Typical System Configuration

#### **FUNCTIONAL DESCRIPTION**

#### **Bus Acquisition**

et4U.com

In a multimaster, bus oriented system, each master requires some method of gaining access to global resources such as, main memory, disk storage and I/O devices. A very precise access arbitration protocol is implemented (fully defined in the VMEbus Specification) and is basically:

- 1. Asserting a bus request.

- Receiving a grant that the bus is available.

- Acknowledging that mastership has been assumed.

#### Requesting the Bus

Local devices capable of becoming bus masters, for example, CPU and interrupt handler, request the system bus by asserting  $\overline{\text{OFFBD}}$ . This signal is typically the output from an address decoder indicating that the required resource (memory, I/O) is accessible only via the host bus. With both  $\overline{\text{OFFBD}}$  and  $\overline{\text{LAS}}$  low, the SCB68175/8X821 asserts the system bus request signal ( $\overline{\text{BR}}$ ). In a VMEbus system,  $\overline{\text{BR}}$  is tied to one of the four bus request signals ( $\overline{\text{BR}}$ 0 –  $\overline{\text{BR}}$ 3).

January 1986

#### Receiving the Bus Grant

The BGIN/BGOUT signals comprise a daisy-chain network allowing multiple bus masters to share the same bus request level. The SCB68175/8X821 will assert BGOUT only if BGIN is received low prior to the assertion of a bus request (BR). This allows the next master, in the daisy-chain, access to the bus. If BR precedes BGIN, then the SCB68175/8X821 will assert BBSY and release BR. This completes the bus request phase.

If BGIN precedes BR, then BR remains asserted pending the next arbitration cycle. If a bus request and BGIN are asserted simultaneously, an onboard arbiter guarantees the outputs to remain stable until a random choice is made of either BR or BGIN.

#### **Bus Access**

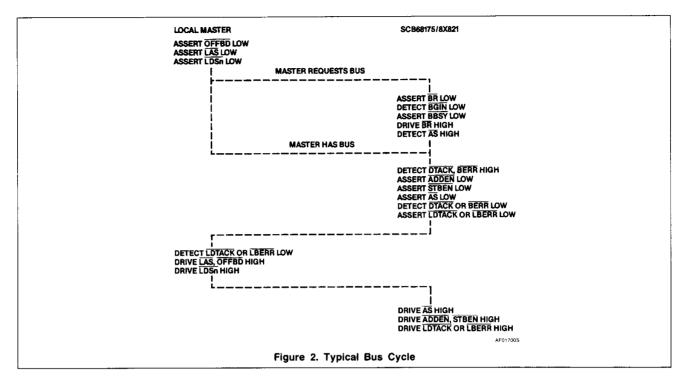

Actual bus access does not occur until the previous master has relinquished control of the bus. This is detected when the system signals AS, DTACK and BERR are received high. The SCB68175/8X821 then controls the sequencing of the address, data and strobe signals required for each bus cycle.

Typical Bus Cycle

See Figure 2 for a typical bus access flow-chart. For each bus access, the SCB68175/8X821 drives ADDEN, STBEN and AS low. An external delay line (35ns minimum), when connected between ADDLY0 and ADDLY1, guarantees a minimum set-up time between the assertion of ADDEN and AS.

In most cases, the local master will require multiple accesses to the host bus. To accommodate, the SCB68175/8X821 cycles  $\overline{AD}$ - $\overline{DEN}$ ,  $\overline{STBEN}$  and  $\overline{AS}$  for each bus access. For a local cycle (when the master asserts  $\overline{LAS}$ , but  $\overline{OFFBD}$  is high), the SCB68175/8X821 holds  $\overline{ADDEN}$ ,  $\overline{STBEN}$  and  $\overline{AS}$  high, and allows the master access to its local bus.

#### Read-Modify-Write Cycle

The SCB68175/8X821 also allows a readmodify-write access for system resources. A read-modify-write cycle is similar to a read cycle followed by a write cycle, except that  $\overline{AS}$  is continuously driven low during both transfer cycles. However, unlike a read followed by a write, the read-modify-write cycle cannot be interrupted because  $\overline{AS}$  is driven low continuously through both cycles, and

2-429

www.DataSheet4U.com

ataSheet4U.com

control of the host bus may only be transferred while  $\overline{AS}$  is high. The SCB68175/8X821 will cycle  $\overline{STBEN}$  as required for a read-modify-write cycle.

#### Bus Release

et4U.com

Following initial bus acquisition, BBSY remains low for a minimum of 90ns, providing a 35ns delay line is connected between ADD-LY0 and ADDLY1. If BREL is asserted high any time before the end of the current bus cycle, the SCB68175/8X821 will release BBSY allowing bus arbitration to take place. At the conclusion of the current bus cycle, the SCB68175/8X821 will release the bus by negating ADDEN, AS and STBEN. A subsequent offboard request will result in the start of a new bus acquisition cycle.

The bus release signal can be used to control the duration, that is the number of cycles the master will control the bus. For most simple masters, BREL can be tied high resulting in a single-cycle RWD configuration. In this case, the SCB68175/8X821 must request the bus for each and every bus cycle. A DMA controller might use the RWD mode, but would

assert BREL only after performing a fixed number of cycles.

An ROR mode can be achieved by asserting BREL only when some other master is requesting bus access. Typically, this may be achieved by NANDing the appropriate  $\overline{BR}$  lines together to assert BREL. BREL is not monitored by the SCB68175/8X821 until the last leading edge of either  $\overline{BGIN}$  or  $\overline{ADDLYI}$ . This prevents the SCB68175/8X821 from relinquishing control due to its own bus request.

For improved system performance, BREL should be asserted early in the current cycle (that is, as soon as possible after  $\overline{\text{LAS}}$  is asserted), to allow bus arbitration to be performed concurrently with the existing bus cycle.

#### **Bus Error/Entry**

The SCB68175/8X821 provides a bus error/entry facility which allows the local master to rerun its last cycle once, if the cycle was terminated by a bus error.

The bus error/entry sequence is initiated when a bus error is received instead of a

(normal) data transfer acknowledge signal.

Upon receipt of a bus error (either BERR for a bus cycle, or EXBERR for a local cycle), the SCB68175/8X821 asserts both LBERR AND RST/HLT. This will allow the local master to rerun the cycle.

The local master can then rerun the bus cycle using the same address, and the same data for a write. If this cycle is also terminated by a bus error, the SCB68175/8X821 will assert LBERR but not RST/HLT.

The EXBERR input is provided for local resources to initiate a retry sequence. Local devices may drive LBERR (an open collector output) directly to bypass the retry function.

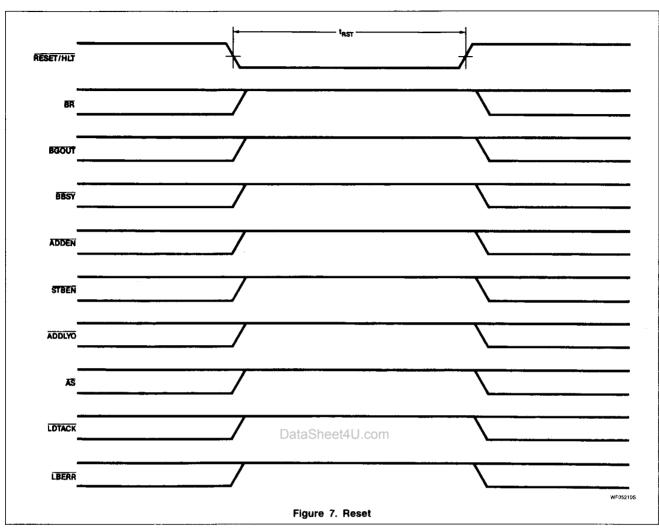

#### Reset

The SCB68175/8X821 must be reset as specified in the reset timing in order to ensure proper operation. When RST/HLT is asserted, the SCB68175/8X821 will drive all outputs high to release the bus. If the SCB68175/8X821 has control of the system bus and the local master fails, RST/HLT should be asserted. This will ensure that the system bus is relinquished by the SCB68175/8X821 Bus Controller.

January 1986

2-430

DataShe

# Signetics Microprocessor Products

**Bus Controller** SCB68175

#### ABSOLUTE MAXIMUM RATINGS1

| PARAMETER                                  | RATING         | UNIT |

|--------------------------------------------|----------------|------|

| Operating ambient temperature <sup>2</sup> | 0 to +70       | °C   |

| Storage temperature                        | -65 to +150    | °C   |

| Supply voltage                             | -0.5 to $+7.0$ | V    |

| Input voltage                              | -0.5 to $+5.5$ | V    |

#### DC ELECTRICAL CHARACTERISTICS TA = 0°C to + 70°C, VCC = 5.0V ± 5%4.5

|                                                       | 242445752                                                                          |                                                                                                 | LIMITS |                   | UNIT           |

|-------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|-------------------|----------------|

| PARAMETER                                             |                                                                                    | TEST CONDITIONS                                                                                 | Min    | Max               |                |

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IC</sub> | Input low voltage<br>Input high voltage<br>Input clamp diode voltage               | V <sub>CC</sub> = 4.75V, I <sub>IN</sub> = -18mA                                                | 2.0    | 0.8<br>-1.5       | V<br>V         |

| I <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>I</sub>  | Input low current<br>Input high current<br>Input high current                      | $V_{CC} = 5.25V, V_{IN} = 0.4V$ $V_{CC} = 5.25V, V_{IN} = 2.7V$ $V_{CC} = 5.25V, V_{IN} = 5.5V$ |        | -410<br>20<br>100 | μΑ<br>μΑ<br>μΑ |

| V <sub>OL</sub>                                       | Output low voltage LDTACK, ADDLYO, BGOUT, ADDEN, RST/HLT, LBERR, DTACK AS BR, BBSY | $V_{CC} = 4.75V$ $I_{OL} = 8mA$ $I_{OL} = 20mA$ $I_{OL} = 64mA$                                 |        | 0.5<br>0.5<br>0.5 | \ \ \ \ \ \ \  |

| V <sub>OH</sub>                                       | Output high voltage ADDLYO, BGOUT, ADDEN, STBEN                                    | $V_{CC} = 4.75V$ , $I_{OH} = -400\mu A$                                                         | 2.5    |                   | v              |

| I <sub>CEX</sub>                                      | Open collector leakage current<br>LDTACK, AS, AST/HLT, LBERR                       | V <sub>CC</sub> = 4.75V, V <sub>OUT</sub> = 5.25V                                               |        | 100               | μΑ             |

| los<br>Icc                                            | Short circuit output current  ADDLYÖ, BGOUT, ADDEN, STBEN  Supply current          | aSheet4UVcc                                                                                     | - 15   | - 100<br>140      | mA<br>mA       |

et4U.com

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is stress rating only and functional operation of the device at these or at any other condition above those indicated in the operation section of this specification is not implied.

- 2. For operating at elevated temperatures, the device must be derated based on + 150°C maximum junction temperature and thermal resistance of 60°C/W junction to ambient for ceramic package (116°C/W for plastic package).

- 3. This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima

- 4. Parameters are valid over specified temperature range

- 5. All voltage measurements are referenced to ground (GND). For testing, all inputs swing between 0.4V and 2.4V with a transition time of 3ns maximum and output voltages are checked at 0.8V and 2.0V.

- 6. At any time, no more than one output should be connected to ground.

- 7. If the asynchronous input requirement (t<sub>BG</sub>) is not satisfied, then BGOUT will be asserted low for the duration of BGIN low.

- 8. Requires minumum 35ns delay line connected between ADDLYO and ADDLYI.

- 9. If the asynchronous input requirement (t<sub>BRLS</sub>) is not satisfied, then BBSY will be negated (driven high) on the following assertion of LAS.

- 10. Valid only for system bus cycles not involving bus acquisition

- 11. BREL is a don't care until the leading edge of either ADDLYI or BGIN, whichever occurs last. If ADDLYI occurs last, then tols is valid. If BGIN occurs last, then  $t_{\mbox{\footnotesize{BGS}}}$  is valid. If they occur simultaneously, then  $t_{\mbox{\footnotesize{DIS}}}$  is valid.

- 12. Valid only with 35ns external delay line and if  $t_{BBY}$  (minimum) has been met 13. Valid from last leading edge of either  $\overline{\text{DTACK}/\text{BERR}}$  or  $\overline{\text{AS}}$ .

- 14. Only one of t<sub>REQ1</sub>, t<sub>REQ2</sub> is valid at once. If the falling edge of OFFBD occurs after the falling edge of LAS, then t<sub>REQ1</sub> is valid. If the falling edge of LAS occurs after the falling edge of OFFBD, then t<sub>REO2</sub> is valid. If both LAS and OFFBD occur simultaneously, then t<sub>REO2</sub> is valid.

- 15. Only one of tADN1, tADN2 is valid at once. If the falling edge of OFFBD occurs after the falling edge of LAS, then tADN1 is valid. If the falling edge of LAS occurs after the falling edge of OFFBD, then tADN2 is valid. If both LAS and OFFBD occur simultaneously, then tADN2 is valid.

- 16. The SCB68175/8X821 must see two falling edges of the clock after the rising edge of BERR/EXBERR before tgo is valid.

- 17. Valid only if no bus request is pending.

- 18. The SCB68175/8X821 will only assert LDTACK/LBERR with the high-to-low transition of DTACK/BERR. When running consecutive bus cycles, the SCB68175/ 8X821 will then ensure that any slow or lazy DTACK/BERR terminating the first cycle is not transmitted through to the local master interface.

- 19. These parameters are guaranteed at the values listed; these values were determined either by system bench testing or by Signetics' characterization procedures. All other tabular entries are taken directly from simulation results run at a range of operational frequencies; these values are not tested or guaranteed.

January 1986

2-431

# **Bus Controller**

SCB68175

# AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ} C$ to +70°C, $V_{CC} = 5.0 V \pm 5\%^{4,5}$

|                              |                                                         | LIMITS |     |      |  |

|------------------------------|---------------------------------------------------------|--------|-----|------|--|

| PARAMETER                    |                                                         | Min    | Max | UNIT |  |

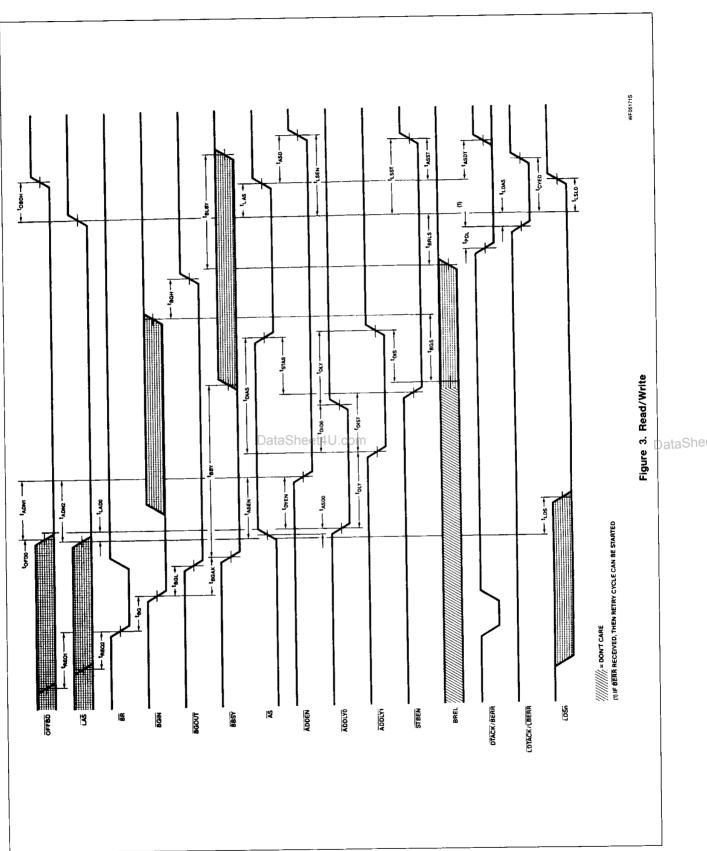

| Read/write (s                | see figure 3)                                           |        |     |      |  |

| t <sub>REQ1</sub> 14         | OFFBD low to BR low                                     |        | 56  | ns   |  |

| REQ2 <sup>14</sup>           | LAS low to BR low                                       |        | 56  | ns   |  |

| t <sub>BG</sub> <sup>7</sup> | BR low to BGIN low set-up                               | 0      |     | ns   |  |

| BGAK                         | BGIN low to BBSY low                                    |        | 32  | ns   |  |

| t <sub>BBY</sub> 8           | BBSY asserted width                                     | 90     |     | ns   |  |

| ASEN 13                      | AS, DTACK, BERR high to ADDEN low                       |        | 39  | ns   |  |

| DIST                         | ADDLYI low to STBEN Low                                 |        | 23  | ns   |  |

| STAS                         | STBEN low to AS low                                     |        | 14  | ns   |  |

| BRLS <sup>9</sup>            | BREL high to LAS high set-up time                       | 0      |     | ns   |  |

| ADN1 10, 15, 19              | OFFBD low to ADDEN low                                  |        | 37  | ns   |  |

| 10, 15<br>ADN2               | LAS low to ADDEN low                                    |        | 35  | ns   |  |

| OBDH                         | LAS high to OFFBD high hold time                        | 0      |     | ns   |  |

| BLBY 12                      | BREL high to BBSY high                                  |        | 65  | ns   |  |

| DYEN                         | ADDLYO low to ADDEN low                                 |        | 10  | ns   |  |

| DIDO                         | ADDLYI to ADDLYO                                        |        | 29  | ns   |  |

| t <sub>DLY</sub>             | ADDLYO high/low to ADDLYI high/low (minimum delay line) | 35     |     | ns   |  |

| tLAS <sup>19</sup>           | LAS high to AS high                                     |        | 11  | ns   |  |

| t <sub>LSEN</sub>            | LAS high to ADDEN high DataSheet4U.com                  |        | 25  | ns   |  |

| tLSST                        | LAS high to STBEN high                                  |        | 25  | ns   |  |

| t <sub>BGS</sub> 11          | BREL high to BGIN high set-up                           | 0      |     | ns   |  |

| t <sub>DIS</sub> 11          | BREL high to ADDLYI high set-up                         | 0      |     | ns   |  |

| t <sub>DIAS</sub>            | ADDLYI low to AS low                                    |        | 37  | ns   |  |

| tasst19                      | AS high to STBEN high                                   |        | 14  | ns   |  |

| tasp <sup>19</sup>           | AS high to ADDEN high                                   |        | 14  | ns   |  |

| t <sub>ASDT</sub>            | AS high to DTACK high                                   | 0      |     | ns   |  |

| tCYED                        | LAS high to LDTACK/LBERR high                           |        | 45  | ns   |  |

| t <sub>LSLD</sub>            | LAS high to LDSn high                                   | 0      |     | ns   |  |

| . 17                         | BGIN low to BGOUT low                                   | ***    | 57  | ns   |  |

| t <sub>BGL</sub> 17          | BGIN high to BGOUT high                                 |        | 57  | ns   |  |

| t <sub>LDS</sub>             | LAS low to LDSn low                                     | 0      |     | ns   |  |

| t <sub>LDSO</sub> 10         | LAS low to ADDLYO low                                   |        | 26  | ns   |  |

| toFDO <sup>10</sup>          | OFFBD low to ADDLYO low                                 |        | 26  | ns   |  |

| t <sub>ASDO</sub> 13         | AS, DTACK, BERR high to ADDLYO low                      |        | 38  | ns   |  |

et4U.com

DataShe

January 1986 2-432

DataSheet4U.com www.DataSheet4U.com

Signetics Microprocessor Products

## Bus Controller SCB68175

#### AC ELECTRICAL CHARACTERISTICS (Continued)

|                               |                                                         | LIMITS |                    | UNIT |

|-------------------------------|---------------------------------------------------------|--------|--------------------|------|

|                               | PARAMETER                                               |        | Max                |      |

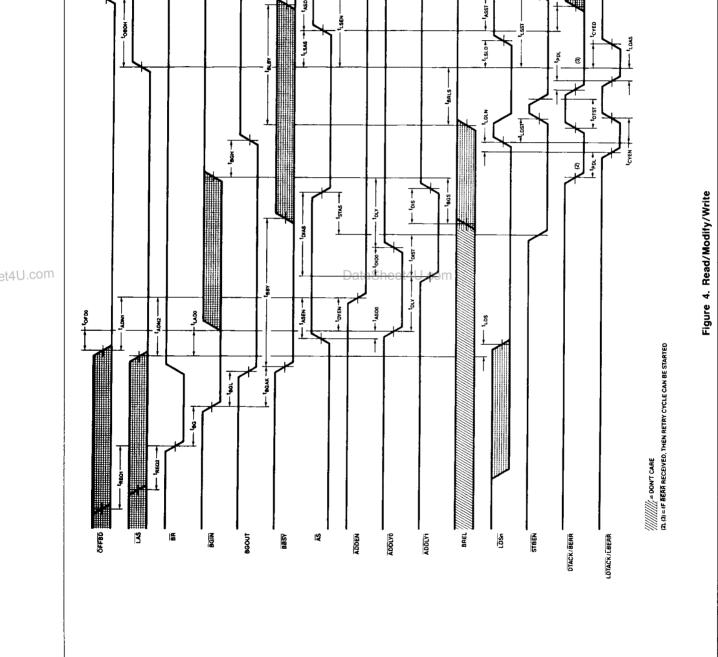

| Read-mod                      | lify-write (see figure 4)                               |        |                    |      |

| t <sub>PDL</sub> 18           | DTACK/BERR low time, LDTACK/LBERR low propagation delay |        | 28                 | ns   |

| tCYEN                         | Local data strobe 0 and 1 high to LDTACK/LBERR high     |        | 45                 | ns   |

| t <sub>LDA\$</sub>            | LDTACK/LBERR low to LAS high                            | 0      |                    | ns   |

| t <sub>LDST</sub>             | Local data strobe 0 and 1 high to STBEN high            |        | 32                 | ns   |

| t <sub>DTST</sub>             | DTACK/BERR high to STBEN                                |        | 38                 | ns   |

| t <sub>LDLN</sub>             | LDTACK/LBERR low to local data strobe 0 or 1 high       | 0      |                    | ns   |

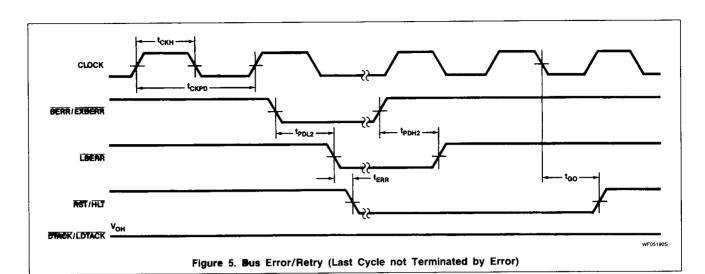

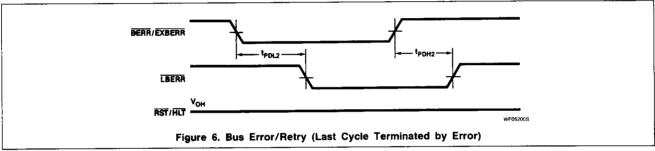

| Bus error                     | /retry and reset (see figures 5, 6 and 7)               |        |                    |      |

| t <sub>RST</sub>              | RST low time                                            |        | 3t <sub>CKPD</sub> | ns   |

| t <sub>CKH</sub>              | Clock high time                                         | 20     |                    | ns   |

| t <sub>CKPD</sub>             | Clock period                                            | 40     |                    | ns   |

| t <sub>PDL2</sub>             | BERR/EXBERR low to LBERR low propagation delay          |        | 28                 | ns   |

| t <sub>PDH2</sub>             | BERR/EXBERR high/to LBERR propagation delay             |        | 12                 | ns   |

| tean                          | LBERR low to RST/HLT low                                |        | 16                 | ns   |

| t <sub>GO</sub> <sup>16</sup> | Clock to RST/HLT high                                   |        | 38                 | ns   |

et4U.com

DataSheet4U.com

DataShe

January 1986 2-433

### **Bus Controller**

SCB68175

January 1986

2-434

DataSheet4U.com

et4U.com

DataShe

January 1986

2-435

DataSheet4U.com

et4U.com

DataSheet4U.com

2-436

January 1986

www.DataSheet4U.com

DataShe

DataSheet4U.com

et4U.com

January 1986 2-437

www.DataSheet4U.com

DataSheet4U.com