# CMOS GRAPHIC LCD/TV CONTROLLER

- For Medium-Scale LCD

- Output to LCD-Screen

- Virtual Screen Display RAM

- Enhanced Control Function

- Simultaneous LCD & TV Display

#### DESCRIPTION

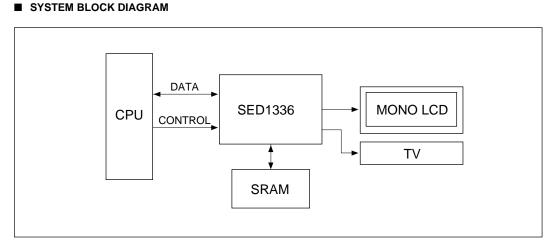

The SED1336 is a CMOS low-power dot matrix liquid crystal graphic display controller with built-in TV support. The built-in TV support IC is capable of displaying characters and graphic images simultaneously on TV monitors and flat panels.

The SED1336 has a built-in TV control circuit that generates either NTSC or PAL system synchronous signals, memory. The device stores the display data in external SRAM that is sent by an 8-bit microcomputer, and generates all the control signals required by the LCD drivers.

The controller incorporates an internal character generator ROM which supports user-defined characters. An external CG ROM can also be supported to provide additional characters.

The SED1336 can be interfaced to high-speed microprocessors such as the Intel 80xx family or the Motorola 68xx family. The controller supports a set of commands that allow the user to create a layered display of characters and graphics.

#### FEATURES

- Low-power CMOS fabrication

- Compatible with both Intel 80XX and Motorola 68XX high-speed MPU

- Display duty:

- LCD ..... 1/2 to 1/256 can be selected

- TV ..... 256 × 200 dots

- Internal and external character generator ROM

- Simultaneous LCD and TV operation

- Selectable display synthesis

- Programmable cursor movement

- Multimode display:

- 2 layers of overlapping character and graphic 3 layers of overlapping graphic

- Supports 64K bytes of memory

- Single power supply ..... 3.0V to 5.5V

- Package ..... Plastic QFP6-60 pin (FoA)

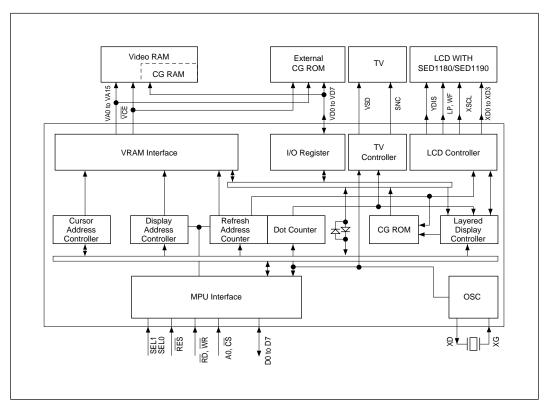

#### BLOCK DIAGRAM

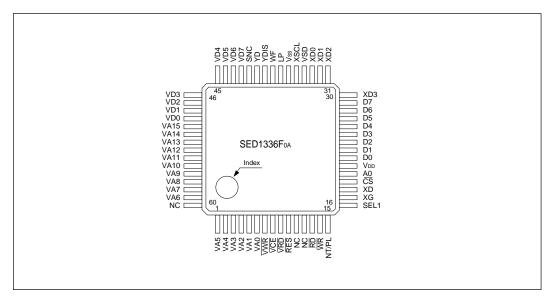

### PIN ASSIGNMENT DIAGRAM

#### PIN DESCRIPTION

| Name                      | Number             | Туре         | Description                                               |

|---------------------------|--------------------|--------------|-----------------------------------------------------------|

| VA0 to VA5<br>VA6 to VA15 | 6 to 1<br>59 to 50 | Output       | VRAM address bus                                          |

| VWR                       | 7                  | Output       | VRAM write signal                                         |

| VCE                       | 8                  | Output       | Memory control signal                                     |

| VRD                       | 9                  | Output       | VRAM read signal                                          |

| RES                       | 10                 | Input        | Reset                                                     |

| NC                        | 11, 60             | —            | No connection                                             |

| CLO                       | 12                 | Output       | Clock output                                              |

| RD                        | 13                 | Input        | 8080-family: Read signal<br>6800-family: Enable clock (E) |

| WR                        | 14                 | Input        | 8080-family: Write signal<br>6800-family: R/W signal      |

| NT/PL                     | 15                 | Input        | NTSC or PAL TV mode select                                |

| SEL1                      | 16                 | Input        | 8080- or 6800-family interface select                     |

| OSC1                      | 17                 | Input        | Oscillator connection                                     |

| OSC2                      | 18                 | Output       | Oscillator connection                                     |

| CS                        | 19                 | Input        | Chip select                                               |

| A0                        | 20                 | Input        | Data type select                                          |

| VDD                       | 21                 | Supply       | 3.0 to 5.5V supply                                        |

| D0 to D7                  | 22 to 29           | Input/output | Data bus                                                  |

| XD0 to XD3                | 30 to 33           | Output       | Data to LCD X-driver                                      |

| VSD                       | 34                 | Output       | Video data                                                |

| XSCL                      | 35                 | Output       | Data shift clock                                          |

| VSS                       | 36                 | Supply       | Ground                                                    |

| LP                        | 37                 | Output       | Latch pulse                                               |

| WF                        | 38                 | Output       | Frame signal                                              |

| YDIS                      | 39                 | Output       | Power-down signal when display is blanked                 |

| YD                        | 40                 | Output       | Scan start pulse                                          |

| SNC                       | 41                 | Output       | TV sync signal                                            |

| VD0 to VD7                | 42 to 49           | Input/output | VRAM data bus                                             |

#### ■ ELECTRICAL CHARACTERISTICS

### • Absolute Maximum Ratings

| Parameter                                       | Symbol  | Rating            | Unit |

|-------------------------------------------------|---------|-------------------|------|

| Supply voltage range                            | Vdd     | -0.3 to 7.0       | V    |

| Input voltage range                             | Vin     | -0.3 to VDD + 0.3 | V    |

| Power dissipation                               | PD      | 300               | mW   |

| Operating temperature range                     | Topr    | -20 to 75         | °C   |

| Storage temperature range                       | Tstg    | -65 to 150        | °C   |

| Soldering temperature (10 seconds). See note 1. | Tsolder | 260               | °C   |

1. The humidity resistance of the flat package may be reduced if the package is immersed in solder. Use a soldering technique that does not heatstress the package.

2. If the power supply has a high impedance, a large voltage differential can occur between the input and supply voltages. Take appropriate care with the power supply and the layout of the supply lines.

3. All supply voltages are referenced to Vss = 0V.

#### • DC Electrical Characteristics

|                                 | ,          | VDD = 4.5 to 5.5V, Vss = 0V, Ta = $-20$ to 75°C                |           |        |           |      |  |

|---------------------------------|------------|----------------------------------------------------------------|-----------|--------|-----------|------|--|

| Parameter                       | Symbol     | Condition                                                      | Min       | Тур    | Max       | Unit |  |

| Supply voltage                  | Vdd        |                                                                | 4.5       | 5.0    | 5.5       | V    |  |

| Register data retention voltage | Vно        |                                                                | 2.0       | —      | 6.0       | V    |  |

| Input leakage current           | LI         | VI = VDD. See note 6.                                          | —         | 0.05   | 2.0       | μA   |  |

| Output leakage current          | Ilo        | VI = Vss. See note 6.                                          | —         | 0.10   | 5.0       | μA   |  |

| Operating supply current        | lopr       | See note 4.                                                    | —         | 11     | 15        | mA   |  |

| Quiescent supply current        | lq         | Sleep mode,<br>VOSC1 = $V\overline{CS} = V\overline{RD} = VDD$ | —         | 0.05   | 20.0      | μA   |  |

| Oscillator frequency            | fosc       | Measured at crystal,                                           | 1.0       | _      | 10.0      | MHz  |  |

| External clock frequency        | fc∟        | 47.5% duty cycle.                                              | 1.0       | _      | 10.0      | MHz  |  |

| Oscillator feedback resistance  | Rf         | See note 7.                                                    | 0.5       | 1.0    | 3.0       | MΩ   |  |

| TTL                             | •          | ·                                                              |           |        |           |      |  |

| HIGH-level input voltage        | Viht       | See note 1.                                                    | 0.8Vdd    | _      | Vdd       | V    |  |

| LOW-level input voltage         | VILT       | See note 1.                                                    | Vss       | _      | 0.2Vdd    | V    |  |

| HIGH-level output voltage       | <b>ОНТ</b> | Iон = -5.0 mA.<br>See note 1.                                  | 2.4       | —      | _         | V    |  |

| LOW-level output voltage        | Volt       | IOL = 5.0 mA. See note 1.                                      | —         | _      | Vss + 0.4 | V    |  |

| CMOS                            | •          | ·                                                              |           |        |           |      |  |

| HIGH-level input voltage        | VIHC       | See note 2.                                                    | 0.8Vdd    | _      | Vdd       | V    |  |

| LOW-level input voltage         | VILC       | See note 2.                                                    | Vss       | _      | 0.2Vdd    | V    |  |

| HIGH-level output voltage       | Vонс       | Іон = -2.0 mA. See note 2.                                     | Vdd - 0.4 | —      | —         | V    |  |

| LOW-level output voltage        | Volc       | IOH = 1.6 mA. See note 2.                                      | —         | _      | Vss + 0.4 | V    |  |

| Open-drain                      |            |                                                                |           |        |           |      |  |

| LOW-level output voltage        | Voln       | IOL = 6.0  mA. See note 5.                                     | —         | —      | Vss + 0.4 | V    |  |

| Schmitt-trigger                 |            |                                                                |           |        |           |      |  |

| Rising-edge threshold voltage   | Vt+        | See note 3.                                                    | 0.5Vdd    | 0.7Vdd | 0.8Vdd    | V    |  |

| Falling-edge threshold voltage  | Vt-        | See note 3.                                                    | 0.2Vdd    | 0.3Vdd | 0.5Vdd    | V    |  |

Notes:

- 1. D0 to D7, A0,  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , VD0 to VD7, VA0 to VA15,  $\overline{VRD}$ ,  $\overline{VWR}$  and  $\overline{VCE}$  are TTL-level inputs.

- SEL1 and NT/PL are CMOS-level inputs. YD, XD0 to XD3, XSCL, LP, WF, YDIS and CLO are CMOS-level outputs.

- 3.  $\overline{\text{RES}}$  is a Schmitt-trigger input. The pulsewidth on  $\overline{\text{RES}}$  must be at least 200  $\mu s.$  Note that pulses of more than a few seconds will cause DC voltages to be applied to the LCD panel.

- 4. fOSC = 10 MHz, no load (no display memory), internal character generator, 256 × 200 pixel display. The operating supply current can be reduced by approximately 1 mA by setting both CLO and the display OFF.

- SNC and VSD are n-channel, open-drain outputs. The voltage on the outputs should not exceed Vbb as internal diodes connect the pins to Vbb (SED1336F only).

- 6. VD0 to VD7 and D0 to D7 have internal feedback circuits so that if the inputs become high-impedance, the input state immediately prior to that is held. Because of the feedback circuit, input current flow occurs when the inputs are in an intermediate state.

- Because the oscillator circuit input bias current is in the order of μA, design the printed circuit board so as to reduce leakage currents.

|                                 |        |                                                                  | - 0.0 10 4.0 | ,        | - ,       |      |

|---------------------------------|--------|------------------------------------------------------------------|--------------|----------|-----------|------|

| Parameter                       | Symbol | Condition                                                        | Min          | Тур      | Max       | Unit |

| Supply voltage                  | Vdd    | See note 8.                                                      | 3.0          | 3.5      | 4.5       | V    |

| Register data retention voltage | Vно    |                                                                  | 2.0          | —        | 6.0       | V    |

| Input leakage current           | ILI    | VI = VDD. See note 6.                                            | —            | 0.05     | 2.0       | μA   |

| Output leakage current          | Ilo    | VI = Vss. See note 6.                                            | —            | 0.10     | 5.0       | μA   |

| Operating supply current        | lopr   | VDD = 3.5V. See note 4.<br>See note 4.                           | _            | 3.5<br>— | —<br>7.0  | mA   |

| Quiescent supply current        | lq     | Sleep mode,<br>Vosc1 = $V\overline{cs}$ = $V\overline{RD}$ = VDD | —            | 0.05     | 20.0      | μΑ   |

| Oscillator frequency            | fosc   | Measured at crystal,                                             | 1.0          | _        | 8.0       | MHz  |

| External clock frequency        | fc∟    | 47.5% duty cycle.                                                | 1.0          | —        | 8.0       | MHz  |

| Oscillator feedback resistance  | Rf     | See note 7.                                                      | 0.7          | —        | 3.0       | MΩ   |

| TTL                             |        |                                                                  |              |          |           |      |

| HIGH-level input voltage        | VIHT   | See note 1.                                                      | 0.8Vdd       | —        | Vdd       | V    |

| LOW-level input voltage         | VILT   | See note 1.                                                      | Vss          | —        | 0.2Vdd    | V    |

| HIGH-level output voltage       | Vонт   | Іон = –3.0 mA.<br>See note 1.                                    | 2.4          | —        | —         | V    |

| LOW-level output voltage        | Volt   | IoL = 3.0 mA. See note 1.                                        | —            | _        | Vss + 0.4 | V    |

| CMOS                            |        |                                                                  |              |          |           |      |

| HIGH-level input voltage        | VIHC   | See note 2.                                                      | 0.8Vdd       | _        | Vdd       | V    |

| LOW-level input voltage         | VILC   | See note 2.                                                      | Vss          | _        | 0.2Vdd    | V    |

| HIGH-level output voltage       | Vонс   | Iон = -2.0 mA. See note 2.                                       | Vdd - 0.4    | _        | —         | V    |

| LOW-level output voltage        | Volc   | Іон = 1.6 mA. See note 2.                                        | —            |          | Vss + 0.4 | V    |

| Open-drain                      |        |                                                                  |              |          | · · ·     |      |

| LOW-level output voltage        | Voln   | IoL = 6.0 mA. See note 5.                                        | —            | _        | Vss + 0.4 | V    |

| Schmitt-trigger                 |        |                                                                  |              |          | · · ·     |      |

| Rising-edge threshold voltage   | VT+    | See note 3.                                                      | 0.5Vdd       | 0.7Vdd   | 0.8Vdd    | V    |

| Falling edge threshold voltage  | Vt–    | See note 3.                                                      | 0.2Vdd       | 0.3Vdd   | 0.5Vdd    | V    |

VDD = 3.0 to 4.5V, Vss = 0V, Ta = -20 to  $75^{\circ}C$

Notes:

- 1. D0 to D7, A0,  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , VD0 to VD7, VA0 to VA15, VRD,  $\overline{VWR}$  and  $\overline{VCE}$  are TTL-level inputs.

- SEL1 and NT/PL are CMOS-level inputs. YD, XD0 to XD3, XSCL, LP, WF, YDIS and CLO are CMOS-level outputs.

- 3.  $\overline{\text{RES}}$  is a Schmitt-trigger input. The pulsewidth on  $\overline{\text{RES}}$  must be at least 200  $\mu s.$  Note that pulses of more than a few seconds will cause DC voltages to be applied to the LCD panel.

- fOSC = 10 MHz, no load (no display memory), internal character generator, 256 × 200 pixel display. The operating supply current can be reduced by approximately 1 mA by setting both CLO and the display OFF.

- SNC and VSD are n-channel, open-drain outputs. The voltage on the outputs should not exceed VDD as internal diodes connect the pins to VDD.

- 6. VD0 to VD7 and D0 to D7 have internal feedback circuits so that if the inputs become high-impedance, the input state immediately prior to that is held. Because of the feedback circuit, input current flow occurs when the inputs are in an intermediate state.

- Because the oscillator circuit input bias current is in the order of μA, design the printed circuit board so as to reduce leakage currents.

- 8. VDD = 2.7 to 4.5V (SED1335F)

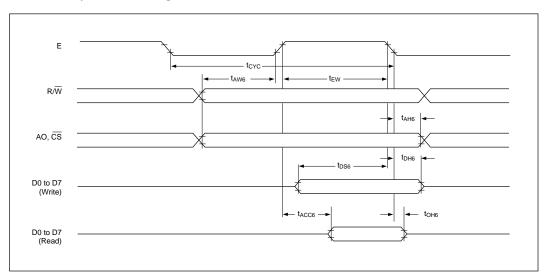

Timing Diagrams

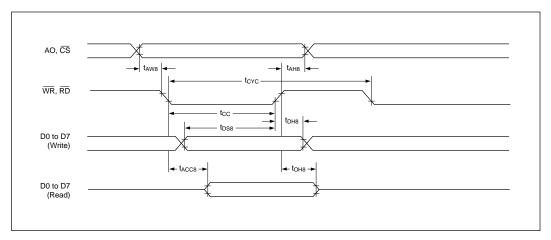

8080-Family Interface Timing

Ta = -20 to  $75^{\circ}C$

| Signal              | Symbol | Parameter -         | VDD = 4.5 | 5 to 5.5V | VDD = 3.0 | ) to 4.5V | Unit | Condition |

|---------------------|--------|---------------------|-----------|-----------|-----------|-----------|------|-----------|

| Signal              | Symbol | i arameter          |           | max       | min       | max       | Unit | Condition |

| A0, <del>CS</del> – | tah8   | Address hold time   | 10        | —         | 10        | —         | ns   |           |

|                     | taw8   | Address setup time  | 0         | —         | 0         | —         | ns   |           |

| WR, RD              | tCYC   | System cycle time   | See note  | —         | See note  | —         | ns   |           |

|                     | tcc    | Strobe pulsewidth   | 120       | —         | 140       | —         | ns   | CL = 100  |

|                     | tDS8   | Data setup time     | 120       | —         | 120       | —         | ns   | pF        |

| D0 to D7            | tdh8   | Data hold time      | 5         | —         | 5         | —         | ns   |           |

|                     | tACC8  | RD access time      | _         | 50        | _         | 70        | ns   |           |

|                     | tонв   | Output disable time | 10        | 50        | 10        | 50        | ns   |           |

Note: For memory control and system control commands:

$t_{CYC8} = 2t_{C} + t_{CC} + t_{CEA} + 75 > t_{ACV} + 245$

For all other commands:

$t_{CYC8} = 4t_{C} + t_{CC} + 30$

• 6800-Family Interface Timing

**Note:** tcyc6 indicates the interval during which  $\overline{CS}$  is LOW and E is HIGH.

$T_a = -20$  to  $75^{\circ}C$

| Signal            | Symbol | Parameter           | VDD = 4.5 | 5 to 5.5V | VDD = 3.0 | ) to 4.5V | Unit | Condition |

|-------------------|--------|---------------------|-----------|-----------|-----------|-----------|------|-----------|

| Signal            | Symbol | raiametei           |           | max       | min       | max       | Unit | Condition |

| A0,               | tCYC6  | System cycle time   | See note  | —         | See note  | —         | ns   |           |

| A0,<br>CS,<br>R/W | tAW6   | Address setup time  | 0         | —         | 10        | —         | ns   |           |

| R/W               | tah6   | Address hold time   | 0         | —         | 0         | —         | ns   |           |

|                   | tDS6   | Data setup time     | 100       | —         | 120       | —         | ns   | CL =      |

| D0 to D7          | tDH6   | Data hold time      | 0         | —         | 0         | —         | ns   | 100 pF    |

| 001007            | tOH6   | Output disable time | 10        | 50        | 10        | 70        | ns   |           |

|                   | tACC6  | Access time         | —         | 85        | —         | 120       | ns   |           |

| E                 | tew    | Enable pulsewidth   | 120       | _         | 140       | _         | ns   |           |

Note: For memory control and system control commands:

tCYC6 = 2tC + tEW + tCEA + 75 > tACV + 245

For all other commands:

tCYC6 = 4tC + tEW + 30

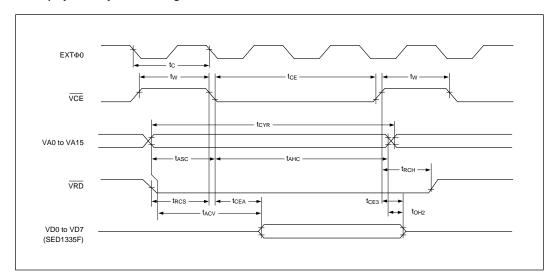

# • Display Memory Read Timing

$T_a = -20$  to  $75^{\circ}C$

| Cianal         | Symbol       | Doromotor                                     | VDD = 4. | 5 to 5.5V | VDD = 3. | 0 to 4.5V | Linit | Condition   |

|----------------|--------------|-----------------------------------------------|----------|-----------|----------|-----------|-------|-------------|

| Signal         | Symbol       | Parameter                                     | min      | max       | min      | max       | Unit  | Condition   |

| EXT <i>φ</i> 0 | tc           | Clock period                                  | 100      | —         | 125      | —         | ns    |             |

| VCE            | tw           | VCE HIGH-level<br>pulsewidth                  | tc - 50  | _         | tc - 50  | _         | ns    |             |

| VOL            | tCE          | VCE LOW-level<br>pulsewidth                   | 2tc - 30 | _         | 2tc - 30 |           | ns    |             |

|                | tCYR         | Read cycle time                               | 3tc      | —         | 3tc      | —         | ns    |             |

| VA0 to<br>VA15 | tasc         | Address setup time to falling edge of VCE     | tc – 70  | _         | tc - 100 |           | ns    |             |

|                | <b>t</b> AHC | Address hold time from<br>falling edge of VCE | 2tc – 30 | _         | 2tc - 40 | _         | ns    | CL = 100 pF |

| VRD            | tRCS         | Read cycle setup time to falling edge of VCE  | tc – 45  | _         | tc – 55  | _         | ns    |             |

| VILD           | trch         | Read cycle hold time from rising edge of VCI  | 0.5tc    | —         | 0.5tc    | _         | ns    |             |

|                | tacv         | Address access time                           | —        | 3tc - 100 | —        | 3tc – 110 | ns    |             |

| VD0 to         | <b>t</b> CEA | VCE access time                               | —        | 2tc - 80  | —        | 2tc - 85  | ns    | 1           |

| VD7            | tOH2         | Output data hold time                         | 0        | —         | 0        | —         | ns    | ]           |

|                | tCE3         | VCE to data off time                          | 0        | _         | 0        | _         | ns    |             |

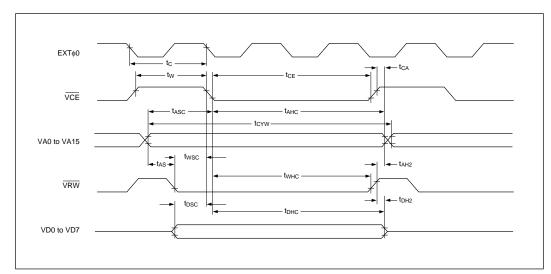

• Display Memory Write Timing

#### Ta = -20 to $75^{\circ}C$

| Signal         | Symbol       | Parameter                                                     | VDD = 4. | 5 to 5.5V | VDD = 3.0 | ) to 4.5V | Unit | Condition      |

|----------------|--------------|---------------------------------------------------------------|----------|-----------|-----------|-----------|------|----------------|

| Oignai         | Cymbol       | i arameter                                                    | min      | max       | min       | max       | Onic | Condition      |

| EXT <i>φ</i> 0 | tc           | Clock period                                                  | 100      | _         | 125       | _         | ns   |                |

| VCE            | tw           | VCE HIGH-level pulse-<br>width                                | tc - 50  |           | tc - 50   | _         | ns   |                |

| 102            | tCE          | VCE LOW-level pulse-<br>width                                 | 2tc - 30 |           | 2tc - 30  | _         | ns   |                |

|                | tCYW         | Write cycle time                                              | 3tc      | -         | 3tc       |           | ns   |                |

|                | <b>t</b> AHC | Address hold time from falling edge of VCE                    | 2tc - 30 |           | 2tc - 40  |           | ns   |                |

|                | tasc         | Address setup time to falling edge of VCE                     | tc – 70  | _         | tc - 100  |           | ns   |                |

| VA0 to<br>VA15 | tCA          | Address hold time from rising edge of $\overline{\text{VCE}}$ | 0        |           | 0         | _         | ns   |                |

|                | tas          | Address setup time to falling edge of VWR                     | 0        | _         | 0         | -         | ns   | CL =<br>100 pF |

|                | tAH2         | Address hold time from rising edge of VWR                     | 10       |           | 10        |           | ns   |                |

| VWR            | twsc         | Write setup time to falling edge of VCE                       | tc - 80  |           | tc – 110  |           | ns   |                |

|                | twnc         | Write hold time from falling edge of VCE                      | 2tc – 20 | _         | 2tc - 20  |           | ns   |                |

|                | tDSC         | Data input setup time to falling edge of $\overline{VCE}$     | tc - 85  | _         | tc – 120  | —         | ns   |                |

| VD0 to<br>VD7  | <b>t</b> DHC | Data input hold time<br>from falling edge of VCE              | 2tc - 30 | —         | 2tc - 30  | —         | ns   |                |

|                | tDH2         | Data hold time from rising edge of VWR                        | 5        | 50        | 5         | 50        | ns   |                |

Note: VD0 to VD7 are latching input/outputs. While the bus is high impedance, VD0 to VD7 retain the write data until the data read from the memory is placed on the bus.

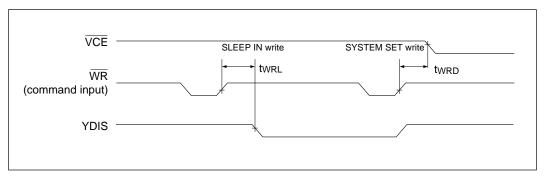

### • SLEEP IN Command Timing

$T_a = -20$  to  $75^{\circ}C$

| Signal | Symbol       | Symbol Parameter             | VDD = 4.5 to 5.5V |     | VDD = 3.0 to 4.5V |     | Unit       | Condition |

|--------|--------------|------------------------------|-------------------|-----|-------------------|-----|------------|-----------|

|        | i didiliotor | min                          | max               | min | max               | 01m | Contaition |           |

| WR -   | twrd         | VCE falling-edge delay time  | *1                | _   | *1                | _   | ns         | CL =      |

|        | twrL         | YDIS falling-edge delay time | —                 | *2  | —                 | *2  | ns         | 100 pF    |

1. twrd = 18tc + toss + 40 (toss is the time delay from the sleep state until stable operation)

2. twrl =  $36tc \times [TC/R] \times [L/F] + 70$

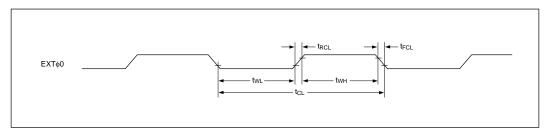

### • External Oscillator Signal Timing

$T_a = -20$  to  $75^{\circ}C$

| Signal         | Symbol | Parameter                               | VDD = 4. | VDD = 4.5 to 5.5V |     | VDD = 3.0 to 4.5V |      | Condition |

|----------------|--------|-----------------------------------------|----------|-------------------|-----|-------------------|------|-----------|

| Olghai         | Cymbol | T diameter                              | min      | max               | min | max               | Unit | Condition |

| ЕХТ <i>ф</i> 0 | tRCL   | External clock rise time                | —        | 15                | —   | 15                | ns   |           |

|                | tFCL   | External clock fall time                | _        | 15                | _   | 15                | ns   |           |

|                | twн    | External clock<br>HIGH-level pulsewidth | *1       | *2                | *1  | *2                | ns   |           |

|                | twL    | External clock<br>LOW-level pulsewidth  | *1       | *2                | *1  | *2                | ns   |           |

|                | tc     | External clock period                   | 100      | _                 | 125 | _                 | ns   |           |

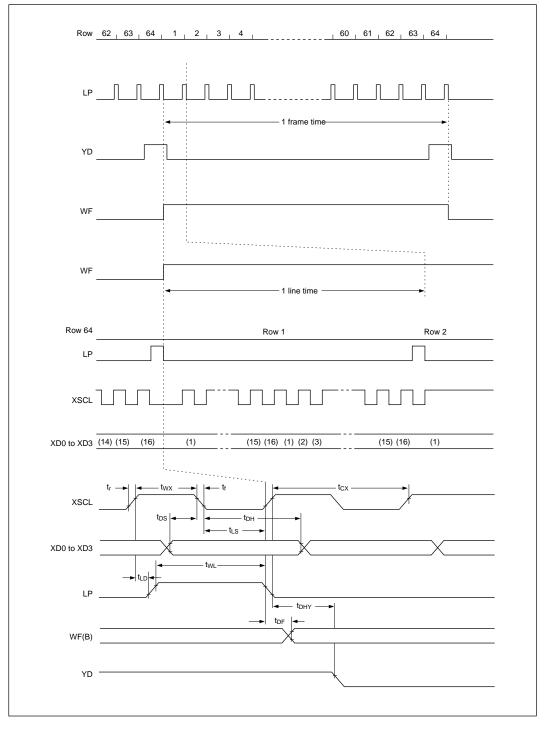

# • LCD Output Timing

The following characteristics are for a 1/64 duty cycle.

|         |              |                         |           |                   |           |                   | Ta =   | –20 to 75°C |

|---------|--------------|-------------------------|-----------|-------------------|-----------|-------------------|--------|-------------|

| Signal  | Symbol       | Parameter               | VDD = 4.  | VDD = 4.5 to 5.5V |           | VDD = 3.0 to 4.5V |        | Condition   |

| Cigilai | Cymbol       | T didinotor             | min       | max               | min       | max               | - Unit | Contaition  |

|         | tr           | Rise time               | —         | 30                | —         | 35                | ns     |             |

|         | tf           | Fall time               | —         | 30                | —         | 35                | ns     |             |

| XSCL    | tcx          | Shift clock cycle time  | 4tc       | —                 | 4tc       | —                 | ns     |             |

| XOOL    | twx          | XSCL clock pulsewidth   | 2tc - 60  | —                 | 2tc - 60  | —                 | ns     |             |

| XD0 to  | tdн          | X data hold time        | 2tc - 50  | —                 | 2tc - 50  | —                 | ns     | CL=         |

| XD3     | tDS          | X data setup time       | 2tc - 100 | —                 | 2tc - 100 | —                 | ns     | 100 pF      |

|         | t∟s          | Latch data setup time   | 2tc - 50  | _                 | 2tc - 50  | _                 | ns     |             |

| LP      | twL          | LP pulsewidth           | 4tc - 80  | _                 | 4tc - 100 | _                 | ns     |             |

|         | tLD          | LP delay time from XSCI | 0         |                   | 0         | _                 | ns     |             |

| WF      | tDF          | Permitted WF delay      | —         | 50                | —         | 50                | ns     |             |

| YD      | <b>t</b> DHY | Y data hold time        | 2tc - 20  | _                 | 2tc - 20  | —                 | ns     |             |

Note: The SED1336F reads display memory data from the address of the top left corner of the display screen, then scans horizontally until it reaches the address for the bottom right corner of the display screen. Therefore, each line of X-driver data is sent starting from the left side of the display line.