# n -Balance<sup>TM</sup> PWM Power Switch Fixed 50KHz Fsw

#### **FEATURES**

- ◆ Built-in 600V Power MOSFET

- Proprietary η -Balance<sup>TM</sup> Control to Boost Light Load Efficiency

- ◆ Proprietary "Zero OCP/OPP Recovery Gap" Control

- ♦ Fixed 50KHz Switching Frequency

- ♦ Built-in Soft Start Function

- ♦ Very Low Startup Current

- Frequency Reduction and Burst Mode Control for Energy Saving

- **♦** Current Mode Control

- Built-in Frequency Shuffling

- **♦** Built-in Synchronous Slope Compensation

- ◆ Cycle-by-Cycle Current Limiting

- Built-in Leading Edge Blanking (LEB)

- ◆ Constant Power Limiting

- ♦ Pins Floating Protection

- **♦** Audio Noise Free Operation

- ♦ VDD OVP & Clamp

- VDD Under Voltage Lockout (UVLO)

#### **APPLICATIONS**

Offline AC/DC Flyback Converter for

- **♦** AC/DC Adaptors

- **♦** Open-frame SMPS

- ♦ Set-Top Box Power Supplies

- ATX Standby Power

#### GENERAL DESCRIPTION

SF1533 is a high performance, high efficiency, highly integrated current mode PWM power switch for offline flyback converter applications.

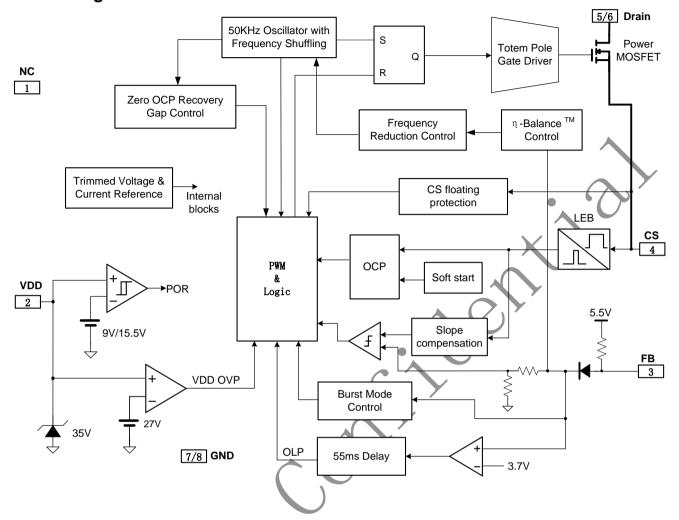

In SF1533, PWM switching frequency with shuffling is fixed to 50KHz and is trimmed to tight range. When the output power demands decrease, the IC decreases switching frequency based on the proprietary **\eta** -**Balance**<sup>TM</sup> control to boost power conversion efficiency at the light load. When output power falls below a given value, the IC enters into burst mode and provides excellent efficiency without audio noise.

The IC can achieve "**Zero OCP/OPP Recovery Gap**" using SiFirst's proprietary control algorithm. Meanwhile, the OCP/OPP variation versus universal line input is compensated.

The IC has built-in synchronized slope compensation to prevent sub-harmonic oscillation at high PWM duty output. The IC also has built-in soft start function to soften the stress on the MOSFET during power on period.

SF1533 integrates functions and protections of Under Voltage Lockout (UVLO), VCC Over Voltage Protection (OVP), Cycle-by-cycle Current Limiting (OCP), Pins Floating Protection, Over Load Protection (OLP), VCC Clamping, Leading Edge Blanking (LEB), etc.

SF1533 is available in SOP8 packages.

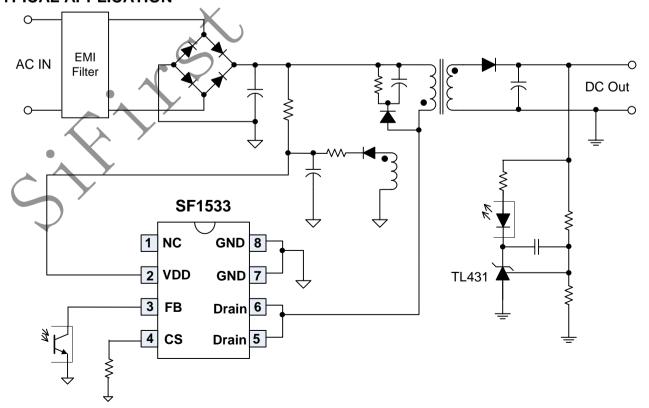

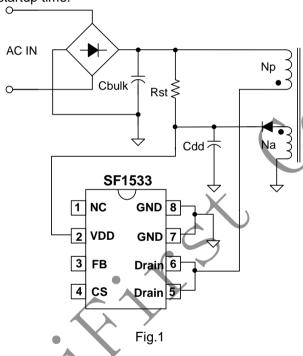

### TYPICAL APPLICATION

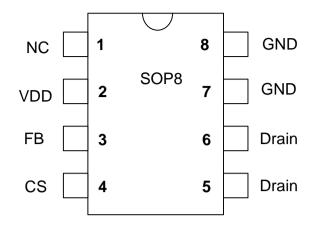

# **Pin Configuration**

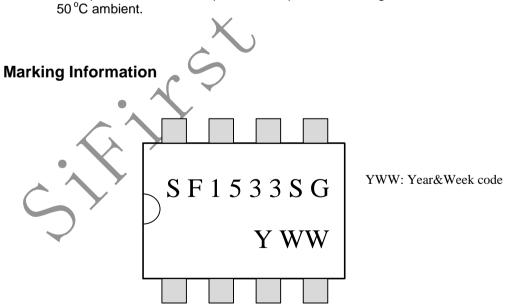

**Ordering Information**

| Part Number | Top Mark | Pac  | kage  | Tape & Reel |

|-------------|----------|------|-------|-------------|

| SF1533SG    | SF1533SG | SOP8 | Green |             |

| SF1533SGT   | SF1533SG | SOP8 | Green | Yes         |

**Output Power Table**(1)

| Part Number | 230VAC ± 15% <sup>(2)</sup> | 85-265VAC              |

|-------------|-----------------------------|------------------------|

|             | Adapter <sup>(3)</sup>      | Adapter <sup>(3)</sup> |

| SF1533      | 7W                          | 5.5W                   |

- Note 1. The Max. output power is limited by junction temperature

- Note 2. 230VAC or 100/115VAC with doublers

- **Note 3.** Typical continuous power in a non-ventilated enclosed adapter with sufficient drain pattern as a heat sink at 50 °C ambient.

- **Note 4.** Max. practical continuous power in a open-frame design with sufficient drain pattern as a heat sink at 50 °C ambient.

# **Block Diagram**

**Pin Description**

| Pin Num | Pin Name | 1/0        | Description                                                                                                                                                                              |

|---------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | NC       | (          | No connect.                                                                                                                                                                              |

| 2       | VDD      | )<br>P     | IC power supply pin.                                                                                                                                                                     |

| 3       | FB       | <b>X</b> - | Voltage feedback pin. The loop regulation is achieved by connecting a photo-coupler to this pin. PWM duty cycle is determined by this pin voltage and the current sense signal at Pin 4. |

| 4       | CS       | I          | Current sense input pin.                                                                                                                                                                 |

| 5-6     | Drain    | Р          | High voltage power MOSFET drain connection.                                                                                                                                              |

| 7-8     | GND      | Р          | Ground.                                                                                                                                                                                  |

**Absolute Maximum Ratings** (Note 5)

| Parameter                              | Value       | Unit |

|----------------------------------------|-------------|------|

| VDD DC Supply Voltage                  | 35          | V    |

| VCC DC Clamp Current                   | 10          | mA   |

| Drain pin                              | -0.3 to 600 | V    |

| FB, CS voltage range                   | -0.3 to 7   | V    |

| Package Thermal Resistance (SOP-8)     | 150         | °C/W |

| Maximum Junction Temperature           | 150         | °C   |

| Operating Temperature Range            | -40 to 85   | °C   |

| Storage Temperature Range              | -65 to 150  | °C   |

| Lead Temperature (Soldering, 10sec.)   | 260         | °C   |

| ESD Capability, HBM (Human Body Model) | 3           | kV   |

| ESD Capability, MM (Machine Model)     | 250         | V    |

**Recommended Operation Conditions** (Note 6)

| Parameter                     | Value     | Unit |

|-------------------------------|-----------|------|

| Supply Voltage, VDD           | 11 to 25  | V    |

| Operating Ambient Temperature | -40 to 85 | °C   |

# **ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C, VDD=18V, if not otherwise noted)$

| Symbol Parameter         |                        | Test Conditions               | Min                                     | Тур          | Max     | Unit |

|--------------------------|------------------------|-------------------------------|-----------------------------------------|--------------|---------|------|

|                          | Section (VDD Pin)      | 1000 001101110110             |                                         | - <b>7</b> P | 1110121 | 1 0  |

| UVLO(ON)                 | VDD Under Voltage      |                               | 14.5                                    | 15.5         | 16.5    | À    |

| OVLO(OIV)                | Lockout Exit (Startup) |                               | 14.5                                    | 13.3         | 10.5    |      |

| UVLO(OFF)                | VDD Under Voltage      |                               | 8                                       | 9            | 9.8     | V    |

| 0110(011)                | Lockout Enter          |                               |                                         |              | 3.0     |      |

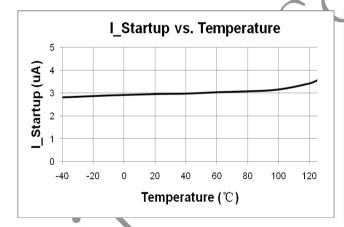

| I_Startup                | VDD Start up Current   | VDD =UVLO(ON)-1V,             |                                         | 3            | 15      | иA   |

| 0.aap                    | 122 Start up Sarrow    | Measure current into VDD      |                                         |              |         |      |

| I_VDD_Op                 | Operation Current      | V <sub>FB</sub> =3V           |                                         | 2.0          | 3.5     | mA   |

| VDD OVP                  | VDD Over Voltage       | 1.5                           | 25                                      | 27           | 29      | V    |

| _                        | Protection trigger     |                               |                                         |              |         |      |

| V <sub>DD</sub> _Clamp   | VDD Zener Clamp        | $I(V_{DD}) = 10mA$            | ^                                       | 35.5         |         | V    |

| ,                        | Voltage                | ( 22 )                        |                                         |              |         |      |

| T_Softstart              | Soft Start Time        |                               | IV.                                     | 4            |         | mSec |

| Feedback Input           | Section(FB Pin)        |                               |                                         |              |         |      |

| V <sub>FB</sub> Open     | FB Open Voltage        |                               | \ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \ | 5.5          |         | V    |

| . 5_ 1                   | ,                      |                               |                                         |              |         |      |

| I <sub>FB</sub> _Short   | FB short circuit       | Short FB pin to GND,          |                                         | 1.2          |         | mA   |

|                          | current                | measure current               |                                         |              |         |      |

| A <sub>VCS</sub>         | PWM Input Gain         | $\Delta V_{FB}/\Delta V_{cs}$ |                                         | 1.6          |         | V/V  |

| VFB_min_duty             | FB under voltage gate  | 4 \                           |                                         | 1.0          |         | V    |

|                          | clock is off.          |                               |                                         |              |         |      |

| V <sub>TH</sub> _PL      | Power Limiting FB      | $\wedge$ ( ) $'$              |                                         | 3.7          |         | V    |

|                          | Threshold Voltage      |                               |                                         |              |         |      |

| T <sub>D</sub> _PL       | Power limiting         | Note 7                        |                                         | 55           |         | mSec |

|                          | Debounce Time          |                               |                                         |              |         |      |

| Z <sub>FB</sub> _IN      | Input Impedance        |                               |                                         | 5            |         | Kohm |

|                          | nput Section (CS Pin)  | l .                           |                                         |              |         |      |

| Vth_OC_min               | Internal current       | Zero duty cycle               | 0.70                                    | 0.75         | 0.80    | V    |

|                          | limiting threshold     |                               |                                         |              |         |      |

| T_blanking               | CS Input Leading       |                               |                                         | 250          |         | nSec |

|                          | Edge Blanking Time     |                               |                                         |              |         |      |

| T <sub>D</sub> OC        | Over Current           |                               |                                         | 90           |         | nSec |

|                          | Detection and Control  |                               |                                         |              |         |      |

|                          | Delay                  |                               |                                         |              |         |      |

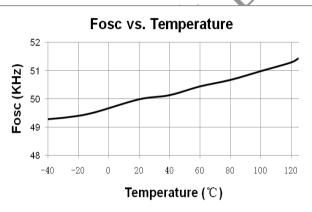

| Oscillator Section       |                        |                               | ,                                       | ,            | ,       |      |

| Fosc                     | Normal Oscillation     |                               | 45                                      | 50           | 55      | KHZ  |

|                          | Frequency              |                               |                                         |              |         |      |

| $\Delta$ F(shuffle)/Fosc | Frequency shuffling    | Note 8                        | -4                                      |              | 4       | %    |

|                          | range                  |                               |                                         | _            |         |      |

| ∆f_Temp                  | Frequency              | -20°C to 100 °C (Note 7)      |                                         | 5            |         | %    |

|                          | Temperature Stability  | \/DD 40.05\/                  |                                         |              |         | 0.4  |

| $\Delta f$ _VDD          | Frequency Voltage      | VDD = 12-25V,                 |                                         | 5            |         | %    |

| Duty mai:                | Stability Duty avala   |                               | 75                                      | 00           | 0.5     | 0/   |

| Duty_max                 | Maximum Duty cycle     |                               | 75                                      | 80           | 85      | %    |

| F_BM                     | Burst Mode Base        |                               | 1                                       | 22           |         | KHZ  |

| Dawer MOOFET             | Frequency (8)          |                               | 1                                       | 1            | 1       |      |

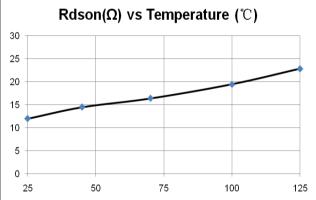

| Power MOSFET             |                        | I                             | 000                                     | 1            | 1       |      |

| BVdss                    | Power MOSFET           |                               | 600                                     |              |         | V    |

|                          | Drain Source           |                               | 1                                       | 1            |         |      |

|                          | Breakdown Voltage      |                               |                                         |              |         |      |

| Rdson               | Static Drain-Source On Resistance  | I(Drain)=0.5A | 12  | 15 | Ω  |

|---------------------|------------------------------------|---------------|-----|----|----|

| Idss                | Zero Gate Voltage<br>Drain Current |               |     | 1  | uA |

| Td <sub>(on)</sub>  | Turn-on delay time                 |               | 5.5 |    | ns |

| Td <sub>(off)</sub> | Turn-off delay time                |               | 13  |    | ns |

- **Note 5.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- **Note 6.** The device is not guaranteed to function outside its operating conditions.

- Note 7. Guaranteed by design.

- Note 8. These parameters, although guaranteed, are not 100% tested in production

# **CHARACTERIZATION PLOTS**

### **OPERATION DESCRIPTION**

SF1533 is a high performance, high efficiency, highly integrated current mode PWM power switch for offline flyback converter applications. The built-in advanced energy saving with high level protection features improves the SMPS reliability and performance without increasing the system cost.

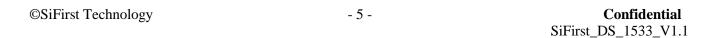

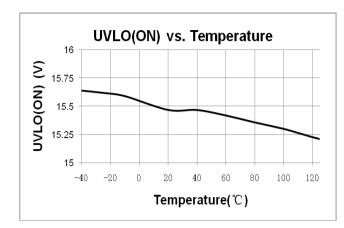

### UVLO and Startup Operation

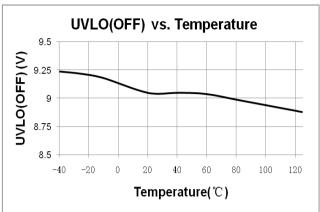

Fig.1 shows a typical startup circuit. Before the IC begins switching operation, it consumes only startup current (typically 3uA) and current supplied through the startup resistor Rst charges the VDD hold-up capacitor Cdd. When VDD reaches UVLO turn-on voltage of 15.5V(typical), SF1533 begins switching and the IC current consumed increased to 2mA (typical). The hold-up capacitor Cdd continues to supply VDD before the energy can be delivered from auxiliary winding Na. During this process, VDD must not drop below UVLO turn-off voltage (typical 9V). The selection of Rst and Cdd should be a trade off between the power loss and startup time.

# **♦** Low Operating Current

The operating current in SF1533 is as small as 2mA (typical). The small operating current results in higher efficiency and reduces the VDD hold-up capacitance requirement.

#### **♦** Soft Start

SF1533 features an internal 4ms (typical) soft start that slowly increases the threshold of cycle-by-cycle current limiting comparator during startup sequence. It helps to prevent transformer saturation and reduce the stress on the secondary diode during startup. Every restart attempt is followed by a soft start activation.

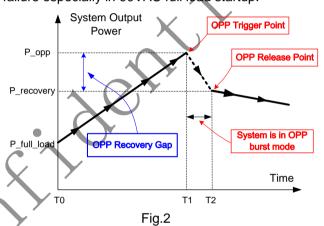

### ◆ "Zero OCP/OPP Recovery Gap" Control

The definition of OCP or OPP recovery gap of a power adaptor is illustrated in Fig.2. assuming an adaptor is at full loading mode. If the loading keeps increasing, then the system will output maximum power P\_opp, which will trigger OPP protection at the same time. After the OPP protection is triggered, usually the system will enter into the auto-recovery mode, in burst manner. If the system power demand decreases P recovery, then system will enter into normal mode again, as shown in Fig.2. The difference between P opp and P recovery is defined as "OPP Recovery Gap", which can cause system startup failure especially in 90VAC full load startup.

SF1533 can achieve "Zero OCP/OPP Recovery Gap" in the whole universal AC input range using SiFirst's proprietary control algorithm.

#### **♦** Oscillator with Frequency Shuffling

PWM switching frequency in SF1533 is fixed to 50KHz and is trimmed to tight range. To improve system EMI performance, SF1533 operates the system with  $\pm 4\%$  frequency shuffling around setting frequency.

### Synchronous Slope Compensation

InSF1533, the synchronous slope compensation circuit is integrated by adding voltage ramp onto the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

## **♦** Leading Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs across the sensing resistor. The spike is caused by primary side capacitance and secondary side rectifier reverse recovery. To avoid premature termination of the switching pulse, an internal leading edge blanking circuit is built in. During this blanking period (250ns, typical), the PWM comparator is disabled and cannot switch off

the gate driver. Thus, external RC filter with a small time constant is enough for current sensing.

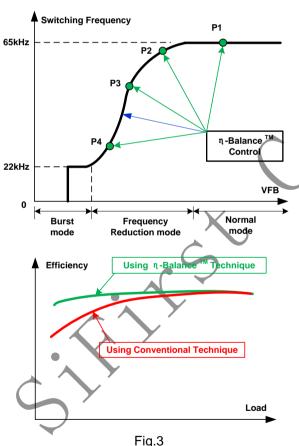

# ♦ Proprietary η -Balance<sup>™</sup> Control

The efficiency requirement of power conversion is becoming tighter than before. These new energy standards focus on the average efficiency of the whole loading range. Therefore, the light load efficiency is becoming more and more important.

In SF1533, a proprietary  $\eta$  -Balance<sup>TM</sup> control is integrated to boost the light load efficiency. As shown in Fig.3, when the loading becomes light, the IC will reduce the PWM switching frequency according to an optimized frequency reduction curve. The specific frequency reduction curve and the power at a frequency are determined by the output of  $\eta$  -Balance<sup>TM</sup> control. For example, P1 is at full load, P2 is at 75% full load, P3 and P4 are 50% and 25% full load respectively. The  $\eta$  -Balance<sup>TM</sup> control can provide higher average efficiency than conventional frequency reduction technique, as illustrated in Fig.3

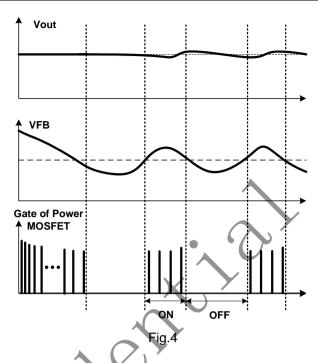

### Burst Mode Control

When the loading is very small, the system enters into burst mode. When VFB drops below Vskip, SF1533 will stop switching and output voltage starts to drop, which causes the VFB to rise. Once VFB rises above Vskip, switching resumes. Burst mode control alternately enables and disables switching, thereby reducing switching loss in standby mode.

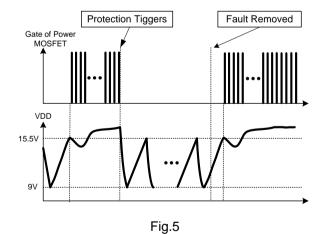

# **♦** Auto Recovery Mode Protection

As shown in Fig.5, once a fault condition is detected, switching will stop. This will cause VDD to fall because no power is delivered form the auxiliary winding. When VDD falls to UVLO(off) (typical 9V), the protection is reset and the operating current reduces to the startup current, which causes VDD to rise, as shown in Fig.4. However, if the fault still exists, the system will experience the above mentioned process. If the fault has gone, the system resumes normal operation. In this manner, the auto restart can alternatively enable and disable the switching until the fault condition is disappeared.

#### ◆ VDD OVP(Over Voltage Protection)

VDD OVP (Over Voltage Protection) is implemented in SF1533 and it is a protection of auto-recovery mode.

#### Over Load Protection (OLP) / Over Current Protection (OCP) / Over Power **Protection** (OPP) 1 Open **Protection (OLP)**

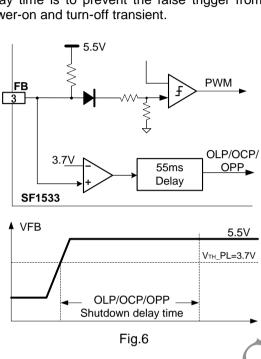

When OLP/OCP/OPP/Open Loop occurs, a fault is detected. If this fault is present for more than 55ms (typical), the protection will be triggered, the IC will experience an auto-recovery mode protection as mentioned above, as shown in Fig.6. The 55ms delay time is to prevent the false trigger from the power-on and turn-off transient.

## **♦** Pins Floating Protection

In SF1533, if pin floating situation or RT pin shortto-GND occurs, the protection is triggered immediately and the system will experience the process of auto-recovery mode protection.

#### **♦** Soft Gate Drive

The driving stage of SF1533 is a soft totem-pole gate driver to minimize EMI. Cross conduction has been avoided to minimize heat dissipation, increase efficiency, and enhance reliability.

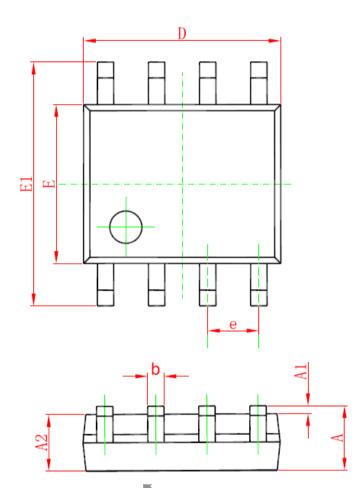

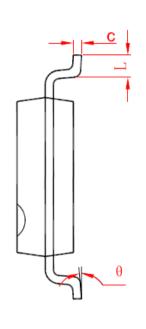

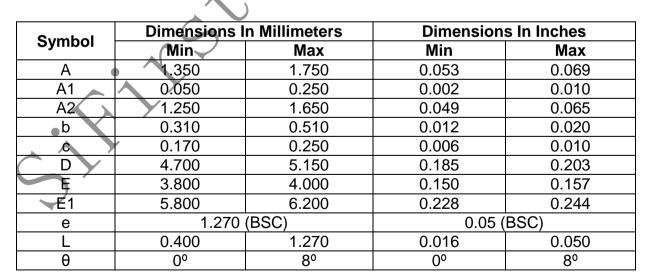

# **PACKAGE MECHANICAL DATA**

## SOP8 PACKAGE OUTLINE DIMENSIONS

#### IMPORTANT NOTICE

SiFirst Technology Nanhai, Ltd (SiFirst) reserves the right to make corrections, modifications, enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

SiFirst warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with SiFirst's standard warranty. Testing and other quality control techniques are used to the extent SiFirst deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

SiFirst assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using SiFirst's components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

Reproduction of SiFirst's information in SiFirst's data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. SiFirst is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of SiFirst's products or services with statements different from or beyond the parameters stated by SiFirst for that product or service voids all express and any implied warranties for the associated SiFirst's product or service and is an unfair and deceptive business practice. SiFirst is not responsible or liable for any such statements.

SiFirst's products are neither designed nor intended for use in military applications. SiFirst will not be held liable for any damages or claims resulting from the use of its products in military applications.

SiFirst's products are not designed to be used as components in devices intended to support or sustain human life. SiFirst will not be held liable for any damages or claims resulting from the use of its products in medical applications.