# **REGULATING PULSE WIDTH MODULATOR**

### DESCRIPTION

The SG1526 is a high-performance monolithic pulse width modulator circuit designed for fixed-frequency switching regulators and other power control applications. Included in an 18-pin dual-in-line package are a temperature compensated voltage reference, sawtooth oscillator, error amplifier, pulse width modulator, pulse metering and steering logic, and two low impedance power drivers. Also included are protective features such as soft-start and undervoltage lockout, digital current limiting, double pulse inhibit, a data latch for single pulse metering, adjustable deadtime, and provision for symmetry correction inputs. For ease of interface, all digital control ports are TTL and B-series CMOS compatible. Active LOW logic design allows wired-OR connections for maximum flexibility. This versatile device can be used to implement single-ended or push-pull switching regulators of either polarity, both transformerless and transformer coupled. The SG1526 is characterized for operation over the full military ambient junction temperature range of -55°C to +150°C. The SG2526 is characterized for operation from -25°C to +150°C, and the SG3526 is characterized for operation from 0°C to +125°C.

### **FEATURES**

- 8V to 35V Operation

- 5V Reference Trimmed to ±1%

- 1Hz to 350kHz Oscillator Range

- Dual 100mA Source/Sink Outputs

- Digital Current Limiting

- Double Pulse Suppression

- Programmable Deadtime

- Undervoltage Lockout

- Single Pulse Metering

- Programmable Soft-start

- Wide Current Limit Common Mode

- Range TTL/CMOS Compatible Logic

- Ports Symmetry Correction Capability

- Guaranteed 6 Unit Synchronization

#### **HIGH RELIABILITY FEATURES**

- Available to MIL-STD-883, ¶ 1.2.1

- Available to DSCC Standard Microcircuit Drawing (SMD)

- Radiation data available

- MSC-AMS level "S" processing available

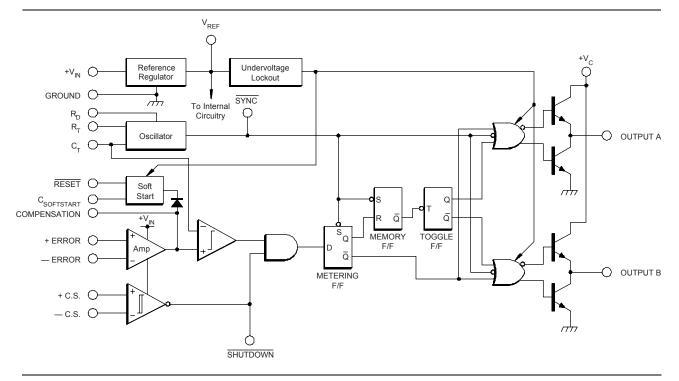

## BLOCK DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage (V <sub>IN</sub> )           | 40V                     |

|--------------------------------------------|-------------------------|

| Collector Supply Voltage (V <sub>c</sub> ) | 40V                     |

| Logic Inputs                               |                         |

| Analog Inputs                              | 0.3V to V <sub>IN</sub> |

| Source/Sink Load Current (each output)     | 200mÄ                   |

| Reference Load Current                     | 50mA                    |

|                                            |                         |

Note 1. Exceeding these ratings could cause damage to the device.

#### **THERMAL DATA**

#### J Package:

| e i denage.                                           |        |

|-------------------------------------------------------|--------|

| Thermal Resistance-Junction to Case, θ <sub>ιc</sub>  | 25°C/W |

| Thermal Resistance-Junction to Ambient, $\theta_{IA}$ |        |

| N Package:                                            |        |

| Thermal Resistance-Junction to Case, $\theta_{IC}$    | 30°C/W |

| Thermal Resistance-Junction to Ambient, $\theta_{IA}$ | 60°C/W |

| DW Package:                                           |        |

| Thermal Resistance-Junction to Case, θ <sub>ιc</sub>  | 35°C/W |

| Thermal Resistance-Junction to Ambient, $\theta_{IA}$ |        |

| L Package:                                            |        |

| Thermal Resistance-Junction to Case, $\theta_{JC}$    | 35°C/W |

| Thermal Resistance-Junction to Ambient, $\theta_{JA}$ |        |

|                                                       |        |

### **RECOMMENDED OPERATING CONDITIONS** (Note 2)

| Input Voltage                          | 8V to 35V                  |

|----------------------------------------|----------------------------|

| Collector Supply Voltage               | 4.5V to 35V                |

| Sink/Source Load Current (each output) | 0 to 100mA                 |

| Reference Load Current                 | 0 to 20mA                  |

| Oscillator Frequency Range             | 1Hz to 350kHz              |

| Oscillator Timing Resistor             | $2k\Omega$ to $150k\Omega$ |

Note 2. Range over which the device is functional.

#### **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for SG1526 with -55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, SG2526 with  $-25^{\circ}C \le T_{A} \le 85^{\circ}C$ , SG3526 with 0°C  $\le T_{A} \le 70^{\circ}C$ , and  $V_{IN} = 15V$ . Low duty cycle pulse testing techniques are used which maintains junction and case temperatures equal to the ambient temperature.)

| Parameter                           | Test Conditions                              |      | SG1526/2526 |      |      | SG3526 |      |       |

|-------------------------------------|----------------------------------------------|------|-------------|------|------|--------|------|-------|

| Falanleter                          |                                              |      | Тур.        | Max. | Min. | Тур.   | Max. | Units |

| Reference Section (Note 3)          |                                              |      |             |      | _    |        |      |       |

| Output Voltage                      | T_ = 25°C                                    | 4.95 | 5.00        | 5.05 | 4.90 | 5.00   | 5.10 | V     |

| Line Regulation                     | V <sub>IN</sub> = 8 to 35V                   |      | 10          | 30   |      | 10     | 30   | mV    |

| Load Regulation                     | I, = 0 to 20mA                               |      | 10          | 30   |      | 10     | 50   | mV    |

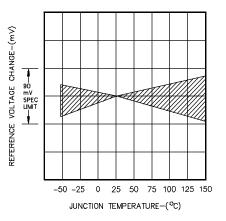

| Temperature Stability (Note 9)      | Över Operating T                             |      | 15          | 50   |      | 15     | 50   | mV    |

| Total Output Voltage Range (Note 9) |                                              |      | 5.00        | 5.10 | 4.85 | 5.00   | 5.15 | V     |

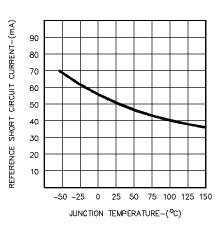

| Short Circuit Current               | V <sub>REF</sub> = 0V                        |      | 50          | 125  |      | 50     | 125  | mA    |

| Undervoltage Lockout Section        |                                              |      |             |      |      |        |      |       |

| RESET Output Voltage                | V <sub>REF</sub> = 3.8V                      |      | 0.2         | 0.4  |      | 0.2    | 0.4  | V     |

| RESET Output Voltage                | $V_{\text{REF}}^{\text{NEF}} = 4.8 \text{V}$ | 2.4  | 4.8         |      | 2.4  | 4.8    |      | V     |

| Logic Sink Current                                                       |

|--------------------------------------------------------------------------|

| Operating Junction Temperature                                           |

| Hermetic (J, L Packages) 150°C                                           |

| Plastic (N, DW Packages) 150°C                                           |

| Storage Temperature Range65°C to 150°C                                   |

| Lead Temperature (Soldering, 10 Seconds) 300°C                           |

| RoHS Peak Package Solder Reflow Temp. (40 sec. max. exp.) 260°C (+0, -5) |

|                                                                          |

Note A. Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ . Note B. The above numbers for  $\theta_{JC}$  are maximums for the limiting thermal resistance of the package in a standard mounting configuration. The  $\theta_{JA}$  numbers are meant to be guidelines for the thermal performance of the device/pcboard system. All of the above assume no ambient airflow.

| Oscillator Timing Capacitor          | 1nF to 20μF   |

|--------------------------------------|---------------|

| Available Deadtime Range at 40kHz    | 3% to 50%     |

| Operating Ambient Temperature Range: |               |

| SG1526                               | 55°C to 125°C |

| SG2526                               | 25°C to 85°C  |

| SG3526                               | 0°C to 70°C   |

### ELECTRICAL CHARACTERISTICS (continued)

| Parameter                          | Test Conditions                                                            |      | SG1526/2526 |       |      | G352      |       | Units    |

|------------------------------------|----------------------------------------------------------------------------|------|-------------|-------|------|-----------|-------|----------|

| Falameter                          | Test conditions                                                            | Min. | i. Typ. M   |       | Min. | Typ. Max. |       |          |

| Oscillator Section (Note 4)        |                                                                            |      |             |       |      |           |       |          |

| Initial Accuracy                   | $T_{J} = 25^{\circ}C$ $\pm 3 \pm 8$                                        |      |             |       |      | ±3        | ±8    | %        |

| Voltage Stability                  | V <sub>IN</sub> = 8 to 35V 0.5 1.0                                         |      |             | 0.5   | 1.0  | %         |       |          |

| Temperature Stability (Note 9)     | Over Operating T                                                           |      | 7           | 10    |      | 5         | 10    | %        |

| Minimum Frequency (Note 9)         | $R_{T} = 150 k\Omega, C_{T} = 20 \mu F$                                    |      |             | 1.0   |      |           | 1.0   | Hz       |

| Maximum Frequency                  | $R_T = 2k\Omega, C_T = 1.0nF$                                              | 350  |             |       | 350  |           |       | kHz      |

| Sawtooth Peak Voltage              | V <sub>IN</sub> = 35V                                                      |      | 3.0         | 3.5   |      | 3.0       | 3.5   | V        |

| Sawtooth Valley Voltage            | $V_{\rm IN} = 8V$                                                          | 0.5  | 1.0         |       | 0.5  | 1.0       |       | V        |

| Error Amplifier Section (Note 5)   |                                                                            | I    |             |       |      |           |       |          |

| Input Offset Voltage               | $R_{s} \leq 2k\Omega$                                                      |      | 2           | 5     |      | 2         | 10    | mV       |

| Input Bias Current                 | 5                                                                          |      | -350        | -1000 |      | -350      | -2000 | nA       |

| Input Offset Current               |                                                                            |      | 35          | 100   |      | 35        | 200   | nA       |

| DC Open Loop Gain                  | $R_1 \ge 10M\Omega, T_1 = 25^{\circ}C$                                     | 64   | 72          |       | 60   | 72        |       | dB       |

| High Output Voltage                | $V_{PIN1}^{L} - V_{PIN2} \ge 150 \text{mV}, I_{SOURCE} = 100 \mu \text{A}$ | 3.6  | 4.2         |       | 3.6  | 4.2       |       | V        |

| Low Output Voltage                 | $V_{PIN2} - V_{PIN1} \ge 150 \text{mV}, I_{SINK} = 100 \mu \text{A}$       |      | 0.2         | 0.4   |      | 0.2       | 0.4   | V        |

| Common Mode Rejection              | $R_{s} \leq 2k\Omega$                                                      | 70   | 94          |       | 70   | 94        |       | dB       |

| Supply Voltage Rejection           | $V_{\rm IN} = 8V$ to 35V                                                   | 66   | 80          |       | 66   | 80        |       | dB       |

| PWM Comparator Section (Note 4)    |                                                                            |      |             |       |      |           |       |          |

| Minimum Duty Cycle                 | V <sub>COMPENSATION</sub> = 0.4V                                           |      |             | 0     |      |           | 0     | %        |

| Maximum Duty Cycle                 | V <sub>COMPENSATION</sub> = 3.6V                                           | 45   | 49          |       | 45   | 49        |       | %        |

| Digital Ports (SYNC, SHUTDOWN      |                                                                            |      |             |       | 1    |           |       |          |

| HIGH Output Voltage                | I <sub>SOURCE</sub> = 40μA                                                 | 2.4  | 4           |       | 2.4  | 4         |       | V        |

| LOW Output Voltage                 | $I_{SINK} = 3.6 \text{mA}$                                                 |      | 0.2         | 0.4   |      | 0.2       | 0.4   | V        |

| HIGH Input Current                 | $V_{\rm H} = 2.4 V$                                                        |      | -125        | -300  |      | -125      | -300  | μA       |

| LOW Input Current                  | $V_{\parallel}^{\parallel} = 0.4V$                                         |      | -225        | -500  |      | -225      | -500  | μA       |

| Current Limit Comparator Section   | 10                                                                         |      |             |       | 1    | 1         |       |          |

| Sense Voltage                      | $R_{s} \le 50\Omega, T_{1} = 25^{\circ}C$                                  | 90   | 100         | 110   | 80   | 100       | 120   | mV       |

| Input Bias Current                 | ···s = •••==, ··j =•••                                                     |      | -3          | -10   |      | -3        | -10   | μA       |

| Soft-Start Section                 |                                                                            |      | _           | _     | 1    | _         |       | 1 1-     |

| Error Clamp Voltage                | RESET = 0.4V                                                               |      | 0.1         | 0.4   |      | 0.1       | 0.4   | V        |

| C <sub>s</sub> Charging Current    | $\overline{\text{RESET}} = 2.4 \text{V}$                                   | 50   | 100         | 200   | 50   | 100       | 200   | μA       |

| Output Drivers (each output) (Note |                                                                            |      |             |       |      |           |       | port     |

| HIGH Output Voltage                | I <sub>SOURCE</sub> = 20mA                                                 | 12.5 | 13.5        |       | 12.5 | 13.5      |       | V        |

| Thigh Output voltage               | $I_{SOURCE} = 100 \text{mA}$<br>$I_{SOURCE} = 100 \text{mA}$               | 12.5 | 13.5        |       | 12.5 | 13.5      |       | V        |

| LOW Output Voltage                 | $I_{SOURCE} = 100 \text{ mA}$                                              | 12   | 0.2         | 0.3   | 12   | 0.2       | 0.3   | V        |

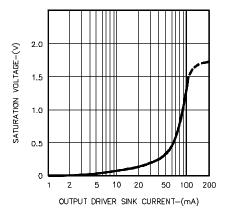

|                                    | $I_{SINK} = 2000A$<br>$I_{SINK} = 100mA$                                   |      | 1.2         | 2     |      | 1.2       | 2     | V        |

| Collector Leakage                  | $V_c = 40V$ 50 150                                                         |      |             | 50    | 150  | μA        |       |          |

| Rise Time                          | $V_{c} = 40V$<br>$C_{c} = 1000 \text{pF}$                                  |      | 0.3         | 0.6   |      | 0.3       | 0.6   | μA<br>μs |

| Fall Time                          | $C_{1} = 1000 \text{pF}$                                                   |      | 0.0         | 0.2   |      | 0.1       | 0.0   | μs       |

|                                    |                                                                            |      | 0.1         | 0.2   |      | 0.1       | 0.2   | μο       |

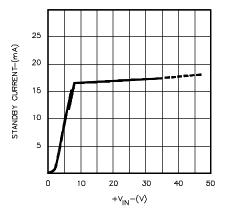

| Power Consumption Section (Note    | shuttown = 0.4V                                                            |      | 10          | 20    |      | 18        | 20    | mA       |

| Standby Current                    | SHUTDOWN = 0.4V                                                            |      | 18          | 30    |      | 18        | 30    | mA       |

Note 3.  $I_{L} = 0mA$ Note 4.  $F_{OSC} = 40kHz (R_{T} = 4.12k\Omega \pm 1\%, C_{T} = .01\mu F \pm 1\%, R_{D} = 0\Omega)$ Note 5.  $V_{CM} = 0$  to 5.2V Note 6.  $V_{CM} = 0$  to 12V

Note 7.  $V_c = 15V$ Note 8.  $V_N = 35V$ Note 9. These parameters, although guaranteed over the recommended operating conditions, are not tested in production.

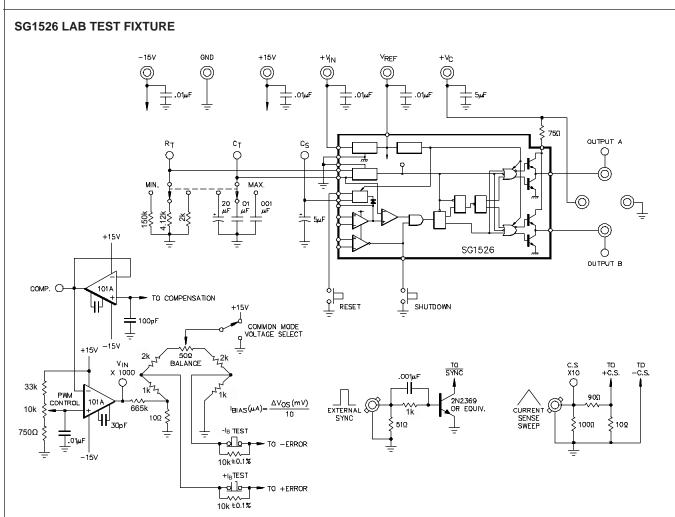

## **CHARACTERISTIC CURVES**

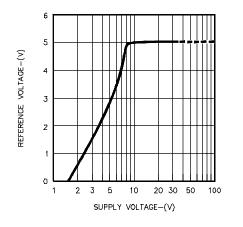

FIGURE 1. REFERENCE VOLTAGE VS. SUPPLY VOLTAGE

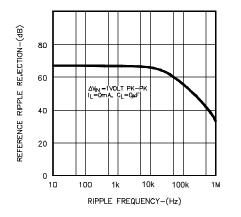

FIGURE 4. REFERENCE RIPPLE REJECTION

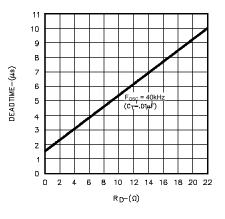

FIGURE 6. OUTPUT DRIVER DEADTIME VS.  $\rm R_{\rm D}$  VALUE

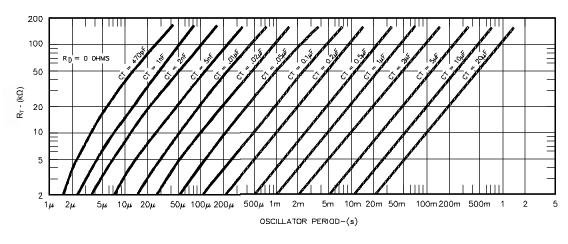

FIGURE 7. OSCILLATOR PERIOD VS.  $\rm R_T$  AND  $\rm C_T$

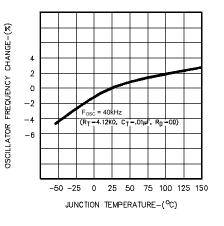

#### CHARACTERISTIC CURVES (continued)

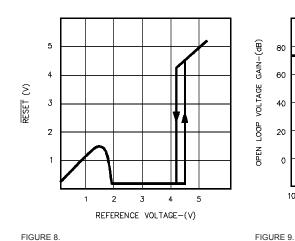

UNDERVOLTAGE LOCKOUT CHARACTERISTIC

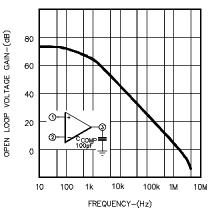

ERROR AMPLIFIER OPEN LOOP GAIN

VS. FREQUENCY

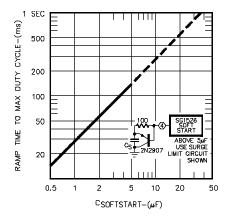

FIGURE 10. SOFTSTART TIME CONSTANT VS. C<sub>S</sub>

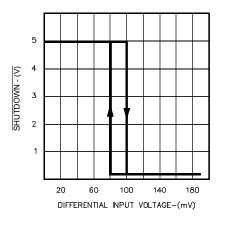

FIGURE 11. CURRENT LIMIT TRANSFER FUNCTION

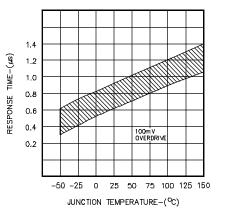

FIGURE 13. SHUTDOWN INPUT TO DRIVER OUTPUT DELAY

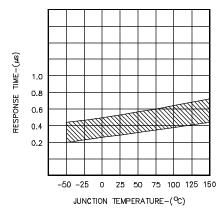

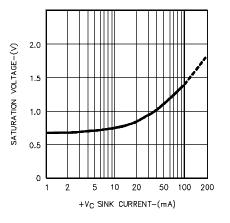

FIGURE 14. OUTPUT DRIVER SATURATION VOLTAGE VS. I<sub>SINK</sub>

FIGURE 15. OUTPUT SUPPLY SATURATION VOLTAGE VS. I<sub>SINK</sub>

FIGURE 16. STANDBY CURRENT VS. SUPPLY VOLTAGE

### **APPLICATION INFORMATION**

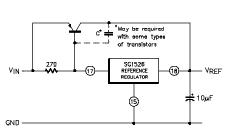

#### **VOLTAGE REFERENCE**

The reference regulator of the SG1526 is based on a temperature compensated Zener diode. The circuitry is fully active at supply voltages above +8 volts, and provides up to 20mA of load current to external circuitry at +5.0 volts. In systems where additional current is required, an external PNP transistor can be used to boost the available current. A rugged low frequency audio-type transistor should be used, and lead lengths between the PWM and transistor should be as short as possible to minimize the risk of oscillations. Even so, some types of transistors may require collector-base capacitance for stability. Up to 1 amp of load current can be obtained with excellent regulation if the device selected maintains high current gain.

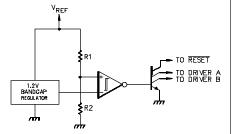

#### UNDERVOLTAGE LOCKOUT

The undervoltage lockout circuit protects the SG1526 and the power devices it controls from inadequate supply voltage. If  $+V_{\mathbb{N}}$  is too low, the circuit disables the output drivers and holds the RESET pin LOW. This prevents spurious output pulses while the control circuitry is stabilizing, and holds the soft-start timing capacitor in a discharged state.

The circuit consists of a +1.2 volt bandgap reference and comparator circuit which is active when the reference voltage has risen to  $3V_{BE}$  or 1.8 volts at 25°C. When the reference voltage rises to approximately +4.4 volts, the circuit enables the output drivers and releases the RESET pin, allowing a normal soft-start. The comparator has 200mV of hysteresis to minimize oscillation at the trip point. When  $+V_{IN}$  to the PWM is removed and the reference drops to +4.2 volts, the undervoltage circuit pulls RESET LOW again. The soft-start capacitor is immediately discharged, and the PWM is ready for another soft-start cycle.

The SG1526 can operate from a +5 volt supply by connecting the V<sub>REF</sub> pin to the  $+V_{N}$  pin and maintaining the supply between +4.8 and +5.2 volts.

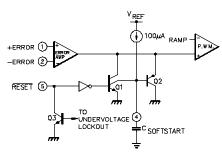

#### SOFT-START CIRCUIT

The soft-start circuit protects the power transistors and rectifier diodes from high current surges during power supply turn-on. When supply voltage is first applied to the SG1526, the undervoltage lockout circuit holds RESET LOW with Q3. Q1 is turned on, which holds the soft-start capacitor voltage at zero. The second collector of Q1 clamps the output error amplifier to ground, guaranteeing zero duty cycle at the driver outputs. When the supply voltage reaches normal operating range, RESET will go HIGH. Q1 turns off, allowing the internal 100µA current source to charge  $C_{\rm s}$ . Q2 clamps the error amplifier output to  $1V_{\rm BE}$  above the voltage on  $C_{\rm s}$ . As the soft-start voltage ramps up to +5 volts, the duty cycle of the PWM linearly increases to whatever value the voltage regulation loop requires for an error null. Figure 10 gives the timing relationship between  $C_{\rm s}$  and ramp time to 100% duty cycle.

SIMPLIFIED UNDERVOLTAGE LOCKOUT

FIGURE 18

FIGURE 19

SOFT-START CIRCUIT SCHEMATIC

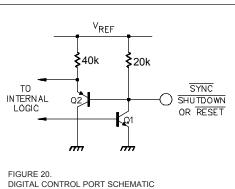

#### **DIGITAL CONTROL PORTS**

The three digital control ports of the SG1526 are bi-directional. Each pin can drive TTL and 5 volt CMOS logic directly, up to a fan-out of 10 low-power Schottky gates. Each pin can also be directly driven by open-collector voltage comparators; fanin is equivalent to 1 low-power Schottky gate. Each port is normally HIGH; the pin is pulled LOW to activate the particular function. Driving SYNC LOW initiates a discharge cycle in the oscillator. Pulling SHUTDOWN LOW immediately inhibits all PWM output pulses. Holding RESET LOW discharges the soft-start capacitor. The logic threshold is +1.1 volts at 25°C. Noise immunity can be gained at the expense of fan-out with an external 2k pullup resistor to +5 volts.

#### **APPLICATION INFORMATION** (continued)

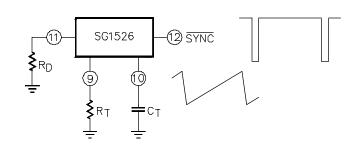

#### OSCILLATOR

FIGURE 21 - OSCILLATOR CONNECTIONS AND WAVEFORMS

The oscillator is programmed for frequency and deadtime with three components:  $R_{\tau}$ ,  $C_{\tau}$ , and  $R_{D}$ . Two waveforms are generated: a sawtooth waveform at pin 10 for pulse width modulation, and a logic clock at pin 12. The following procedure is recommended for choosing timing values:

- 1. With  $R_{D} = 0\Omega$  (pin 11 shorted to ground) select values for  $R_{T}$  and  $C_{T}$  from Figure 7 to give the desired oscillator period. Remember that the frequency at each driver output is half the oscillator frequency, and the frequency at the +V<sub>c</sub> terminal is the same as the oscillator frequency.

- 2. If more dead time is required, select a larger value of R<sub>D</sub> using Figure 6 as a guide. At 40kHz dead time increases by 400nSec/ohm.

- Increasing the dead time will cause the oscillator frequency to decrease slightly. Go back and decrease the value of R<sub>T</sub> slightly to bring the frequency back to the nominal design value.

The SG1526 can be synchronized to an external logic clock by programming the oscillator to free-run at a frequency 10% slower than the sync frequency. A periodic LOW logic pulse approximately  $0.5\mu$ Sec wide at the SYNC pin will then lock the oscillator to the external frequency.

Multiple devices can be synchronized together by programming one master unit for the desired frequency, and then sharing its sawtooth and clock waveforms with the slave units. All  $C_{\tau}$  terminals are connected to the  $C_{\tau}$  pin of the master, and all SYNC terminals are likewise connected to the SYNC pin of the master. Slave  $R_{\tau}$  terminals should not be left open nor should they be tied to the +5V reference; at least 50k should be connected to each pin. Slave  $R_{\tau}$  terminals may be either left open or grounded.

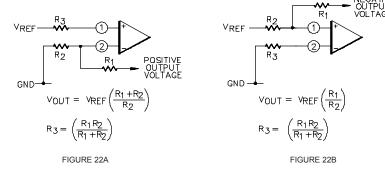

#### ERROR AMPLIFIER

ERROR AMPLIFIER CONNECTIONS

The error amplifier is a transconductance design, with an output impedance of 2 megohms and an effective output capacitance of 100 pF. Since all voltage gain takes place at the output pin, the open-loop gain can be shaped with shunt reactance to ground. For unity gain stability the amplifier requires an additional external 100 pF to ground, resulting in an open-loop pole at 400 Hz.

The input connections to the error amplifier are determined by the polarity of the switching supply output voltage. For positive supplies, the common-mode voltage is +5.0 volts and the feedback connections in Figure 22A are used. With negative supplies, the common-mode voltage is ground and the feedback divider is connected between the negative output and the +5.0 volt reference voltage, as shown in Figure 22B.

#### **APPLICATION INFORMATION** (continued)

#### OUTPUT DRIVERS

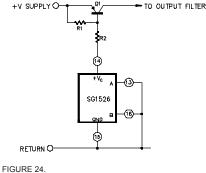

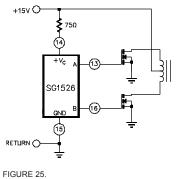

The totem-pole output drivers of the SG1526 are designed to source and sink 100mA continuously and 200mA peak. Loads can be driven either from the output pins 13 and 16, or from the  $+V_c$  pin, as required. Curves for the saturation voltage at these outputs as a function of load current are found in Figures 14 and 15.

Since the bottom transistor of the totem-pole is allowed to saturate, there is a momentary conduction path from the  $+V_c$  terminal to ground during switching. To limit the resulting current spikes a small resistor in series with pin 14 is always recommended. The resistor value is determined by the driver supply voltage, and should be chosen for 200mA peak currents, as shown in Figure 25.

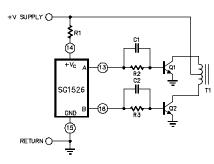

SINGLE-ENDED CONFIGURATION

DRIVING N-CHANNEL POWER MOSFETS

FIGURE 23. PUSH-PULL CONFIGURATION

## CONNECTION DIAGRAMS & ORDERING INFORMATION (See Notes Below)

| Package                                               | Part No.                                      | Ambient<br>Temperature Range                                     | Connection Diagram                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-PIN CERAMIC DIP<br>J - PACKAGE                     | SG1526J-883B<br>SG1526J<br>SG2526J<br>SG3526J | -55°C to 125°C<br>-55°C to 125°C<br>-25°C to 85°C<br>0°C to 70°C | +ERROR $\begin{bmatrix} 1 \\ 18 \end{bmatrix}$ V <sub>REF</sub><br>- ERROR $\begin{bmatrix} 2 \\ 17 \end{bmatrix}$ +V <sub>N</sub><br>COMPENSATION $\begin{bmatrix} 3 \\ 16 \end{bmatrix}$ OUTPUT B<br>C <sub>SOFTSTART</sub> $\begin{bmatrix} 4 \\ 15 \end{bmatrix}$ GROUND<br>RESET $\begin{bmatrix} 5 \\ 14 \end{bmatrix}$ V <sub>COLLECTOR</sub> |

| 18-PIN PLASTIC DIP<br>N - PACKAGE                     | SG2526N<br>SG3526N                            | -25°C to 85°C<br>0°C to 70°C                                     | - CURRENT SENSE 6 13 OUTPUT A<br>+CURRENT SENSE 7 12 SYNC<br>SHUTDOWN 8 11 R <sub>DEADTIME</sub><br>R <sub>T</sub> 9 10 C <sub>T</sub>                                                                                                                                                                                                               |

|                                                       | N Package: RoHS Comp                          | liant / Pb-free Transition DC: 0503                              | N Package: RoHS / Pb-free 100% Matte Tin Lead Finish                                                                                                                                                                                                                                                                                                 |

| 18-PIN WIDE BODY<br>PLASTIC SOIC<br>DW - PACKAGE      | SG2526DW<br>SG3526DW                          | -25°C to 85°C<br>0°C to 70°C                                     | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                               |

|                                                       | DW Package: RoHS Con                          | npliant / Pb-free Transition DC: 0516                            | DW Package: RoHS / Pb-free 100% Matte Tin Lead Finish                                                                                                                                                                                                                                                                                                |

| 20-PIN CERAMIC<br>LEADLESS CHIP CARRIER<br>L- PACKAGE | SG1526L-883B<br>SG1526L                       | -55°C to 125°C<br>-55°C to 125°C                                 | 1. N.C. 3 2 1 20 19 11. C <sub>T</sub> 2. +ERROR 4   4. COMP 5   5. C <sub>SOFTSTART</sub> 6   6. RESET 6   7C.S. 7   8. +C.S. 8   9. SHUTDOWN 9 10 11 12 13   10.R <sub>T</sub> 9 10 11 12 13                                                                                                                                                       |

Note 1. Contact factory for JAN and DESC product availability.

Note 2. All parts are viewed from the top.

Note 3. Hermetic Packages J, L use Pb37/Sn63 hot solder lead finish, contact factory for availability of RoHS versions.

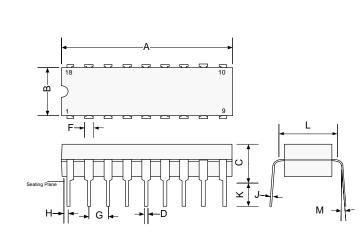

### PACKAGE OUTLINE DIMENSIONS

Controlling dimensions are in inches, metric equivalents are shown for general information.

| DIM | MILLIM | IETERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIN | MIN    | MAX    | MIN   | MAX   |

| А   | -      | 24.38  | -     | 0.960 |

| В   | 5.59   | 7.11   | 0.220 | 0.280 |

| С   | -      | 5.08   | -     | 0.200 |

| D   | 0.38   | 0.51   | 0.015 | 0.020 |

| F   | 1.02   | 1.77   | 0.040 | 0.070 |

| G   | 2.54   | BSC    | 0.100 | BSC   |

| H   | -      | 2.03   | -     | 0.080 |

| J   | 0.20   | 0.38   | 0.008 | 0.015 |

| K   | 3.18   | 5.08   | 0.125 | 0.200 |

| L   | 7.37   | 7.87   | 0.290 | 0.310 |

| М   | -      | 15°    | -     | 15°   |

**Note:** Dimensions do not include protrusions; these shall not exceed 0.155mm (0.006") on any side. Lead dimension shall not include solder coverage.

#### Figure 26 · J 18-Pin CERDIP Package Dimensions

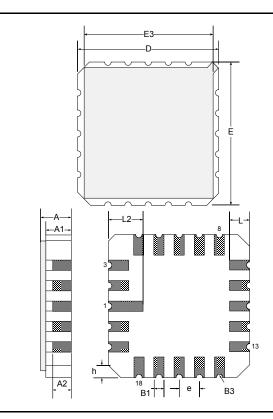

| Dim | MILLIME | ETERS | INCHES    |       |  |

|-----|---------|-------|-----------|-------|--|

| Dim | MIN     | MAX   | MIN       | MAX   |  |

| D/E | 8.64    | 9.14  | 0.340     | 0.360 |  |

| E3  | -       | 8.128 | -         | 0.320 |  |

| е   | 1.270   | BSC   | 0.050     | ) BSC |  |

| B1  | 0.635   | TYP   | 0.025 TYP |       |  |

| L   | 1.02    | 1.52  | 0.040     | 0.060 |  |

| Α   | 1.626   | 2.286 | 0.064     | 0.090 |  |

| h   | 1.016   | TYP   | 0.040 TYP |       |  |

| A1  | 1.372   | 1.68  | 0.054     | 0.066 |  |

| A2  | -       | 1.168 | -         | 0.046 |  |

| L2  | 1.91    | 2.41  | 0.075     | 0.95  |  |

| B3  | 0.20    | 3R    | 0.008R    |       |  |

**Note:** All exposed metalized area shall be gold plated 60 μ-inch minimum thickness over nickel plated unless otherwise specified in purchase order.

Figure 27 · L 20-Pin Ceramic LCC Package Dimensions

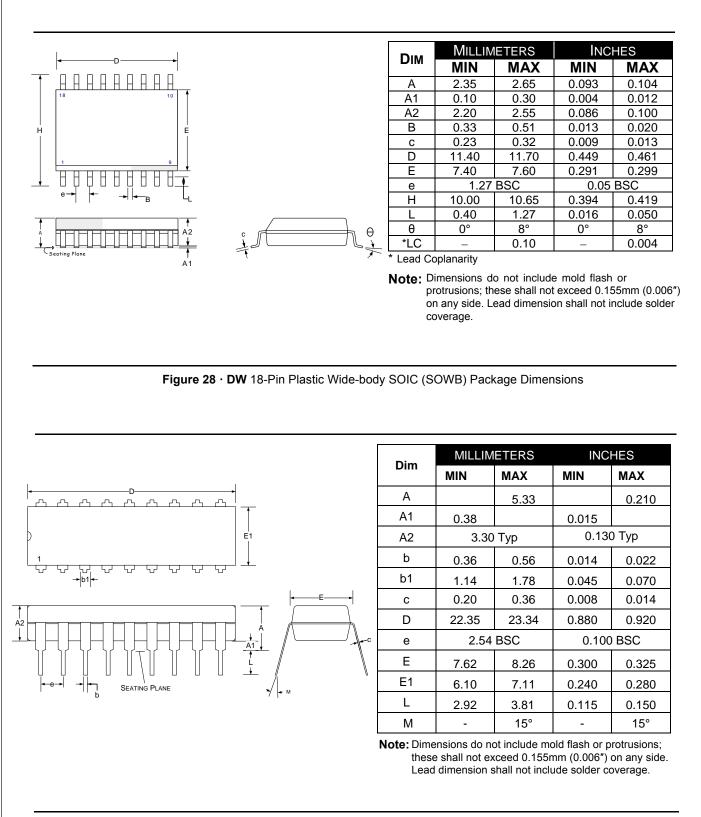

#### PACKAGE OUTLINE DIMENSIONS (continued)

Figure 29 · N 18-Pin Plastic Dual Inline Package Dimensions

#### Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.