# SGM2536SGM1CROSGM1CROSupporting Bidirectional Current Conduction

# **GENERAL DESCRIPTION**

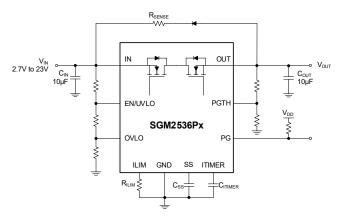

The SGM2536 family is a compact electronic fuse (eFuse) with a full suite of protection functions. With precision current limit, the device can provide excellent accuracy and be well applied to many system protection applications. The output current limit threshold and the transient over-current blanking timer can be adjusted by the user. Due to the back-to-back FETs packaged inside the chip, the SGM2536 allows bidirectional current to flow through the channel when it is turned on, but prohibits bidirectional current flow when it is turned off, which is very suitable for USB OTG. The V<sub>OUT</sub> rise time can be programmed by setting an additional capacitor to the SS pin, which can minimize inrush current. Programmable over-voltage protection is used to turn off the device if the IN raises over a threshold value and the downstream circuitry is not damaged by unintended power supply.

The SGM2536 is available in a Green TQFN-2×2-10L package.

# **APPLICATIONS**

Tablet PC USB OTG POS Device Smartphone Digital Camera

#### Wireless Charger

# FEATURES

- Input Voltage: 2.7V to 23V, Surge up to 28V

- Back-to-Back FETs Structure

- Low On-Resistance: 23.7mΩ (TYP)

- On-State: Bidirectional Current Flow

- Off-State: Reverse Current Blocking

- Programmable Output Ramp Time

- Programmable Current Limit: 0.5A to 6A (±10% Accuracy for I<sub>ILIM</sub> > 1A)

- Load Current Monitor

- Programmable Transient Blanking Timer (ITIMER Pin) to Allow Peak Current up to 2 × I<sub>ILIM</sub>

- UL Recognized Component (File No. E532373\*)

- Full Set of Protections

- Programmable Over-Voltage Lockout (OVLO)

- Short-Circuit Protection on OUT Pin

- Under-Voltage Lockout

- Thermal Shutdown

- Indication Options

- SGM2536Px: PG and PGTH

- SGM2536Fx: SPGD and nFAULT

- Behavior after Fault

- SGM2536xR: Auto-Retry

- SGM2536xL: Latch-Off

# SIMPLIFIED SCHEMATIC

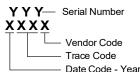

# **PACKAGE/ORDERING INFORMATION**

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|---------------------|--------------------|---------------------|

| SGM2536PR | TQFN-2×2-10L           | -40°C to +125°C                   | SGM2536PRXTSP10G/TR | 0EB<br>XXXX        | Tape and Reel, 3000 |

| SGM2536PL | TQFN-2×2-10L           | -40°C to +125°C                   | SGM2536PLXTSP10G/TR | 0EC<br>XXXX        | Tape and Reel, 3000 |

| SGM2536FR | TQFN-2×2-10L           | -40°C to +125°C                   | SGM2536FRXTSP10G/TR | 0ED<br>XXXX        | Tape and Reel, 3000 |

| SGM2536FL | TQFN-2×2-10L           | -40°C to +125°C                   | SGM2536FLXTSP10G/TR | 043<br>XXXX        | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Input Voltage Range, V <sub>IN</sub>                                |                          |

|---------------------------------------------------------------------|--------------------------|

| T <sub>J</sub> = +25°C MIN (28V)                                    | , V <sub>IN</sub> + 22V) |

| Output Voltage Pulse (< 1µs), V <sub>OUT_PLS</sub><br>Voltage Range | > -0.8V                  |

| Ven/uvlo                                                            | 2)/ to 6 5)/             |

|                                                                     |                          |

| -0                                                                  |                          |

| V <sub>PG</sub> , V <sub>PGTH</sub> (SGM2536Px)0                    |                          |

| V <sub>SPGD</sub> , V <sub>nFAULT</sub> (SGM2536Fx)0                | .3V to 6.5V              |

| V <sub>SS</sub> Intern                                              | ally Limited             |

| V <sub>ITIMER</sub> Intern                                          |                          |

| V <sub>ILIM</sub> Intern                                            |                          |

| Maximum Continuous Switch Current, I <sub>MAX</sub>                 |                          |

| Intern                                                              |                          |

|                                                                     | any Linneu               |

| Package Thermal Resistance                                          |                          |

| TQFN-2×2-10L, θ <sub>JA</sub>                                       |                          |

| TQFN-2×2-10L, θ <sub>JB</sub>                                       |                          |

| TQFN-2×2-10L, θ <sub>JC</sub>                                       | 46.6°C/W                 |

| Package Thermal Characterization Parameter                          |                          |

| TQFN-2×2-10L, ψ <sub>JT</sub>                                       | 1.1°C/W                  |

| Junction Temperature                                                |                          |

| Storage Temperature Range65°C                                       |                          |

| Lead Temperature (Soldering, 10s)                                   |                          |

|                                                                     | +200 C                   |

| ESD Susceptibility                                                  |                          |

| HBM (NC Pin 7)                                                      |                          |

| CDM                                                                 | 1000V                    |

| MM                                                                  | 400V                     |

|                                                                     |                          |

#### **RECOMMENDED OPERATING CONDITIONS**

| Input Voltage Range, VIN   | 2.7V to 23V                      |

|----------------------------|----------------------------------|

| Output Voltage Range, VOUT | MIN (23V, V <sub>IN</sub> + 20V) |

| Voltage Range              |                                  |

| VEN/UVLO                   | 5V <sup>(1)</sup>                |

| V <sub>OVLO</sub>          |                                  |

NOTE: 1. If the supply voltage is less than 5V, EN/UVLO pin can be pulled up to the IN directly. If the supply voltage is larger than 5V, a 350k $\Omega$  (MIN) pull-up resistor is recommended for the EN/UVLO pin.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions.

Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

# **PIN CONFIGURATIONS**

# **PIN DESCRIPTION**

| PIN | NAME    | TYPE                                           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----|---------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | EN/UVLO | Analog Input                                   | Enable and Under-Voltage Lockout Input. Asserting EN/UVLO pin high enables the device. As a UVLO pin, the UVLO threshold is programmed by an external resistor divider. This pin cannot be left floating.                                                                                                                                                                                               |  |

| 2   | OVLO    | Analog Input                                   | Over-Voltage Lockout Pin. The over-voltage lockout threshold is programmed by the resistor divider from the power supply to the OVLO terminal to GND. The device is enabled when this pin is tied to low level. This pin cannot be left floating.                                                                                                                                                       |  |

| 3   | PG      | Digital Output                                 | Power Good Indication (SGM2536Px). This is an open-drain pin, when the internal channels of the chip are all turned on and the PGTH signal value is higher than the set value, the pin is set to high level.                                                                                                                                                                                            |  |

|     | SPGD    |                                                | Supply Good Indication (SGM2536Fx). This is an open-drain pin, when the input voltage is within the valid range and the surge has finished, this pin goes high.                                                                                                                                                                                                                                         |  |

|     | PGTH    | Analog Input Power Good Threshold (SGM2536Px). |                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 4   | nFAULT  | Digital Output                                 | Fault Event Indicator (SGM2536Fx). This pin is an open-drain output, and when a fault occurs, it will be low.                                                                                                                                                                                                                                                                                           |  |

| 5   | IN      | Power                                          | Input Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 6   | OUT     | Power                                          | Output of the Device.                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 7   | SS      | Analog Output                                  | Soft-Start Pin. The capacitor between SS and GND pins will set the slew rate according to the application requirements. When this pin is left floating, the device will start up at the fastest rate.                                                                                                                                                                                                   |  |

| 8   | GND     | Ground                                         | GND.                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 9   | ILIM    | Analog Output                                  | Programming Current Limit Pin. A resistor between this pin and GND sets the overload and short-circuit current limit levels. Do not float this pin.                                                                                                                                                                                                                                                     |  |

| 10  | ITIMER  | Analog Output                                  | Place a capacitor between this pin and GND can set the over-current blanking time, at this stage, the output current value can temporarily exceed the internally set current limit value (but not exceed the fast-trip threshold). After this time, the device will take action if it is still in over-current state. Leaving this pin open will provide the fastest response to an over-current event. |  |

# **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN} = 12V, V_{EN/UVLO} = 2V, R_{ILIM} = 549\Omega, V_{OVLO} = 0V, OUT, SS, ITIMER, PGTH/nFAULT, PG/SPGD pins are open, typical values are at T<sub>J</sub> = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                             | SYMBOL                    | CONDITIONS                                                           | MIN   | TYP   | MAX   | UNITS |  |

|-------------------------------------------------------|---------------------------|----------------------------------------------------------------------|-------|-------|-------|-------|--|

| Input Supply (IN)                                     |                           |                                                                      |       |       |       |       |  |

| Linden Maltana Dasta stien Thursdadd                  | $V_{UVP\_R}$              | Rising                                                               | 2.47  | 2.54  | 2.61  |       |  |

| Under-Voltage Protection Threshold                    | $V_{UVP_F}$               | Falling                                                              | 2.24  | 2.31  | 2.37  | V     |  |

| Supply Quiescent Current                              | I <sub>Q_ON</sub>         |                                                                      |       | 132   | 270   | μA    |  |

| Supply Disabled State Current                         | $I_{Q_{OFF}}$             | V <sub>SD_F</sub> < V <sub>EN/UVLO</sub> < V <sub>UVLO_F</sub>       |       | 48    | 100   | μA    |  |

| Supply Shutdown Current                               | I <sub>SD</sub>           | V <sub>EN/UVLO</sub> < V <sub>SD_F</sub>                             |       | 3.2   | 10    | μA    |  |

| On-Resistance (IN - OUT)                              |                           | •                                                                    | •     |       |       |       |  |

|                                                       | _                         | V <sub>IN</sub> = 12V, I <sub>OUT</sub> = 3A                         |       | 23.7  |       |       |  |

| On-Resistance                                         | R <sub>on</sub>           | $2.7V \le V_{IN} \le 23V$ , $I_{OUT} = 3A$                           |       |       | 40    | mΩ    |  |

| Enable/Under-Voltage Lockout (EN/UVLO)                |                           | •                                                                    |       |       |       |       |  |

|                                                       | $V_{\text{UVLO}_{R}}$     | Rising Threshold                                                     | 1.184 | 1.20  | 1.217 |       |  |

| EN/UVLO Threshold                                     | V <sub>UVLO_F</sub>       | Falling Threshold                                                    | 1.076 | 1.09  | 1.108 | V     |  |

| EN/UVLO Falling Threshold for Lowest Shutdown Current | $V_{\text{SD}\_\text{F}}$ |                                                                      | 0.35  | 0.71  |       | V     |  |

| EN/UVLO Leakage Current                               | I <sub>ENLKG</sub>        |                                                                      | -0.13 |       | 0.13  | μA    |  |

| Over-Voltage Lockout (OVLO)                           |                           |                                                                      |       |       |       |       |  |

| OVLO Rising Threshold                                 | $V_{\text{OVLO}_R}$       |                                                                      | 1.184 | 1.20  | 1.217 | V     |  |

| OVLO Falling Threshold                                | V <sub>OVLO_F</sub>       |                                                                      | 1.076 | 1.09  | 1.108 | V     |  |

| OVLO Pin Leakage Current                              | I <sub>ovlkg</sub>        | V <sub>OVLO</sub> = 0.5V                                             | -0.1  |       | 0.1   |       |  |

|                                                       |                           | V <sub>OVLO</sub> = 1V                                               | -0.1  |       | 0.1   | μA    |  |

|                                                       |                           | V <sub>OVLO</sub> = 1.5V                                             | -0.1  |       | 0.1   |       |  |

| Over-Current Protection (OUT)                         |                           | •                                                                    |       |       |       |       |  |

|                                                       |                           | R <sub>ILIM</sub> = 6.65kΩ, T <sub>J</sub> = +25°C                   | 0.475 | 0.516 | 0.557 |       |  |

|                                                       |                           | $R_{ILIM} = 6.65 k\Omega$ , $T_J = -40^{\circ}C$ to +125°C           | 0.467 |       | 0.581 |       |  |

|                                                       |                           | R <sub>ILIM</sub> = 3.32kΩ, T <sub>J</sub> = +25°C                   | 0.969 | 1.014 | 1.061 | -     |  |

|                                                       |                           | $R_{ILIM} = 3.32 k\Omega$ , $T_J = -40^{\circ}C$ to +125°C           | 0.954 |       | 1.095 |       |  |

|                                                       |                           | R <sub>ILIM</sub> = 1.65kΩ, T <sub>J</sub> = +25°C                   | 1.947 | 2.020 | 2.094 |       |  |

| Over-Current Threshold                                | I <sub>ILIM</sub>         | $R_{ILIM} = 1.65k\Omega$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$   | 1.924 |       | 2.131 | A     |  |

|                                                       |                           | R <sub>ILIM</sub> = 750Ω, T <sub>J</sub> = +25°C                     | 4.226 | 4.379 | 4.534 | -     |  |

|                                                       |                           | $R_{ILIM} = 750\Omega, T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ | 4.187 |       | 4.581 |       |  |

|                                                       |                           | R <sub>ILIM</sub> = 549Ω, T <sub>J</sub> = +25°C                     | 5.730 | 5.946 | 6.163 |       |  |

|                                                       |                           | R <sub>ILIM</sub> = 549Ω, T <sub>J</sub> = -40°C to +125°C           | 5.674 |       | 6.231 |       |  |

|                                                       |                           | ILIM pin open                                                        |       | 0.1   |       |       |  |

| Circuit Breaker Threshold                             | I <sub>nFAULT</sub>       | ILIM pin shorted to GND                                              |       | 1.1   | 1.5   | A     |  |

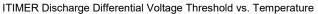

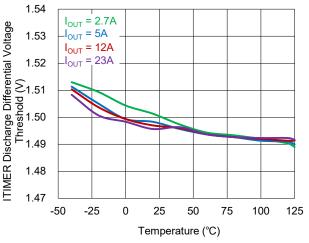

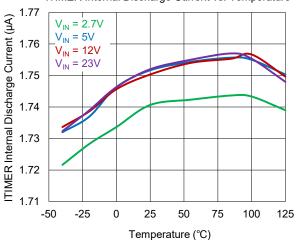

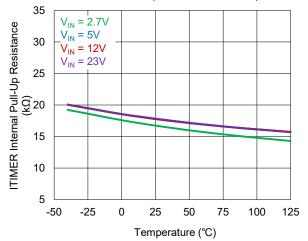

| Over-Current Fault Timer (ITIMER)                     |                           |                                                                      |       |       |       |       |  |

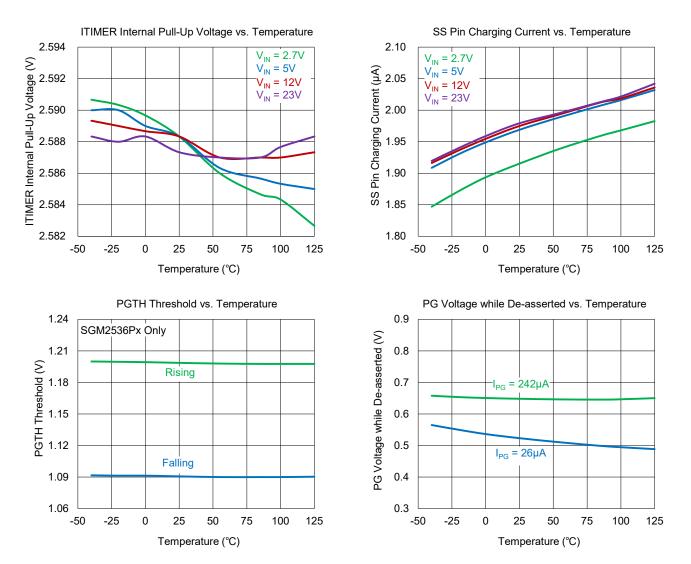

| ITIMER Internal Pull-Up Voltage                       | V <sub>INT</sub>          |                                                                      | 2.40  | 2.59  | 2.80  | V     |  |

| ITIMER Internal Pull-Up Resistance                    | RITIMER                   |                                                                      |       | 17    |       | kΩ    |  |

| ITIMER Internal Discharge Current                     | IITIMER                   | I <sub>OUT</sub> > I <sub>ILIM</sub>                                 | 1.1   | 1.8   | 2.5   | μA    |  |

| i i i i i i i i i i i i i i i i i i i                 |                           |                                                                      |       |       |       |       |  |

# 5.5A, 23.7mΩ Electronic Fuse Supporting Bidirectional Current Conduction

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, V_{IN} = 12V, V_{EN/UVLO} = 2V, R_{ILIM} = 549\Omega, V_{OVLO} = 0V, OUT, SS, ITIMER, PGTH/nFAULT, PG/SPGD pins are open, typical values are at T<sub>J</sub> = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                                                               | SYMBOL                 | CONDITIONS                                                                            | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------|-------|------|-------|-------|

| Output Load Current Monitor (ILIM)                                      |                        |                                                                                       |       |      |       |       |

|                                                                         |                        | I <sub>OUT</sub> = 0.5A, T <sub>J</sub> = +25°C                                       | 165   | 176  | 188   |       |

|                                                                         |                        | $I_{OUT} = 0.5A, T_J = -40^{\circ}C \text{ to } +125^{\circ}C$                        | 154   |      | 195   |       |

|                                                                         |                        | I <sub>OUT</sub> = 0.75A, T <sub>J</sub> = +25°C                                      | 169   | 179  | 187   |       |

|                                                                         |                        | $I_{OUT} = 0.75A, T_J = -40^{\circ}C$ to +125°C                                       | 162   |      | 191   |       |

|                                                                         |                        | I <sub>OUT</sub> = 1A, T <sub>J</sub> = +25°C                                         | 172   | 180  | 187   |       |

| An share have a Querrant Maniferra Querra (I                            |                        | $I_{OUT}$ = 1A, $T_J$ = -40°C to +125°C                                               | 167   |      | 190   |       |

| Analog Load Current Monitor Gain (I <sub>MON</sub> : I <sub>OUT</sub> ) | GIMON                  | I <sub>OUT</sub> = 2A, T <sub>J</sub> = +25°C                                         | 175   | 182  | 187   | µA/A  |

|                                                                         |                        | $I_{OUT}$ = 2A, $T_J$ = -40°C to +125°C                                               | 173   |      | 191   |       |

|                                                                         |                        | I <sub>OUT</sub> = 4A, T <sub>J</sub> = +25°C                                         | 176   | 183  | 189   |       |

|                                                                         |                        | $I_{OUT}$ = 4A, $T_{J}$ = -40°C to +125°C                                             | 175   |      | 192   | -     |

|                                                                         |                        | I <sub>OUT</sub> = 5.5A, T <sub>J</sub> = +25°C                                       | 176   | 183  | 190   |       |

|                                                                         |                        | $I_{OUT} = 5.5A, T_J = -40^{\circ}C$ to +125°C                                        | 175   |      | 192   |       |

| Power Good (PG) Indication: SGM2536Px or Su                             | pply Good              | (SPGD) Indication: SGM2536Fx                                                          |       |      |       |       |

|                                                                         |                        | $V_{IN} < V_{UVP_F}$ , $V_{EN} > V_{UVLO_R}$ , weak pull-up $(I_{PG} = 26\mu A)$      |       | 0.52 | 1     |       |

| PG/SPGD Voltage while De-asserted                                       | V <sub>PGD</sub>       | $V_{IN} < V_{UVP_F}, V_{EN} > V_{UVLO_R}$ , strong pull-up<br>( $I_{PG} = 242\mu A$ ) |       | 0.65 | 1     | V     |

|                                                                         |                        | $V_{IN} > V_{UVP_R}, V_{EN} < V_{SD_F}, I_{PG} = 10mA$                                |       | 0.16 | 0.27  | 7     |

| PG/SPGD Leakage Current, PG/SPGD Asserted                               | I <sub>PGLKG</sub>     |                                                                                       |       | 0.9  | 3     | μA    |

| Power Good Threshold (PGTH): SGM2536Px                                  |                        |                                                                                       |       |      |       |       |

| PGTH Threshold                                                          | $V_{PGTH_R}$           | Rising                                                                                | 1.183 | 1.20 | 1.218 | V     |

| PGTA Threshold                                                          | $V_{PGTH_F}$           | Falling                                                                               | 1.076 | 1.09 | 1.108 | V     |

| PGTH Leakage Current                                                    | IPGTHLKG               |                                                                                       | -0.1  |      | 0.3   | μA    |

| Fault (nFAULT) Indication: SGM2536Fx                                    |                        |                                                                                       |       |      |       |       |

| nFAULT Leakage Current                                                  | I <sub>nFAULTLKG</sub> |                                                                                       | -1    |      | 1     | μA    |

| nFAULT Pull-Down Resistance                                             | R <sub>nFAULT</sub>    |                                                                                       |       | 13   | 20    | Ω     |

| Over-Temperature Protection (OTP)                                       |                        | ·                                                                                     |       |      | •     |       |

| Thermal Shutdown Rising Threshold                                       | T <sub>SD</sub>        |                                                                                       |       | 155  |       | °C    |

| Thermal Shutdown Hysteresis                                             | T <sub>HYS</sub>       |                                                                                       |       | 30   |       | °C    |

| SS                                                                      |                        |                                                                                       |       |      |       |       |

| SS Pin Charging Current                                                 | I <sub>SS</sub>        |                                                                                       | 1.00  | 2.01 | 3.00  | μA    |

|                                                                         |                        |                                                                                       |       |      |       |       |

# TIMING REQUIREMENTS

| PARAMETER                                   | SYMBOL            | CONDITIONS                                                                                                    | MIN | TYP | MAX | UNITS |

|---------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Over-Voltage Lockout Response Time          | t <sub>ovlo</sub> | $V_{OVLO} > V_{OV_R}$ to $V_{OUT}$                                                                            |     | 2.5 |     | μs    |

| Current Limit Response Time                 | t <sub>LIM</sub>  | $I_{ILIM}$ = 2A, $I_{OUT}$ > 1.2 × $I_{ILIM}$ and $I_{ITIMER}$<br>expired to $I_{OUT}$ settling to $I_{ILIM}$ |     | 250 |     | μs    |

| Scalable Fast-Trip Response Time            | t <sub>sc</sub>   | $I_{OUT} > 3 \times I_{ILIM}$ to $I_{OUT}\downarrow$                                                          |     | 500 |     | ns    |

| Auto-Retry Interval after Fault (SGM2536xR) | t <sub>RST</sub>  |                                                                                                               |     | 110 |     | ms    |

| PG Assertion De-Glitch                      | t <sub>PGA</sub>  |                                                                                                               |     | 15  |     | μs    |

| PG De-Assertion De-Glitch                   | t <sub>PGD</sub>  |                                                                                                               |     | 15  |     | μs    |

# 5.5A, 23.7mΩ Electronic Fuse **Supporting Bidirectional Current Conduction**

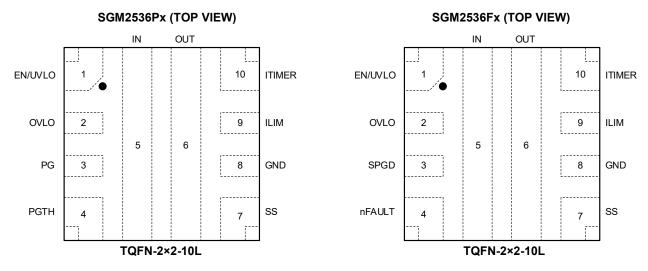

# SWITCHING CHARACTERISTICS

$(R_L = 100\Omega, C_{OUT} = 10\mu F$ , typical values are at  $T_J = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER               | SYMBOL             | V <sub>IN</sub>        | C <sub>ss</sub> = Open | C <sub>ss</sub> = 1800pF | C <sub>SS</sub> = 3300pF | UNITS |

|-------------------------|--------------------|------------------------|------------------------|--------------------------|--------------------------|-------|

|                         |                    | V <sub>IN</sub> = 2.7V | 7.4                    | 0.86                     | 0.47                     |       |

| Output Rising Slew Rate | SR <sub>ON</sub>   | V <sub>IN</sub> = 12V  | 22                     | 0.96                     | 0.48                     | V/ms  |

|                         |                    | V <sub>IN</sub> = 23V  | 35                     | 0.97                     | 0.46                     |       |

|                         |                    | V <sub>IN</sub> = 2.7V | 0.58                   | 3.9                      | 6.6                      |       |

| Turn-On Time            | t <sub>on</sub>    | V <sub>IN</sub> = 12V  | 0.79                   | 12.4                     | 24.3                     | ms    |

|                         |                    | V <sub>IN</sub> = 23V  | 0.87                   | 22.6                     | 46.2                     |       |

|                         |                    | V <sub>IN</sub> = 2.7V | 0.29                   | 1.4                      | 2                        |       |

| Turn-On Delay           | t <sub>D_ON</sub>  | V <sub>IN</sub> = 12V  | 0.35                   | 2.4                      | 4.4                      | ms    |

|                         |                    | V <sub>IN</sub> = 23V  | 0.35                   | 3.6                      | 6.2                      |       |

|                         |                    | V <sub>IN</sub> = 2.7V | 0.29                   | 2.5                      | 4.6                      |       |

| Rise Time               | t <sub>R</sub>     | V <sub>IN</sub> = 12V  | 0.44                   | 10                       | 19.9                     | ms    |

|                         |                    | V <sub>IN</sub> = 23V  | 0.52                   | 19                       | 40                       |       |

|                         |                    | V <sub>IN</sub> = 2.7V | 48                     | 48                       | 50                       |       |

| Turn-Off Delay          | t <sub>D_OFF</sub> | V <sub>IN</sub> = 12V  | 15                     | 15                       | 15.4                     | μs    |

|                         |                    | V <sub>IN</sub> = 23V  | 9                      | 8                        | 10                       | 1     |

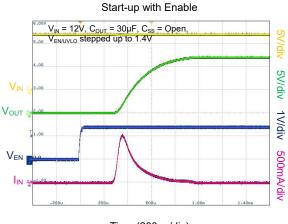

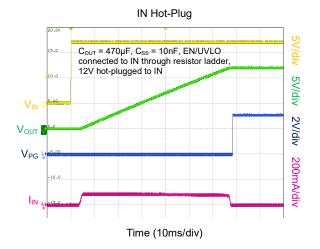

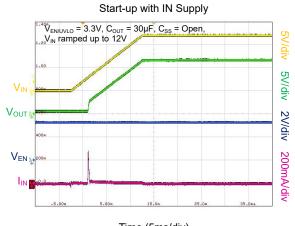

In the entire normal voltage range, the output voltage rise rate is set by the internal circuit and remains unchanged to ensure that the load state does not affect the start-up sequence. Adding capacitance between the SS pin and GND can change the OUT rising slope. Increasing capacitor C<sub>SS</sub> will reduce the rate of rise (SR) of the output voltage. For a detailed description, please refer to the relevant sections on inrush current suppression (SS) and slew rate. However, the time that V<sub>OUT</sub> falls when the device is turned off is determined by the RC time constants of the load resistor (R<sub>L</sub>) and load capacitor (C<sub>OUT</sub>). The control of the switch only affects the power-on sequence when the chip is turned on.

Figure 1. SGM2536 Switching Times

# 5.5A, 23.7mΩ Electronic Fuse Supporting Bidirectional Current Conduction

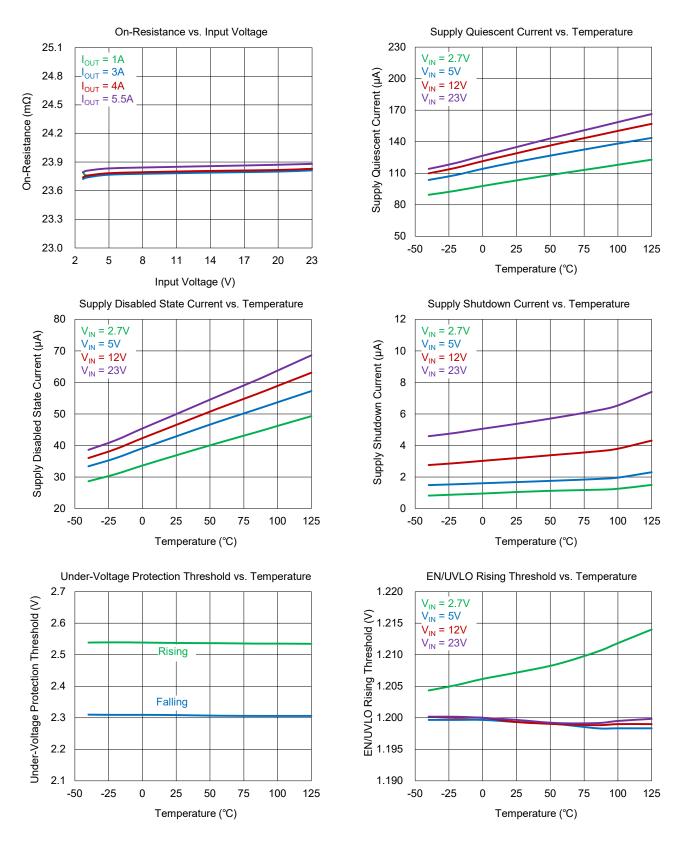

# **TYPICAL PERFORMANCE CHARACTERISTICS**

SG Micro Corp

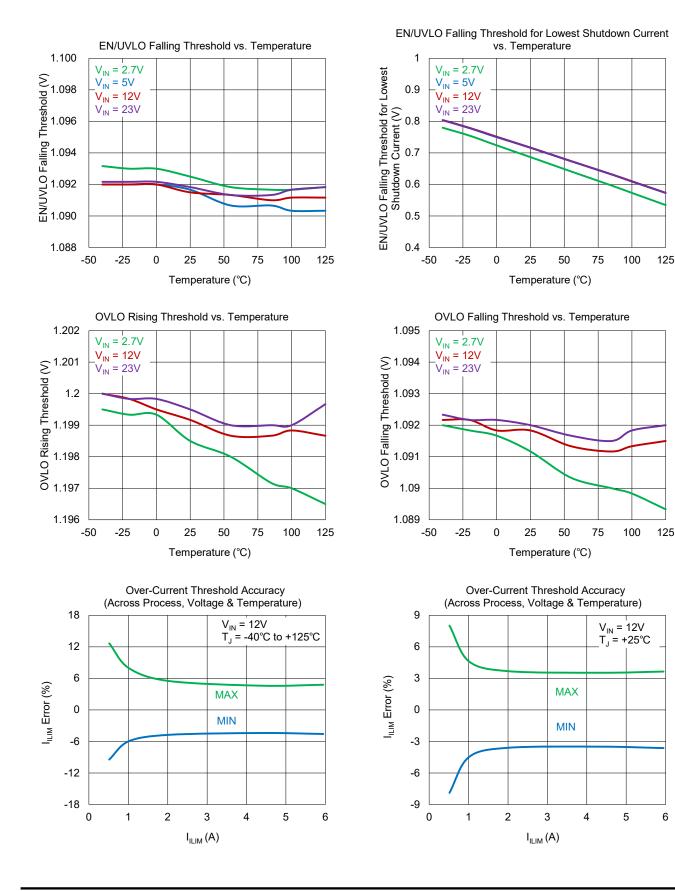

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

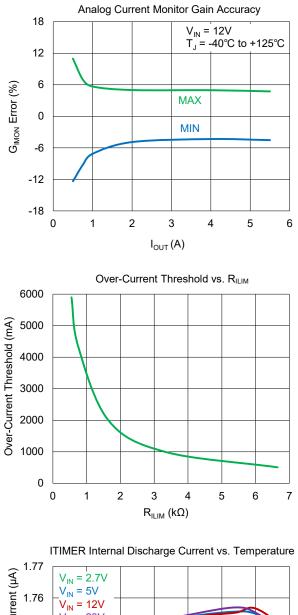

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

ITIMER Internal Pull-Up Resistance vs. Temperature

SG Micro Corp

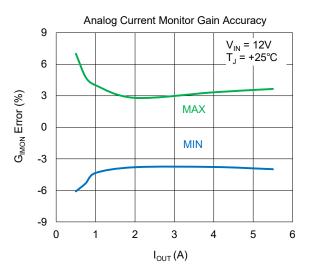

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Time (10ms/div)

Time (5ms/div)

Time (1ms/div)

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Time (2ms/div)

Time (20µs/div)

Time (2ms/div)

SG Micro Corp SGMICRO www.sg-micro.com

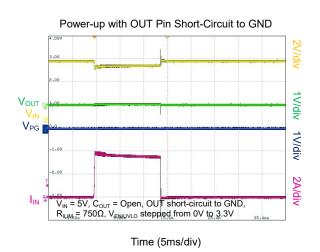

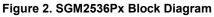

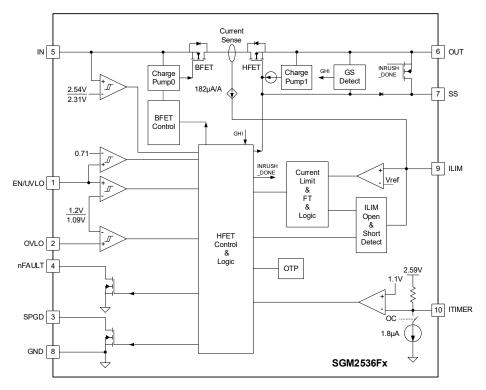

# FUNCTIONAL BLOCK DIAGRAM

## **DETAILED DESCRIPTION**

#### Overview

SGM2536 is an eFuse with internal integration of back-to-back FETs (BFET + HFET). It ensures the safety of the power delivery system due to its rich features. When the V<sub>IN</sub> is greater than V<sub>UVP\_R</sub>, the device starts to sample the voltage of the EN/UVLO pin (V<sub>EN/UVLO</sub>). If V<sub>EN/UVLO</sub> exceeds V<sub>UVLO\_R</sub>, BFET and HFET start conducting and the current can flow in both directions. When the V<sub>IN</sub> is less than V<sub>UVP\_F</sub> or V<sub>EN/UVLO</sub> < V<sub>UVLO\_F</sub>, both BFET and HFET are turned off to realize the reverse current blocking.

After device start-up, the SGM2536 will monitor the V<sub>IN</sub> and forward current (from IN to OUT). By controlling HFET, the load current cannot exceed the set current limit threshold (IILIM), and over-voltage spikes are cut-off if they exceed the user-adjustable over-voltage lockout threshold  $(V_{OVIO})$ . The fast-trip response of the device provide rapid can protection against serious over-current during short-circuit of OUT pin, so as to prevent the system from being damaged by harmful voltage and current. In addition, the device also provides a user-adjustable over-current blanking timer to allow short-time over-current in the power path without tripping the device frequently. Therefore, SGM2536 not only provides complete protection functions, but also ensures the maximum system uptime during transient events.

There is an integrated thermal sensor to protect itself when the device temperature exceeds the  $T_{SD}$ .

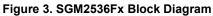

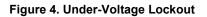

#### Under-Voltage Lockout (UVLO and UVP)

The SGM2536 implements under-voltage protection at IN pin to prevent IN voltage from being too low for normal operation of system and equipment. A fixed locking threshold voltage ( $V_{UVP}$ ) is provided inside the device for under-voltage protection. In addition, the comparator on the EN/UVLO terminal can be used to set the user-adjustable under-voltage protection threshold through the external resistor divider. Figure 4 and Equation 1 show how to set the specific value of under-voltage protection threshold using an external resistor divider.

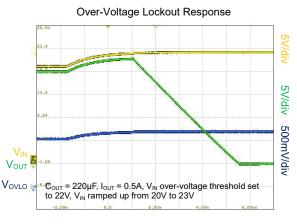

#### Over-Voltage Lockout (OVLO)

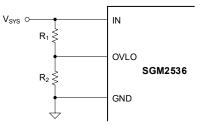

The SGM2536 implements over-voltage lockout at OVLO pin to prevent IN voltage from being too high for normal operation of system and equipment. The comparator on the OVLO pin is used to set the user-adjustable over-voltage protection threshold through the external resistor divider. If the voltage of OVLO pin exceeds the V<sub>OVLO\_R</sub>, the device will shut down the power path. When the voltage of OVLO pin is lower than the V<sub>OVLO\_F</sub>, the power path will be reopened with inrush control. There is a hysteresis between the rising threshold and falling threshold of OVLO. The Equation 2 and Figure 5 show how to set the specific value of over-voltage protection threshold using an external resistor divider.

$$V_{\rm IN_OV} = \frac{V_{\rm OVLO} \times (R_1 + R_2)}{R_2}$$

(2)

Figure 5. Adjustable Over-Voltage Protection

Figure 6. Over-Voltage Lockout and Recovery

# Inrush Current, Over-Current, and Short-Circuit Protection

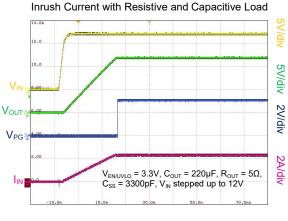

SGM2536 adopts four levels of forward over-current protection function:

- Programmable slew rate (SR) for inrush current protection.

- Programmable current limit threshold (I<sub>ILIM</sub>) for over-current in steady state or start-up.

- Programmable threshold (I<sub>SC</sub>) for severe over-current in steady state or start-up.

- Fixed I<sub>FT</sub> for fast-trip function when short-circuit of OUT occurs.

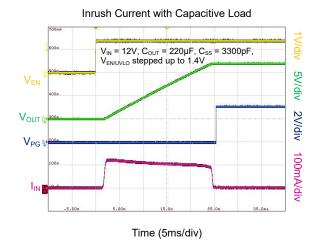

Slew Rate (SR) and Inrush Current Protection When hot-plug or system charging large capacitive load occurs, a large inrush current is generated in the equipment power path. The input connector may be damaged or the input power rail voltage may drop, which affects the normal operation and even restarts other equipment in the system.

For a given  $C_{\text{OUT}},$  the relationship between the slew rate (SR) and inrush current (I\_{\text{INRUSH}}) is shown in Equation 3.

$$SR (V/ms) = \frac{I_{INRUSH} (mA)}{C_{OUT} (\mu F)}$$

(3)

The slew rate can be controlled by connecting a capacitor at the SS pin to reduce inrush current. For a given slew rate, the corresponding  $C_{SS}$  can be calculated by Equation 4. When the SS pin is left floating, the fastest output slew rate can be obtained.

$$C_{ss} (pF) = \frac{2000}{SR (V/ms)}$$

(4)

NOTE: For  $C_{SS}$  > 10nF, a 100 $\Omega$  resistor is recommended to be in series with the  $C_{SS}$  on the SS pin.

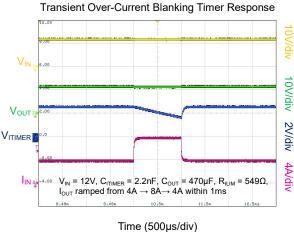

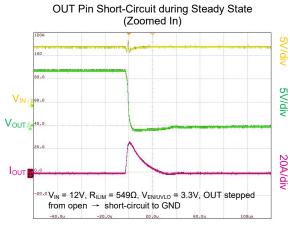

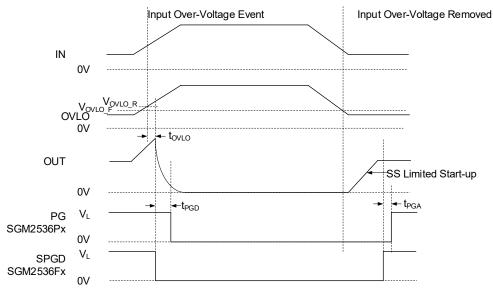

#### **Current Limit**

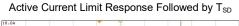

In case of output over-current, the device actively limits the current after the blanking timer expiring. When the load current exceeds the over-current threshold  $(I_{\parallel M})$ , but is less than the short-circuit threshold  $(2 \times I_{IIIM})$ , the device discharges CITIMER on the ITIMER pin through an internal 1.8µA pull-down current source. Once the load current decreases below the over-current threshold before the  $C_{\text{ITIMER}}$  is discharged by  $\Delta V_{\text{ITIMER}}$ , the ITIMER pin will be pulled up to VINT internally and the current limit will not be triggered. If the over-current condition still exists after the  $C_{ITIMER}$  voltage drops by  $\Delta V_{ITIMER}$ , the device will limit the current to the over-current threshold by regulating HFET. At the same time, the ITIMER pin is recharged to the V<sub>INT</sub> to maintain the default state before the next over-current event, which ensures a complete blanking time for each over-current event. In general, the device can provide protection against over-current events and also allow transient current pulses to flow through the power path. For a given over-current threshold, the value of R<sub>ILIM</sub> can be calculated by Equation 5.

$$R_{ILIM}(\Omega) = \frac{3260}{I_{ILIM} - 0.03 (A)}$$

or  $R_{ILIM}(\Omega) = \frac{3334}{I_{ILIM}(A)}$  (5)

#### NOTES:

1. The device only provides forward (from IN to OUT) over-current protection function.

2. Leave the ILIM pin floating to set the over-current threshold near zero, and the device can hardly be loaded.

3. The current limit circuit implements the fold-back mechanism. In the fold-back region (0V <  $V_{OUT}$  <  $V_{FB}$ ), the current limit threshold is smaller than the current limit threshold (I<sub>ILIM</sub>) under steady state.

4. When the ILIM is short to the GND under normal operations, it will be detected as a fault case. There is a minimum  $I_{nFAULT}$  which the device allows in this case before the pin short condition is detected.

The blanking time can be adjusted by changing the capacitance connected to the ITIMER pin. Over-current blanking time can be calculated by Equation 6.

$$t_{\text{ITIMER}} \text{ (ms)} = \frac{\Delta V_{\text{ITIMER}} (V) \times C_{\text{ITIMER}} (nF)}{I_{\text{ITIMER}} (\mu A)}$$

(6)

#### NOTES:

1. Leaving the ITIMER pin floating or short to GND sets the minimum over-current blanking time. But it is not recommended to leave ITIMER pin short to GND, because it increases the current consumption of the device.

2. The active current limit set by  $R_{ILIM}$  is still valid during start-up, which ensures that the load current does not exceed  $I_{ILIM}$  during start-up. However, there is no over-current blanking time in the start-up process.

3. Increasing C<sub>ITIMER</sub> can increase the over-current blanking time, but it also increases the time for C<sub>ITIMER</sub> to charge to V<sub>INT</sub>. If the next over-current case occurs before the C<sub>ITIMER</sub> is fully charged to the V<sub>INT</sub>, the current blanking time of this event will be shorter than intended.

During the active current limit, there is more power dissipation on the HFET because the output voltage drops. If the internal temperature of the device exceeds the  $T_{SD}$ , the HFET will be turned off, and the device will either be latched off (SGM2536xL) or restarted automatically after a certain time interval (SGM2536xR).

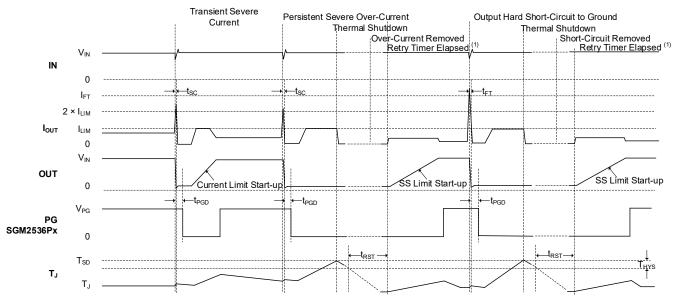

#### Figure 7. Current Limit Response

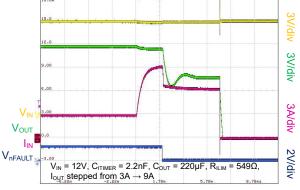

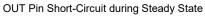

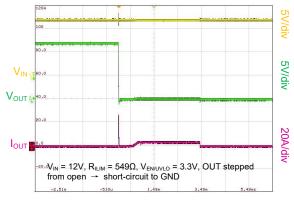

#### **Short-Circuit Protection**

When a serious over-current event similar to a short-circuit event occurs, the SGM2536 triggers a fast-trip response to prevent the system from being damaged by excessive current flowing through the device. A fast-trip comparator with scalable threshold ( $I_{SC} = 2 \times I_{ILIM}$ ) is adopted inside the device, which allows users to program the fast-trip threshold in low current system. A fixed fast-trip threshold is also set inside the device for fast protection against hard short-circuit events in steady state. It is recommended

that the fixed fast-trip threshold be greater than the maximum value of the scalable fast-trip threshold. HFET will be completely turned off within  $t_{FT}$  if the current exceeds  $I_{FT}$  or  $I_{SC}$ . Then the device will turn HFET on again after a short of deglitch time in a current limit mode. In this way, the rapid recovery of HFET can be realized after a transient severe over-current event, and the drop of OUT voltage can be minimized. If the fault persists, the devices continue to operate in the current limit mode, causing the internal temperature of the device to rise until the thermal shutdown.

NOTE: 1. SGM2536xR only.

Figure 8. Short-Circuit Response

#### Load Current Monitor Output

The device provides an analog current sensing output proportional to the load current at the ILIM pin, which enables the device to monitor the load current (from IN to OUT). The user can calculate the load current through the voltage of the ILIM pin connected to the  $R_{ILIM}$ . The relationship between  $V_{ILIM}$  and  $I_{OUT}$  is shown in Equation 7.

$$I_{OUT} (A) = \frac{V_{ILIM} (\mu V)}{R_{ILIM} (\Omega) \times G_{IMON} (\mu A/A)}$$

(7)

NOTES:

1. ILIM pin is sensitive to capacitive loads. In order to ensure the normal operation of the device, the parasitic capacitance of the ILIM pin needs to be less than 50pF.

2. The analog load current monitor is only applicable to the forward current (from IN to OUT).

#### **Reverse Current Protection**

The SGM2536 is internally integrated with back-to-back MOSFETs connected in a common drain configuration. When the device is disabled or shutdown, both FETs are turned off, so the current in both directions is blocked.

#### **Over-Temperature Protection (OTP)**

The SGM2536 always monitors the temperature (T<sub>J</sub>) of the internal die. Once the internal temperature exceeds the T<sub>SD</sub>, the device shuts down immediately. The SGM2536 will not turn on until the internal temperature is lower than a safe threshold (T<sub>SD</sub> - T<sub>HYS</sub>).

When SGM2536xL triggers the thermal shutdown, it still remains in the shutdown state unless the equipment is re-enabled or power cycled. When SGM2536xR triggers the thermal shutdown, it remains in the shutdown state until the internal temperature of the equipment drops by  $T_{HYS}$ . After that, it will retry to turn on automatically after a  $t_{RST}$  delay time if the device is still enabled.

#### Fault Response and Indication (nFAULT)

Table 2 shows the protection response of equipment under different fault conditions. The SGM2536Fx provides an active-low external fault flag pin.

A latched fault can be cleared by power cycling (pulling  $V_{IN}$  to 0V) or re-enable (pulling EN/UVLO pin below  $V_{SD}$ ). This will also reset the  $t_{RST}$  in SGM2536xR. It is worth mentioning for the whole SGM2536 series, pulling down EN/UVLO below the UVLO threshold cannot clear the latched fault. The SGM2536xR will retry automatically after the  $t_{RST}$  timer expiring when a fault has occurred.

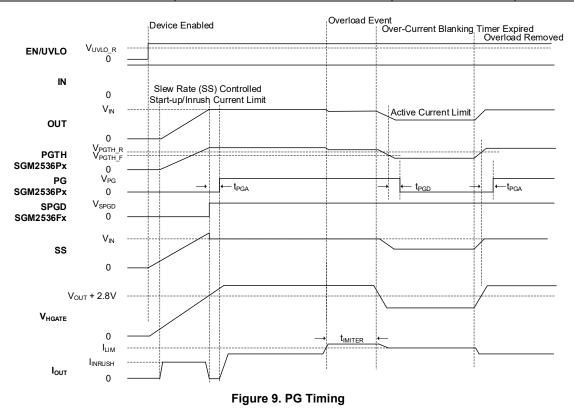

#### Power Good Pin (PG)

The SGM2536Px provides an active-high open-drain output (PG) as the indication pin of power good. It is asserted as high according to the PGTH pin voltage and the equipment working state. PG pin needs to be pulled up to an external power supply.

At the initial stage of power-on, PG is pulled down. Then the device enters the start-up sequence, in which the HFET has been controlled and not fully conductive. When the gate voltage of HFET reaches overdrive, HFET is fully conductive and the start-up sequence is completed,  $V_{PGTH}$  is higher than  $V_{PGTH_R}$ , and PG is asserted high after a deglitch time ( $t_{PGA}$ ).

The PG will be de-asserted when the PGTH voltage falls below  $V_{PGTH_F}$  or when the system has faults other than over-current during steady state. The deglitch time is  $t_{PGD}$ , when PG is de-asserted.

When the device is not powered, the PG pin should be low. However, there is no effective power supply to drive the PG pin down to GND in this case. If the PG is pulled up by an independent power supply and the device is not powered, there may be a small voltage on the PG caused by sink current, which is a function of the pull-up supply and pull-up resistance connected to the PG. In order to avoid the small voltage on the PG pin being detected as logic high by the external related circuit, the sink current of the pin should be minimized.

#### Table 1. Thermal Shutdown

| Device                 | Enter T <sub>SD</sub> | Exit T <sub>SD</sub>                                                              |

|------------------------|-----------------------|-----------------------------------------------------------------------------------|

| SGM2536xL (Latch-Off)  | $T_J \ge T_{SD}$      | $T_J < T_{SD}$ - $T_{HYS}$ , device power cycled or re-enabled (with EN/UVLO pin) |

| SGM2536xR (Auto-Retry) | $T_J \ge T_{SD}$      | $T_J < T_{SD}$ - $T_{HYS}$ , $t_{RST}$ timer expired                              |

Table 2. Fault Summary

| Event                                                               | Protection Response                          | Fault Latched<br>Internally | nFAULT Pin Status <sup>(1)</sup> | nFAULT Assertion<br>Delay <sup>(1)</sup> |

|---------------------------------------------------------------------|----------------------------------------------|-----------------------------|----------------------------------|------------------------------------------|

| Over-Temperature                                                    | Shutdown                                     | Y                           | L                                |                                          |

| Under-Voltage (UVP or UVLO)                                         | Shutdown                                     | N                           | Н                                |                                          |

| Over-Voltage                                                        | Shutdown                                     | N                           | Н                                |                                          |

| Transient Over-Current ( $I_{ILIM} < I_{OUT} < 2 \times I_{ILIM}$ ) | None                                         | N                           | Н                                |                                          |

| Persistent Over-Current (from IN to OUT)                            | Current Limit                                | N                           | L                                | t <sub>ITIMER</sub>                      |

| OUT Short-Circuit to GND                                            | Circuit Breaker Followed<br>by Current Limit | Ν                           | н                                |                                          |

| Over-Current during ILIM Open                                       | Shutdown                                     | Ν                           | L                                | t <sub>ITIMER</sub>                      |

| Over-Current during ILIM Shorted to GND                             | Shutdown                                     | Y                           | L                                |                                          |

NOTE: 1. SGM2536Fx only.

#### Table 3. SGM2536Px PG Indication

| Event                                   | Protection Response                 | PG Pin Status                   | PG Delay         |

|-----------------------------------------|-------------------------------------|---------------------------------|------------------|

| Under-Voltage (UVP or UVLO)             | Shutdown                            | L                               |                  |

| Over-Voltage                            | Shutdown                            | L                               | t <sub>PGD</sub> |

| Steady State                            | NA                                  | H (If $V_{PGTH} > V_{PGTH_R}$ ) | t <sub>PGA</sub> |

| Sleady State                            | NA                                  | $L (If V_{PGTH} < V_{PGTH_F})$  | t <sub>PGD</sub> |

| Transient Over-Current                  | NA                                  | H (If $V_{PGTH} > V_{PGTH_R}$ ) | t <sub>PGA</sub> |

| Transient Over-Current                  | NA                                  | $L (If V_{PGTH} < V_{PGTH_F})$  | t <sub>PGD</sub> |

| Persistent Overload (from IN to OUT)    | Current Limit                       | H (If $V_{PGTH} > V_{PGTH_R}$ ) | t <sub>PGA</sub> |

| Persistent Overload (Iron in to COT)    | Current Linnt                       | $L (If V_{PGTH} < V_{PGTH_F})$  | t <sub>PGD</sub> |

| OUT Short-Circuit to GND                | Fast-Trip followed by Current Limit | L                               | t <sub>PGD</sub> |

| Over-Current during ILIM Open           | Shutdown                            | L                               | t <sub>PGD</sub> |

| Over-Current during ILIM Shorted to GND | Shutdown                            | L                               | t <sub>PGD</sub> |

| Over-Temperature                        | Shutdown                            | L                               | t <sub>PGD</sub> |

#### Input Supply Good Indication (SPGD)

The SGM2536Fx provides an active-high open-drain output (SPGD) as a supply valid status indication to the downstream load or system supervisor. SPGD is asserted when the IN voltage is in a proper range (UVP/UVLO <  $V_{IN}$  < OVLO) and the inrush sequence of the device is completed. SPGD pin needs to be pulled up to an external power supply.

At the initial stage of power-on, SPGD pin is pulled down. Then the device enters the start-up sequence, in which the HFET has been controlled and not fully conductive. When the gate voltage of HFET reaches overdrive, HFET is fully conductive and the start-up sequence is completed, the SPGD is asserted high. When the device is not powered, the SPGD pin should be low. However, there is no effective power supply to drive the SPGD pin down to 0V in this case. If the SPGD is pulled up by an independent power supply and the device is not powered, there may be a small voltage on the SPGD caused by sink current, which is a function of the pull-up supply and pull-up resistance connected to the SPGD. In order to avoid the small voltage on the SPGD pin being detected as logic high by the external related circuit, the sink current of the pin should be minimized.

#### **Device Functional Modes**

When operating under the recommended operating conditions, the device has one applicable operating mode.

#### Table 4. SGM2536Fx SPGD Indication

| Event                                   | SPGD Pin |

|-----------------------------------------|----------|

| Under-Voltage (UVP or UVLO)             | L        |

| Over-Voltage (OVLO)                     | L        |

| Inrush                                  | L        |

| Steady State                            | Н        |

| Over-Current                            | Н        |

| OUT Short-Circuit to GND                | L        |

| Over-Current during ILIM Open           | L        |

| Over-Current during ILIM Shorted to GND | L        |

| Over-Temperature                        | L        |

# **APPLICATION INFORMATION**

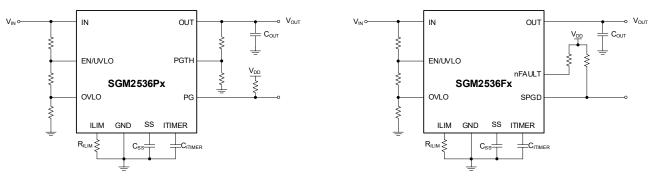

#### Single Device, Self-Controlled

In a system where the MCU is the host, the EN/UVLO or OVLO pin of the device can be driven by the GPIO of the host to realize the control of the device. The ILIM pin can be used as an ADC input to the MCU for current monitoring.

NOTE: ILIM pin is sensitive to capacitive loading. In order to ensure the normal operation of the device, the parasitic capacitance of the ILIM pin needs to be less than 50pF.

For the SGM2536Px, resistor divider of PGTH can be connected to either IN or OUT, depending on which voltage is more suitable as a power good indication.

#### **Typical Application**

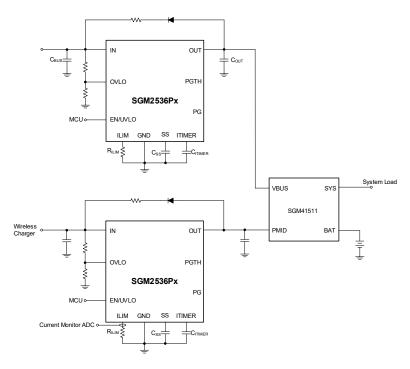

Many smartphones are equipped with a USB OTG function, which not only allows charging the phone battery, but also allows the phone to be used as a USB host or to charge accessories such as headphones. In addition, some mobile phones are equipped with wireless charging and support wireless charging to charge other devices in reverse. The SGM2536 series can be used as a bidirectional power switch in the above system, as shown in Figure 11.

Figure 11. Power Path Example for Smartphone

# **APPLICATION INFORMATION (continued)**

When the USB interface is externally connected to the charger to charge the mobile phone battery, the SGM2536 provides the current path from IN to OUT, and the battery charging IC manages the output control signal to control the charging process of the battery while supplying power to other circuits inside the mobile phone. In this case, the SGM2536 provides over-current and over-voltage protections. Another situation is that when the USB interface is connected to the accessories such as headphones that require the mobile phone battery to provide power, the internal MCU of the mobile phone recognizes the accessories

and configures the battery charging IC to BOOST mode and supplies power to the accessories through the USB interface. The SGM2536 needs to provide a current from OUT to IN, and since the IN pin requires a certain voltage ( $V_{UVP_R}$ ) to turn on the power switch, a diode and resistor in parallel with the device can provide the required bias voltage. The MCU then enables the SGM2536 and establishes a low impedance path to deliver power to the accessories.

Similarly, the device provides a bidirectional power flow path during wireless charging and wireless reverse charging.

\* Transient protection requires optional circuit components. See the *Transient Protection* section for details.

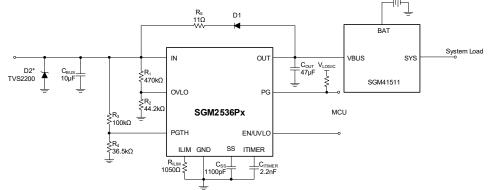

Figure 12. USB On-the-Go Port Protection

### **Design Requirements**

Table 5. Design Parameters

| Parameter                                                             | Value      |

|-----------------------------------------------------------------------|------------|

| Bus Voltage during Charging, V <sub>IN</sub>                          | 9V         |

| Over-Voltage Protection Threshold during Charging, $V_{IN_OV}$        | 14V        |

| Bus Power Good Threshold, V <sub>PG</sub>                             | 4.5V       |

| Max Continuous Charging Current                                       | 3A         |

| Load Transient Blanking Interval during Charging, $t_{\text{ITIMER}}$ | 2ms        |

| Output Capacitance, C <sub>OUT</sub>                                  | 47µF       |

| Output Rise Time, t <sub>R</sub>                                      | 5ms        |

| Over-Current Threshold $(I_{ILIM})$ during Charging                   | 3.25A      |

| Start-up Load Current Supported during USB OTG Operation, $I_{LOAD}$  | 100mA      |

| Fault Response                                                        | Auto-Retry |

# **APPLICATION INFORMATION (continued)**

#### **Detailed Design Procedure**

SGM2536PR is selected according to the actual application scenario.

#### Setting Over-Voltage Threshold

The over-voltage threshold is set by a resistor divider connected to the OVLO pin. This threshold can be calculated from Equation 8:

$$V_{IN_{OV}} = \frac{V_{OV_{R}} \times (R_1 + R_2)}{R_2}$$

(8)

where  $V_{OV_R}$  is the rising threshold of the OVLO pin and  $R_1 \& R_2$  are the resistors of the resistor divider. Since  $R_1 \& R_2$  causes additional leakage current to flow out of the input voltage, their values need to be taken into account for the acceptable leakage current of the system. The leakage current flowing through  $R_1 \& R_2$  from the supply voltage is  $I_{R12} = V_{IN}/(R_1 + R_2)$ . Considering that an external active device connected to a resistor divider causes additional leakage current, this increases the calculation error of the supply over-voltage threshold. Therefore, the leakage current flowing through  $R_1 \& R_2$  ( $I_{R12}$ ) should be greater than 20 times the leakage current expected by the OVLO pin.

As can be seen from the EC table, the maximum leakage current of the OVLO pin is  $0.1\mu$ A, and  $V_{OV_R}$  = 1.2V. According to the application scenario requirements,  $V_{IN_OV}$  = 14V. Given  $R_1$  = 470k $\Omega$ ,  $R_2$  = 44.06k $\Omega$  can be obtained according to the above equation.

Selecting the nearest standard 1% resistor values,  $R_1 = 470k\Omega \& R_2 = 44.2k\Omega$  are chosen.

#### Setting Output Voltage Rise Time (t<sub>R</sub>)

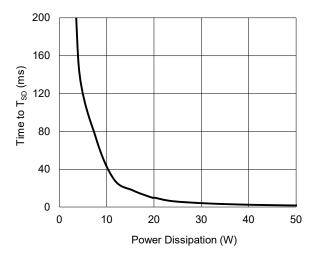

During the design process, it must be ensured that the junction temperature of the device does not meet the thermal shutdown threshold under either start-up or steady-state conditions. Given that the power stress to which the device is subjected at start-up is typically an order of magnitude larger than under steady-state conditions, the determination of start-up time and inrush current limit is particularly important to avoid thermal shutdown at start-up.

After rise time  $(t_R)$  is determined, the slew rate (SR) can be calculated by:

SR (V/ms)

$$= \frac{V_{IN}(V)}{t_{R}(ms)} = \frac{9V}{5ms} = 1.8V/ms$$

(9)

The value of the capacitance  $(C_{SS})$  on the SS pin corresponding to this SR can be calculated by the following equation:

$$C_{ss}(pF) = \frac{2000}{SR(V/ms)} = \frac{2000}{1.8} = 1111pF$$

(10)

Select the nearest standard capacitor with a capacitance of 1100pF.

The inrush current can be calculated as:

$$I_{INRUSH}$$

(mA) = SR (V/ms)×C<sub>OUT</sub> (µF) = 1.8×47 = 84.6mA (11)

During inrush, the average power dissipation inside the device can be calculated as:

$$PD_{INRUSH} (W) = \frac{I_{INRUSH} (A) \times V_{IN} (V)}{2} = \frac{0.085 \times 9}{2} = 0.38W$$

(12)

Based on the calculated power dissipation, the corresponding thermal shutdown time must be higher than the output rise time. Figure 13 shows that for 0.38W, the device thermal shutdown time is greater than 100ms, which is much larger than the output rise time (5ms). Therefore, setting the output rise time to 5ms has no negative impact on device security.

Figure 13. Thermal Shutdown Plot during Inrush

# **APPLICATION INFORMATION (continued)**

#### **Power Good Assertion Threshold**

The power good assertion threshold is set by a resistor divider connected to the PGTH pin. This threshold can be calculated from Equation 13:

$$V_{PG} = \frac{V_{PGTH_R} \times (R_3 + R_4)}{R_4}$$

(13)

where V<sub>PGTH\_R</sub> is the rising threshold of the PGTH pin and R<sub>3</sub> & R<sub>4</sub> are the resistors of the resistor divider. Since R<sub>3</sub> & R<sub>4</sub> causes additional leakage current to flow out of the output voltage, their values need to be taken into account for the acceptable leakage current of the system. The leakage current flowing through R<sub>3</sub> & R<sub>4</sub> from the supply is I<sub>R34</sub> = V<sub>IN</sub>/(R<sub>3</sub> + R<sub>4</sub>). Considering that an external active device connected to a resistor divider causes additional leakage current, this increases the calculation error of the supply over-voltage threshold. Therefore, the leakage current flowing through R<sub>3</sub> & R<sub>4</sub> (I<sub>R34</sub>) should be greater than 20 times the leakage current expected by the PGTH pin.

As can be seen from the EC table, the maximum leakage current of the PGTH pin is  $0.3\mu$ A, and  $V_{PGTH_R}$  = 1.2V. According to the application scenario requirements,  $V_{PG}$  = 4.5V. Given  $R_3$  = 100k $\Omega$ ,  $R_4$  = 36.4k $\Omega$  can be obtained according to the above equation.

Choose the nearest standard 1% resistor values,  $R_3 = 100 k\Omega \& R_4 = 36.5 k\Omega$  are recommended.

#### Setting Over-Current Threshold (IILIM)

The over-current threshold can be set by the resistor  $R_{ILIM}$  connected to the ILIM pin, and its value can be calculated by Equation 14:

$$R_{ILIM}(\Omega) = \frac{3334}{I_{ILIM}(A)} = \frac{3334}{3.25A} = 1025.8\Omega$$

(14)

Choose the nearest standard 1% resistor values,  $R_{ILIM}$  = 1050 $\Omega$  is recommended.

# Setting Over-Current Blanking Interval (t<sub>ITIMER</sub>)

The over-current blanking time can be set by  $C_{\text{ITIMER}}$ , and it can be calculated as following.

$$C_{\text{ITIMER}} (nF) = \frac{t_{\text{ITIMER}} (ms) \times I_{\text{ITIMER}} (\mu A)}{\Delta V_{\text{ITIMER}} (V)} = \frac{2 \times 1.8}{1.5} = 2.4 nF \quad (15)$$

Select the nearest standard capacitor with a capacitance of 2.2nF.

#### Choosing External Bias Resistor (R<sub>5</sub>)

In OTG mode, the initial state of the SGM2536PR is off. The initial voltage across the USB bus through the diode (D1) and resistor ( $R_5$ ) can be calculated by:

$$V_{BUS}(V) = V_{OUT}(V) - V_F(V) - I_{LOAD}(A) \times R_5(\Omega)$$

(16)

where:

$V_{\mbox{\scriptsize OUT}}$  is the voltage supplied by the battery charging IC in Boost mode.

V<sub>F</sub> is the forward voltage drop across diode D1.

$\ensuremath{\mathsf{I}_{\mathsf{LOAD}}}$  is the current drawn by USB powered peripheral initially.

The USB bus voltage must be higher than V<sub>UVP\_R</sub> to ensure that the SGM2536PR can be turned on and can provide sufficient current for USB peripheral devices. Given V<sub>F</sub> = 0.4V, V<sub>OUT\_MIN</sub> = 4.5V, V<sub>UVP\_R</sub> = 2.54V, I<sub>LOAD</sub> = 100mA, the maximum R<sub>5</sub> value of 15.6 $\Omega$  can be calculated. Select R<sub>5</sub> = 11 $\Omega$ .

The power dissipation of  $R_5$  under initial conditions can be calculated from Equation 17.

$$P_{D}(W) = I_{LOAD}(A) \times I_{LOAD}(A) \times R_{5}(\Omega) \quad (17)$$

When the load current is 100mA and  $R_5$  is 11 $\Omega$ , the power dissipation across  $R_5$  is 0.11W. Therefore, a resistor with a power rate of 0.25W is appropriate.

#### External Diode (D1) Selection

1. The diode forward voltage drop should be as small as possible to ensure that there is enough headroom for the USB bus voltage to be greater than  $V_{UVP_R}$ .

2. The diode can flow more than the maximum current required by the USB peripheral.

3. It must have small footprint.

#### **Power Supply Recommendations**

The SGM2536 is designed for a supply voltage from 2.7V to 23V. If the power supply is more than a few inches away from the device, it is recommended to place an input bypass ceramic capacitor greater than 0.1 $\mu$ F. The rated current of the power supply must be greater than the over-current threshold set by the device, otherwise the supply voltage will drop in the event of an over-current or short-circuit.

# **APPLICATION INFORMATION (continued)**

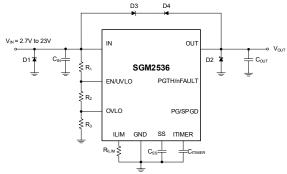

#### **Transient Protection**

If the short-circuit or over-current limit case occurs, the device may cut off the current, and due to the parasitic inductance in series at the input and output of the device, a positive voltage spike will occur at the input and output, and a negative voltage spike will occur at the output. The amplitude of the voltage spike is determined by the parasitic inductance. These transients can cause the voltage on the device pins to exceed their maximum absolute rating if the following measures are not taken:

- The length of the wires at the input and output of the device is as small as possible.

- A TVS diode is paralleled at the input port of the device to absorb a positive voltage spike, and a Schottky diode is connected in parallel to the output port to absorb a negative voltage spike.

- Choose a large PCB GND plane.

- Connect a low ESR ceramic capacitor larger than 10µF near the OUT pin.

- A ceramic capacitor greater than 10µF is connected near the input pin to absorb and suppress transient voltage spikes and ringing.

The value of the input capacitance can be calculated from the Equation 18:

$$V_{\text{SPIKE (Absolute)}} = V_{\text{IN}} + I_{\text{LOAD}} \times \sqrt{\frac{L_{\text{IN}}}{C_{\text{IN}}}}$$

(18)

where  $V_{IN}$  is the rating of the input voltage,  $I_{LOAD}$  is the load current,  $L_{IN}$  is the effective inductance seen looking into the source, and  $C_{IN}$  is the capacitance of the input.

For applications such as USB-C interfaces, the power cord may be plugged into the output of the device. In this case, the voltage stress from OUT to IN may exceed the absolute maximum rating, so it is recommended to add a TVS diode from OUT to IN to clamp the voltage for safety.

Figure 14. Application with Optional Protection Components

#### **Output Short-Circuit Measurements**

The output short-circuit waveform may be affected by factors such as input leads, power supply bypass, layout, device selection, circuit location, and output short-circuit method. It is difficult to obtain repeatable and similar output short-circuit test results. Therefore, the short-circuit results in this datasheet are for informational purposes only. Different short-circuit test results may be achieved because of different test conditions.

#### **Layout Guidelines**

In any application, it is recommended to connect a decoupling capacitor of  $0.1\mu F$  or greater between IN and GND. This decoupling capacitor should be as close as possible to IN and GND pins.

The power path should be as wide and short as possible, with a current carrying capacity of more than twice the device's current limit.

The GND pin of the device must be connected to PCB ground which is a copper plane or island as short as possible.

The IN and OUT pins of the device are used to dissipate heat. Therefore, these two pins should be dissipated as much as possible through the copper plane on the top layer or bottom layer on the PCB. Placing thermal vias on the copper plane improves on-resistance as well as current sensing accuracy.

External components of the device as follows should be placed as close to the corresponding pins as possible:

- R<sub>ILIM</sub>

- C<sub>SS</sub>

- C<sub>ITIMER</sub>

- Resistor dividers of EN/UVLO, OVLO and PGTH

The other end of these components is connected to ground via the shortest possible path. The ILIM pin should have a parasitic capacitance of less than 50pF, and the connection path of this pin should be away from the switching signal.

Protection components such as TVS or Schottky diodes should be connected to the device via a short path to avoid large line inductance. It is important to note that the loop area formed by the protection components should be as small as possible.

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| SEPTEMBER 2024 – REV.A.1 to REV.A.2                  | Page |

|------------------------------------------------------|------|

| Added UL Recognized Component (File No. E532373*)    | 1    |

| Updated Detailed Description (Current Limit section) |      |

| MAY 2024 – REV.A to REV.A.1                          | Page |

| Added Package Thermal Resistance                     | 2    |

| Updated Functional Block Diagram section             |      |

| Changes from Original (OCTOBER 2023) to REV.A        | Page |

| Changed from product preview to production data      | All  |

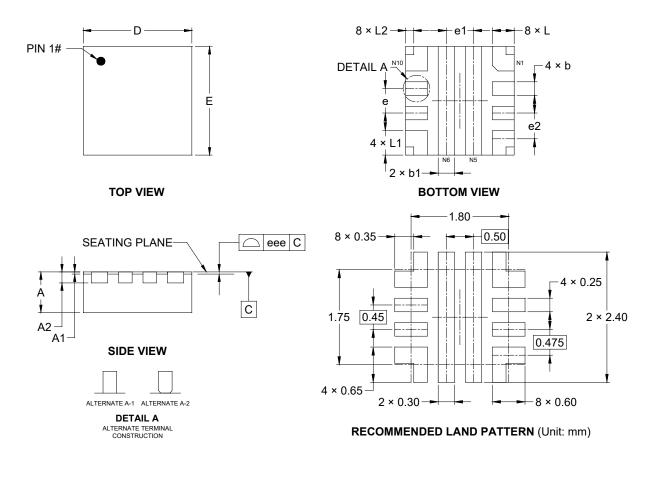

# PACKAGE OUTLINE DIMENSIONS TQFN-2×2-10L

| Symbol | Dimensions In Millimeters |     |       |  |  |  |

|--------|---------------------------|-----|-------|--|--|--|

| Symbol | MIN                       | NOM | МАХ   |  |  |  |

| A      | 0.700                     | -   | 0.800 |  |  |  |

| A1     | 0.000                     | -   | 0.050 |  |  |  |

| A2     | 0.203 REF                 |     |       |  |  |  |

| b      | 0.200                     | -   | 0.300 |  |  |  |

| b1     | 0.250                     | -   | 0.350 |  |  |  |

| D      | 1.900                     | -   | 2.100 |  |  |  |

| E      | 1.900                     | -   | 2.100 |  |  |  |

| е      | 0.450 BSC                 |     |       |  |  |  |

| e1     | 0.500 BSC                 |     |       |  |  |  |

| e2     | 0.475 BSC                 |     |       |  |  |  |

| L      | 0.300                     | -   | 0.500 |  |  |  |

| L1     | 0.350                     | -   | 0.550 |  |  |  |

| L2     | 0.150 REF                 |     |       |  |  |  |

| eee    | 0.080                     |     |       |  |  |  |

NOTE: This drawing is subject to change without notice.

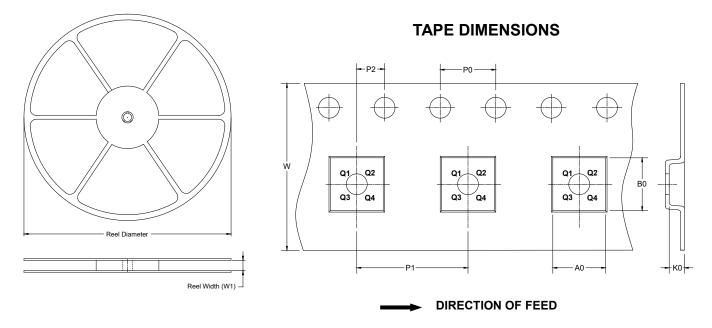

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-2×2-10L | 7"               | 9.5                      | 2.30       | 2.30       | 1.10       | 4.0        | 4.0        | 2.0        | 8.0       | Q2               |

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width Height<br>(mm) (mm) |     | Pizza/Carton |        |

|-------------|----------------|---------------------------|-----|--------------|--------|

| 7" (Option) | 368            | 227                       | 224 | 8            |        |

| 7"          | 442            | 410                       | 224 | 18           | DD0002 |