# SGM6514 16-Input, 8-Output Crosspoint Switch

### **GENERAL DESCRIPTION**

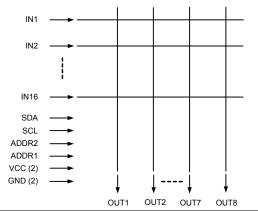

The SGM6514 crosspoint switch provides flexible options for applications. The 16 inputs can be routed to any of 8 outputs. Each input can be routed to one or more outputs, but only one input can be routed to any one output. More than one output can connect to the same input channel for one-to-many routing. The input to output routing is controlled via an I<sup>2</sup>C-compatible digital interface.

For analog signal switching application, 8 outputs can be 8 single outputs or 4 differential outputs depending on configuration. Crosspoint structure can reduce PCB complexity. For digital signal switching, SGM6514 supports up to 400kHz digital signal.

The resistance profile of SGM6514 is very flat over the full analog input range, ensuring excellent linearity and low distortion when switching audio signals. For video application, SGM6514 supports up to 1080p or VGA video.

The SGM6514 is available in Green LQFP-7×7-32L package. It operates over an ambient temperature range of -40°C to +85°C.

### **FEATURES**

- Supply Range: 2.7V to 5.5V

- 16 x 8 Crosspoint Switch

- One-to-One or One-to-Many Output Switching

- Supports Bidirectional Transmission

- I<sup>2</sup>C-Compatible Digital Interface, Standard Mode

- Supports WUXGA (1920 x 1200) Video

- Supports Low Noise Analog Signal Switching

- -3dB Bandwidth: 250MHz

- 1.8V Logic Control I/O

- Available in Green LQFP-7×7-32L Package

- Extended Industrial Temperature Range:

-40°C to +85°C

### **APPLICATIONS**

Video and Audio Matrix Switching System Audio and Video Receiver Automotive Entertainment System Data Acquisition and Control System

## **BLOCK DIAGRAM**

## PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKAGE<br>OPTION |

|---------|------------------------|-----------------------------------|--------------------|----------------------------|-------------------|

| SGM6514 | LQFP-7×7-32L           | -40℃ to +85℃                      | SGM6514YLFA32G/TY  | SGM6514<br>YLFA32<br>XXXXX | Tray, 250         |

NOTE: XXXXX = Date Code and Vendor Code.

### ABSOLUTE MAXIMUM RATINGS

| DC Supply Voltage                   |                |

|-------------------------------------|----------------|

| Analog and Digital I/O              |                |

| Continuous Current IN, OUT          | 10mA           |

| Storage Temperature Range           | 65°C to +150°C |

| Junction Temperature                | 150°C          |

| Operating Temperature Range         | 40°C to +85°C  |

| Lead Temperature (Soldering 10 sec) | 260°C          |

| ESD Susceptibility                  |                |

| HBM                                 | 7000V          |

| MM                                  | 300V           |

#### NOTE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

SGMICRO reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. Please contact SGMICRO sales office to get the latest datasheet.

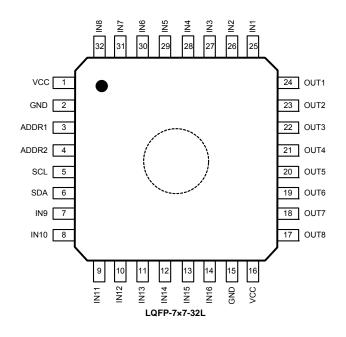

# PIN CONFIGURATION (TOP VIEW)

# I<sup>2</sup>C ADDRESS SELECTION TABLE

| ADDR2 | ADDR1 | I <sup>2</sup> C ADDRESS |

|-------|-------|--------------------------|

| 0 0   |       | 0x06 (0000 0110)         |

| 0     | 1     | 0x46 (0100 0110)         |

| 1     | 0     | 0x86 (1000 0110)         |

| 1     | 1     | 0xC6 (1100 0110)         |

# **PIN DESCRIPTION**

| PIN   | NAME  | DESCRIPTION                            |

|-------|-------|----------------------------------------|

| 1, 16 | VCC   | Positive Power Supply.                 |

| 2, 15 | GND   | Ground.                                |

| 3     | ADDR1 | Selects I <sup>2</sup> C Address.      |

| 4     | ADDR2 | Selects I <sup>2</sup> C Address.      |

| 5     | SCL   | Serial Clock for I <sup>2</sup> C Bus. |

| 6     | SDA   | Serial Data for I <sup>2</sup> C Bus.  |

| 7     | IN9   | Input. Channel 9.                      |

| 8     | IN10  | Input. Channel 10.                     |

| 9     | IN11  | Input. Channel 11.                     |

| 10    | IN12  | Input. Channel 12.                     |

| 11    | IN13  | Input. Channel 13.                     |

| 12    | IN14  | Input. Channel 14.                     |

| 13    | IN15  | Input. Channel 15.                     |

| 14    | IN16  | Input. Channel 16.                     |

| 17    | OUT8  | Output. Channel 8.                     |

| 18    | OUT7  | Output. Channel 7.                     |

| 19    | OUT6  | Output. Channel 6.                     |

| 20    | OUT5  | Output. Channel 5.                     |

| 21    | OUT4  | Output. Channel 4.                     |

| 22    | OUT3  | Output. Channel 3.                     |

| 23    | OUT2  | Output. Channel 2.                     |

| 24    | OUT1  | Output. Channel 1.                     |

| 25    | IN1   | Input. Channel 1.                      |

| 26    | IN2   | Input. Channel 2.                      |

| 27    | IN3   | Input. Channel 3.                      |

| 28    | IN4   | Input. Channel 4.                      |

| 29    | IN5   | Input. Channel 5.                      |

| 30    | IN6   | Input. Channel 6.                      |

| 31    | IN7   | Input. Channel 7.                      |

| 32    | IN8   | Input. Channel 8.                      |

# SGM6514

# **ELECTRICAL CHARACTERISTICS**

$(V_{CC}$  = +4.5V to +5.5V, Full = -40°C to +85°C. Typical values are at  $V_{CC}$  = +5.0V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                    | SYMBOL                | CONDITIONS                                                             | TEMP  | MIN | TYP | MAX             | UNITS |

|------------------------------|-----------------------|------------------------------------------------------------------------|-------|-----|-----|-----------------|-------|

| ANALOG SWITCH                |                       | •                                                                      | •     |     | •   | •               | •     |

| Analog Signal Range          | $V_{IN}, V_{OUT}$     |                                                                        | Full  | 0   |     | V <sub>CC</sub> | V     |

| On-Resistance                | Ron                   | $V_{CC} = 4.5V, \ 0V \le V_{IN} \le V_{CC},$                           | +25°C |     | 30  | 36              | Ω     |

| On-Resistance                | NON                   | $I_{OUT} = -10 \text{mA}$                                              | Full  |     |     | 42              | 1 12  |

| On-Resistance Match          | $\Delta R_ON$         | $V_{CC} = 4.5V, \ 0V \le V_{IN} \le V_{CC},$                           | +25°C |     | 4   | 7.2             | 0     |

| Between Channels             | ΔΚΟΝ                  | $I_{OUT} = -10 \text{mA}$                                              | Full  |     |     | 8.6             | 1 12  |

| On-Resistance Flatness       | D                     | $V_{CC} = 4.5V, \ 0V \le V_{IN} \le V_{CC},$                           | +25°C |     | 8   | 11.8            | 0     |

| On-Resistance Flatness       | R <sub>FLAT(ON)</sub> | I <sub>OUT</sub> = -10mA                                               | Full  |     |     | 12.5            | 1 12  |

| Source OFF Leakage Current   | I <sub>OFF</sub>      | $V_{CC} = 5.5V, V_{IN} = 4.5V/1V, V_{OUT} = 1V/4.5V$                   | Full  |     |     | 1               | μA    |

| Channel ON Leakage Current   | I <sub>ON</sub>       | $V_{CC} = 5.5V$ , $V_{OUT} = 1V/4.5V$ , $V_{IN} = 1V/4.5V$ or floating | Full  |     |     | 1               | μA    |

| Supply Current               | I <sub>CC</sub>       | V <sub>CC</sub> = 5.5V                                                 | Full  |     | 15  | 80              | μA    |

| DYNAMIC CHARACTERISTICS      |                       |                                                                        |       |     |     |                 |       |

| Break-Before-Make Time Delay | $t_D$                 | $V_{IN} = 3V, R_L = 50\Omega, C_L = 35pF$                              | +25°C |     | 7   |                 | ns    |

| Charge Injection             | Q                     | $V_G = GND, R_G = 0\Omega, C_L = 1.0nF,$<br>$Q = C_L \times V_{OUT}$   | +25°C |     | 7   |                 | pC    |

| -3dB Bandwidth               | BW                    | $V_{IN} = 1V_{PP}$                                                     | +25°C |     | 250 |                 | MHz   |

| Channel ON Capacitance       | C <sub>ON</sub>       | f = 1MHz                                                               | +25°C |     | 50  |                 | pF    |

| Digital Input Capacitance    | C <sub>DIN</sub>      | V <sub>CC</sub> = 5V                                                   | +25°C |     | 7   |                 | pF    |

# SGM6514

# **ELECTRICAL CHARACTERISTICS**

$(V_{CC}$  = +2.7V to +3.6V, Full = -40°C to +85°C. Typical values are at  $V_{CC}$  = +3.0V,  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                    | SYMBOL                | CONDITIONS                                                                   | TEMP  | MIN | TYP | MAX             | UNITS |

|------------------------------|-----------------------|------------------------------------------------------------------------------|-------|-----|-----|-----------------|-------|

| ANALOG SWITCH                |                       |                                                                              |       |     |     |                 |       |

| Analog Signal Range          | $V_{IN}, V_{OUT}$     |                                                                              | Full  | 0   |     | V <sub>CC</sub> | V     |

| On-Resistance                | Ron                   | $V_{CC} = 2.7V$ , $0V \le V_{IN} \le V_{CC}$ ,                               | +25°C |     | 65  | 84              | 0     |

| OII-Nesisiance               | NON                   | $I_{OUT} = -10mA$                                                            | Full  |     |     | 88              | 12    |

| On-Resistance Match          | ΔRon                  | $V_{CC} = 2.7V$ , $0V \le V_{IN} \le V_{CC}$ ,                               | +25°C |     | 4   | 9.6             | Ω     |

| Between Channels             | ΔΙΚΟΝ                 | I <sub>OUT</sub> = -10mA                                                     | Full  |     |     | 10.5            | 1 12  |

| On-Resistance Flatness       | D                     | $V_{CC} = 2.7V$ , $0V \le V_{IN} \le V_{CC}$ ,                               | +25°C |     | 35  | 50.5            | Ω     |

| On-Resistance Flatness       | R <sub>FLAT(ON)</sub> | I <sub>OUT</sub> = -10mA                                                     | Full  |     |     | 51              | 1 12  |

| Source OFF Leakage Current   | l <sub>OFF</sub>      | $V_{CC} = 3.6V, V_{IN} = 3.3V/0.3V, V_{OUT} = 0.3V/3.3V$                     | Full  |     |     | 1               | μA    |

| Channel ON Leakage Current   | I <sub>ON</sub>       | $V_{CC} = 3.6V, V_{OUT} = 0.3V/3.3V, V_{IN} = 0.3V/3.3V \text{ or floating}$ | Full  |     |     | 1               | μA    |

| Supply Current               | I <sub>CC</sub>       | V <sub>CC</sub> = 3.6V                                                       | Full  |     | 8   | 50              | μA    |

| DYNAMIC CHARACTERISTICS      |                       |                                                                              |       |     |     |                 |       |

| Break-Before-Make Time Delay | $t_D$                 | $V_{IN} = 1.5V$ , $R_L = 50\Omega$ , $C_L = 35pF$                            | +25°C |     | 10  |                 | ns    |

| Charge Injection             | Q                     | $V_G = GND, R_G = 0\Omega, C_L = 1.0nF,$<br>$Q = C_L \times V_{OUT}$         | +25°C |     | 3   |                 | рС    |

| -3dB Bandwidth               | BW                    | $V_{IN} = 1V_{PP}$                                                           | +25°C |     | 250 |                 | MHz   |

| Channel ON Capacitance       | C <sub>ON</sub>       | f = 1MHz                                                                     | +25°C |     | 50  |                 | pF    |

| Digital Input Capacitance    | C <sub>DIN</sub>      | V <sub>CC</sub> = 3V                                                         | +25°C |     | 7   |                 | pF    |

## DIGITAL INTERFACE

The  $I^2$ C-compatible interface is used to program output enables, and input to output routing. The  $I^2$ C address of the SGM6514 can be programmed to 0x06 (0000 0110) or 0x46(0100 0110) or 0x86(1000 0110) or 0xC6 (1100 0110) by connecting ADDR2, ADDR1 pin to "LOW" or "HIGH".

Both data and address data, of eight bits each, are written to the  $I^2C$  address to access all the control functions.

There are separate internal addresses for each output. Each output's address includes bits to select an input channel. More than one output can connect to the same input channel for one-to-many routing. When the outputs are disabled, they are placed in a high-impedance state. This allows multiple SGM6514 devices to be paralleled to create a larger switch matrix. Typical output power-up time is less than 500ns.

All undefined addresses may be written without effect.

### **Output Control Register Contents and Defaults**

| Control Name | Width  | Туре  | Default | Bit (s)   | Description                                                                                                           |

|--------------|--------|-------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------|

| INx          | 5 bits | Write | 0       | Bit4:Bit0 | Input selected to drive this output: 00000 = OFF, 00001 = IN1, 00010 = IN2,, 01100 = IN12,, 01111=IN15, 10000 = IN16. |

### **Output Control Register Map**

| Name | Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|---------|------|------|------|------|------|------|------|------|

| OUT1 | 0x01    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT2 | 0x02    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT3 | 0x03    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT4 | 0x04    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT5 | 0x05    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT6 | 0x06    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT7 | 0x07    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

| OUT8 | 0x08    | Х    | Х    | Х    | IN4  | IN3  | IN2  | IN1  | IN0  |

NOTE: "X" means "don't care".

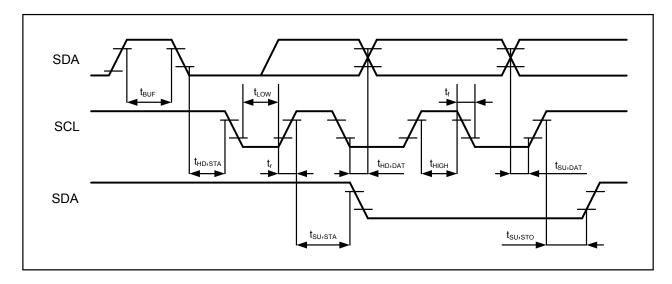

# I<sup>2</sup>C BUS CHARACTERISTICS

( $T_A$  = +25°C,  $V_{CC}$  = +5.0V, unless otherwise noted.)

| PARAMETER                                     | SYMBOL                           | CONDITIONS     | MIN | TYP  | MAX             | UNITS |

|-----------------------------------------------|----------------------------------|----------------|-----|------|-----------------|-------|

| Digital Input Low                             | V <sub>IL</sub>                  | SDA, SCL, ADDR | 0   |      | 0.6             | V     |

| Digital Input High                            | V <sub>IH</sub>                  | SDA, SCL, ADDR | 2.5 |      | V <sub>CC</sub> | V     |

| Clock Frequency                               | f <sub>SCL</sub>                 | SCL            |     | 100  |                 | kHz   |

| Input Rise Time                               | t <sub>r</sub>                   | 1.5V to 3V     |     | 1000 |                 | ns    |

| Input Fall Time                               | t <sub>f</sub>                   | 1.5V to 3V     |     | 300  |                 | ns    |

| Clock Low Period                              | $t_{LOW}$                        |                |     | 4.7  |                 | μs    |

| Clock High Period                             | t <sub>HIGH</sub>                |                |     | 4.0  |                 | μs    |

| Data Set-up Time                              | t <sub>SU</sub> , <sub>DAT</sub> |                |     | 300  |                 | ns    |

| Data Hold Time                                | t <sub>HD</sub> , <sub>DAT</sub> |                |     | 0    |                 | ns    |

| Set-up Time from Clock High to Stop           | t <sub>SU</sub> , <sub>STO</sub> |                |     | 4    |                 | μs    |

| Start Set-up Time Following a Stop            | t <sub>BUF</sub>                 |                |     | 4.7  |                 | μs    |

| Start Hold Time                               | t <sub>HD</sub> , STA            |                |     | 4    |                 | μs    |

| Start Set-up Time Following Clock Low to High | t <sub>SU</sub> , <sub>STA</sub> |                |     | 4.7  |                 | μs    |

Figure 1. I<sup>2</sup>C Bus Timing

## I<sup>2</sup>C INTERFACE

### Operation

The  $I^2C$ -compatible interface conforms to the  $I^2C$  specification for Standard Mode. Individual addresses may be written, but there is no read capability. The interface consists of two lines: a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply through an external resistor. Data transfer may be initiated only when the bus is not busy.

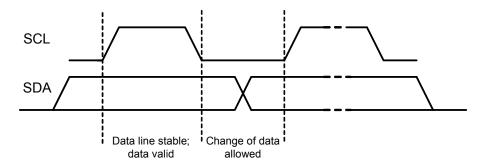

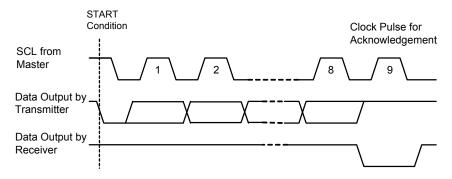

#### **Bit Transfer**

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse. Changes in the data line during this time are interpreted as control signals.

Figure 2. Bit Transfer

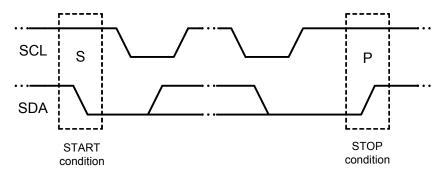

### **START and STOP Conditions**

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH, is defined as START condition (S).

A LOW-to-HIGH transition of the data line, while the clock is HIGH, is defined as STOP condition (P).

Figure 3. START and STOP Conditions

## I<sup>2</sup>C INTERFACE

### **Acknowledge**

The number of data bytes transferred between the START and STOP conditions from transmitter to receiver is unlimited. Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH level signal put on the bus by the transmitter while the master generates an extra acknowledge-related clock pulse. The slave receiver addressed must generate an acknowledge after the reception of each byte. A master receiver must generate an acknowledge after the reception of each byte clocked out of the slave transmitter.

The device that acknowledges must pull down the SDA line during the acknowledge clock pulse so the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Figure 4. Acknowledgement on the I<sup>2</sup>C Bus

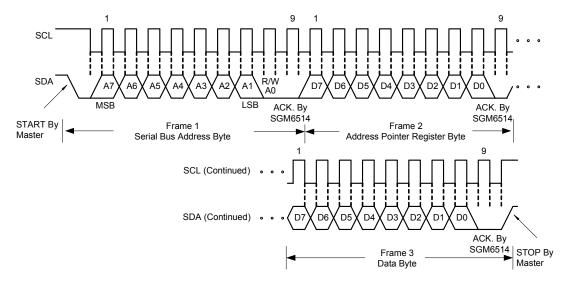

#### I<sup>2</sup>C Bus Protocol

Before any data is transmitted on the I<sup>2</sup>C bus, the device which is to respond is addressed first. The addressing is always carried out with the first byte transmitted after the start procedure. The I<sup>2</sup>C bus configuration for a data write to the SGM6514 is shown in Figure 5.

Figure 5. Write Register Address to Pointer Register; Write Data to Selected Register

## **APPLICATION NOTES**

### **Layout Considerations**

General layout and supply bypassing play a major role in high-frequency performance and thermal characteristics. SGMICRO offers a demonstration board to guide layout and aid device evaluation. The demo board is a four layers board with full power and ground planes. Following this layout configuration provides optimum performance and thermal characteristics for the device. For the best results, follow the steps and recommended routing rules listed below.

### **Recommended Routing/Layout Rules**

- Do not run analog and digital signals in parallel.

- Use separate analog and digital power planes to supply power.

- Traces should run on top of the ground plane at all times.

- No trace should run over ground/power splits.

- Avoid routing at 90-degree angles.

- Minimize clock and video data trace length differences.

- Include 10μF and 0.1μF ceramic power supply bypass capacitors.

- Place the 0.1µF capacitor within 0.1 inches of the device power pin.

- Place the 10µF capacitor within 0.75 inches of the device power pin.

- For multilayer boards, use a large ground plane to help dissipate heat.

- For two-layer boards, use a ground plane that extends beyond the device body by at least 0.5 inches on all sides. Include a metal paddle under the device on the top layer.

- Minimize all trace lengths to reduce series inductance.

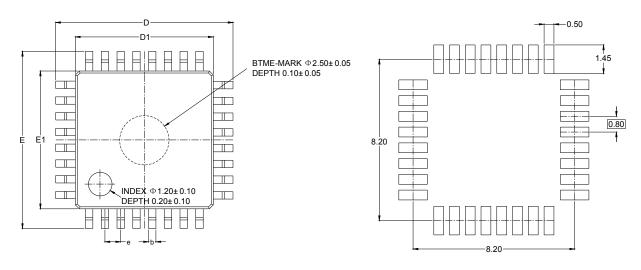

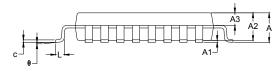

# **PACKAGE OUTLINE DIMENSIONS**

### LQFP-7×7-32L

**TOP VIEW**

RECOMMENDED LAND PATTERN (Unit: mm)

SIDE VIEW

| Symbol | Dir  | mensions In Millimet | ers  |

|--------|------|----------------------|------|

| Symbol | MIN  | MOD                  | MAX  |

| А      |      |                      | 1.60 |

| A1     | 0.05 |                      | 0.15 |

| A2     | 1.35 | 1.40                 | 1.45 |

| A3     | 0.59 | 0.64                 | 0.69 |

| b      | 0.32 |                      | 0.43 |

| С      | 0.13 |                      | 0.18 |

| D      | 8.80 | 9.00                 | 9.20 |

| D1     | 6.90 | 7.00                 | 7.10 |

| E      | 8.80 | 9.00                 | 9.20 |

| E1     | 6.90 | 7.00                 | 7.10 |

| е      |      | 0.80 BSC             |      |

| L      | 0.45 | 0.60                 | 0.75 |

| θ      | 0°   | 3.5°                 | 7°   |

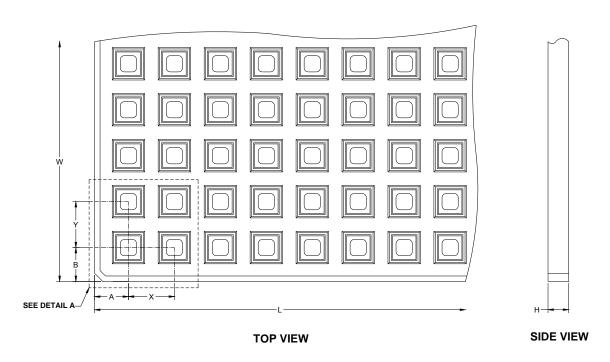

# **TRAY INFORMATION**

Pin 1 is closest to the chamfered corner of the tray.

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF TRAY**

| Package Type | A<br>(mm) | B<br>(mm) | X<br>(mm) | Y<br>(mm) | L<br>(mm) | W<br>(mm) | H<br>(mm) | Devices/Tray |

|--------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--------------|

| LQFP-7×7-32L | 11.10     | 11.25     | 12.20     | 12.60     | 322.6     | 135.9     | 7.6       | 250          |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Packing Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Inner Box/Carton | Tray/Inner Box |

|--------------|----------------|---------------|----------------|------------------|----------------|

| Tray         | 560            | 375           | 180            | 6                | 2              |