# SGM864S 4-Channel Adjustable Power Supply Sequencer

### **GENERAL DESCRIPTION**

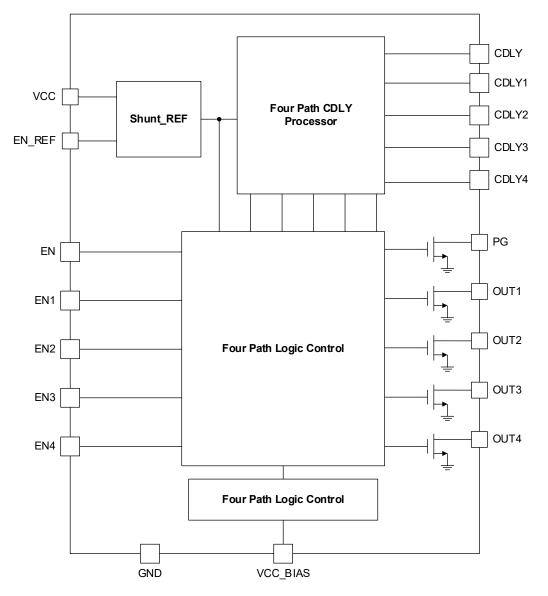

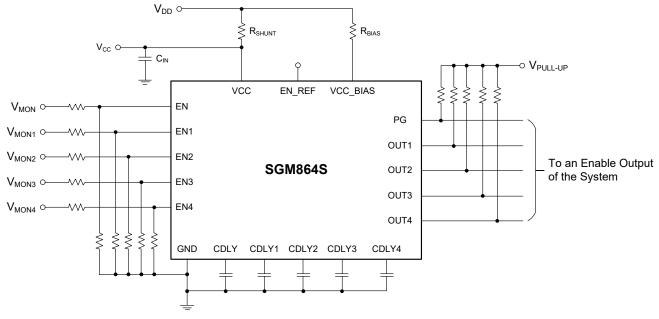

The SGM864S is an integrated, 4-rail power sequencer. It controls the power-up and power-down sequence of four power supplies by pulling their enable or shutdown pins high or low. Staggered start sequence can avoid the impact of latch conditions or large inrush current on system reliability.

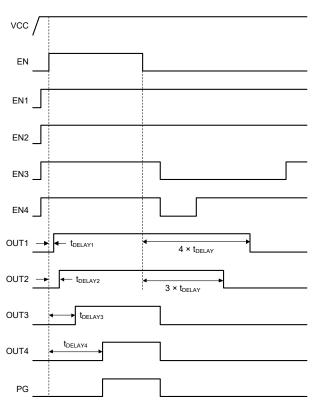

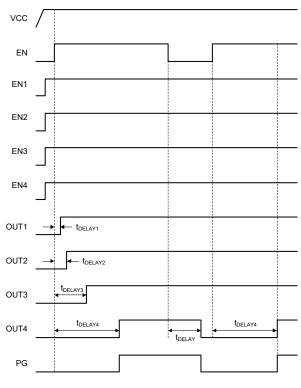

The device has five open-drain outputs that are controled by five enable pins. When the EN pin is pulled high and the ENx pin is high, each of the four outputs (OUT1 to OUT4) is released after a fixed delay time, which can be adjusted by the NP0 capacitor outside the CDLYx pin. When EN remains high and any ENx is pulled low, the OUTx will be shut down correspondingly. When ENx remains high and EN is pulled low, the outputs are pulled low in reverse order (from OUT4 to OUT1) after CDLY programmable delay time. If the four OUTx all output high, the PG pin outputs high.

The SGM864S also includes an internal clamp voltage regulator that stabilizes the internal reference voltage at 5V with an accuracy of  $\pm 2.6\%$  by using shunt resistors (R<sub>SHUNT</sub>) on VCC. The maximum external supply voltage (V<sub>DD</sub>) is 22V. The total value of the capacitor (C<sub>IN</sub>) pulled down to GND should be limited to between 1µF and 10µF. When V<sub>CC</sub> is 2V to 5.5V, set EN\_REF to high or connect it to VCC, then the shunt voltage reference is disabled. VCC does not require any external resistor. Once V<sub>CC</sub> rises above 6V, the shunt voltage reference is enabled. Set EN\_REF to low or keep it floating (a 500kΩ built-in resistor). VCC requires the shunt resistors of 130Ω to 40kΩ.

The SGM864S is available in a Green TQFN- $3.5 \times 3.5$ -20L package. It operates over a junction temperature range of -40°C to +125°C.

### FEATURES

- Sequence Four Voltage Rails

- Input Voltage Range: 2V to 5.5V

- Shunt Voltage Reference: 5V (±2.6% Accuracy)

- EN and ENx Threshold Voltage: 1.23V (TYP)

- Hysteresis: ≥ 0.2V

- Low Quiescent Current: 55µA (TYP)

- Capacitor-Adjustable Delay Time

- External Power Supply by VCC when Shunt Voltage Reference is Enabled: 15mA (MAX)

- Sequence Controlled by ENx and CDLYx Pins

- Power Good Function

- Open-Drain OUTx Outputs

- Available in a Green TQFN-3.5×3.5-20L Package

### **APPLICATIONS**

Communication Equipment Enterprise Servers 5G Wireless Product DC/DC Converters Power Inverter

### **PACKAGE/ORDERING INFORMATION**

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING     | PACKING<br>OPTION   |

|---------|------------------------|-----------------------------------|--------------------|------------------------|---------------------|

| SGM864S | TQFN-3.5×3.5-20L       | -40°C to +125°C                   | SGM864SXTRL20G/TR  | 0NJ<br>XTRL20<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

XXXXX

Vendor Code

Trace Code

— Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage, V <sub>CC</sub>        | 0.3V to 6V     |

|---------------------------------------|----------------|

| EN, ENx Voltages                      |                |

| OUTx Voltage                          |                |

| Input Current                         |                |

| Package Thermal Resistance            |                |

| TQFN-3.5×3.5-20L, θ <sub>JA</sub>     | 41.6°C/W       |

| TQFN-3.5×3.5-20L, θ <sub>JB</sub>     | 18.9°C/W       |

| TQFN-3.5×3.5-20L, θ <sub>JC_TOP</sub> |                |

| TQFN-3.5×3.5-20L, θ <sub>JC_BOT</sub> | 6.5°C/W        |

| Junction Temperature                  |                |

| Storage Temperature Range             | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)     | +260°C         |

| ESD Susceptibility                    |                |

| НВМ                                   |                |

| CDM                                   | 1000V          |

#### **RECOMMENDED OPERATING CONDITIONS**

| Input Voltage, V <sub>CC</sub>                     | 2V to 5.5V     |

|----------------------------------------------------|----------------|

| Shunt Resistor, R <sub>SHUNT</sub> <sup>(1)</sup>  | 130Ω to 40kΩ   |

| Delay Capacitor, C <sub>DELAY</sub> <sup>(2)</sup> | 100nF (MAX)    |

| Total Capacitor on VCC, CIN                        | 1µF to 10µF    |

| Pull-up Resistor, R <sub>PULL-UP</sub>             | 10kΩ to 100kΩ  |

| Operating Junction Temperature Range               | 40°C to +125°C |

#### NOTES:

1. R<sub>SHUNT</sub> should be power resistor.

2. C<sub>DELAY</sub> should be NP0 capacitor.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

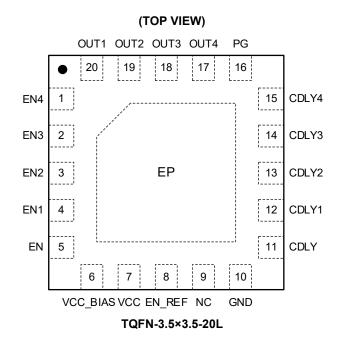

## **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1   | EN4      | Voltage Rail 4 Enable Pin. 1.23V Threshold Volta                                                                                                                                                                                                                                                                                   | Voltage Rail 4 Enable Pin. 1.23V Threshold Voltage. A 500k $\Omega$ pull-down resistor is internally set.                                                                                |  |  |  |  |  |  |  |  |

| 2   | EN3      | Voltage Rail 3 Enable Pin. 1.23V Threshold Voltage. A 500k $\Omega$ pull-down resistor is internally set.                                                                                                                                                                                                                          |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 3   | EN2      | Voltage Rail 2 Enable Pin. 1.23V Threshold Volta                                                                                                                                                                                                                                                                                   | Voltage Rail 2 Enable Pin. 1.23V Threshold Voltage. A 500k $\Omega$ pull-down resistor is internally set.                                                                                |  |  |  |  |  |  |  |  |

| 4   | EN1      | Voltage Rail 1 Enable Pin. 1.23V Threshold Volta                                                                                                                                                                                                                                                                                   | Voltage Rail 1 Enable Pin. 1.23V Threshold Voltage. A 500kΩ pull-down resistor is internally set.                                                                                        |  |  |  |  |  |  |  |  |

| 5   | EN       | ENx Controlled Pin. The ENx input flitering time is 600ns (TYP). If EN is set high (EN = 1), the ENx asserts after an adjustable CDLYx time. If EN is low (EN = 0), the OUTx asserts in reverse order from OUT4 to OUT1). 1.23V threshold voltage. A $500k\Omega$ pull-down resistor is internally set.                            |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 6   | VCC_BIAS | Low-Level Output Confirmed Pin. Connect a 1M                                                                                                                                                                                                                                                                                       | ow-Level Output Confirmed Pin. Connect a $1M\Omega$ to $10M\Omega$ resistor to the external power supply.<br>'he maximum current consumption flowing through this resistor is $22\mu$ A. |  |  |  |  |  |  |  |  |

| 7   | VCC      | V to 5.5V Supply Voltage. If $V_{DD}$ is higher than 6V, VCC has the drive capability to provide current xternally and stabilizes the internal reference voltage at 5V.                                                                                                                                                            |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 8   | EN_REF   | Active-Low Enable Input Pin. Pulling this pin logic low or keeping it floating enables the shunt voltage reference. Pulling this pin logic high or connecting it to VCC disables the shunt voltage eference. Use this pin to adjust the VCC shunt voltage reference to 5V. And a $500k\Omega$ pull-down esistor is internally set. |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 9   | NC       | No Connection. It is recommended to connect it to GND.                                                                                                                                                                                                                                                                             |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 10  | GND      | Ground.                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 11  | CDLY     | Connecting an NP0 capacitor (100nF, MAX) between this pin and GND to select the programmable delay time. See Table 1 for more details.                                                                                                                                                                                             |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 12  | CDLY1    |                                                                                                                                                                                                                                                                                                                                    | Capacitor-Adjustable Delay Pin for EN1.                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 13  | CDLY2    | Connecting an NP0 capacitor (100nF, MAX)                                                                                                                                                                                                                                                                                           | Capacitor-Adjustable Delay Pin for EN2.                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 14  | CDLY3    | between this pin and GND to select the programmable delay time.                                                                                                                                                                                                                                                                    | Capacitor-Adjustable Delay Pin for EN3.                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 15  | CDLY4    |                                                                                                                                                                                                                                                                                                                                    | Capacitor-Adjustable Delay Pin for EN4.                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 16  | PG       | Power Good Open-Drain Output. If the four OUT<br>OUTx outputs low, the PG pin outputs low. Before<br>from OUTx, and the equivalent impedance of the                                                                                                                                                                                | e the VCC rises to 1V, Pull up a resistor of $10k\Omega$                                                                                                                                 |  |  |  |  |  |  |  |  |

| 17  | OUT4     |                                                                                                                                                                                                                                                                                                                                    | OUT4 is the output for EN4.                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 18  | OUT3     | Active-High Open-Drain Output Pin. Before the VCC rises to 1V, Pull up a resistor of $10k\Omega$ from                                                                                                                                                                                                                              | OUT3 is the output for EN3.                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 19  | OUT2     | OUTx, and the equivalent impedance of the OUTx to GND is $1k\Omega$ .                                                                                                                                                                                                                                                              | OUT2 is the output for EN2.                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 20  | OUT1     |                                                                                                                                                                                                                                                                                                                                    | OUT1 is the output for EN1.                                                                                                                                                              |  |  |  |  |  |  |  |  |

|     | EP       | Exposed Pad.                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 2V to 5.5V,  $T_J$  = -40°C to +125°C, typical values are measured at V<sub>CC</sub> = 5V and  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                    | SYMBOL                                                | CONDITIONS                                | MIN                   | TYP  | MAX                 | UNITS |

|----------------------------------------------|-------------------------------------------------------|-------------------------------------------|-----------------------|------|---------------------|-------|

| Supply                                       | L                                                     | •                                         |                       |      |                     |       |

| Operating Voltage Range                      | V <sub>cc</sub>                                       |                                           | 2                     |      | 5.5                 | V     |

| Under-Voltage Lockout Threshold              | V <sub>UVLO</sub>                                     | V <sub>cc</sub> falling                   | 1.51                  | 1.57 | 1.64                | V     |

| Under-Voltage Lockout Hysteresis             | V <sub>UVLO_HYS</sub>                                 | V <sub>cc</sub> rising                    | 170                   | 230  | 280                 | mV    |

| V <sub>CC</sub> Supply Current               | I <sub>cc</sub>                                       |                                           |                       | 55   | 110                 | μA    |

| V <sub>cc</sub> Shunt Voltage                |                                                       |                                           |                       | 5    |                     | V     |

| Accuracy on VCC                              |                                                       |                                           | -2.6                  |      | 2.6                 | %     |

| EN/ENx                                       |                                                       |                                           |                       |      | -                   |       |

| High-Level Input Voltage                     | $V_{\text{EN}_{\text{H}}}, V_{\text{ENx}_{\text{H}}}$ | t <sub>F</sub> = 600ns                    | 1.18                  | 1.23 | 1.28                | V     |

| Low-Level Input Voltage                      | $V_{\text{EN}_{L}}, V_{\text{ENx}_{L}}$               |                                           | 0.97                  | 1.01 | 1.05                | V     |

| EN_REF                                       |                                                       |                                           |                       |      | -                   |       |

| EN_REF Low-Level Input Voltage               | V <sub>IL</sub>                                       |                                           |                       |      | $0.3 \times V_{CC}$ | V     |

| EN_REF High-Level Input Voltage              | VIH                                                   |                                           | 0.7 × V <sub>CC</sub> |      |                     | V     |

| CDLY/CDLYx                                   |                                                       |                                           |                       |      |                     |       |

| Charging Current                             | I <sub>CDELAY</sub>                                   |                                           |                       | 2    |                     | μA    |

| Threshold Voltage                            |                                                       |                                           |                       | 750  |                     | mV    |

| Oscillator Power Consumption                 |                                                       | $V_{\rm CC} = 5V^{(1)}$                   |                       | 110  | 220                 | μA    |

| Parasitic Capacitance                        | ΔC                                                    |                                           |                       | 4    |                     | pF    |

| OUT/OUTx                                     |                                                       |                                           |                       |      |                     |       |

| Output Low Voltage                           | V <sub>OL</sub>                                       | I <sub>SINK</sub> = 3mA                   |                       |      | 0.2                 | V     |

| Output Open-Drain Leakage Current            | I <sub>LKG</sub>                                      |                                           |                       |      | 0.5                 | μA    |

| OUT/OUTx Pull-Down Resistance <sup>(2)</sup> | R <sub>OUTx</sub>                                     | $R_{PULL-UP} = 10k\Omega, V_{CC} = 600mV$ |                       | 1    |                     | kΩ    |

| Switching                                    |                                                       |                                           |                       |      |                     |       |

| Adjustable Delay Time                        | t <sub>D</sub>                                        |                                           |                       |      | 1.5                 | s     |

| Adjustable Delay Time Accuracy               |                                                       | After 2ms delay                           | -11                   |      | 11                  | %     |

| EN Input Filtering Time                      | t <sub>F</sub>                                        |                                           | 100                   | 600  | 1200                | ns    |

NOTES:

1. When  $V_{CC}$  is 5V, all four channels are in the judge process (the CDLY oscillator is on for each channel).

2. Connect a 10k $\Omega$  pull-up resistor to OUTx. At the worst corner, the 1k $\Omega$  (TYP) pull-down resistor is provided by V<sub>CC</sub> = 750mV.

## SGM864S

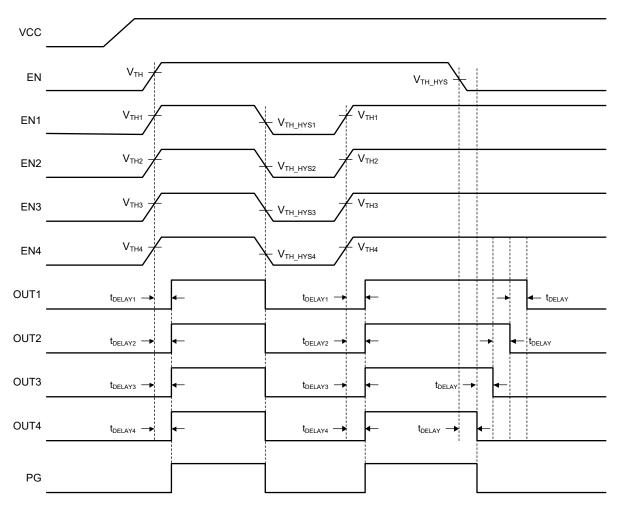

### TIMING DIAGRAM

Figure 1. Timing Diagram

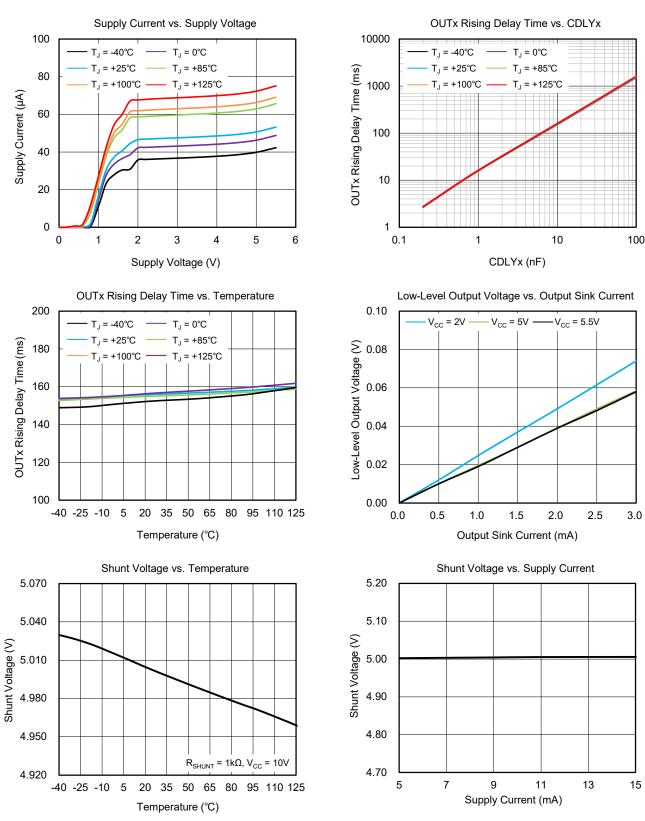

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_J$  = +25°C and V<sub>CC</sub> = 5V, unless otherwise noted.

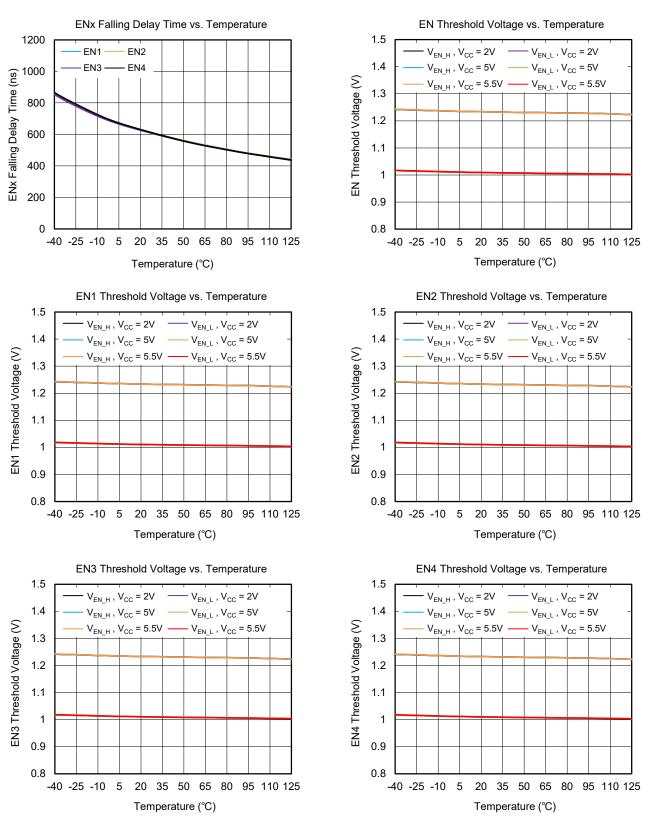

### **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_J$  = +25°C and  $V_{CC}$  = 5V, unless otherwise noted.

### FUNCTIONAL BLOCK DIAGRAM

Figure 2. Block Diagram

# DETAILED DESCRIPTION

The SGM864S is an integrated, 4-rail power sequencer. It controls the power-up and power-down sequence of four power supplies by pulling their enable or shutdown pins high or low. Staggered start sequence can avoid the impact of latch conditions or large inrush current on system reliability. The integrated Shunt\_REF function can stabilize the VCC at 5V with ±2.6% accuracy, and with different R<sub>SHUNT</sub> options, the VCC can provide a maximum drive capacity of 15mA for external devices.

#### **Voltage Monitoring**

The SGM864S can be used for voltage detection. With an external resistance divider, any voltage threshold above 1.23V can be monitored by each ENx (x = 1, 2, 3, 4) pin. EN is used as an enable signal for the four channels of ENx. ENx can only determine the voltage of each channel when the voltage of EN exceeds 1.23V. And the four ENx channels trigger reset independently of each other. It is also possible to directly monitor the status of the target source through direct access to EN/ENx. The SGM864S supports a wide range of voltage threshold detection and adjustable power-up and power-down delay times, making it suitable for a lot of applications.

#### Output

In the typical application of the SGM864S, users can connect the OUTx/PG pin to the devices such as DSPS, ASIC, FPGA and CPU as a reset input pin, or connect it to DC/DC converter and LDO regulator as an enable input signal.

The outputs of SGM864S are open-drain structure and pull-up resistors are needed to hold the lines high if OUTx/PG is not asserted. The OUTx/PG can be connected to other devices at correct voltage level by connecting the pull-up resistor to the proper voltage rails. Choose the pull-up resistor larger than  $10k\Omega$  for the safe operation of output transistors. Any combination of OUTx/PG can be combined into one logic signal with the wire-OR logic.

#### **Delay Time and Power-Off Delay Time**

When the EN pin is pulled high and the ENx pin is high, each of the four outputs (OUT1 to OUT4) is released after a fixed delay time, which can be adjusted by the NP0 capacitor outside the CDLYx pin. Each channel of ENx can be individually programmed with a delay time by the corresponding CDLYx, and the delay time of each channel is expressed by Equation 1.

$$\begin{split} t_{\text{DELAY}} &= \frac{\left(C_{\text{DELAY}} + \Delta C\right) \times 0.75 \times 40}{2 \times 10^{-6}} \\ &= 1.5 \times \left(C_{\text{DELAY}} + \Delta C\right) \times 10^{7} \end{split} \tag{1}$$

where:

1.5 is the time constant.

$\Delta C$  is the parasitic capacitance of 4pF (TYP).

Note that the maximum value of  $C_{\text{DELAY}}$  is 100nF, and its temperature coefficient should be PPM level. The delay accuracy is considered only when  $t_{\text{DELAY}}$  exceeds 2ms.

Table 1 shows the examples of four delay times programmed by four typical NP0 capacitors.

Table 1. Different Delay Times Programmed by CDELAY

| C <sub>DELAY</sub> (nF) | I <sub>SOURCE</sub> (μΑ), TYP | t <sub>DELAY</sub> (ms) |

|-------------------------|-------------------------------|-------------------------|

| 0.15                    | 2                             | 2.25                    |

| 0.68                    | 2                             | 10.2                    |

| 1                       | 2                             | 15                      |

| 2.2                     | 2                             | 33                      |

When the ENx is high and EN pin is pulled down, the outputs are asserted with a reverse sequence from OUT4 to OUT1 after CDLYx programmable delay time. The EN pin controls the falling sequence of OUTx. The falling delay time is programmed by a capacitor connected to CDLY. The delay time of each channel is also expressed by Equation 1.

#### **Power-Down Sequence Priority**

When EN becomes low and ENx remains high, the power-down sequence will execute. During the process of reverse power-down of OUTx, if ENx becomes low, the corresponding OUTx will be asserted immediately, while the OUTx corresponding to the high ENx will still maintain the original power-down delay time (Figure 4).

When EN becomes low and ENx remains high, the power-down sequence will execute. During the process of reverse power-down of OUTx, if the EN returns to high again, the asserted OUTx will be released again with a CDLYx time, and the OUTx that has not yet been asserted will remain in the released state (Figure 5).

## **DETAILED DESCRIPTION (Continued)**

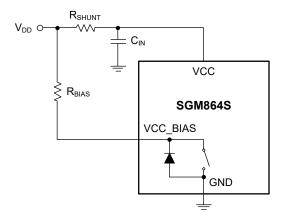

#### **VCC\_Bias Function**

When the EN\_REF pin of the SGM864S is low or floating, the shunt REF function is enabled. When the external supply voltage  $V_{DD}$  is powered on quickly, the internal VCC will be set up very slowly due to  $R_{SHUNT}$  and  $C_{IN}$ , which will result in the OUTx and PG not providing a strong enough pull-down capability for a long time. At this time, an external resistor of 1M $\Omega$  to 10M $\Omega$  can be connected between VCC\_BIAS and the external power supply, which is used for current limiting. The rapid establishment of VCC\_BIAS provides a fast pull-down capability for OUTx and PG, thus ensuring the determined output states for the OUTx and PG.

A brief description of the VCC\_BIAS function is shown below. Before the internal VCC is built up, VCC\_BIAS will be clamped up to a maximum of 1.9V. A current of  $(V_{DD} - 1.9V)/R_{BIAS}$  will flow into the diode inside of the SGM864S. After the internal VCC is built up, the internal logic circuit pulls the voltage of the VCC\_BIAS down to GND. A current of  $V_{DD}/R_{BIAS}$  will flow into the the SGM864S.

Figure 3. VCC\_Bias Function Diagram

### **APPLICATION INFORMATION**

### **Typical Application**

Figure 6. Typical Application Circuit

#### **Application Guidelines**

When the Shunt\_REF function is enabled and the  $R_{SHUNT}$  is greater than 500 $\Omega$ , the EN and ENx voltages are all above the rising thresholds of EN and ENx ( $V_{EN_{L}H}$ ,  $V_{EN_{X}H}$ ) before SGM864S is powered on and stabilized, it is recommended that the user set the external supply voltage ( $V_{DD}$ ) above the safe voltage ( $V_{SOA}$ ) within 1ms, to ensure the normal establishment of the VCC during the power-up process. Otherwise, the power consumption will increase due to premature triggering of the internal CDLY oscillator, which will lower the VCC and trigger UVLO locking during the power-on process, resulting in oscillations near the UVLO during the VCC power-on process. See Table 2 for more details.

When EN\_REF is low, and  $V_{\text{DD}}$  is above 6V, the VCC has the drive capability to provide current externally

and stabilizes the internal reference voltage at 5V. Use Equation 2 to caculate the current flowing through the shunt resistor.

$$I_{L} = \frac{V_{DD} - 5V}{R_{SHUNT}} - I_{CC_MAX}$$

(2)

where:

$I_L$  is the drive current provided by VCC.

$I_{\text{CC}\ \text{MAX}}$  is the maximum current consumption of the IC.

If users want to obtain the maximum drive current ( $I_{L_MAX}$ ) provided by VCC under different application situations, set  $R_{SHUNT} = 130\Omega$ ,  $V_{DD} = 7V$ , or  $R_{SHUNT} = 800\Omega$ ,  $V_{DD} = 17V$ ,  $I_L = I_{L_MAX} = 15mA$ , or  $R_{SHUNT} = 1k\Omega$ ,  $V_{DD} = 20V$ .

| V <sub>DD</sub> (V) | Shunt Resistor<br>R <sub>SHUNT</sub> (kΩ) | EN_REF State | Total Capacitance<br>on VCC, C <sub>IN</sub> (μF) | $\mathbf{V}_{\text{SOA}}$ | Recommended Values                                   | Recommended Values<br>at I <sub>L_MAX</sub> = 15mA |

|---------------------|-------------------------------------------|--------------|---------------------------------------------------|---------------------------|------------------------------------------------------|----------------------------------------------------|

| 2V to 5.5V          | -                                         | High         | 1μF to 10μF                                       | NA                        | C <sub>IN</sub> = 2.2μF                              | -                                                  |

| 4.5V to 7V          | 130Ω to 5kΩ                               | Low/Floating | 1μF to 10μF                                       | 2.8V                      | $R_{SHUNT}$ = 500 $\Omega$ , $C_{IN}$ = 2.2 $\mu$ F  | $R_{SHUNT}$ = 130 $\Omega$ , $V_{DD}$ = 7V         |

| 7V to 17V           | 800Ω to 10kΩ                              | Low/Floating | 1μF to 10μF                                       | 3.8V                      | $R_{SHUNT}$ = 1.5k $\Omega$ , $C_{IN}$ = 2.2 $\mu$ F | $R_{SHUNT}$ = 800 $\Omega$ , $V_{DD}$ = 17V        |

| 17V to 22V          | 1kΩ to 40kΩ                               | Low/Floating | 1μF to 10μF                                       | 8.8V                      | $R_{SHUNT}$ = 5k $\Omega$ , $C_{IN}$ = 2.2 $\mu$ F   | $R_{SHUNT}$ = 1k $\Omega$ , $V_{DD}$ = 20V         |

#### Table 2. Design Parameters

### **APPLICATION INFORMATION (Continued)**

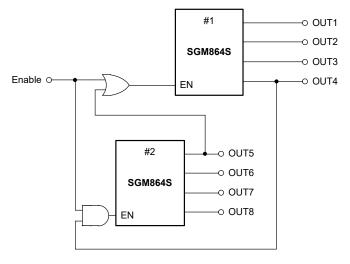

### **Cascade Application**

Figure 7. SGM864S Cascade Circuit

#### **Layout Guidelines**

Some guidelines are given below to prepare the layout of the PCB for SGM864S.

- CDLY/CDLYx pins routing should be as short as possible to improve accuracy and require shielding treatment.

- 2) Take short traces from EN/ENx to the resistor divider and long traces from RsxH to VMONX.

- Connect the VCC capacitor as close as possible to the device.

- 4) Use short traces to connect VCC. The parasitic inductance from the supply to the capacitor and the capacitor at VCC form an LC tank and may lead to ring voltages that higher than the maximum allowed VCC voltage.

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (APRIL 2024) to REV.A

Changed from product preview to production data.....

Page

..... All

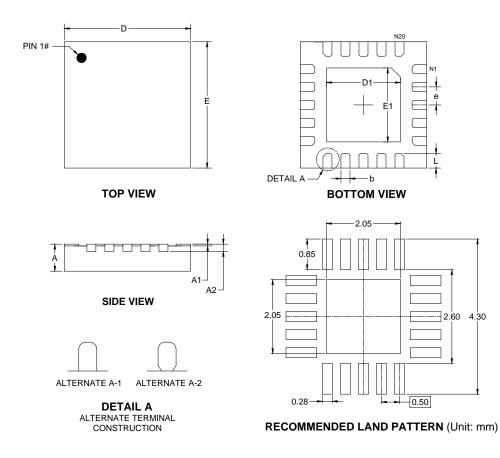

## PACKAGE OUTLINE DIMENSIONS

### TQFN-3.5×3.5-20L

| Symbol | Dimensions In Millimeters |       |       |  |  |  |  |

|--------|---------------------------|-------|-------|--|--|--|--|

|        | MIN                       | MOD   | МАХ   |  |  |  |  |

| A      | 0.700                     | 0.750 | 0.800 |  |  |  |  |

| A1     | -                         | -     | 0.050 |  |  |  |  |

| A2     | 0.203 REF                 |       |       |  |  |  |  |

| D      | 3.450 3.500               |       | 3.550 |  |  |  |  |

| D1     | 2.000                     | 2.050 | 2.100 |  |  |  |  |

| E      | 3.450 3.500               |       | 3.550 |  |  |  |  |

| E1     | 2.000                     | 2.050 | 2.100 |  |  |  |  |

| b      | 0.200                     | 0.250 | 0.300 |  |  |  |  |

| е      | 0.500 BSC                 |       |       |  |  |  |  |

| L      | 0.350                     | 0.450 |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

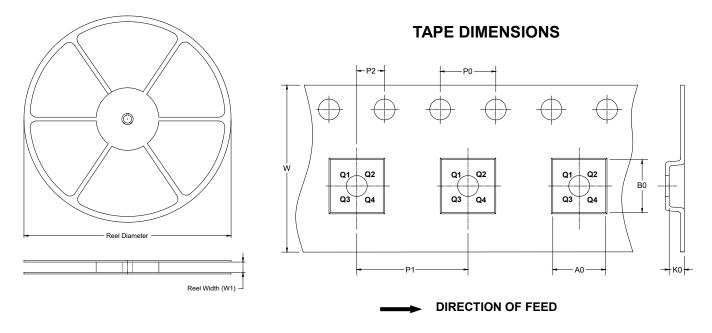

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type     | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-3.5×3.5-20L | 13"              | 12.4                     | 3.80       | 3.80       | 0.95       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

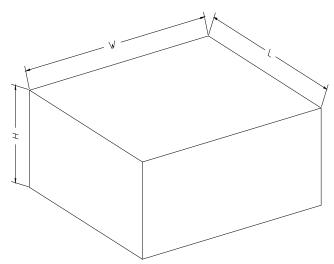

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |