The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

Hardware Manua

# SH7618 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family / SH7618 Series

> SH7618 SH7618A

HD6417618 HD6417618A

Rev.6.00 Revision Date: Jun. 12, 2007

Rancsassechurlagy www.renesas.com

www.DataSheet4U.com

Rev. 6.00 Jun. 12, 2007 Page ii of xxxii

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- www.DataSh6at When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

RENESAS

www.DataSheet4U.com

Rev. 6.00 Jun. 12, 2007 Page iii of xxxii

www.DataSheet4U.com

Rev. 6.00 Jun. 12, 2007 Page iv of xxxii

#### **General Precautions on Handling of Product**

- 1. Treatment of NC Pins

- Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

- 2. Treatment of Unused Input Pins

- Note: Fix all unused input pins to high or low level. Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

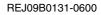

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

- 4. Prohibition of Access to Undefined or Reserved Addresses

- Note: Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

www.DataSheet4U.com Rev. 6.00 Jun. 12, 2007 Page v of xxxii

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the www.DataSmodule.However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

# Preface

The SH7618 Group RISC (Reduced Instruction Set Computer) microcomputers include a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

- Target Users: This manual was written for users who will use the SH7618 and SH7618A in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the SH7618 and SH7618A to the target users. Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed description of the instruction set.

www.DataSheet4U.com Notes on reading this manual:

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the SH-1/SH-2/SH-DSP Software Manual.

- In order to understand the details of a register when its name is known

- The addresses, bits, and initial values of the registers are summarized in section 20, List of Registers.

| Examples: | Register name:   | The following notation is used for cases when the same or a similar function, e.g. 16-bit timer pulse unit or serial communication interface, is implemented on more than one channel:<br>XXX_N (XXX is the register name and N is the channel number) |

|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Bit order:       | The MSB is on the left and the LSB is on the right.                                                                                                                                                                                                    |

|           | Number notation: | Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.                                                                                                                                                                                              |

|           | Signal notation: | An overbar is added to a low-active signal: $\overline{xxxx}$                                                                                                                                                                                          |

Related Manuals: The latest versions of all related manuals are available from our web site. Please ensure you have the latest versions of all documents you require. http://www.renesas.com/

www.DataSheet4U.com

Rev. 6.00 Jun. 12, 2007 Page vii of xxxii

#### SH7618 Group manuals:

| Document Title                   | Document No. |

|----------------------------------|--------------|

| SH7618 Group Hardware Manual     | This manual  |

| SH-1/SH-2/SH-DSP Software Manual | REJ09B0171   |

User's manuals for development tools:

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10B0152 |

|----------------------------------------------------------------------------------------------------|------------|

|                                                                                                    |            |

| SuperH RISC engine High-performance Embedded Workshop 3 User's Manual                              | REJ10B0025 |

| SuperH RISC engine High-performance Embedded Workshop 3 Tutorial                                   | REJ10B0023 |

Application note:

| Document Title                    | Document No. |

|-----------------------------------|--------------|

| SuperH RISC engine C/C++ Compiler | REJ05B0463   |

All trademarks and registered trademarks are the property of their respective owners.

www.DataSheet4U.com Rev. 6.00 Jun. 12, 2007 Page ix of xxxii

# Contents

| Sect | ion 1 C         | Overview                        | 1  |

|------|-----------------|---------------------------------|----|

| 1.1  | Feature         | es                              | 2  |

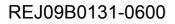

| 1.2  | Block           | Diagram                         | 6  |

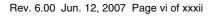

| 1.3  | Pin As          | signments                       | 7  |

| 1.4  | Pin Fu          | nctions                         | 8  |

| Sect | ion 2 C         | CPU                             | 19 |

| 2.1  | Feature         | es                              | 19 |

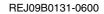

| 2.2  | Registe         | er Configuration                | 19 |

|      | 2.2.1           | General Registers (Rn)          | 21 |

|      | 2.2.2           | Control Registers               |    |

|      | $2.2.3^{\circ}$ | <sup>m</sup> System Registers   |    |

|      | 2.2.4           | Initial Values of Registers     |    |

| 2.3  | Data F          | ormats                          |    |

|      | 2.3.1           | Register Data Format            |    |

|      | 2.3.2           | Memory Data Formats             |    |

|      | 2.3.3           | Immediate Data Formats          |    |

| 2.4  | Feature         | es of Instructions              |    |

|      | 2.4.1           | RISC Type                       | 25 |

|      | 2.4.2           | Addressing Modes                |    |

|      | 2.4.3           | Instruction Formats             |    |

| 2.5  | Instruc         | tion Set                        |    |

|      | 2.5.1           | Instruction Set by Type         |    |

| 2.6  | Proces          | sing States                     |    |

|      | 2.6.1           | State Transition                |    |

| Sect | ion 3 C         | Cache                           | 49 |

| 3.1  | Feature         | es                              |    |

|      | 3.1.1           | Cache Structure                 |    |

|      | 3.1.2           | Divided Areas and Cache         | 51 |

| 3.2  | Registe         | er Descriptions                 |    |

|      | 3.2.1           | Cache Control Register 1 (CCR1) |    |

|      | 3.2.2           | Cache Control Register 3 (CCR3) | 53 |

| 3.3  | Operat          | ion                             |    |

|      | 3.3.1           | Searching Cache                 |    |

|      | 3.3.2           | Read Access                     |    |

|     | 3.3.3                | Write Access                                                          |         |

|-----|----------------------|-----------------------------------------------------------------------|---------|

|     | 3.3.4                | Write-Back Buffer                                                     |         |

|     | 3.3.5                | Coherency of Cache and External Memory                                |         |

| 3.4 | 4 Memo               | bry-Mapped Cache                                                      |         |

|     | 3.4.1                | Address Array                                                         |         |

|     | 3.4.2                | Data Array                                                            |         |

|     | 3.4.3                | Usage Examples                                                        | 61      |

| Se  | ection 4 U           | J Memory                                                              | 63      |

| 4.  | 1 Featur             | es                                                                    |         |

| 4.2 | 2 Usage              | Notes                                                                 |         |

| Se  | ection 5 I           | Exception Handling                                                    | 65      |

| 5.  |                      | iew                                                                   |         |

|     | 5.1.1<br>Sheet4U.cor | Types of Exception Handling and Priority                              |         |

|     | 5.1.2                | Exception Handling Operations                                         |         |

|     | 5.1.3                | Exception Handling Vector Table                                       |         |

| 5.2 | 2 Resets             | · · · · · · · · · · · · · · · · · · ·                                 |         |

|     | 5.2.1                | Types of Resets                                                       | 69      |

|     | 5.2.2                | Power-On Reset                                                        |         |

|     | 5.2.3                | H-UDI Reset                                                           | 70      |

| 5.  | 3 Addre              | ss Errors                                                             | 71      |

|     | 5.3.1                | Address Error Sources                                                 | 71      |

|     | 5.3.2                | Address Error Exception Source                                        | 71      |

| 5.4 | 4 Interru            | upts                                                                  |         |

|     | 5.4.1                | Interrupt Sources                                                     | 72      |

|     | 5.4.2                | Interrupt Priority                                                    | 73      |

|     | 5.4.3                | Interrupt Exception Handling                                          | 73      |

| 5.5 | 5 Excep              | tions Triggered by Instructions                                       | 74      |

|     | 5.5.1                | Types of Exceptions Triggered by Instructions                         | 74      |

|     | 5.5.2                | Trap Instructions                                                     | 74      |

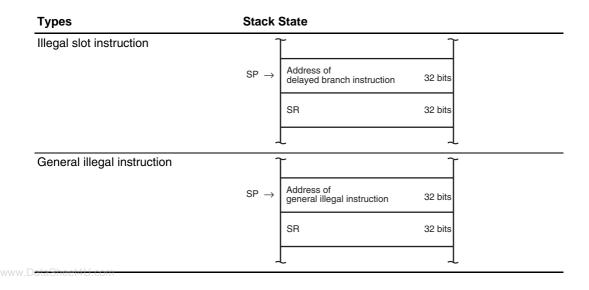

|     | 5.5.3                | Illegal Slot Instructions                                             | 75      |

|     | 5.5.4                | General Illegal Instructions                                          | 75      |

| 5.0 |                      | when Exceptions are Accepted                                          |         |

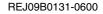

| 5.  | 7 Stack              | States after Exception Handling Ends                                  | 77      |

| 5.8 | 8 Usage              | Notes                                                                 |         |

|     | 5.8.1                | Value of Stack Pointer (SP)                                           |         |

|     | 5.8.2                | Value of Vector Base Register (VBR)                                   |         |

|     | 5.8.3                | Address Errors Caused by Stacking for Address Error Exception Handlin |         |

|     | 5.8.4                | Notes on Slot Illegal Instruction Exception Handling                  |         |

|     |                      | www.DataShee                                                          | t4U.com |

#### RENESAS

Rev. 6.00 Jun. 12, 2007 Page xi of xxxii

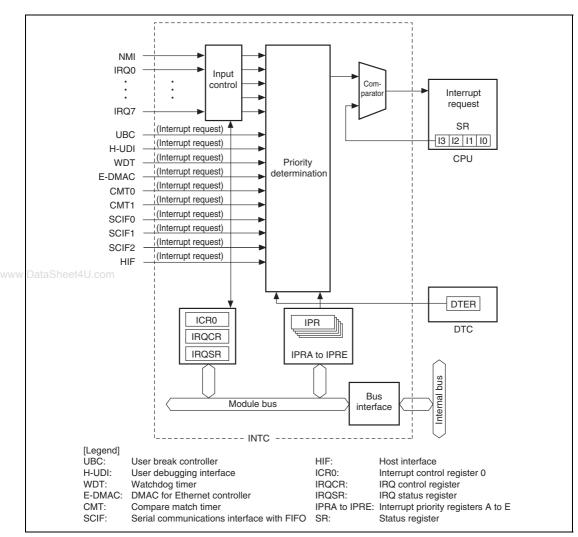

| Sect       | ion 6 I           | nterrupt Controller (INTC)                                                                      |             |

|------------|-------------------|-------------------------------------------------------------------------------------------------|-------------|

| 6.1        | Feature           | es                                                                                              | 81          |

| 6.2        | Input/0           | Output Pins                                                                                     |             |

| 6.3        | Regist            | er Descriptions                                                                                 |             |

|            | 6.3.1             | Interrupt Control Register 0 (ICR0)                                                             |             |

|            | 6.3.2             | IRQ Control Register (IRQCR)                                                                    | 85          |

|            | 6.3.3             | IRQ Status register (IRQSR)                                                                     | 88          |

|            | 6.3.4             | Interrupt Priority Registers A to E (IPRA to IPRE)                                              |             |

| 6.4        | Interru           | pt Sources                                                                                      |             |

|            | 6.4.1             | External Interrupts                                                                             |             |

|            | 6.4.2             | On-Chip Peripheral Module Interrupts                                                            |             |

|            | 6.4.3             | User Break Interrupt                                                                            |             |

|            | 6.4.4             | H-UDI Interrupt                                                                                 |             |

| 6.5        | Interru           | pt Exception Handling Vector Table                                                              |             |

| 6.6        | Interru           | pt Operation                                                                                    |             |

|            | 6.6.1             | Interrupt Sequence                                                                              | 100         |

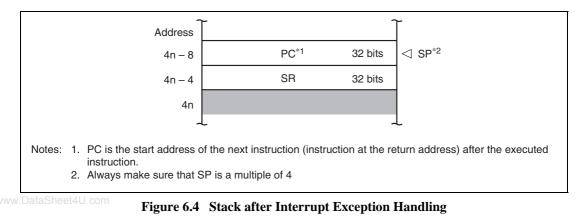

|            | 6.6.2             | Stack after Interrupt Exception Handling                                                        |             |

| 6.7        | Interru           | pt Response Time                                                                                |             |

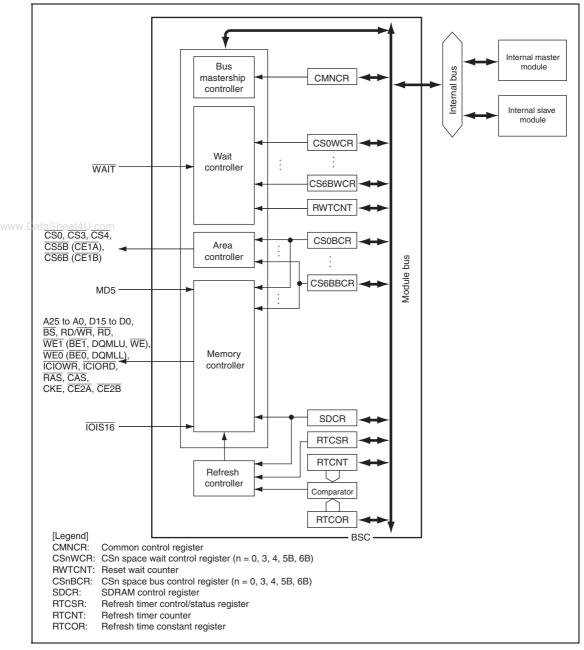

| Sect       | ion 7 D           | Bus State Controller (BSC)                                                                      | 105         |

| 7.1        |                   |                                                                                                 |             |

|            |                   | es<br>Dutput Pins                                                                               |             |

| 7.2<br>7.3 | 1                 | Dutput PinsDverview                                                                             |             |

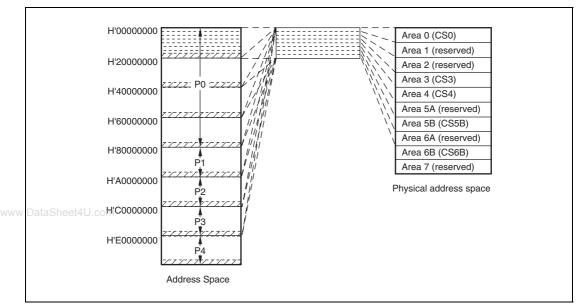

| 1.5        | 7.3.1             |                                                                                                 |             |

|            |                   | Area Division                                                                                   |             |

|            | 7.3.2<br>7.3.3    | Shadow Area                                                                                     |             |

|            | 7.3.3<br>7.3.4    | Address Map                                                                                     |             |

|            |                   | Area 0 Memory Type and Memory Bus Width                                                         |             |

| 74         | 7.3.5<br>Descript | Data Alignment                                                                                  |             |

| 7.4        | 7.4.1             | er Descriptions                                                                                 |             |

|            |                   | Common Control Register (CMNCR)                                                                 |             |

|            | 7.4.2<br>7.4.3    | CSn Space Bus Control Register (CSnBCR) $(n = 0, 2, 3, 4, 5B, 6B)$                              |             |

|            | 7.4.5             | CSn Space Wait Control Register (CSnWCR) (n = 0, 3, 4, 5B, 6B)<br>SDRAM Control Register (SDCR) |             |

|            | 7.4.4             | Refresh Timer Control/Status Register (RTCSR)                                                   |             |

|            | 7.4.5<br>7.4.6    | e , ,                                                                                           |             |

|            |                   | Refresh Timer Counter (RTCNT)                                                                   |             |

| 75         | 7.4.7             | Refresh Time Constant Register (RTCOR)                                                          |             |

| 7.5        | 1                 | ion                                                                                             |             |

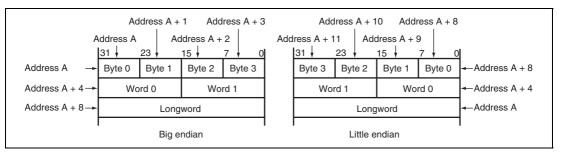

|            | 7.5.1             | Endian/Access Size and Data Alignment                                                           |             |

|            | 7.5.2             | Normal Space Interface                                                                          |             |

|            | 7.5.3             | Access Wait Control                                                                             |             |

|            |                   | www.Data                                                                                        | Sheet4U.com |

|                | 7.5.4    | Extension of Chip Select ( $\overline{CSn}$ ) Assertion Period |                     |

|----------------|----------|----------------------------------------------------------------|---------------------|

|                | 7.5.5    | SDRAM Interface                                                |                     |

|                | 7.5.6    | Byte-Selection SRAM Interface                                  |                     |

|                | 7.5.7    | PCMCIA Interface                                               |                     |

|                | 7.5.8    | Wait between Access Cycles                                     |                     |

|                | 7.5.9    | Others                                                         |                     |

| Sect           | tion 8 C | Clock Pulse Generator (CPG)                                    |                     |

| 8.1            |          | 'es                                                            |                     |

| 8.2            |          | Output Pins                                                    |                     |

| 8.3            | -        | Operating Modes                                                |                     |

| 8.4            |          | ter Descriptions                                               |                     |

|                | 8.4.1    | Frequency Control Register (FRQCR)                             |                     |

|                | 8.4.2    | PHY-LSI Clock Frequency Control Register (MCLKCI               |                     |

|                | 8.4.3    | Usage Notes                                                    |                     |

| DataShe<br>8.5 | Chang    | ng Frequency                                                   |                     |

|                | 8.5.1    | Changing Multiplication Ratio                                  |                     |

|                | 8.5.2    | Changing Division Ratio                                        |                     |

|                | 8.5.3    | Changing Clock Operating Mode                                  |                     |

| 8.6            | Notes    | on Board Design                                                |                     |

| Sect           | tion 9 V | Watchdog Timer (WDT)                                           |                     |

| 9.1            |          | es                                                             |                     |

| 9.2            |          | er Descriptions                                                |                     |

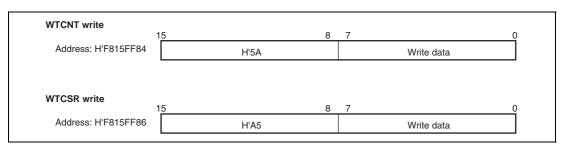

|                | 9.2.1    | Watchdog Timer Counter (WTCNT)                                 |                     |

|                | 9.2.2    | Watchdog Timer Control/Status Register (WTCSR)                 |                     |

|                | 9.2.3    | Notes on Register Access                                       |                     |

| 9.3            | WDT      | Operation                                                      |                     |

|                | 9.3.1    | Canceling Software Standbys                                    |                     |

|                | 9.3.2    | Changing Frequency                                             |                     |

|                | 9.3.3    | Using Watchdog Timer Mode                                      |                     |

|                | 9.3.4    | Using Interval Timer Mode                                      |                     |

| 9.4            | Usage    | Note                                                           |                     |

| Sect           | tion 10  | Power-Down Modes                                               |                     |

| 10.1           |          | es                                                             |                     |

| 10.1           |          | Types of Power-Down Modes                                      |                     |

| 10.2           |          | Output Pins                                                    |                     |

| 10.2           | -        | ter Descriptions                                               |                     |

| 10.5           | 0        | Standby Control Register (STBCR)                               |                     |

|                | 10.5.1   | Sundoy Control Register (OTDER)                                | www.DataSheet4U.com |

Rev. 6.00 Jun. 12, 2007 Page xiii of xxxii

|          | 10.3.2 Standby    | Control Register 2 (STBCR2)                     |                     |

|----------|-------------------|-------------------------------------------------|---------------------|

|          | 10.3.3 Standby    | Control Register 3 (STBCR3)                     |                     |

|          | 10.3.4 Standby    | Control Register 4 (STBCR4)                     |                     |

| 10.4     | Sleep Mode        |                                                 |                     |

|          | 10.4.1 Transitio  | on to Sleep Mode                                |                     |

|          | 10.4.2 Cancelin   | g Sleep Mode                                    |                     |

| 10.5     | Software Standby  | y Mode                                          |                     |

|          | 10.5.1 Transitio  | on to Software Standby Mode                     |                     |

|          | 10.5.2 Cancelin   | g Software Standby Mode                         |                     |

| 10.6     | Module Standby    | Mode                                            |                     |

|          | 10.6.1 Transitio  | on to Module Standby Mode                       |                     |

|          | 10.6.2 Cancelin   | g Module Standby Function                       |                     |

| ~ .      |                   |                                                 |                     |

|          |                   | Controller (EtherC)                             |                     |

| .DataShe |                   |                                                 |                     |

| 11.2     | 1 1               | s                                               |                     |

| 11.3     |                   | tion                                            |                     |

|          |                   | Mode Register (ECMR)                            |                     |

|          |                   | Status Register (ECSR)                          |                     |

|          |                   | nterrupt Permission Register (ECSIPR)           |                     |

|          |                   | erface Register (PIR)                           |                     |

|          |                   | ddress High Register (MAHR)                     |                     |

|          |                   | ddress Low Register (MALR)                      |                     |

|          |                   | Frame Length Register (RFLR)                    |                     |

|          |                   | tus Register (PSR)                              |                     |

|          |                   | t Retry Over Counter Register (TROCR)           |                     |

|          | 11.3.10 Delayed   | Collision Detect Counter Register (CDCR)        |                     |

|          | 11.3.11 Lost Car  | rier Counter Register (LCCR)                    |                     |

|          | 11.3.12 Carrier N | Not Detect Counter Register (CNDCR)             |                     |

|          | 11.3.13 CRC Err   | or Frame Counter Register (CEFCR)               |                     |

|          | 11.3.14 Frame R   | eceive Error Counter Register (FRECR)           |                     |

|          | 11.3.15 Too-Sho   | rt Frame Receive Counter Register (TSFRCR)      |                     |

|          |                   | g Frame Receive Counter Register (TLFRCR)       |                     |

|          | 11.3.17 Residual  | -Bit Frame Counter Register (RFCR)              |                     |

|          | 11.3.18 Multicas  | t Address Frame Counter Register (MAFCR)        |                     |

|          | U                 | ister (IPGR)                                    |                     |

|          | 11.3.20 Automat   | ic PAUSE Frame Set Register (APR)               |                     |

|          |                   | PAUSE Frame Set Register (MPR)                  |                     |

|          | 11.3.22 Automat   | ic PAUSE Frame Retransfer Count Set Register (T | PAUSER) 246         |

| 11.4     | Operation         |                                                 |                     |

|          |                   | ,                                               | www.DataSheet4U.com |

|      | 11.4.1    | Transmission                                                 |     |

|------|-----------|--------------------------------------------------------------|-----|

|      | 11.4.2    | Reception                                                    |     |

|      | 11.4.3    | MII Frame Timing                                             |     |

|      | 11.4.4    | Accessing MII Registers                                      |     |

|      | 11.4.5    | Magic Packet Detection                                       |     |

|      | 11.4.6    | Operation by IPG Setting                                     |     |

|      | 11.4.7    | Flow Control                                                 |     |

| 11.5 | Connec    | ction to PHY-LSI                                             |     |

| 11.6 | Usage     | Notes                                                        |     |

|      |           |                                                              |     |

| Sec  | tion $12$ | Ethernet Controller Direct Memory Access Controller          |     |

|      |           | (E-DMAC)                                                     | 259 |

| 12.1 | Feature   | 28                                                           |     |

| 12.2 | Registe   | er Descriptions                                              |     |

|      | 12.2.1    | E-DMAC Mode Register (EDMR)                                  |     |

|      | 12.2.2    | E-DMAC Transmit Request Register (EDTRR)                     |     |

|      | 12.2.3    | E-DMAC Receive Request Register (EDRRR)                      |     |

|      | 12.2.4    | Transmit Descriptor List Address Register (TDLAR)            |     |

|      | 12.2.5    | Receive Descriptor List Address Register (RDLAR)             |     |

|      | 12.2.6    | EtherC/E-DMAC Status Register (EESR)                         |     |

|      | 12.2.7    | EtherC/E-DMAC Status Interrupt Permission Register (EESIPR)  |     |

|      | 12.2.8    | Transmit/Receive Status Copy Enable Register (TRSCER)        |     |

|      | 12.2.9    | Receive Missed-Frame Counter Register (RMFCR)                |     |

|      | 12.2.10   | ) Transmit FIFO Threshold Register (TFTR)                    |     |

|      | 12.2.11   | FIFO Depth Register (FDR)                                    |     |

|      | 12.2.12   | 2 Receiving method Control Register (RMCR)                   |     |

|      | 12.2.13   | B E-DMAC Operation Control Register (EDOCR)                  |     |

|      | 12.2.14   | Receiving-Buffer Write Address Register (RBWAR)              |     |

|      | 12.2.15   | 5 Receiving-Descriptor Fetch Address Register (RDFAR)        |     |

|      | 12.2.16   | 5 Transmission-Buffer Read Address Register (TBRAR)          |     |

|      | 12.2.17   | 7 Transmission-Descriptor Fetch Address Register (TDFAR)     |     |

|      | 12.2.18   | B Flow Control FIFO Threshold Register (FCFTR)               |     |

|      | 12.2.19   | 9 Transmit Interrupt Register (TRIMD)                        |     |

| 12.3 | Operat    | ion                                                          |     |

|      | 12.3.1    | Descriptor List and Data Buffers                             |     |

|      | 12.3.2    | Transmission                                                 |     |

|      |           | Reception                                                    |     |

|      |           | Multi-Buffer Frame Transmit/Receive Processing               |     |

| 12.4 |           | Notes                                                        |     |

|      | -         | Usage Notes on SH-Ether EtherC/E-DMAC Status Register (EESR) |     |

|      |           |                                                              |     |

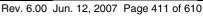

Rev. 6.00 Jun. 12, 2007 Page xv of xxxii

|       | 12.4.2   | Usage Notes on SH-Ether Transmit-FIFO Underflow                  |             |

|-------|----------|------------------------------------------------------------------|-------------|

| Secti | ion 13 ( | Compare Match Timer (CMT)                                        |             |

| 13.1  |          | S                                                                |             |

| 13.2  |          | er Descriptions                                                  |             |

|       | -        | Compare Match Timer Start Register (CMSTR)                       |             |

|       |          | Compare Match Timer Control/Status Register (CMCSR)              |             |

|       |          | Compare Match Counter (CMCNT)                                    |             |

|       |          | Compare Match Constant Register (CMCOR)                          |             |

| 13.3  |          | ion                                                              |             |

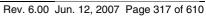

|       | 13.3.1   | Interval Count Operation                                         |             |

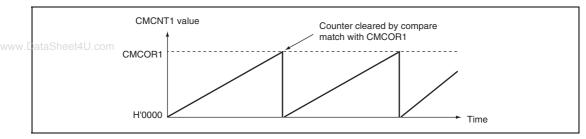

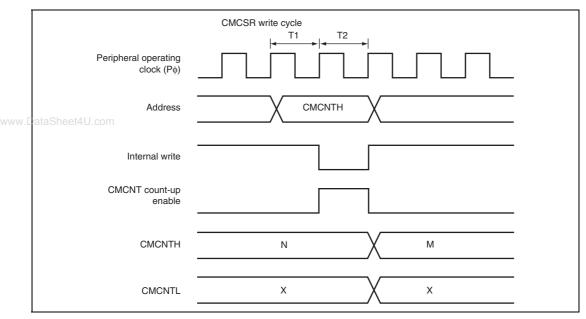

|       | 13.3.2   | CMCNT Count Timing                                               |             |

| 13.4  | Interru  | pts                                                              |             |

|       | 13.4.1   | Interrupt Sources                                                |             |

|       | 13.4.2   | Timing of Setting Compare Match Flag                             |             |

|       |          | Timing of Clearing Compare Match Flag                            |             |

| 13.5  |          | Notes                                                            |             |

|       | 13.5.1   | Conflict between Write and Compare-Match Processes of CMCNT      |             |

|       | 13.5.2   | Conflict between Word-Write and Count-Up Processes of CMCNT      |             |

|       | 13.5.3   | Conflict between Byte-Write and Count-Up Processes of CMCNT      |             |

|       | 13.5.4   | Conflict between Write Processes to CMCNT with the Counting Stop | ped and     |

|       |          | CMCOR                                                            |             |

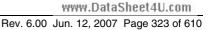

| Secti | ion 14 9 | Serial Communication Interface with FIFO (SCIF)                  | 325         |

| 14.1  |          | ew                                                               |             |

| 1     |          | Features                                                         |             |

| 14.2  |          | nfiguration                                                      |             |

| 14.3  |          | er Description                                                   |             |

| 11.5  | -        | Receive Shift Register (SCRSR)                                   |             |

|       |          | Receive FIFO Data Register (SCFRDR)                              |             |

|       |          | Transmit Shift Register (SCTSR)                                  |             |

|       |          | Transmit FIFO Data Register (SCFTDR)                             |             |

|       |          | Serial Mode Register (SCSMR)                                     |             |

|       |          | Serial Control Register (SCSCR)                                  |             |

|       |          | Serial Status Register (SCFSR)                                   |             |

|       |          | Bit Rate Register (SCBRR)                                        |             |

|       |          | FIFO Control Register (SCFCR)                                    |             |

|       |          | ) FIFO Data Count Register (SCFDR)                               |             |

|       |          | Serial Port Register (SCSPTR)                                    |             |

|       |          | Line Status Register (SCLSR)                                     |             |

|       |          | - · · · · · · · · · · · · · · · · · · ·                          | Sheet4U.com |

| 14.4               | Operation                                                            |                   |

|--------------------|----------------------------------------------------------------------|-------------------|

|                    | 14.4.1 Overview                                                      |                   |

|                    | 14.4.2 Operation in Asynchronous Mode                                |                   |

|                    | 14.4.3 Synchronous Mode                                              |                   |

| 14.5               | SCIF Interrupts                                                      |                   |

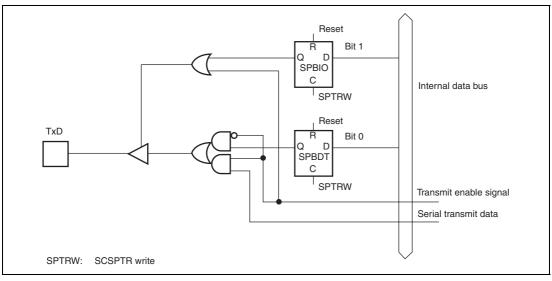

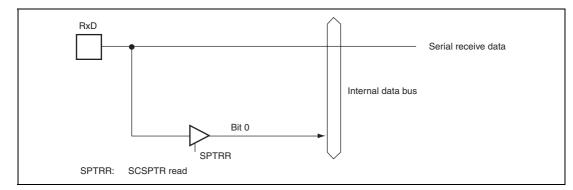

| 14.6               | Serial Port Register (SCSPTR) and SCIF Pins                          |                   |

| 14.7               | Usage Notes                                                          |                   |

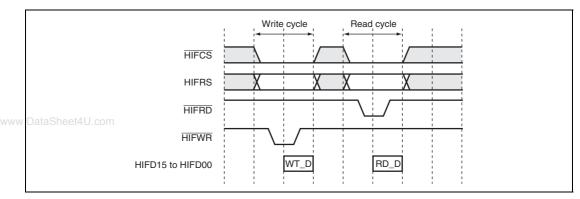

| Sect               | ion 15 Host Interface (HIF)                                          |                   |

| 15.1               | Features                                                             |                   |

| 15.2               | Input/Output Pins                                                    | 393               |

| 15.3               | Parallel Access                                                      |                   |

|                    | 15.3.1 Operation                                                     |                   |

|                    | 15.3.2 Connection Method                                             |                   |

| 15.4<br>w.DataShee | Register Descriptions                                                |                   |

|                    | 15.4.1 HIF Index Register (HIFIDX)                                   |                   |

|                    | 15.4.2 HIF General Status Register (HIFGSR)                          |                   |

|                    | 15.4.3 HIF Status/Control Register (HIFSCR)                          |                   |

|                    | 15.4.4 HIF Memory Control Register (HIFMCR)                          |                   |

|                    | 15.4.5 HIF Internal Interrupt Control Register (HIFIICR)             |                   |

|                    | 15.4.6 HIF External Interrupt Control Register (HIFEICR)             |                   |

|                    | 15.4.7 HIF Address Register (HIFADR)                                 |                   |

|                    | 15.4.8 HIF Data Register (HIFDATA)                                   |                   |

|                    | 15.4.9 HIF Boot Control Register (HIFBCR)                            |                   |

|                    | 15.4.10 HIFDREQ Trigger Register (HIFDTR)                            |                   |

|                    | 15.4.11 HIF Bank Interrupt Control Register (HIFBICR)                |                   |

| 15.5               | Memory Map                                                           |                   |

| 15.6               | Interface (Basic)                                                    |                   |

| 15.7               | Interface (Details)                                                  |                   |

|                    | 15.7.1 HIFIDX Write/HIFGSR Read                                      |                   |

|                    | 15.7.2 Reading/Writing of HIF Registers other than HIFIDX and HIFGSR |                   |

|                    | 15.7.3 Consecutive Data Writing to HIFRAM by External Device         |                   |

|                    | 15.7.4 Consecutive Data Reading from HIFRAM to External Device       |                   |

| 15.8               | External DMAC Interface                                              |                   |

| 15.9               | Interface When External Device Power is Cut Off                      |                   |

| Sect               | ion 16 Pin Function Controller (PFC)                                 |                   |

| 16.1               | Register Descriptions                                                |                   |

|                    | 16.1.1 Port A IO Register H (PAIORH)                                 |                   |

|                    | 16.1.2 Port A Control Register H1 and H2 (PACRH1 and PACRH2)         |                   |

|                    | www.DataS                                                            | heet4U.com        |

|                    | Rev. 6.00 Jun. 12, 2007 F                                            | age xvii of xxxii |

|                   | 16.1.3  | Port B IO Register L (PBIORL)                                  |             |

|-------------------|---------|----------------------------------------------------------------|-------------|

|                   | 16.1.4  | Port B Control Register L1 and L2 (PBCRL1 and PBCRL2)          |             |

|                   | 16.1.5  | Port C IO Register H and L (PCIORH and PCIORL)                 |             |

|                   | 16.1.6  | Port C Control Register H2, L1, and L2 (PCCRH2, PCCRL1, and PC | CRL2) 440   |

|                   | 16.1.7  | Port D IO Register L (PDIORL)                                  |             |

|                   | 16.1.8  | Port D Control Register L2 (PDCRL2)                            |             |

|                   | 16.1.9  | Port E IO Register H and L (PEIORH and PEIORL)                 |             |

|                   | 16.1.10 | Port E Control Register H1, H2, L1, and L2 (PECRH1, PECRH2, PE | CRL1, and   |

|                   |         | PECRL2)                                                        |             |

| ~                 |         |                                                                |             |

|                   |         | I/O Ports                                                      |             |

| 17.1              |         |                                                                |             |

|                   |         | Register Description                                           |             |

|                   |         | Port A Data Register H (PADRH)                                 |             |

| 17.2<br>w.DataShe |         | n                                                              |             |

|                   |         | Register Description                                           |             |

|                   |         | Port B Data Register L (PBDRL)                                 |             |

| 17.3              |         |                                                                |             |

|                   |         | Register Description                                           |             |

|                   |         | Port C Data Registers H and L (PCDRH and PCDRL)                |             |

| 17.4              |         |                                                                |             |

|                   |         | Register Description                                           |             |

|                   |         | Port D Data Register L (PDDRL)                                 |             |

| 17.5              |         |                                                                |             |

|                   |         | Register Description                                           |             |

| . – .             |         | Port E Data Registers H and L (PEDRH and PEDRL)                |             |

| 17.6              | Usage . | Note                                                           |             |

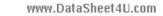

| Soct              | ion 18  | User Break Controller (UBC)                                    | 471         |

| 18.1              |         | 28                                                             |             |

| 18.1              |         | er Descriptions                                                |             |

| 10.2              | -       | Break Address Register A (BARA)                                |             |

|                   |         | Break Address Mask Register A (BANA)                           |             |

|                   |         | Break Bus Cycle Register A (BBRA)                              |             |

|                   |         | Break Address Register B (BARB)                                |             |

|                   | 18.2.5  |                                                                |             |

|                   | 18.2.5  | Break Data Register B (BDRB)                                   |             |

|                   | 18.2.7  |                                                                |             |

|                   | 18.2.8  | Break Bus Cycle Register B (BBRB)                              |             |

|                   |         | Break Control Register (BRCR)                                  |             |

|                   | 10.2.7  | -                                                              | Sheet4U.com |

|      | 18.2.10 Execution Times Break Register (BETR) |                   |

|------|-----------------------------------------------|-------------------|

|      | 18.2.11 Branch Source Register (BRSR)         |                   |

|      | 18.2.12 Branch Destination Register (BRDR)    |                   |

| 18.3 | Operation                                     |                   |

|      | 18.3.1 Flow of User Break Operation           |                   |

|      | 18.3.2 Break on Instruction Fetch Cycle       |                   |

|      | 18.3.3 Break on Data Access Cycle             |                   |

|      | 18.3.4 Sequential Break                       |                   |

|      | 18.3.5 Value of Saved Program Counter (PC)    |                   |

|      | 18.3.6 PC Trace                               |                   |

|      | 18.3.7 Usage Examples                         |                   |

|      | 18.3.8 Usage Notes                            |                   |

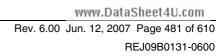

| Sect | ion 19 User Debugging Interface (H-UDI)       |                   |

| 19.1 | Features                                      |                   |

| 19.2 | Input/Output Pins                             |                   |

| 19.3 | Register Descriptions                         |                   |

|      | 19.3.1 Bypass Register (SDBPR)                |                   |

|      | 19.3.2 Instruction Register (SDIR)            | 496               |

|      | 19.3.3 Boundary Scan Register (SDBSR)         |                   |

|      | 19.3.4 ID Register (SDID)                     |                   |

| 19.4 | Operation                                     |                   |

|      | 19.4.1 TAP Controller                         |                   |

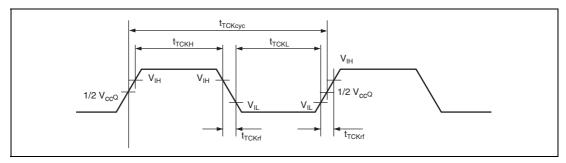

|      | 19.4.2 Reset Configuration                    | 505               |

|      | 19.4.3 TDO Output Timing                      |                   |

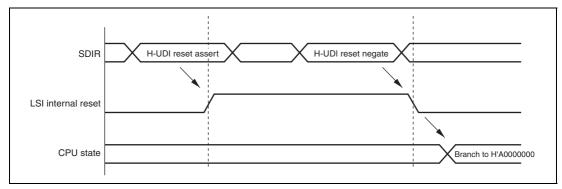

|      | 19.4.4 H-UDI Reset                            |                   |

|      | 19.4.5 H-UDI Interrupt                        |                   |

| 19.5 | Boundary Scan                                 |                   |

|      | 19.5.1 Supported Instructions                 |                   |

|      | 19.5.2 Points for Attention                   |                   |

| 19.6 | Usage Notes                                   | 508               |

| Sect | ion 20 List of Registers                      |                   |

| 20.1 | Register Addresses (Address Order)            |                   |

| 20.2 | Register Bits                                 |                   |

| 20.3 | Register States in Each Processing State      |                   |

| Sect | ion 21 Electrical Characteristics             | 539               |

| 21.1 | Absolute Maximum Ratings                      | 539               |

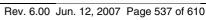

| 21.2 | Power-On and Power-Off Order                  |                   |

|      |                                               | Sheet4U.com       |

|      | Rev. 6.00 Jun. 12, 2007                       | rage xix of xxxII |

| 21.3  | DC Characteristics                                                      |     |

|-------|-------------------------------------------------------------------------|-----|

| 21.4  | AC Characteristics                                                      | 544 |

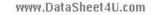

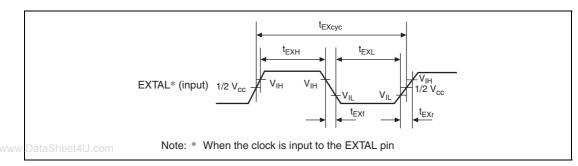

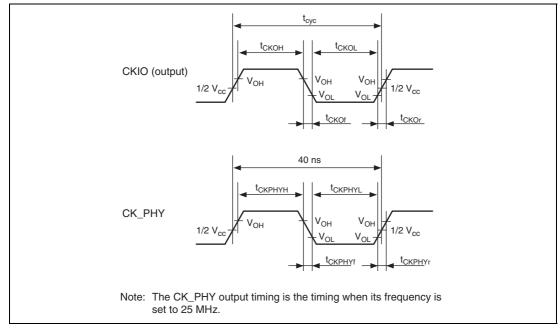

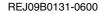

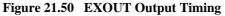

|       | 21.4.1 Clock Timing                                                     | 545 |

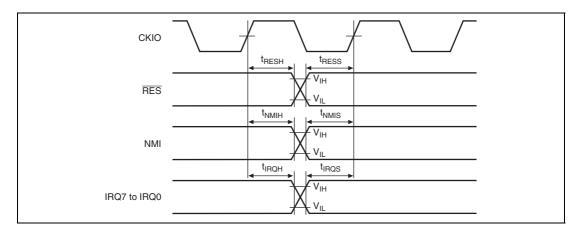

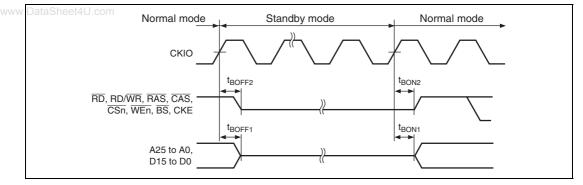

|       | 21.4.2 Control Signal Timing                                            | 549 |

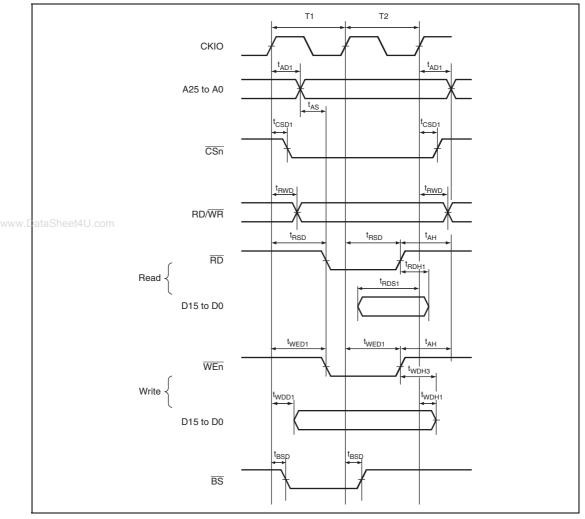

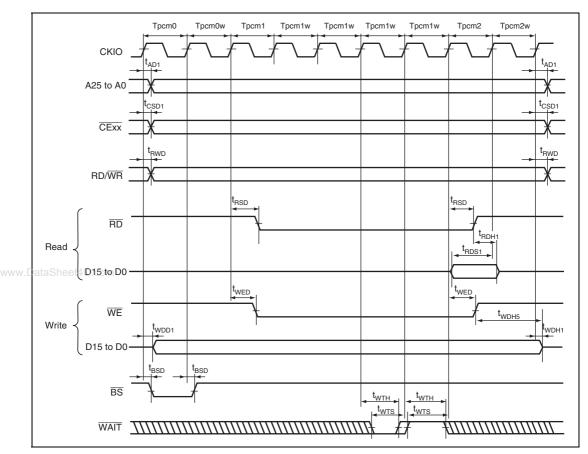

|       | 21.4.3 Bus Timing                                                       | 551 |

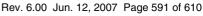

|       | 21.4.4 Basic Timing                                                     | 553 |

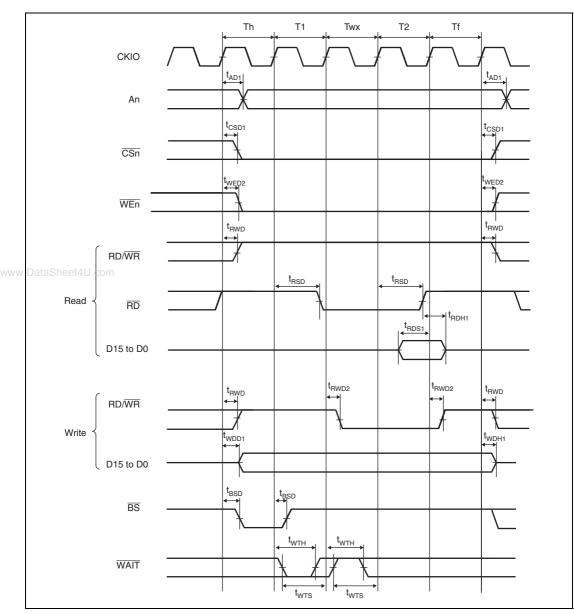

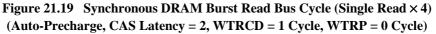

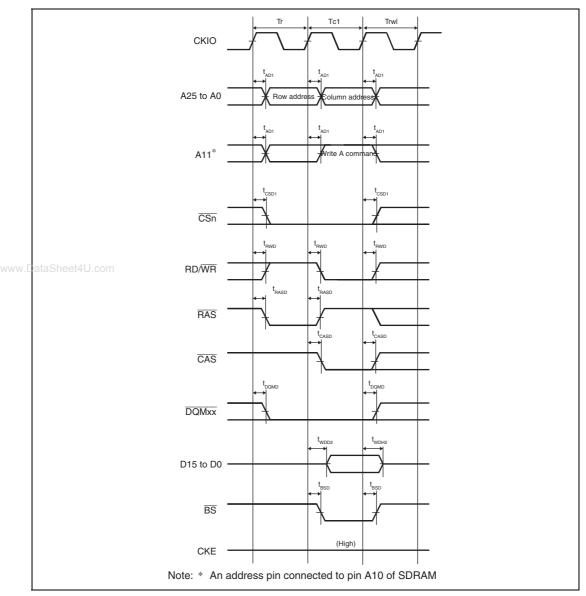

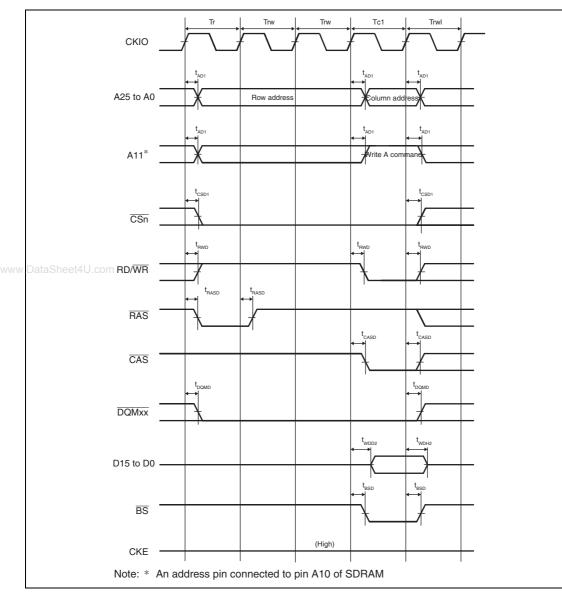

|       | 21.4.5 Synchronous DRAM Timing                                          | 559 |

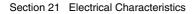

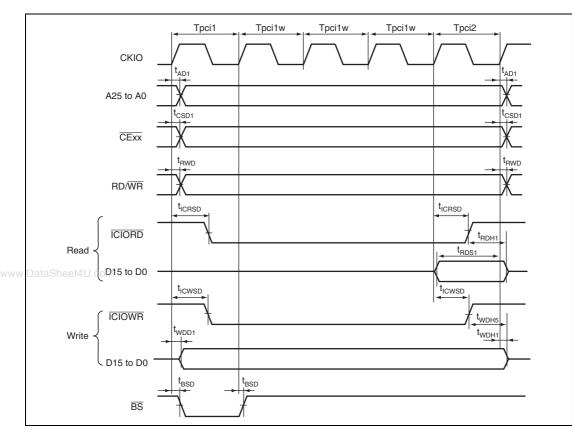

|       | 21.4.6 PCMCIA Timing                                                    | 576 |

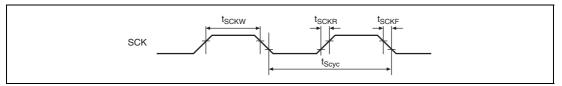

|       | 21.4.7 SCIF Timing                                                      | 580 |

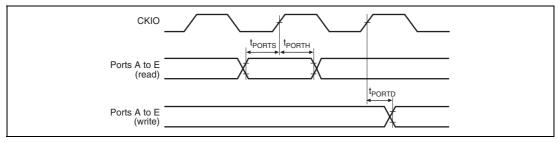

|       | 21.4.8 Port Timing                                                      | 581 |

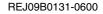

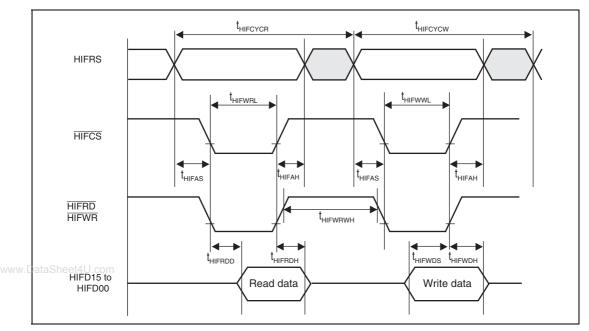

|       | 21.4.9 HIF Timing                                                       |     |

|       | 21.4.10 EtherC Timing                                                   | 585 |

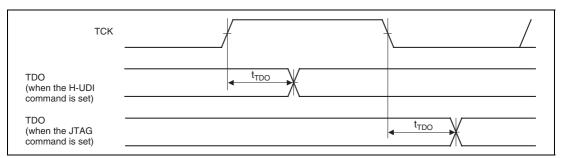

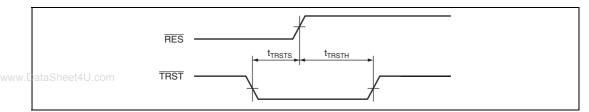

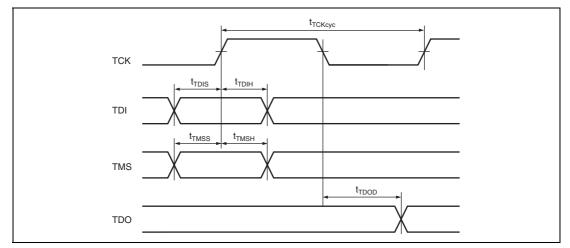

|       | 21.4.11 H-UDI Related Pin Timing                                        | 588 |

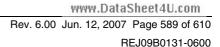

|       | 21.4.12 AC Characteristic Test Conditions                               | 590 |

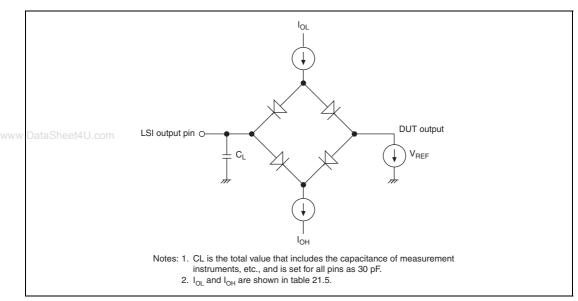

|       | 21.4.13 Delay Time Variation Due to Load Capacitance (Reference Values) | 591 |

|       |                                                                         |     |

| Appe  | endix                                                                   |     |

| A.    | Port States in Each Pin State                                           | 593 |

| B.    | Product Code Lineup                                                     | 597 |

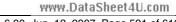

| C.    | Package Dimensions                                                      | 598 |

|       |                                                                         |     |

| Main  | Revisions and Additions in this Edition                                 |     |

|       |                                                                         |     |

| Index | κ                                                                       |     |

# Figures

| Section 1   | Overview                                                                      |     |

|-------------|-------------------------------------------------------------------------------|-----|

| Figure 1.1  | Block Diagram                                                                 | 6   |

| Figure 1.2  | Pin Assignments                                                               | 7   |

| Section 2   | CPU                                                                           |     |

| Figure 2.1  | CPU Internal Register Configuration                                           | 20  |

| U U         | Register Data Format                                                          |     |

| 0           | Memory Data Format                                                            |     |

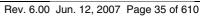

| -           | CPU State Transition                                                          |     |

| Section 3   | Cache                                                                         |     |

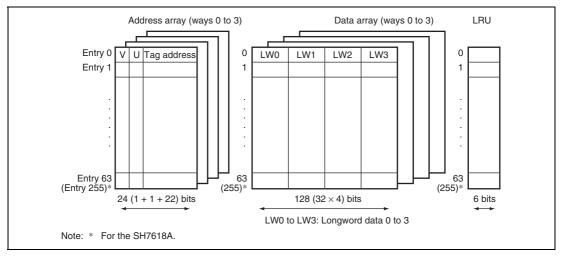

| Figure 3.1  | Cache Structure                                                               | 49  |

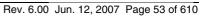

| Figure 3.2  | Cache Search Scheme                                                           | 55  |

| Figure 3.3  | Write-Back Buffer Configuration                                               | 57  |

| Figure 3.4  | Specifying Address and Data for Memory-Mapped Cache Access                    | 60  |

| Section 6   | Interrupt Controller (INTC)                                                   |     |

| Figure 6.1  | INTC Block Diagram                                                            | 82  |

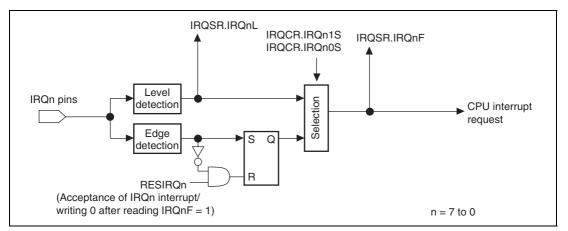

| Figure 6.2  | Block Diagram of IRQ7 to IRQ0 Interrupts Control                              | 96  |

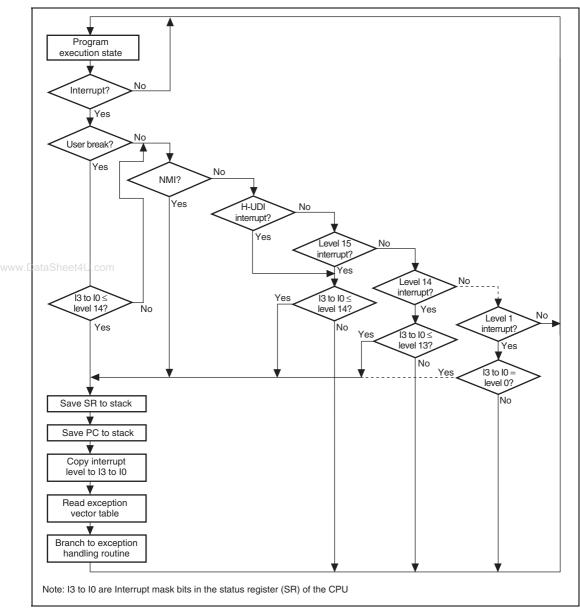

| Figure 6.3  | Interrupt Sequence Flowchart                                                  | 101 |

| Figure 6.4  | Stack after Interrupt Exception Handling                                      | 102 |

| Section 7   | Bus State Controller (BSC)                                                    |     |

| Figure 7.1  | Block Diagram of BSC                                                          | 107 |

| Figure 7.2  | Address Space                                                                 | 110 |

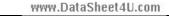

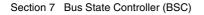

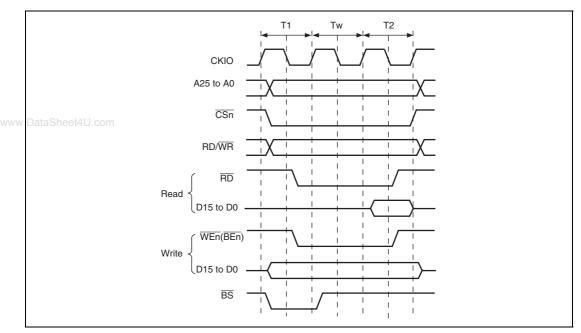

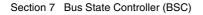

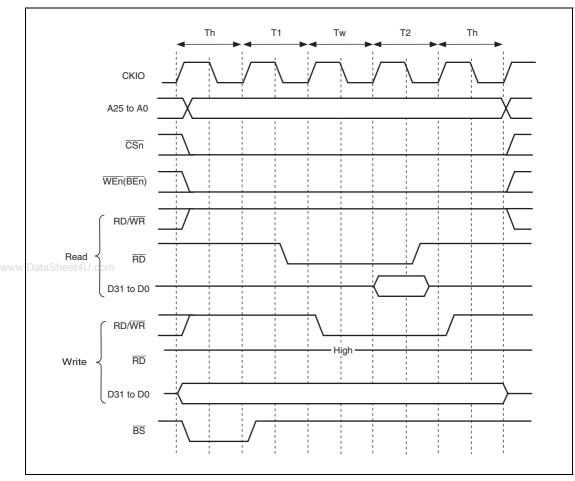

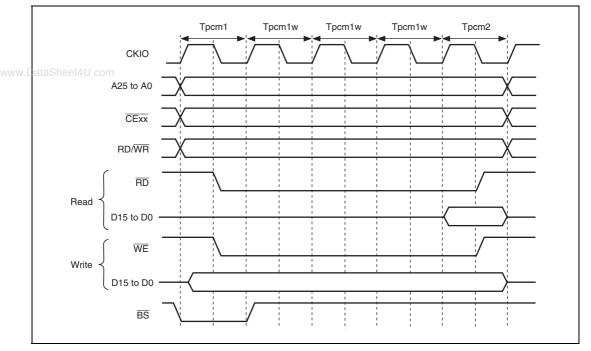

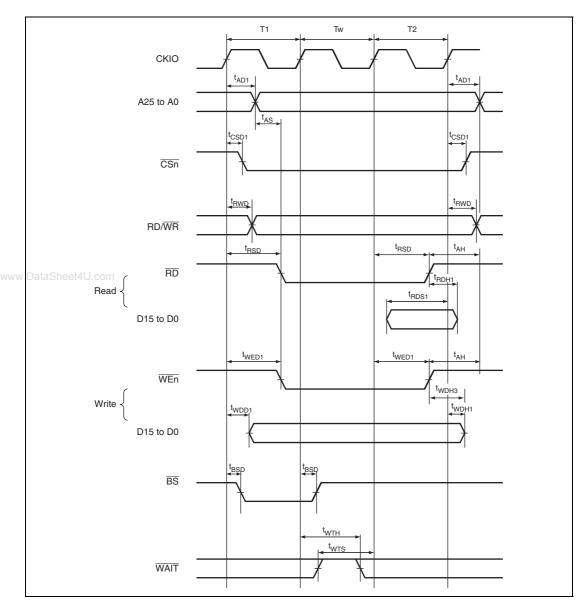

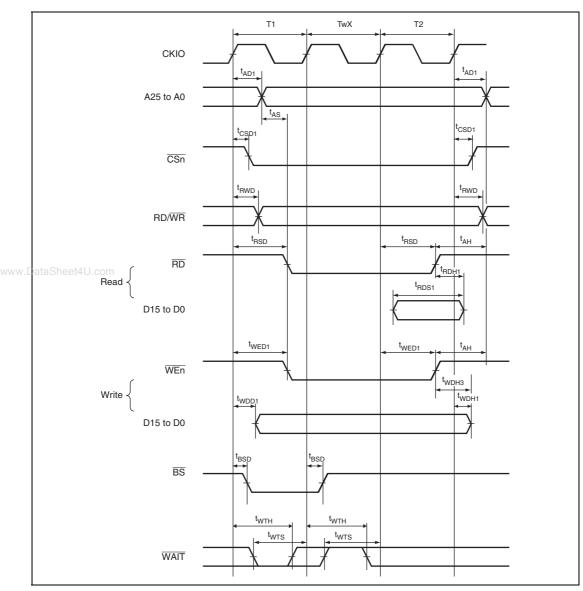

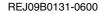

| Figure 7.3  | Normal Space Basic Access Timing (No-Wait Access)                             | 146 |

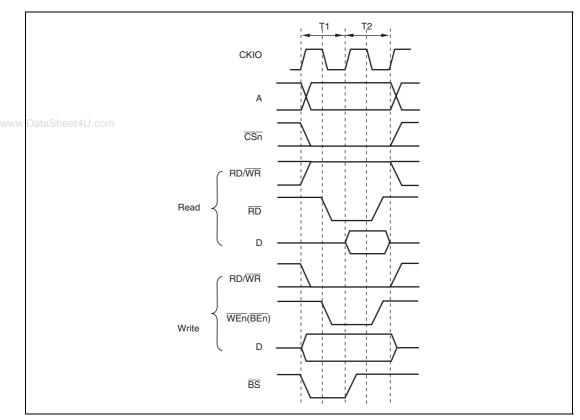

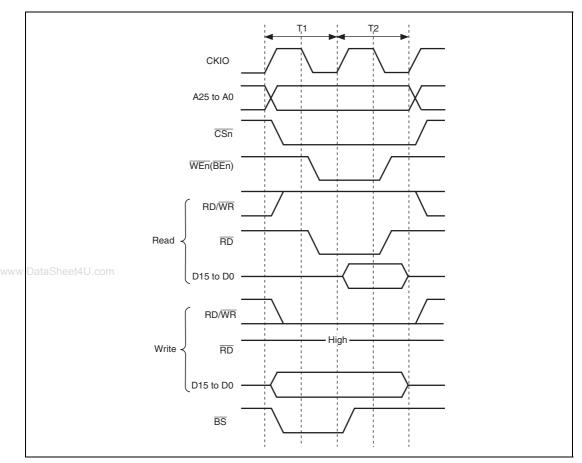

| Figure 7.4  | Consecutive Access to Normal Space (1): Bus Width = 16 bits,                  |     |

|             | Longword Access, CSnWCR.WM = 0 (Access Wait = 0, Cycle Wait = 0)              | 147 |

| Figure 7.5  | Consecutive Access to Normal Space (2): Bus Width = 16 bits,                  |     |

|             | Longword Access, CSnWCR.WM = 1 (Access Wait = 0, Cycle Wait = 0)              |     |

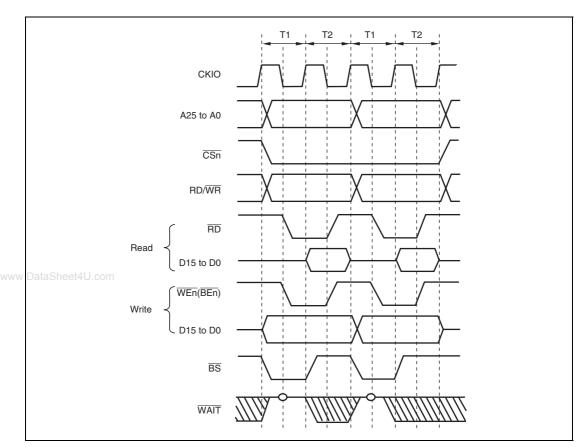

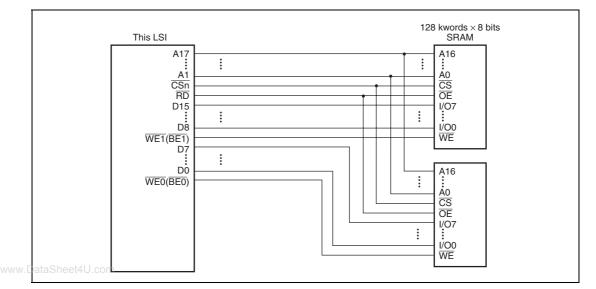

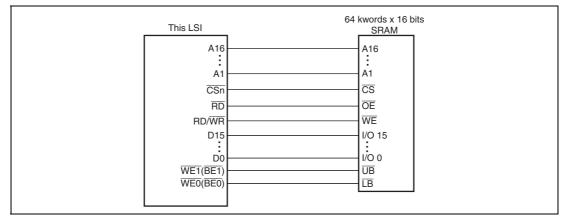

| 0           | Example of 16-Bit Data-Width SRAM Connection                                  |     |

| -           | 1                                                                             |     |

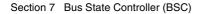

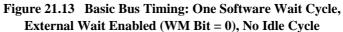

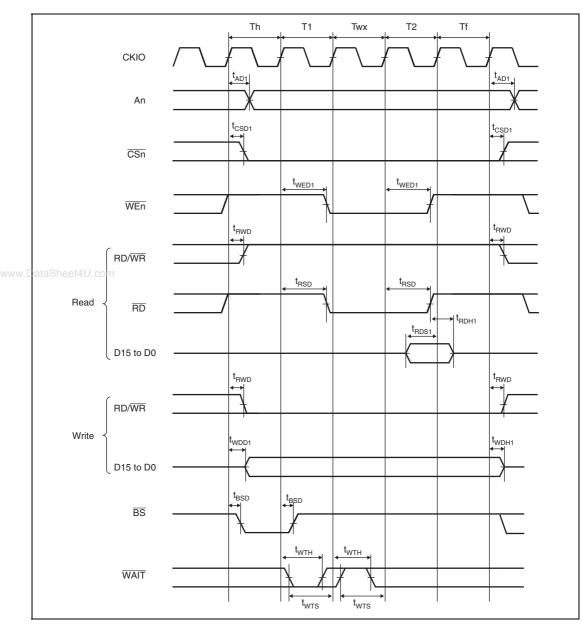

| -           | Wait Timing for Normal Space Access (Software Wait Only)                      |     |

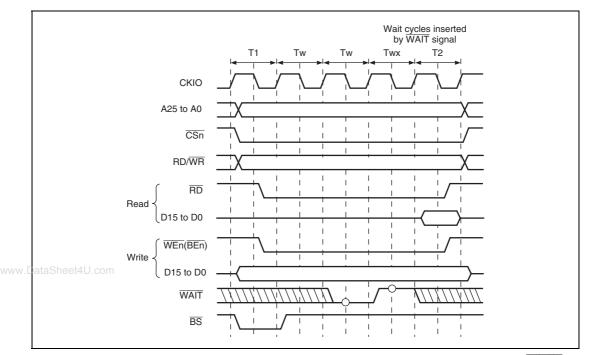

| -           | Wait Cycle Timing for Normal Space Access (Wait cycle Insertion using WAIT)   |     |

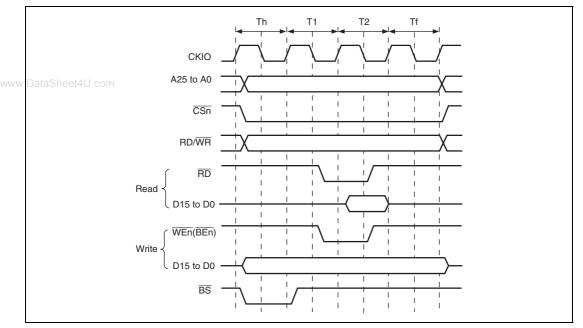

|             | ) Example of Timing when $\overline{\text{CSn}}$ Assertion Period is Extended |     |

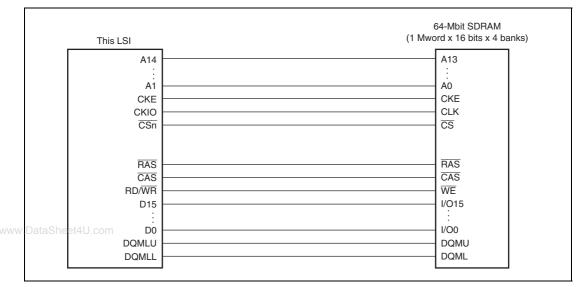

|             | Example of 16-Bit Data-Width SDRAM Connection                                 |     |

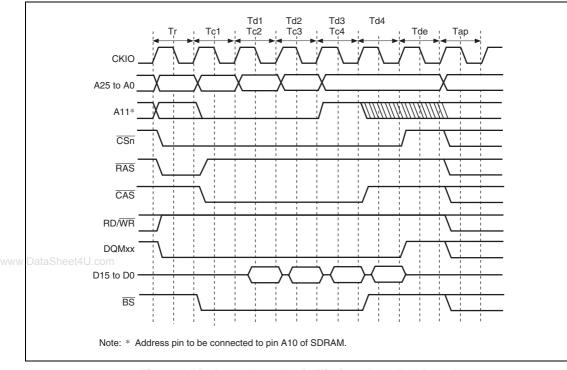

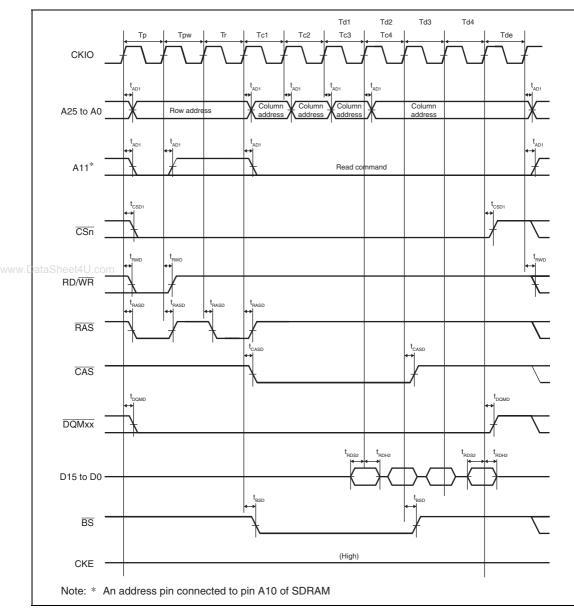

|             | 2 Burst Read Basic Timing (Auto Precharge)                                    |     |

|             | Burst Read Wait Specification Timing (Auto Precharge)                         |     |

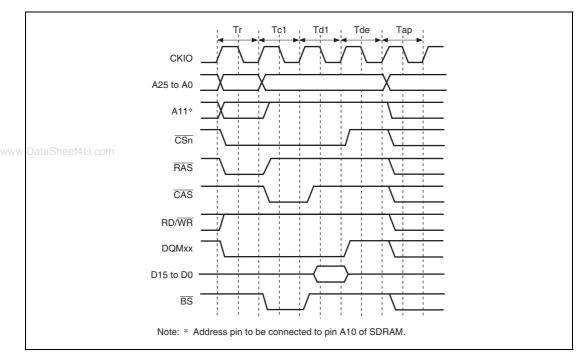

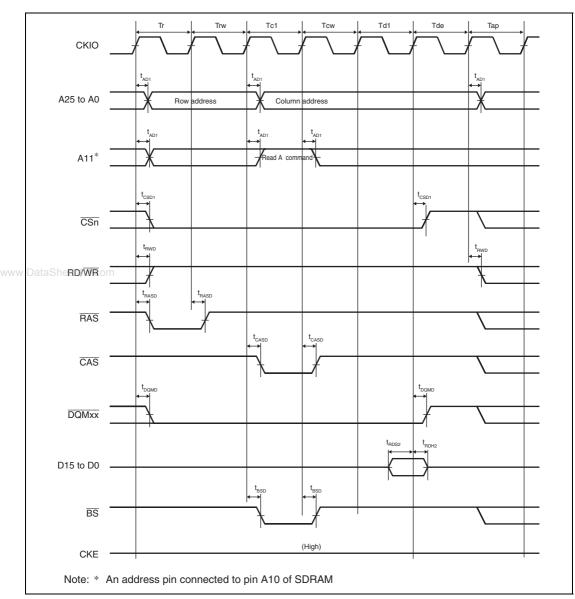

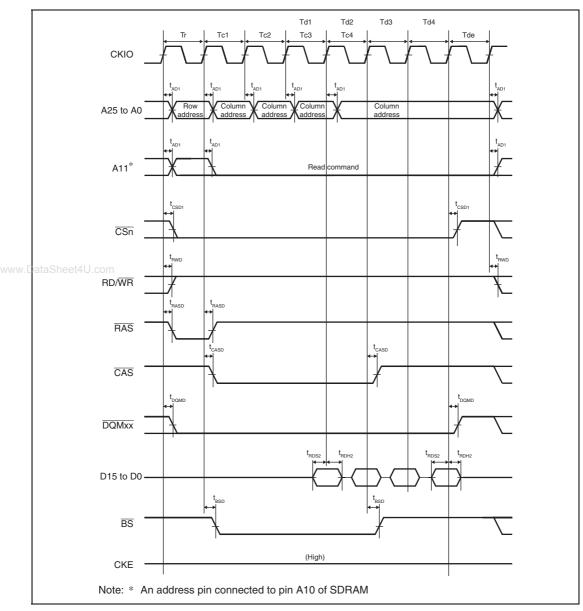

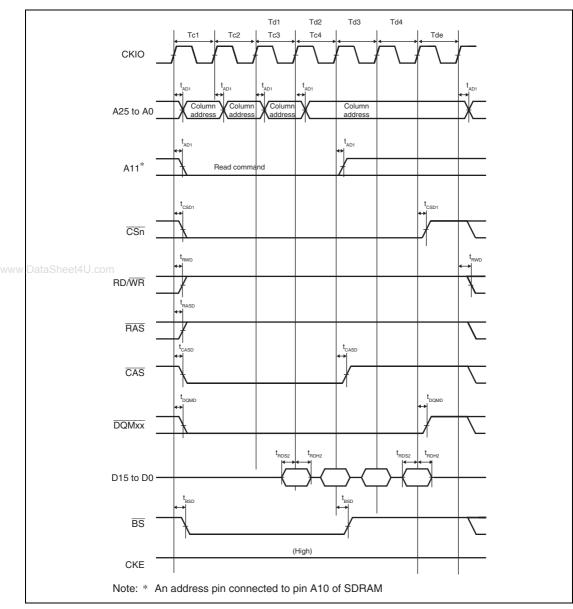

| Figure 7.14 | Basic Timing for Single Read (Auto Precharge)                                 | 164 |

|             |                                                                               |     |

www.DataSheet4U.com

Rev. 6.00 Jun. 12, 2007 Page xxi of xxxii

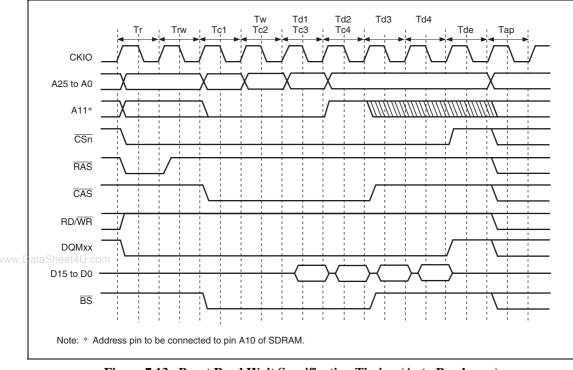

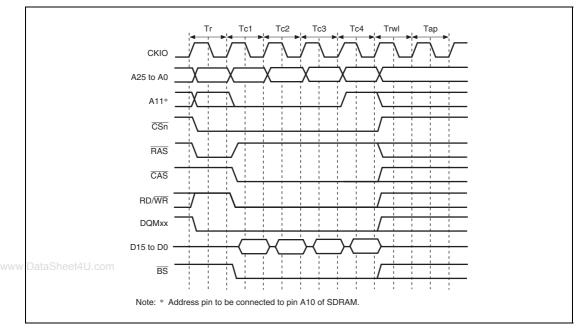

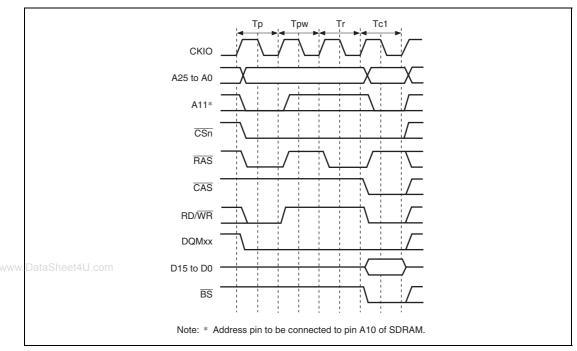

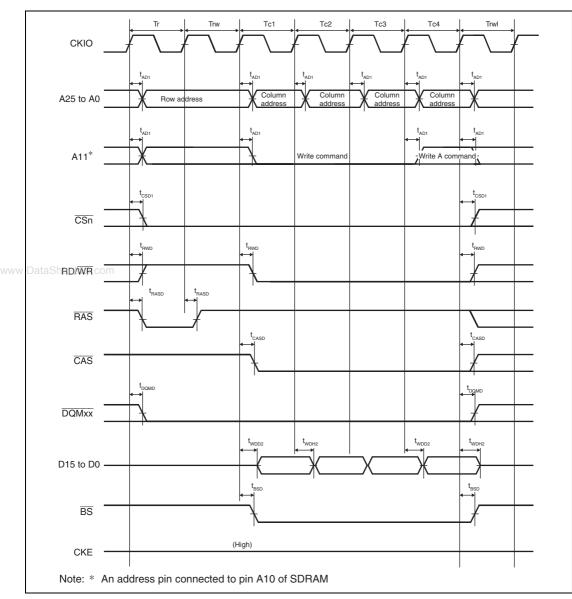

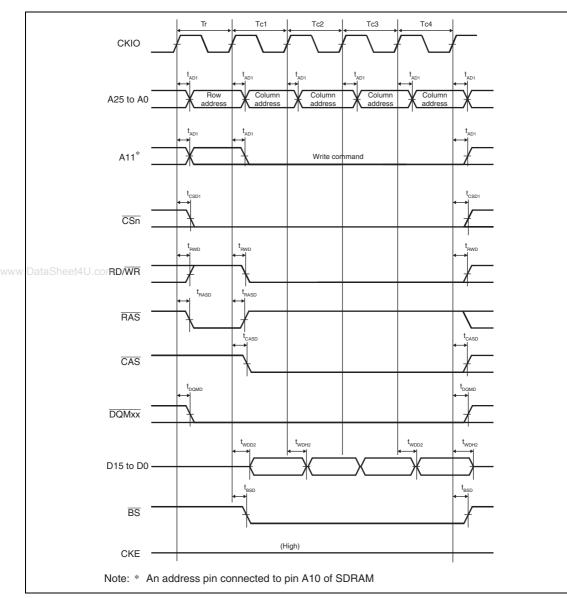

| Figure 7.15   | Basic Timing for Burst Write (Auto Precharge)                      | 166     |

|---------------|--------------------------------------------------------------------|---------|

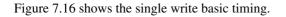

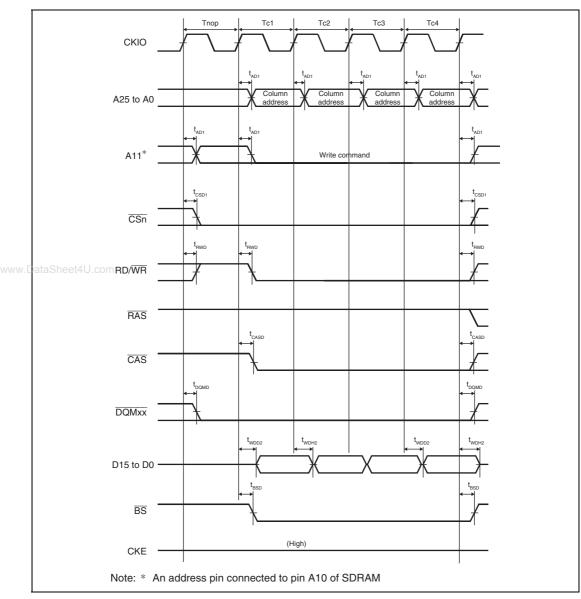

| Figure 7.16   | Basic Timing for Single Write (Auto-Precharge)                     | 167     |

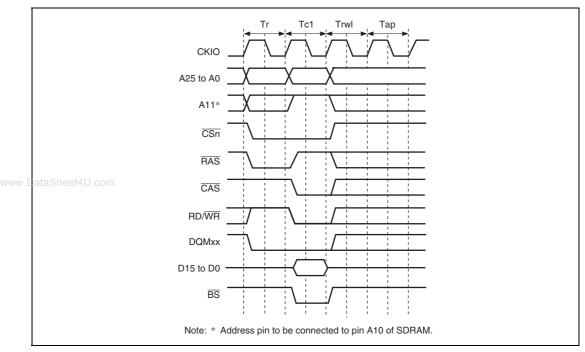

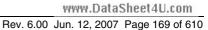

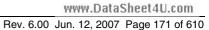

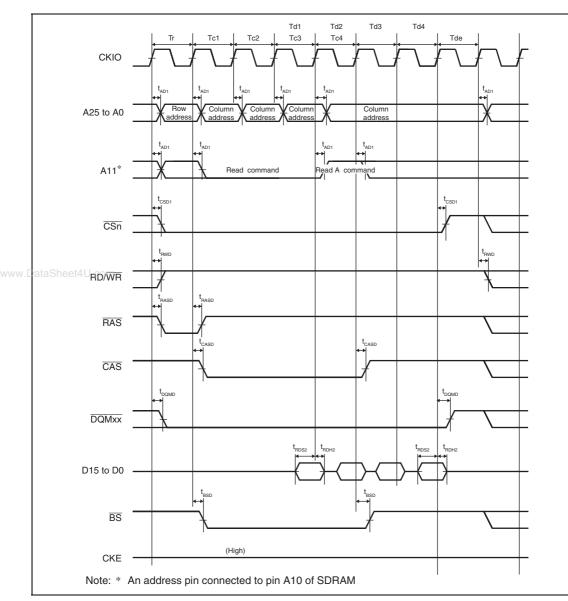

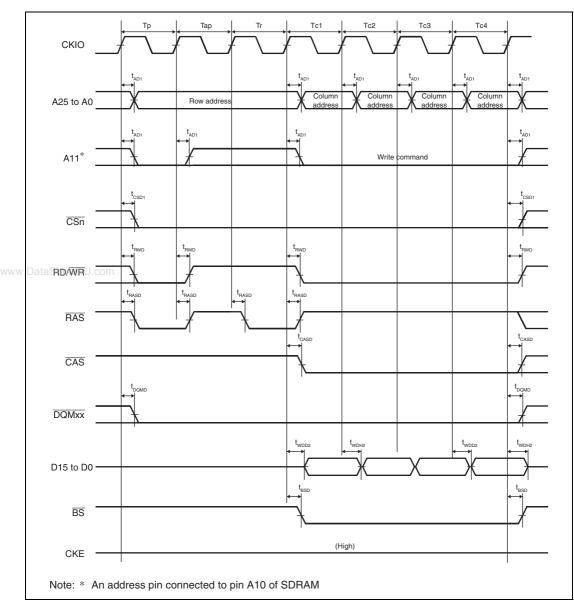

| Figure 7.17   | Burst Read Timing (No Auto Precharge)                              | 169     |

| Figure 7.18   | Burst Read Timing (Bank Active, Same Row Address)                  |         |

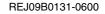

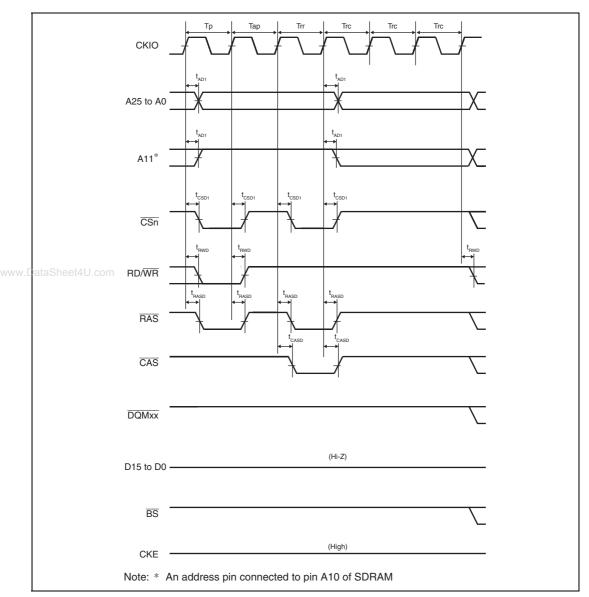

| Figure 7.19   | Burst Read Timing (Bank Active, Different Row Addresses)           | 171     |

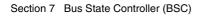

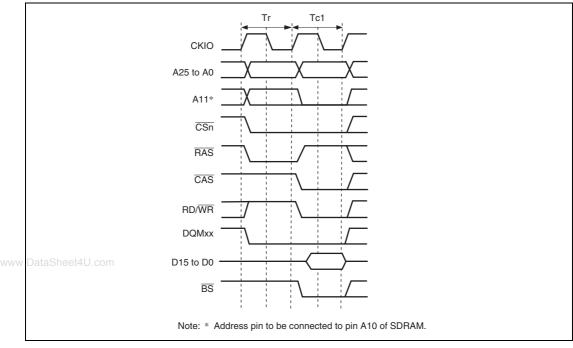

| Figure 7.20   | Single Write Timing (No Auto Precharge)                            | 172     |

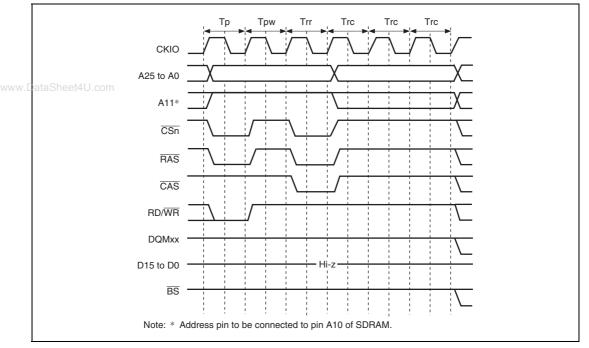

| Figure 7.21   | Single Write Timing (Bank Active, Same Row Address)                |         |

| Figure 7.22   | Single Write Timing (Bank Active, Different Row Addresses)         | 174     |

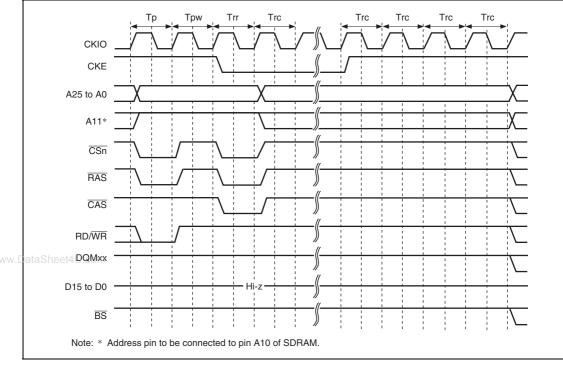

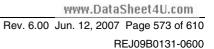

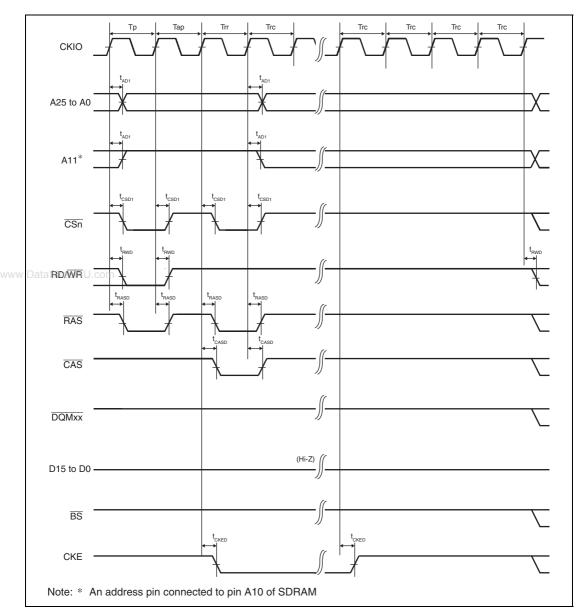

| Figure 7.23   | Auto-Refreshing Timing                                             | 175     |

| Figure 7.24   | Self-Refreshing Timing                                             | 177     |

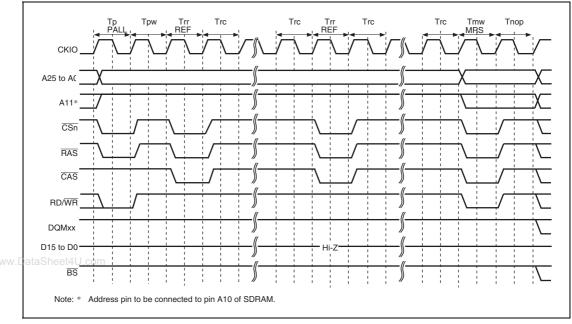

| Figure 7.25   | Write Timing for SDRAM Mode Register (Based on JEDEC)              | 179     |

| Figure 7.26   | Basic Access Timing for Byte-Selection SRAM (BAS = 0)              |         |

| Figure 7.27   | Basic Access Timing for Byte-Selection SRAM (BAS = 1)              |         |

| Figure 7.28   | Wait Timing for Byte-Selection SRAM (BAS = 1) (Software Wait Only) |         |

| Figure 7.29   | Example of Connection with 16-Bit Data-Width Byte-Selection SRAM   |         |

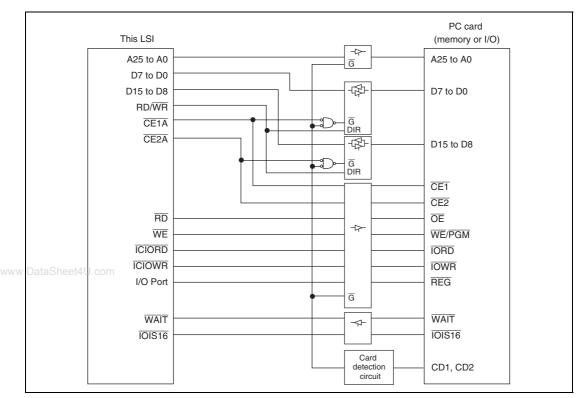

| Figure 7.30   | Example of PCMCIA Interface Connection                             |         |

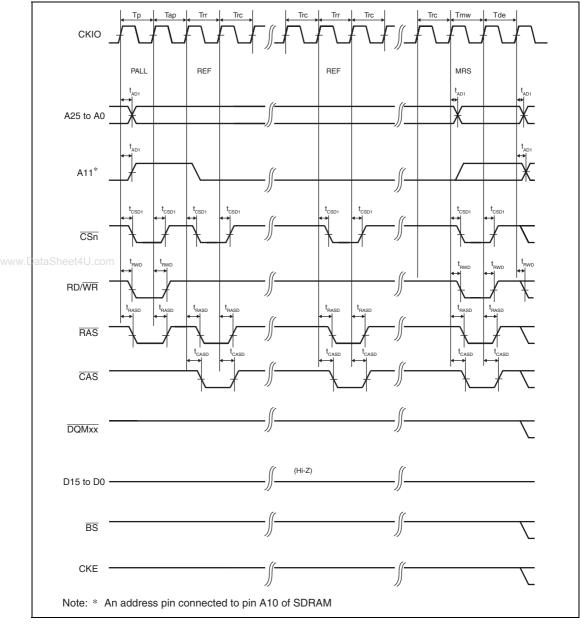

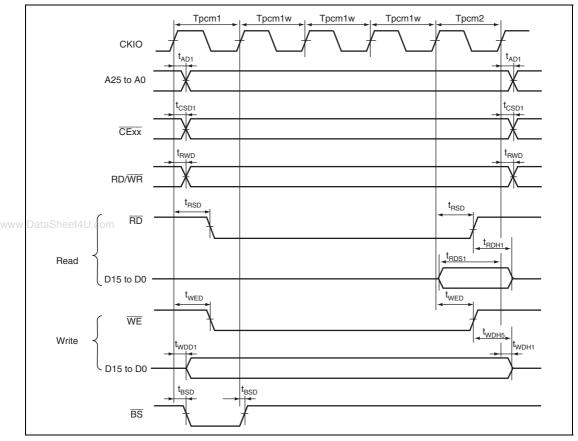

| Figure 7.31   | Basic Access Timing for PCMCIA Memory Card Interface               |         |

| Figure 7.32   | Wait Timing for PCMCIA Memory Card Interface (TED[3:0] = B'0010,   |         |

|               | TEH[3:0] = B'0001, Software Wait = 1, Hardware Wait = 1)           |         |

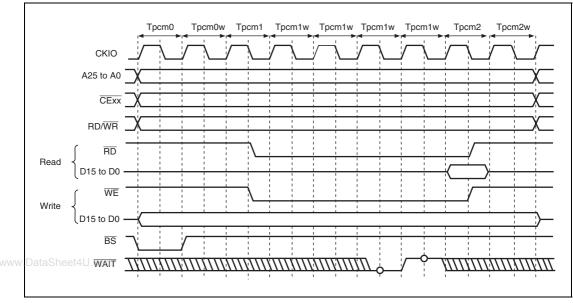

| Figure 7.33   | Example of PCMCIA Space Assignment (CS5BWCR.SA[1:0] = B'10,        |         |

|               | CS6BWCR.SA[1:0] = B'10)                                            |         |

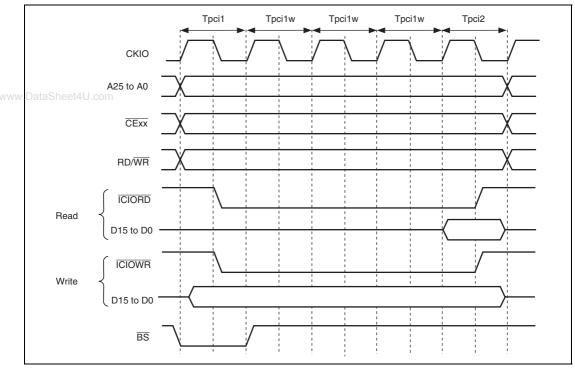

| Figure 7.34   | Basic Timing for PCMCIA I/O Card Interface                         |         |

| Figure 7.35   | Wait Timing for PCMCIA I/O Card Interface (TED[3:0] = B'0010,      |         |

|               | TEH[3:0] = B'0001, Software Wait = 1, Hardware Wait = 1)           |         |

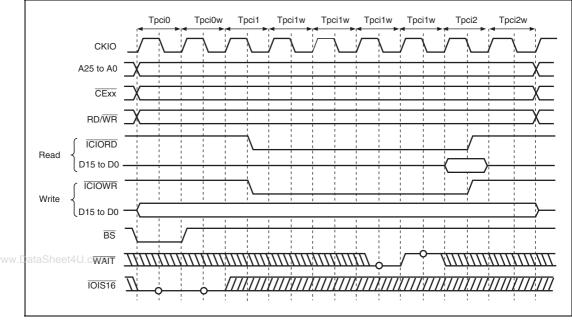

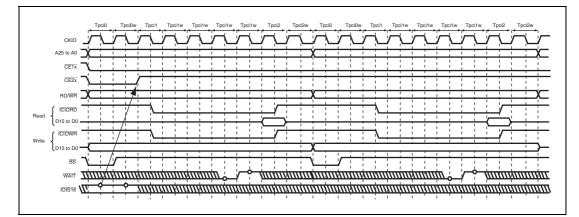

| Figure 7.36   | Timing for Dynamic Bus Sizing of PCMCIA I/O Card Interface         |         |

|               | (TED[3:0] = B'0010, TEH[3:0] = B'0001, Software Waits = 3)         | 189     |

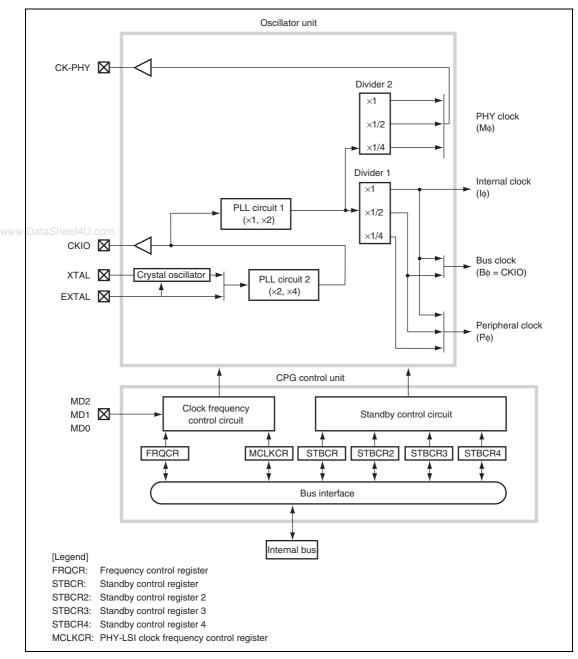

| Section 8 (   | Clock Pulse Generator (CPG)                                        |         |

|               | Block Diagram of CPG                                               | 194     |

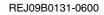

| -             | Points for Attention when Using Crystal Resonator                  |         |

| •             |                                                                    |         |

|               | Vatchdog Timer (WDT)                                               | • • • • |

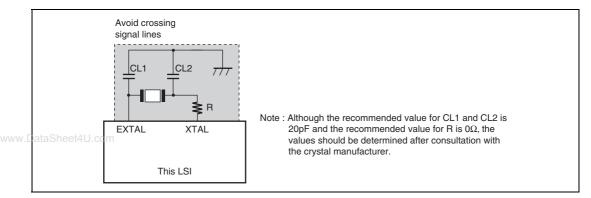

| -             | Block Diagram of WDT                                               |         |

| Figure 9.2    | Writing to WTCNT and WTCSR                                         |         |

| Section 10    | Power-Down Modes                                                   |         |

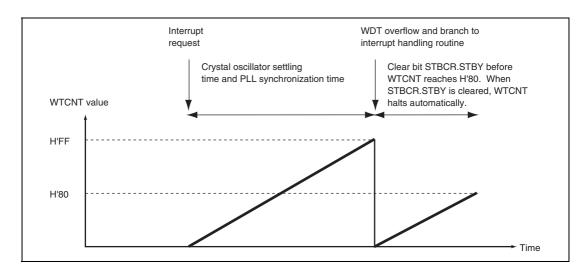

| Figure 10.1   | Canceling Standby Mode with STBY Bit in STBCR                      | 225     |

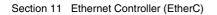

| Section 11    | Ethernet Controller (EtherC)                                       |         |

|               | Configuration of EtherC                                            | 226     |

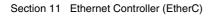

| -             | EtherC Transmitter State Transitions                               |         |

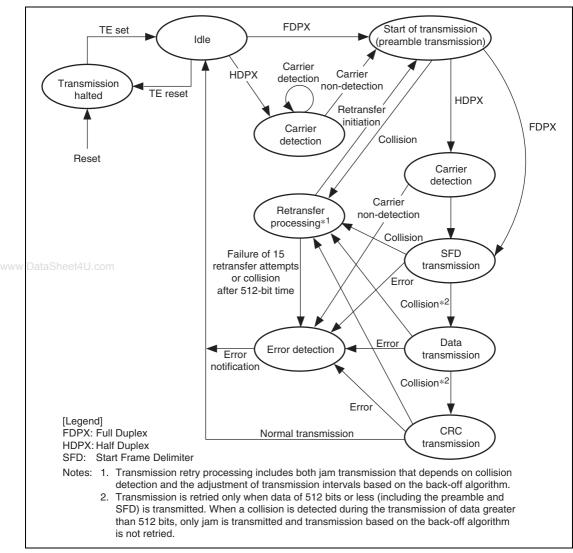

| -             | EtherC Receiver State Transmissions                                |         |

| 1 igui e 11.5 |                                                                    |         |

## RENESAS

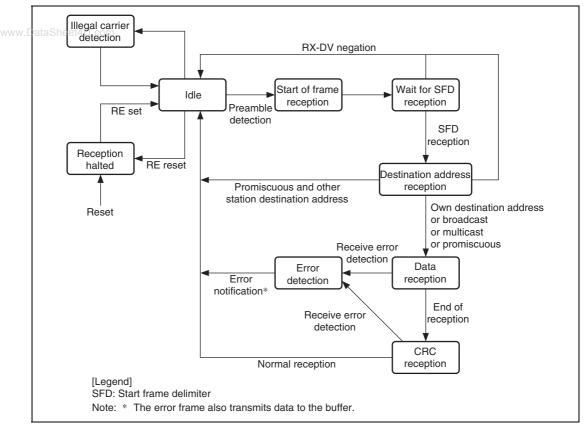

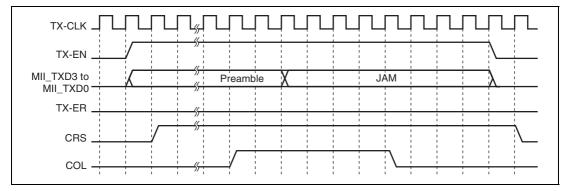

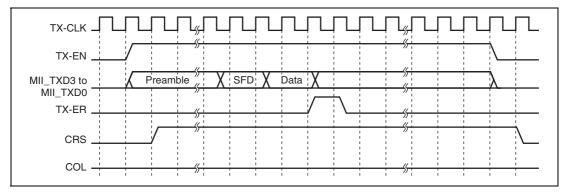

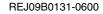

| Figure 11.4 (1) MII Frame Transmit Timing (Normal Transmission)                          |         |

|------------------------------------------------------------------------------------------|---------|

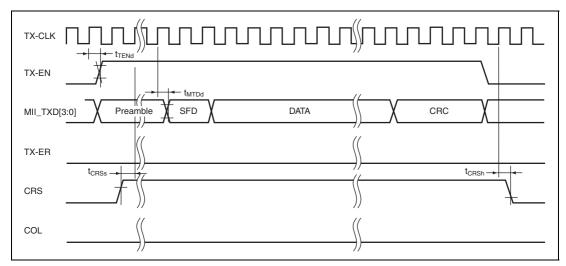

| Figure 11.4 (2) MII Frame Transmit Timing (Collision)                                    |         |

| Figure 11.4 (3) MII Frame Transmit Timing (Transmit Error)                               |         |

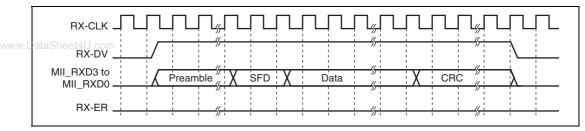

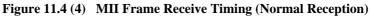

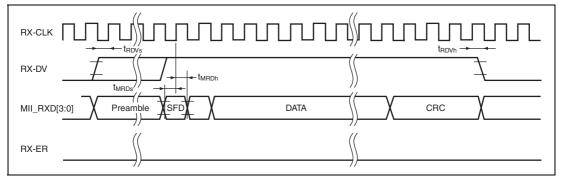

| Figure 11.4 (4) MII Frame Receive Timing (Normal Reception)                              |         |

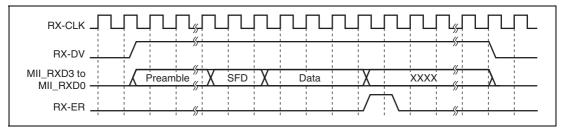

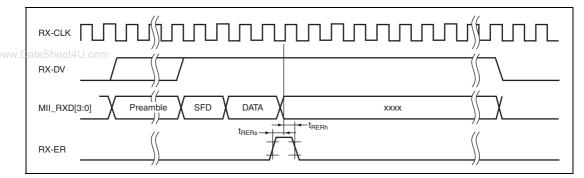

| Figure 11.4 (5) MII Frame Receive Timing (Reception Error (1))                           |         |

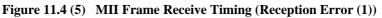

| Figure 11.4 (6) MII Fame Receive Timing (Reception Error (2))                            |         |

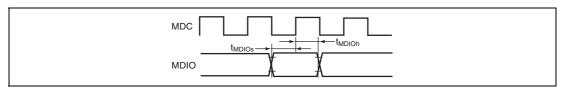

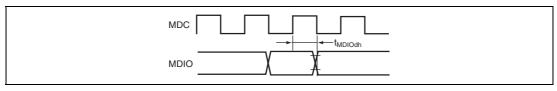

| Figure 11.5 MII Management Frame Format                                                  |         |

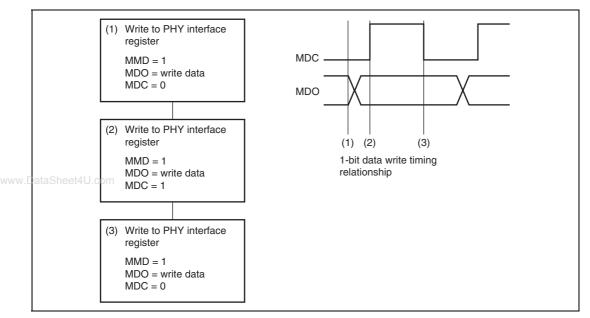

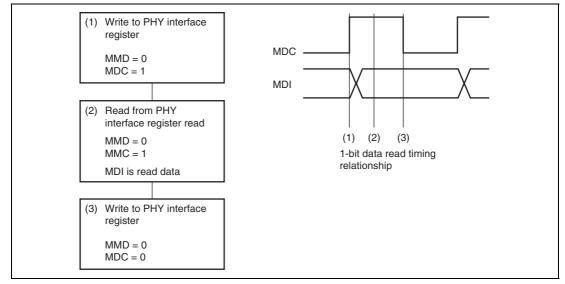

| Figure 11.6 (1) 1-Bit Data Write Flowchart                                               |         |

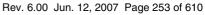

| Figure 11.6 (2) Bus Release Flowchart (TA in Read in Figure 11.5)                        | 254     |

| Figure 11.6 (3) 1-Bit Data Read Flowchart                                                | 254     |

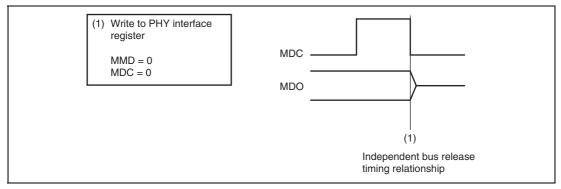

| Figure 11.6 (4) Independent Bus Release Flowchart (IDLE in Write in Figure 11.5)         |         |

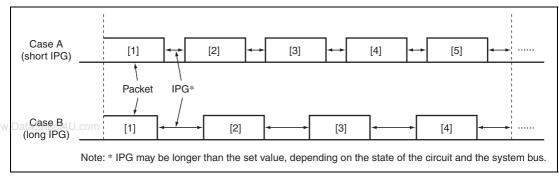

| Figure 11.7 Changing IPG and Transmission Efficiency                                     |         |

| Figure 11.8 Example of Connection to DP83846AVHG                                         |         |

| Section 12 Ethernet Controller Direct Memory Access Controller (E-DMAC)                  |         |

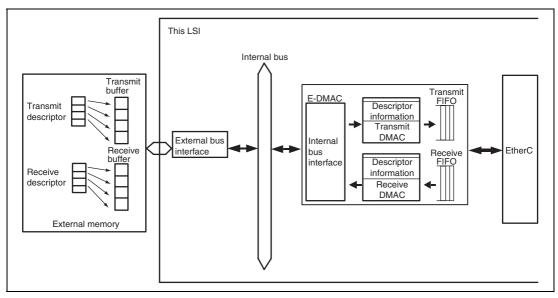

| Da Eigure 42.1 Configuration of E-DMAC, and Descriptors and Buffers                      | 250     |

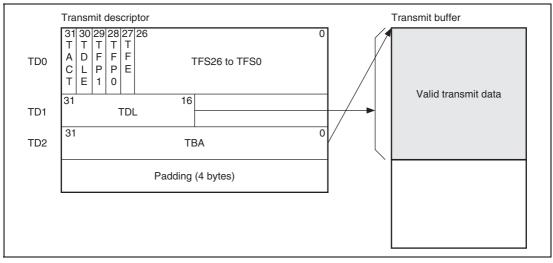

| Figure 12.2 Relationship between Transmit Descriptor and Transmit Buffer                 |         |

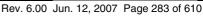

| Figure 12.3 Relationship between Receive Descriptor and Transmit Burler                  |         |

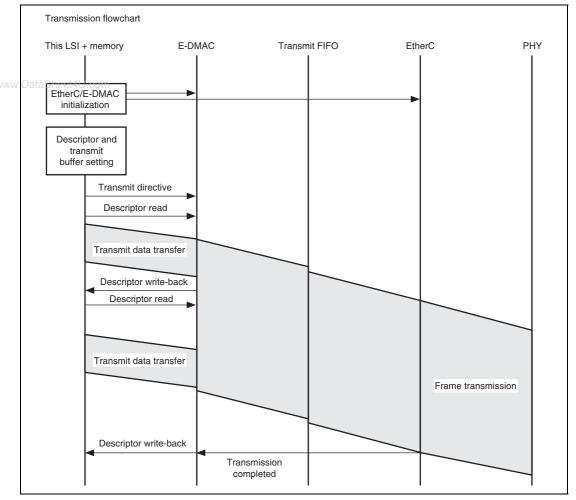

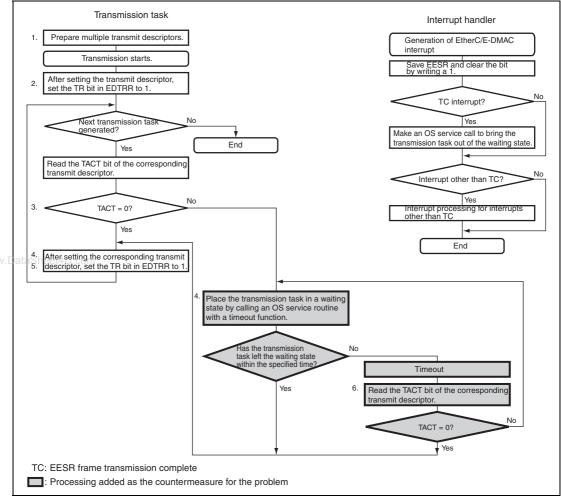

| Figure 12.4 Sample Transmission Flowchart                                                |         |

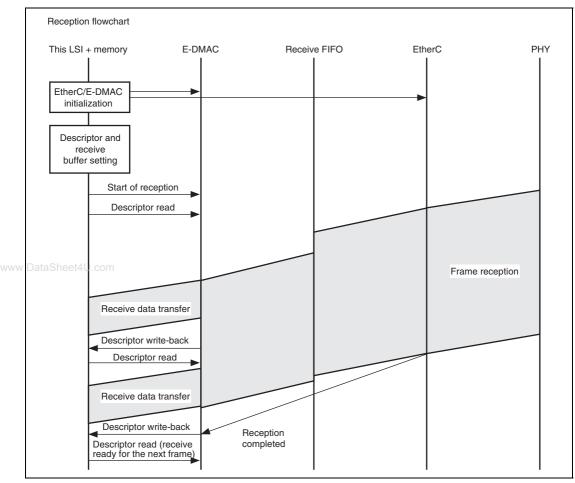

| Figure 12.5 Sample Reception Flowchart                                                   |         |

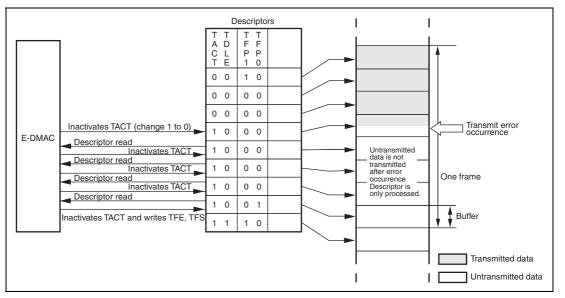

| Figure 12.6 E-DMAC Operation after Transmit Error                                        |         |

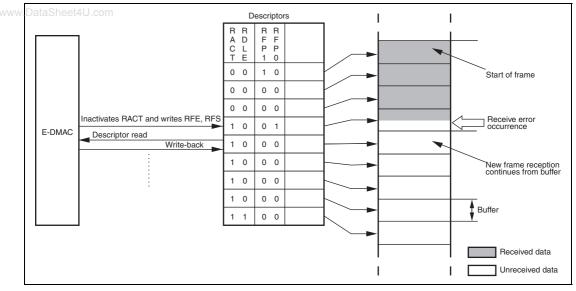

| Figure 12.7 E-DMAC Operation after Receive Error                                         |         |

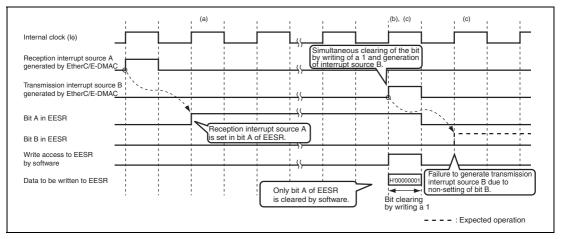

| Figure 12.8 Timing of the Case where Setting of the Interrupt Source Bit in EESR         |         |

| by the E-DMAC Fails                                                                      | 207     |

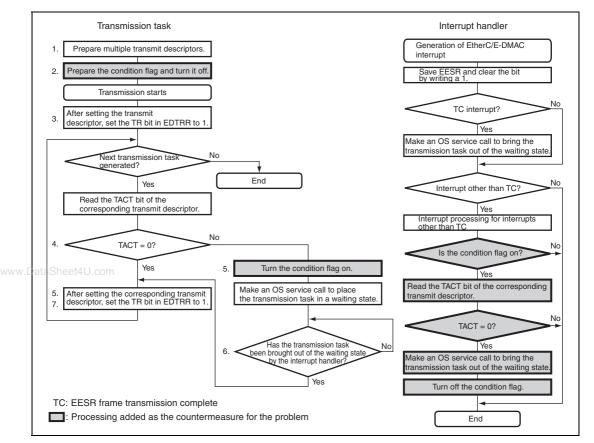

| Figure 12.9 Countermeasure by Monitoring the Transmit Descriptor in Processing           |         |

| of Interrupts Other than the Frame Transmit Complete (TC) Interrupt                      | 202     |

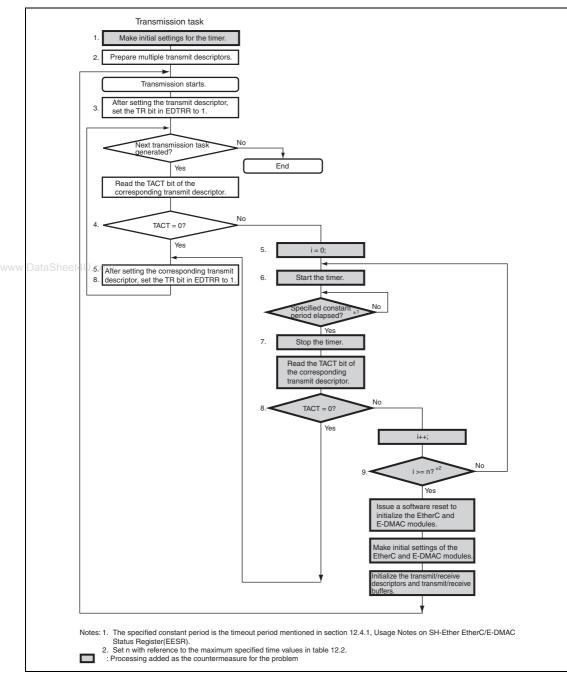

| Figure 12.10 Method of Adding Timeout Processing                                         |         |

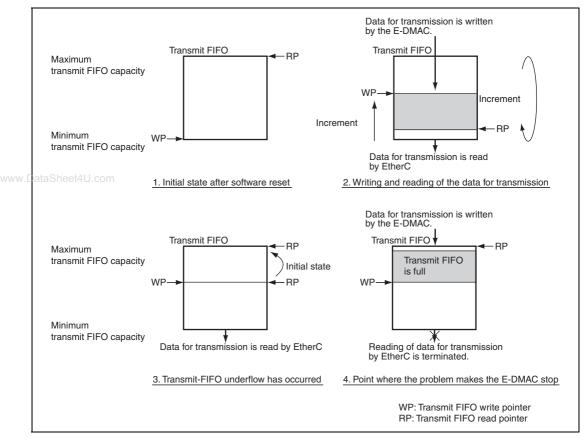

| Figure 12.10 Operation when E-DMAC Stops and the Transmit FIFO                           |         |

| •                                                                                        |         |

| Figure 12.12 Processing Transmission without Handling of the TC Interrupt                |         |

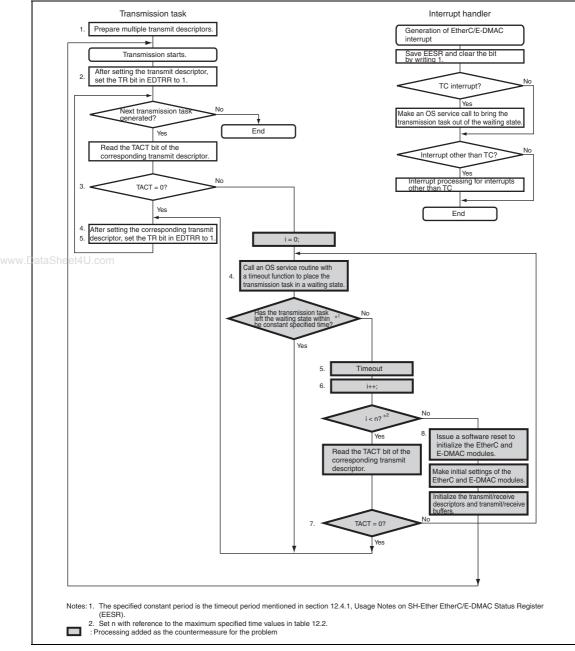

| Figure 12.13 Countermeasure for the Case with TC Interrupt-Driven Software:              |         |

| Addition of Timeout Processing within the Limit Imposed by the<br>Maximum Specified Time | 212     |

| Maximum Specified Time                                                                   |         |

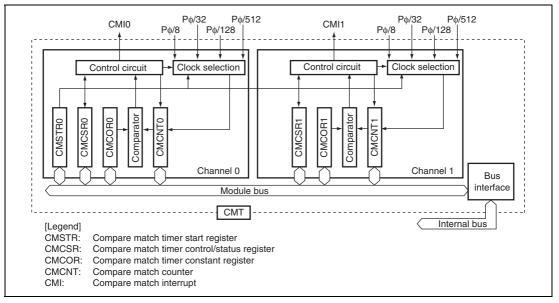

| Section 13 Compare Match Timer (CMT)                                                     |         |

| Figure 13.1 Block Diagram of Compare Match Timer                                         |         |

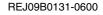

| Figure 13.2 Counter Operation                                                            |         |

| Figure 13.3 Count Timing                                                                 |         |

| Figure 13.4 Timing of CMF Setting                                                        | 320     |

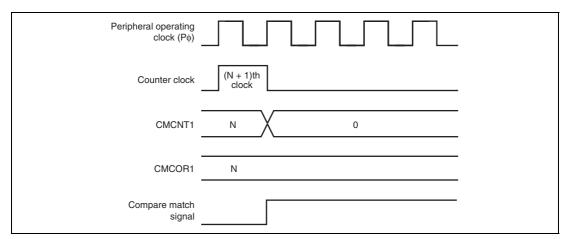

| Figure 13.5 Conflict between Write and Compare-Match Processes of CMCNT                  | 321     |

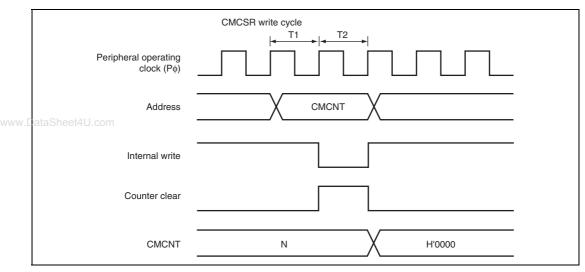

| Figure 13.6 Conflict between Word-Write and Count-Up Processes of CMCNT                  |         |

| Figure 13.7 Conflict between Byte-Write and Count-Up Processes of CMCNT                  |         |

| www.DataSheet                                                                            | 411 com |

Rev. 6.00 Jun. 12, 2007 Page xxiii of xxxii

| Section 14   | Serial Communication Interface with FIFO (SCIF)                      |  |

|--------------|----------------------------------------------------------------------|--|

| Figure 14.1  | Block Diagram of SCIF                                                |  |

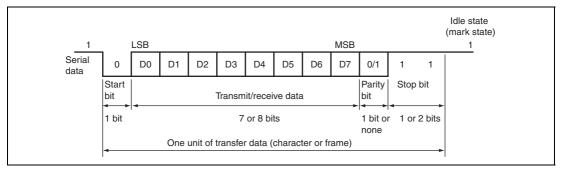

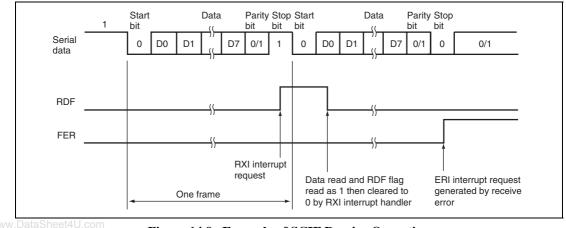

| Figure 14.2  | Example of Data Format in Asynchronous Communication                 |  |

|              | (8-Bit Data with Parity and Two Stop Bits)                           |  |

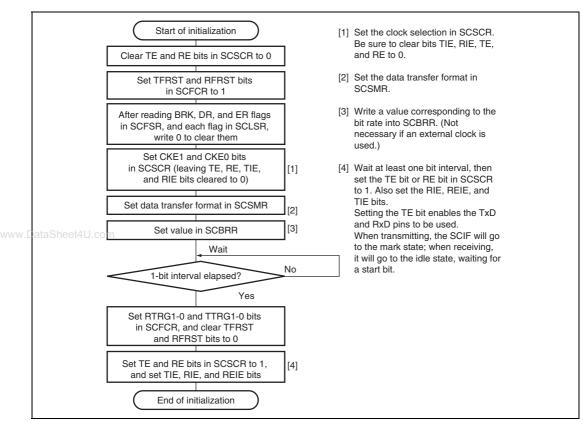

| Figure 14.3  | Sample Flowchart for SCIF Initialization                             |  |

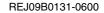

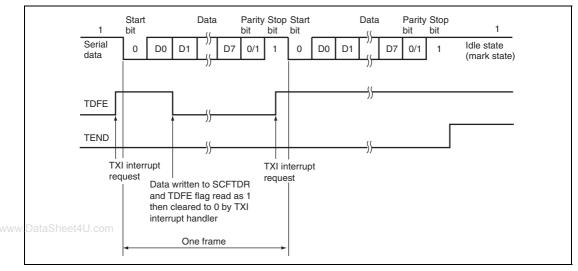

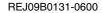

| Figure 14.4  | Sample Flowchart for Transmitting Serial Data                        |  |

| Figure 14.5  | Example of Transmit Operation (8-Bit Data, Parity, One Stop Bit)     |  |

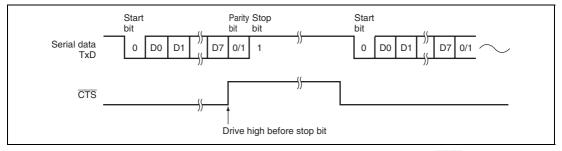

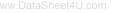

| Figure 14.6  | Example of Operation Using Modem Control (CTS)                       |  |

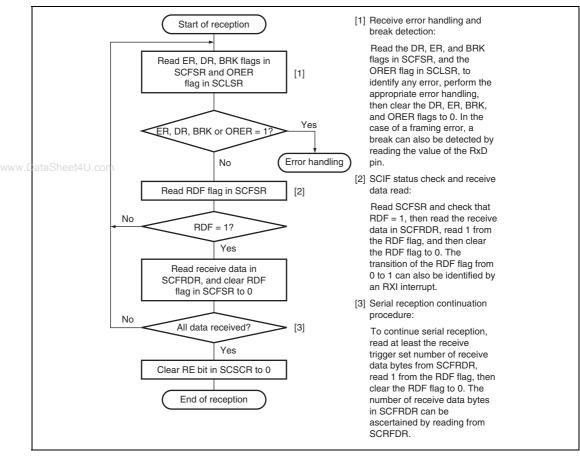

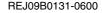

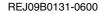

| Figure 14.7  | Sample Flowchart for Receiving Serial Data                           |  |

| Figure 14.8  | Sample Flowchart for Receiving Serial Data (cont)                    |  |

| Figure 14.9  | Example of SCIF Receive Operation (8-Bit Data, Parity, One Stop Bit) |  |

| Figure 14.10 |                                                                      |  |

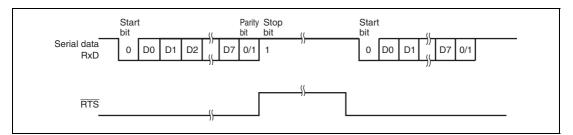

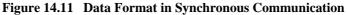

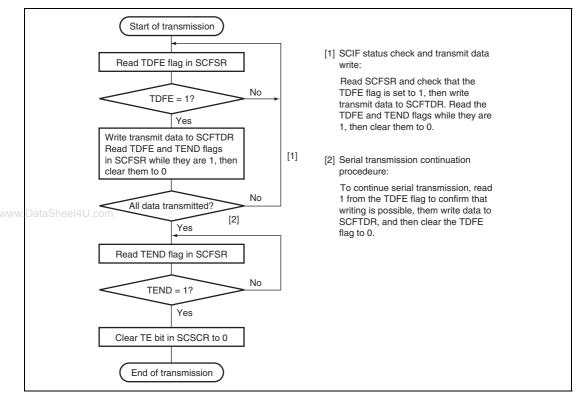

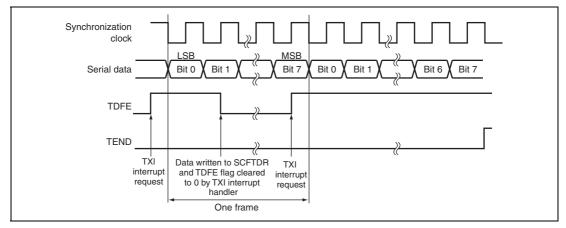

| Figure 14.1  | Data Format in Synchronous Communication                             |  |

| Figure 14.12 | 2 Sample Flowchart for SCIF Initialization                           |  |

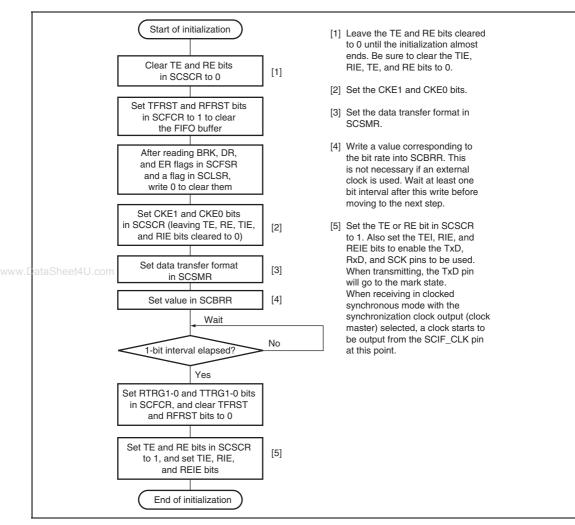

| Figure 14.1. | 3 Sample Flowchart for Transmitting Serial Data                      |  |

| Figure 14.14 | Example of SCIF Transmit Operation                                   |  |

| Figure 14.1: |                                                                      |  |

| Figure 14.10 | 5 Sample Flowchart for Receiving Serial Data (2)                     |  |

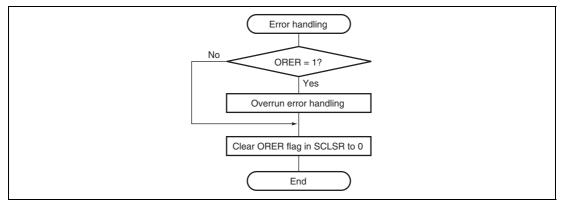

| Figure 14.1  | 7 Example of SCIF Receive Operation                                  |  |

| Figure 14.18 | 3 Sample Flowchart for Transmitting/Receiving Serial Data            |  |

| Figure 14.19 |                                                                      |  |

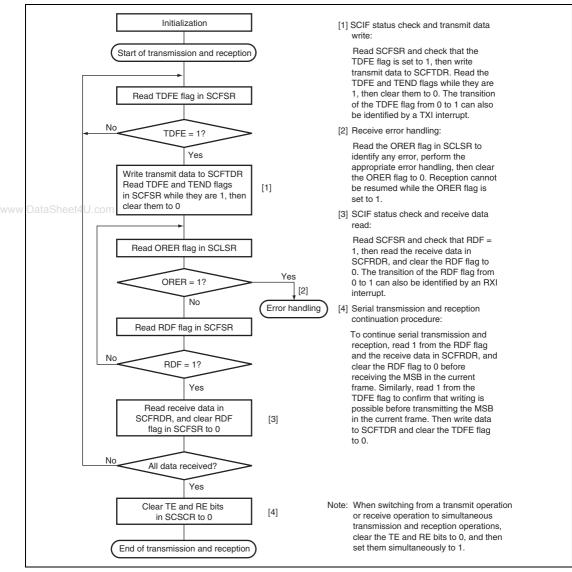

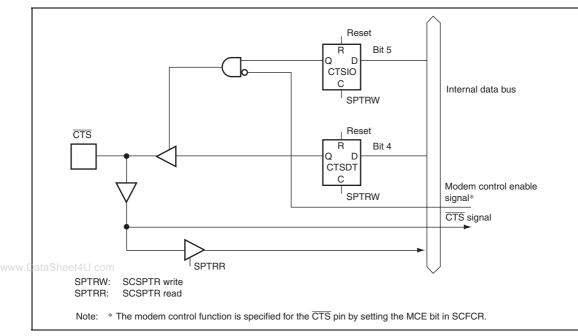

| Figure 14.20 | ) CTSIO Bit, CTSDT bit, and CTS Pin                                  |  |

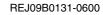

| Figure 14.2  | SCKIO Bit, SCKDT bit, and SCK Pin                                    |  |

| Figure 14.22 |                                                                      |  |

| Figure 14.2  | 3 SPBDT bit and RxD Pin                                              |  |

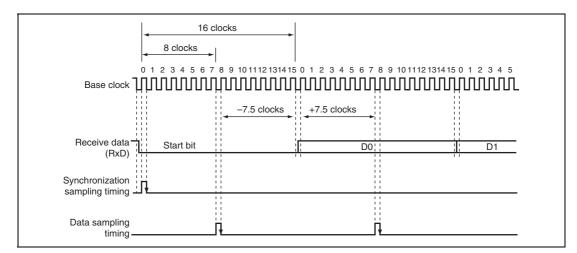

| Figure 14.24 | Receive Data Sampling Timing in Asynchronous Mode                    |  |

| Section 15   | Host Interface (HIF)                                                 |  |

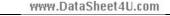

| Figure 15.1  | Block Diagram of HIF                                                 |  |

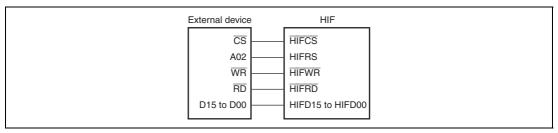

| Figure 15.2  | HIF Connection Example                                               |  |

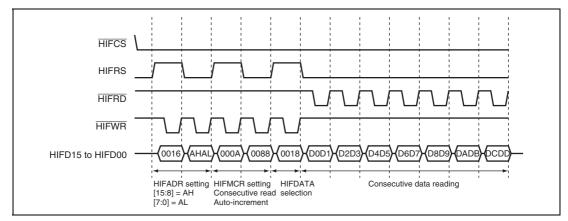

| Figure 15.3  | Basic Timing for HIF Interface                                       |  |

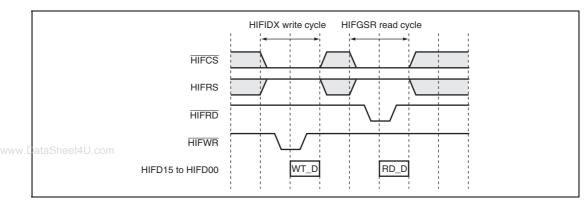

| Figure 15.4  | HIFIDX Write and HIFGSR Read                                         |  |

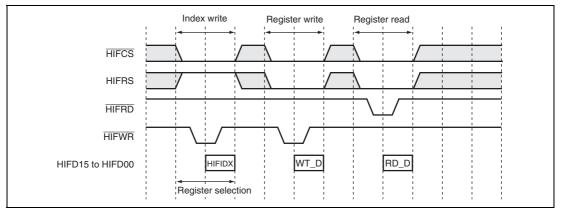

| Figure 15.5  | HIF Register Settings                                                |  |

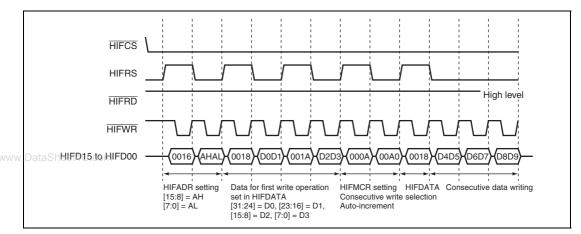

| Figure 15.6  | Consecutive Data Writing to HIFRAM                                   |  |

| Figure 15.7  | Consecutive Data Reading from HIFRAM                                 |  |

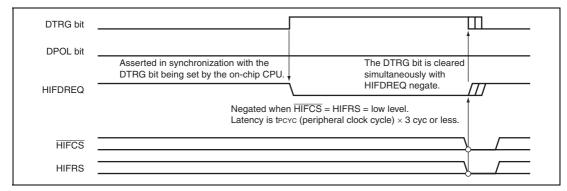

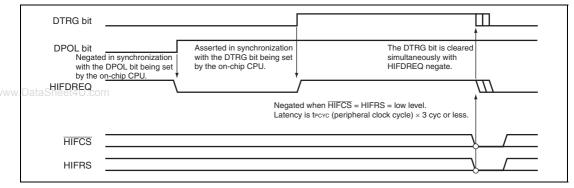

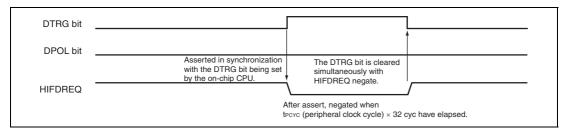

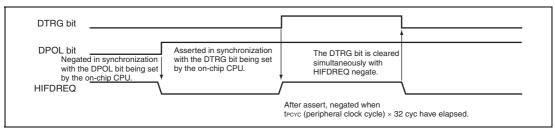

| Figure 15.8  | HIFDREQ Timing (When $DMD = 0$ and $DPOL = 0$ )                      |  |

| Figure 15.9  | HIFDREQ Timing (When DMD = 0 and DPOL = 1)                           |  |

|              | ) HIFDREQ Timing (When DMD = 1 and DPOL = 0)                         |  |

|              | HIFDREQ Timing (When DMD = 1 and DPOL = 1)                           |  |

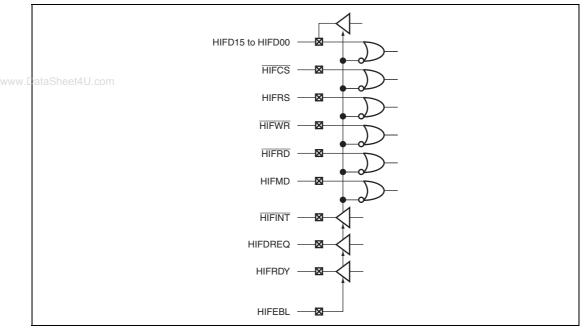

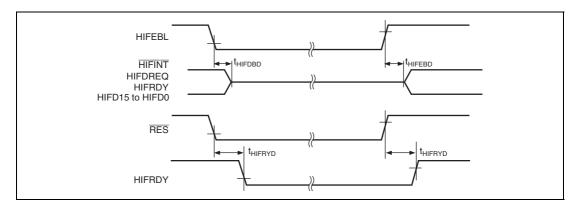

| Figure 15.12 | 2 Image of High-Impedance Control of HIF Pins by HIFEBL Pin          |  |

| Section 17                 | I/O Ports                                                                                                         |       |

|----------------------------|-------------------------------------------------------------------------------------------------------------------|-------|

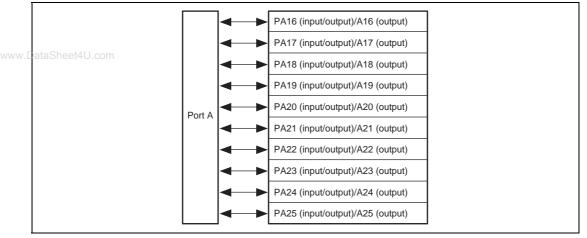

| Figure 17.1                | Port A                                                                                                            | .457  |

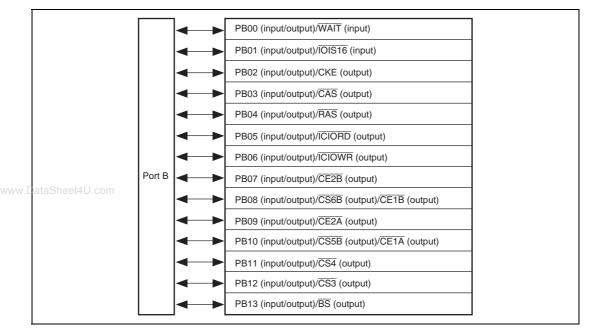

| Figure 17.2                | Port B                                                                                                            | .459  |

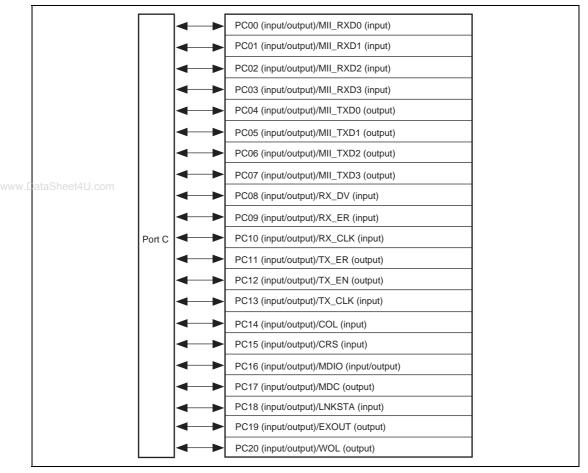

| Figure 17.3                | Port C                                                                                                            | .461  |

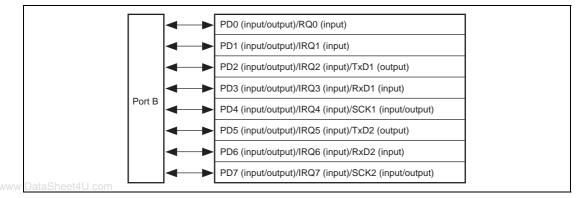

| Figure 17.4                | Port D                                                                                                            | . 464 |

| Figure 17.5                | Port E                                                                                                            | . 466 |

| Section 18                 | User Break Controller (UBC)                                                                                       |       |

|                            | Block Diagram of UBC                                                                                              | .472  |

| •                          | User Debugging Interface (H-UDI)                                                                                  |       |

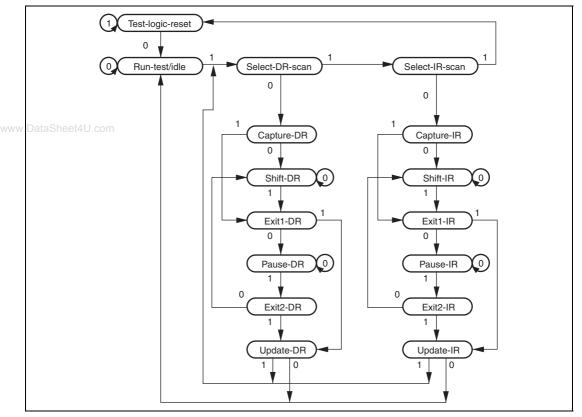

|                            | Block Diagram of H-UDI                                                                                            | 101   |

| -                          | TAP Controller State Transitions                                                                                  |       |