SH79F329 Enhanced 8051 Microprocessor with Analog Front End

#### 1. Features

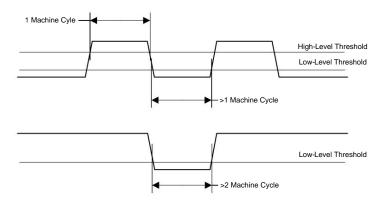

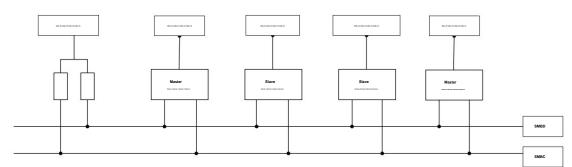

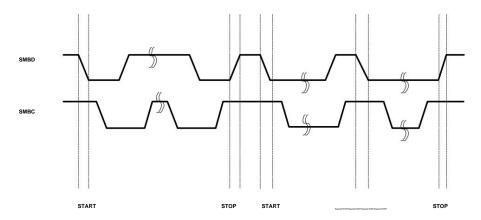

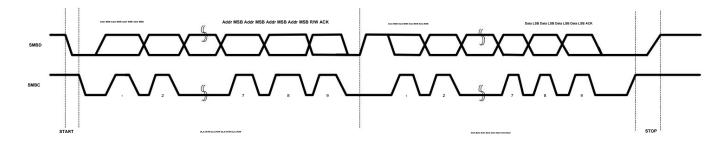

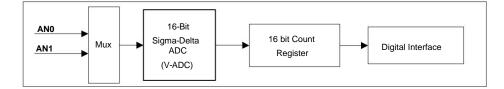

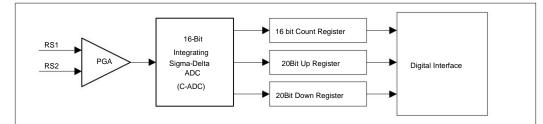

8-bit MCU based on 8051 compatible pipeline instructions ÿ Flash ROM: 32K bytes ÿ RAM: internal 256 bytes, external 1024 bytes ÿ Operating voltage: VVPACK/VBAT = 4.5V - 25V ÿ Oscillator: - Internal RC oscillator: 64KHz - Multiplied to 1MHz, 2MHz, 4MHz, 8MHz ÿ 13 CMOS bidirectional I/O pins ÿ I/O builtin pull-up resistor ÿ 2 open-drain structure I/O pins ÿ 2 8-bit timers T0, T1 ÿ Interrupt sources: - Timer 0, Timer 1 -External interrupts INT1-2 - CADC, VADC, SMBus, SCI, AFE ÿ SMBus interface (master/slave mode) ÿ 2 16-bit ÿ-ÿ analog-todigital converters (ADCs) - CADC: 1 differential input - VADC: 2 single-ended inputs

ÿ Built-in low voltage reset function

LVR voltage: 2.3V (VDD) ÿ CPU

machine cycle: 1 oscillation cycle

ÿ Watchdog Timer (WDT) (Code Option) ÿ Built-in oscillator warm-up

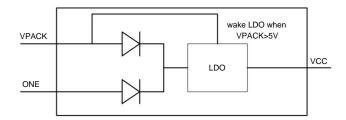

counter ÿ High-voltage analog front end - Builtin 3V, 25mA power regulator

(LDO) - 3 high-voltage output ports - Analog comparator with

programmable threshold and

delay time

- 40mA maximum conduction circuit between VC1-VC5 Low

power working mode: - Idle mode Power down mode

Flash type

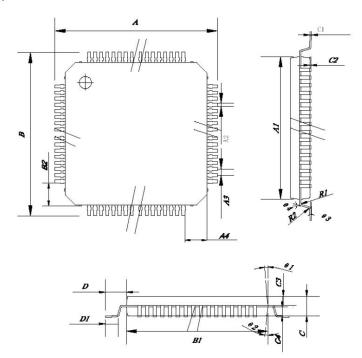

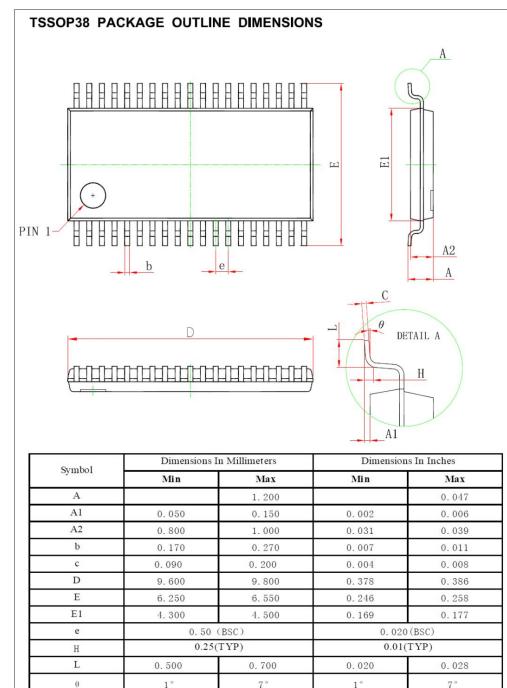

Package: TQFP48,

TSSOP38

### 2. Overview

SH79F329 is a high-speed and high-efficiency 8051 compatible microcontroller. Under the same oscillation frequency, it has the characteristics of faster operation and better performance than the traditional 8051 chip.

1

SH79F329 retains most of the features of the standard 8051 chip, including built-in 256 bytes of RAM and two 8-bit timers and external interrupts INT1 and INT2. In addition,

The SH79F329 also integrates 1024 bytes of RAM. The SH79F329 microcontroller also includes 32K bytes of Flash suitable for programs and data.

SH79F329 not only integrates the SMBus standard communication module, but also integrates two 16-bit ý-ý analog-to-digital converter modules (ADC) and an internal communication module (SCI). To achieve high reliability and low power consumption, the SH79F329 integrates a watchdog timer, has a low voltage reset function, and provides two low power saving modes.

The SH79F329 integrates a high-voltage analog front end (AFE), including 1 AFE interrupt, 1 power regulator, 3 high-voltage output ports that can be used for MOSFET control, 3

analog comparators, 4-way voltage differential input conversion and 4-way internal conduction circuits.

SH79F329

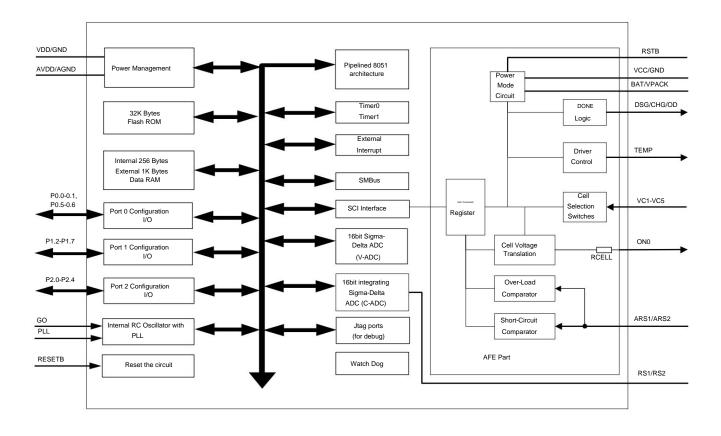

3. Block Diagram

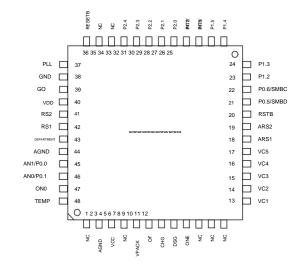

4. Pin configuration

TQFP48 (Total: 48 pins)

TQFP48 pin configuration diagram

TSSOP38 TSSOP38 TSSOP38 TSSOP38 (Total: 38 pins)

TSSOP38 TSSOP38 TSSOP38 TSSOP38 Pin Configuration Diagram

ing, the function written on the outermost side has the highest priority, and the function written on the intermost side has the lowest priority. When a pin is occupied by a high-priority function, it cannot be used as a pin for a low-priority function is allowed. Only when the software prohibits the high-priority function of the pin can the corresponding pin be released for use as a low-priority function written on the outermost side has the high-priority function.

Notice:

Table 4.1 TQFP48 pin functions

| Pin number | Pin Name  | Default function p | n number            | Pin Name   | Default functionality |

|------------|-----------|--------------------|---------------------|------------|-----------------------|

| 2          | AGND      | AGND               | 27                  | P1.6/INT1  | P1.6                  |

| 3          | VCC       | VCC                | 28                  | P1.7/INT2  | P1.7                  |

| 5          | VPACK     | VPACK              | 29                  | P2.0       | P2.0                  |

| 6          | OF        | OF                 | 30                  | P2.1       | P2.1                  |

| 7          | CHG       | CHG                | 31                  | P2.2       | P2.2                  |

| 8          | DSG       | DSG                | 32                  | P2.3       | P2.3                  |

| 9          | ONE       | ONE                | 33                  | P2.4       | P2.4                  |

| 13         | VC1       | VC1                | 36                  | RESETB     | RESETB                |

| 14         | VC2       | VC2                | 37                  | PLL        | PLL                   |

| 15         | VC3       | VC3                | 38                  | GND        | GND                   |

| 16         | VC4       | VC4                | 39                  | GO         | GO                    |

| 17         | VC5       | VC5                | 40                  | VDD        | VDD                   |

| 18         | ARS1      | ARS1               | 41                  | RS2        | RS1                   |

| 19         | ARS2      | ARS2               | 42                  | RS1        | RS1                   |

| 20         | RSTB      | RSTB               | 43                  | DEPARTMENT | DEPARTMENT            |

| 21         | P0.5/SMBD | P0.5               | 44                  | AGND       | AGND                  |

| 22         | P0.6/SMBC | P0.6               | 45                  | P0.0/AN1   | P0.0                  |

| 23         | P1.2      | P1.2               | 46                  | P0.1/AN0   | P0.1                  |

| 24         | P1.3      | P1.3               | 47                  | ON0        | ON0                   |

| 25         | P1.4      | P1.4               | 48                  | ТЕМР       | TEMP                  |

| 26         | P1.5      | P1.5               | 1,4,10-12,<br>34-35 | NC         | NC                    |

Table 4.2 TSSOP38 TSSOP38 TSSOP38 TSSOP38 Pin Function

| Pin number | Pin Name  | Default function p | n number | Pin Name   | Default functionality |

|------------|-----------|--------------------|----------|------------|-----------------------|

| 1          | DSG       | DSG                | 20       | P2.2       | P2.3                  |

| 2          | ONE       | ONE                | 21       | P2.3       | P2.4                  |

| 3          | VC1       | VC1                | 22       | RESETB     | RESETB                |

| 4          | VC2       | VC2                | 23       | PLL        | PLL                   |

| 5          | VC3       | VC3                | 24       | GND        |                       |

| 6          | VC4       | VC4                | 25       | GO         | GO                    |

| 7          | VC5       | VC5                | 26       | VDD        | VDD                   |

| 8          | ARS1      | ARS1               | 27       | RS2        | RS1                   |

| 9          | ARS2      | ARS2               | 28       | RS1        | RS1                   |

| 10         | P0.5/SMBD | P0.5               | 29       | DEPARTMENT | DEPARTMENT            |

| 11         | P0.6/SMBC | P0.6               | 30       | AGND       | AGND                  |

| 12         | P1.2      | P1.2               | 31       | P0.0/AN1   | P0.0                  |

| 13         | P1.3      | P1.3               | 32       | P0.1/AN0   | P0.1                  |

| 14         | P1.4      | P1.4               | 33       | TEMP       | TEMP                  |

| 15         | P1.5      | P1.5               | 34       | AGND       | AGND                  |

| 16         | P1.6/INT1 | P1.6               | 35       | VCC        | VCC                   |

| 17         | P1.7/INT2 | P1.7               | 36 VPACK |            | VPACK                 |

| 18         | P2.1      | P2.0               | 37 OF    |            | OF                    |

| 19         | P2.2      | P2.1               | 38       | СНG        | CHG                   |

## 5. Pin Description

| Pin Number                 | type      | illustrate                                          |

|----------------------------|-----------|-----------------------------------------------------|

| I/O Ports                  |           |                                                     |

| P0.0-P0.1, P0.5-P0.6 P1.2  | I/O 4-bit | bidirectional I/O port                              |

| - P1.7                     | I/O 6-bit | bidirectional I/O port                              |

| P2.0 - P2.4                | I/O 5-bit | bidirectional I/O port                              |

| SMBus Port                 |           |                                                     |

| SMBD                       | I/O SMB   | us communication data line                          |

| SMBC                       | I/O SMB   | us communication clock line                         |

| ADC                        |           |                                                     |

| AN0                        | I VADO    | c single-ended input 0 pin                          |

| AN1                        | I VADO    | c single-ended input 1 pin                          |

| RS1                        | I CADO    | c differential input positive pin                   |

| RS2                        | I CADO    | c differential input negative pin                   |

| Interrupt/Reset/Power Port | -         |                                                     |

| INT1                       | I Exter   | nal interrupt 1 input pin                           |

| INT2                       | I Exter   | nal interrupt 2 input pin                           |

| RESETB                     | l Rese    | pin                                                 |

| GO                         | I Interr  | al oscillation circuit pin                          |

| PLL                        | I frequer | cy multiplication circuit pin                       |

| VDD                        | P Digita  | I power pin                                         |

| GND                        | P Digita  | Il ground pin                                       |

| DEPARTMENT                 | P Analo   | g power pin                                         |

| AGND                       | P Analo   | g ground pin                                        |

| AFE Port                   |           |                                                     |

| VPACK                      | P AFE     | power input pin                                     |

| ONE                        | P AFE     | power input pin                                     |

| VCC                        | P AFE     | power regulator output pin                          |

| AGND                       | P AFE     | analog ground pin                                   |

| CHG                        | O AFE     | nigh voltage output pin                             |

| DSG                        | O AFE     | nigh voltage output pin                             |

| OF                         | O AFE I   | nigh voltage open drain output pin                  |

| RSTB                       | O AFE     | eset output, it is recommended to connect to RESETB |

| VC1                        | I AFE v   | roltage conversion highest input pin                |

| VC2                        | I AFE v   | oltage conversion second high input pin             |

| VC3                        | I AFE V   | roltage conversion third high input pin             |

| VC4                        | IAFE      | roltage conversion fourth high input pin            |

| VC5                        | IAFE      | roltage conversion lowest input pin                 |

| ON0                        | O AFE     | voltage conversion output pin                       |

| TEMP                       | O AFE     | putput pin                                          |

| ARS1                       | I AFE (   | comparator input pin                                |

| ARS2                       | I AFE (   | comparator input pin                                |

Continued from the table above

| Pin Number                                                                                                | type                                         | illustrate                         |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|--|--|--|--|--|--|

| Programmer                                                                                                |                                              |                                    |  |  |  |  |  |  |

| TDOÿP1.2ÿ                                                                                                 | O Debu                                       | g interface: test data output      |  |  |  |  |  |  |

| TMSÿP1.3ÿ                                                                                                 | l debu                                       | oug interface: test mode selection |  |  |  |  |  |  |

| TDİÿP1.4ÿ                                                                                                 | TDIÿP1.4ÿ I Debug interface: test data input |                                    |  |  |  |  |  |  |

| TCKÿP1.5ÿ                                                                                                 | l debu                                       | j interface: test clock input      |  |  |  |  |  |  |

| Notice:<br>When P1.2-1.5 is used as a debugging interface, the original function of P1.2-1.5 is disabled. |                                              |                                    |  |  |  |  |  |  |

## 6. SFR footage

SH79F329 has built-in 256 bytes of direct addressing registers, including general data memory and special function registers (SFR). The SFRs of SH79F329 are as follows : CPU core registers: ACC, B, PSW, SP, DPL, DPH CPU core enhanced registers: AUXC, DPL1, DPH1, INSCON, XPAGE Power clock control register: PCON, SUSLO Flash registers: IB\_CLK0ÿIB\_CLK1ÿIB\_OFFSETÿIB\_DATAÿIB\_CON1ÿIB\_CON2ÿIB\_CON3ÿIB\_CON4ÿ IB\_CON5 Data Page Control Register: XPAGE Watchdog Timer Register: RSTSTAT System clock control register: CLKCON IEN0ÿIEN1ÿIPH0ÿIPL0ÿIPH1ÿIPL1 Interrupt registers: P0ÿP1ÿP2ÿP0CRÿP1CRÿP2CRÿP0PCRÿP1PCRÿP2PCRÿP2SELÿP0OS I/O port registers: TCONÿBTCONÿBT0ÿBT1 Timer register: SMBCONÿSMBSTAÿSMBDATÿSMBADR SMBus Registers: SCICON, SCIDAT, SCIADR SCI Registers: ADCPÿOPDYÿVADCONÿVADC1ÿVADD0ÿCADCONÿCADC1ÿCADD0ÿCAD2ÿCAD1ÿ ADC Registers: CAD0ÿDAD2ÿDAD1ÿDAD0ÿV0OR1ÿV0OR0ÿV0FSR1ÿV0FSR0ÿCOR1ÿCOR0ÿCFSR1ÿCFSR0

## Table 6.1 C51 core SFRs

| Symbolic A | ddress | name                     | PORMOTILVE PORMOTILVE PORMOTILVE PORMOTILVE | No. 7  | No. 6  | No. 5  | No. 4  | No. 3  | No. 2  | No. 1  | No. 0  |

|------------|--------|--------------------------|---------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| ACC        | E0H    | accumulator              | 0000000                                     | ACC.7  | ACC.6  | ACC.5  | ACC.4  | ACC.3  | ACC.2  | ACC.1  | ACC.0  |

| В          | F0H    | B Register               | 0000000                                     | B.7    | B.6    | B.5    | B.4    | B.3    | B.2    | B.1    | B.0    |

| AUXC F1H   |        | C Register               | 0000000                                     | C.7    | C.6    | C.5    | C.4    | C.3    | C.2    | C.1    | C.0    |

| PSW D0H    |        | Program status word      | 0000000                                     | CY     | AC     | F0     | RS1    | RS0    | ov     | F1     | Р      |

| SP         | 81H    | Stack pointer            | 00000111                                    | SP.7   | SP.6   | SP.5   | SP.4   | SP.3   | SP.2   | SP.1   | SP.0   |

| DPL        | 82H    | Data pointer low byte    | 0000000                                     | DPL0.7 | DPL0.6 | DPL0.5 | DPL0.4 | DPL0.3 | DPL0.2 | DPL0.1 | DPL0.0 |

| VAT        | 83H    | Data pointer high byte   | 0000000                                     | DPH0.7 | DPH0.6 | DPH0.5 | DPH0.4 | DPH0.3 | DPH0.2 | DPH0.1 | DPH0.0 |

| DPL1       | 84H    | Data pointer 1 low byte  | 0000000                                     | DPL1.7 | DPL1.6 | DPL1.5 | DPL1.4 | DPL1.3 | DPL1.2 | DPL1.1 | DPL1.0 |

| DPH1       | 85H    | Data pointer 1 high byte | 0000000                                     | DPH1.7 | DPH1.6 | DPH1.5 | DPH1.4 | DPH1.3 | DPH1.2 | DPH1.1 | DPH1.0 |

| INSCON 86H |        | Data pointer selection   | 00-0                                        |        |        |        |        | DIV    | l have | -      | DPS    |

## Table 6.2 Power Clock Control SFRs

| Symbolic A | ddress | name                          | PORMOTELVE PORMOTELVE PORMOTELVE | No. 7        | No. 6           | No. 5            | No. 4            | No. 3 | No. 2 | No. 1 | No. 0 |

|------------|--------|-------------------------------|----------------------------------|--------------|-----------------|------------------|------------------|-------|-------|-------|-------|

| PCON 87H   |        | Power Control                 | 0000                             |              | -               | -                |                  | GF1   | GF0   | PD    | IDL   |

| SUSLO 8EH  |        | Power control protection word | 0000000                          | SUSLO.7 SUSL | O.6 SUSLO.5 SUS | LO.4 SUSLO.3 SUS | SLO.2 SUSLO.1 SU | SLO.0 |       |       |       |

## Table 6.3 Flash Control SFRs

| Symbolic A    | ddress | name                               | PORWOTLUR PORWOTLUR PORWOTLUR PORWOTLUR | No. 7           | No. 6              | No. 5           | No. 4             | No. 3            | No. 2           | No. 1           | No. 0           |

|---------------|--------|------------------------------------|-----------------------------------------|-----------------|--------------------|-----------------|-------------------|------------------|-----------------|-----------------|-----------------|

| IB_CLK0 F9H   |        | Flash Programming Clock Register 0 | 0000000                                 | IB_CLK0.7 IB_C  | K0.6 IB_CLK0.5 IE  | _CLK0.4 IB_CLK0 | 3 IB_CLK0.2 IB_CI | K0.1 IB_CLK0.0   |                 |                 |                 |

| IB_CLK1 FAH   |        | Flash programming clock register 1 | 0000000                                 | IB_CLK1.7 IB_C  | LK1.6 IB_CLK1.5 IE | _CLK1.4 IB_CLK1 | 3 IB_CLK1.2 IB_CI | K1.1 IB_CLK1.0   |                 |                 |                 |

| IB_OFF<br>SET | FBH    | Programmable flash low byte offset | 0000000                                 | IB_OFF<br>SET.7 | IB_OFF<br>SET.6    | IB_OFF<br>SET.5 | IB_OFF<br>SET.4   | IB_OFF<br>SET.3  | IB_OFF<br>SET.2 | IB_OFF<br>SET.1 | IB_OFF<br>SET.0 |

| IB_DATA FCH   |        | Programmable flash data register   | 0000000                                 | IB_DATA.7 IB_D  | ATA.6 IB_DATA.5 I  | B_DATA.4 IB_DAT | A.3 IB_DATA.2 IB_ | DATA.1 IB_DATA.0 |                 |                 |                 |

| IB_CON1 F2H   |        | Flash control register 1           | 0000000                                 | IB_CON1.7 IB_C  | ON1.6 IB_CON1.5    | B_CON1.4 IB_CO  | N1.3 IB_CON1.2 IB | _CON1.1 IB_CON1  | .0              |                 |                 |

| IB_CON2 F3H   |        | flash control register 2           | 00000                                   |                 | -                  |                 | IB_CON2.4 IB_C    | ON2.3 IB_CON2.2  | B_CON2.1 IB_CO  | N2.0            |                 |

| IB_CON3 F4H   |        | flash control register 3           | 0000                                    | -               | -                  |                 |                   | IB_CON3.3 IB_C   | ON3.2 IB_CON3.1 | B_CON3.0        |                 |

| IB_CON4 F5H   |        | Flash control register 4           | 0000                                    |                 | -                  |                 |                   | IB_CON4.3 IB_C   | ON4.2 IB_CON4.1 | B_CON4.0        |                 |

| IB_CON5 F6H   |        | Flash control register 5           | 0000                                    | -               |                    |                 | -                 | IB_CON5.3 IB_C   | ON5.2 IB_CON5.1 | B_CON5.0        |                 |

| XPAGE F7H     |        | flash page register                | 0000000                                 | XPAGE.7 XPAG    | E.6 XPAGE.5 XPA    | GE.4 XPAGE.3 XP | AGE.2 XPAGE.1 XI  | PAGE.0           |                 |                 | 6               |

# Table 6.4 WDT SFR

| Symbolic Ac | ddress       | name                | PORVMOTILINE PORVMOTILINE PORVMOTILINE PORVMOTILINE | No. 7 | No. 6 | No. 5 | No. 4 | No. 3 | No. 2 | No. 1 | No. 0 |

|-------------|--------------|---------------------|-----------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| RSTSTAT B1H | Watchdog tim | er control register | *-***000                                            | WDOF  | -     | PORF  | LVRF  | CLRF  | WDT2  | WDT.1 | WDT.0 |

Note: \* indicates the reset value in the RSTSTAT register for different reset situations. For details, see the WDT section.

# Table 6.5 Clock Control SFR

| Symbolic Ac | dress | name                   | PORMOTILIE PORMOTILIE PORMOTILIE PORMOTILIE | No. 7 | No. 6 | No. 5 | No. 4 | No. 3  | No. 2 | No. 1 | No. 0 |

|-------------|-------|------------------------|---------------------------------------------|-------|-------|-------|-------|--------|-------|-------|-------|

| CLKCON B2H  |       | System clock selection | 0000                                        | -     | -     | -     | -     | PLLCON | FS2   | FS1   | FS0   |

# Table 6.6 Interrupt SFRs

| Symbolic Ac | dress | name                                  | PORMOTELVR PORMOTELVR PORMOTELVR | No. 7 | No. 6       | No. 5    | No. 4 | No. 3 | No. 2 | No. 1      | No. 0 |

|-------------|-------|---------------------------------------|----------------------------------|-------|-------------|----------|-------|-------|-------|------------|-------|

| IEN0 A8H    |       | Interrupt Enable Control 0            | 0000000                          | EA    | EVADC       | ECADC    | ESMB  | ET1   | EX1   | ET0        | EAFE  |

| IEN1        | A9H   | Interrupt Enable Control 1            | 00                               |       | -           | -        |       |       |       | YOU GO OUT | EX2   |

| IPH0        | B4H   | Interrupt priority control high bit 0 | -0000000                         |       | PVADCH PCAD | CH PSMBH |       | PT1H  | PX1H  | PT0H       | PAFEH |

| IPL0        | B8H   | Interrupt priority control low bit 0  | -0000000                         |       | PVADCL PCAD | H PSMBL  |       | PT1L  | PX1L  | PTOL       | PAFEL |

| IPH1        | B5H   | Interrupt priority control high bit 1 | 00                               |       |             | -        | -     |       | -     | PSCIH      | PX2H  |

| IPL1        | B9H   | Interrupt priority control low bit 1  | 00                               |       | -           | -        | -     |       | -     | PSCIL      | PX2L  |

## Table 6.7 Port SFRs

| Symbolic Ac | dress | name                                  | PORMOTILIR PORMOTILIR PORMOTILIR PORMOTILIR | No. 7         | No. 6            | No. 5            | No. 4         | No. 3            | No. 2      | No. 1         | No. 0   |

|-------------|-------|---------------------------------------|---------------------------------------------|---------------|------------------|------------------|---------------|------------------|------------|---------------|---------|

| P0          | 80H   | 8-bit port 0                          | -0000                                       | -             | P0.6             | P0.5             |               |                  | -          | P0.1          | P0.0    |

| P1          | 90H   | 8-bit port 1                          | 00000                                       | P1.7          | P1.6             | P1.5             | P1.4          | P1.3             | P1.2       | -             |         |

| P2          | AH    | 8-bit port 2                          | 00000                                       | -             | -                |                  | P2.4          | P2.3             | P2.2       | P2.1          | P2.0    |

| P0CR E1H    |       | Port 0 input/output direction control | -0000                                       | -             | P0CR.6           | P0CR.5           |               | ·                | ·          | P0CR.1        | P0CR.0  |

| P1CR E2H    |       | Port 1 input/output direction control | 00000                                       | P1CR.7        | P1CR.6           | P1CR.5           | P1CR.4        | P1CR.3           | P1CR.2     | -             |         |

| P2CR E3H    |       | Port 2 input/output direction control | 00000                                       |               |                  |                  | P2CR.4        | P2CR.3           | P2CR.2     | P2CR.1        | P2CR.0  |

| P0PCR E9H   |       | Port 0 internal pull-up enables       | 00                                          | -             |                  |                  |               |                  | ·          | P0PCR.1 P0PCF | 1.0     |

| P1PCR EAH   |       | Port 1 internal pull-up enables       | 00000                                       | P1PCR.7 P1PCF | .6 P1PCR.5 P1PCR | .4 P1PCR.3 P1PCR | 2             |                  |            | -             |         |

| P2PCR EBH   |       | Port 2 internal pull-up allows        | 00000                                       | -             |                  |                  | P2PCR.4 P2PCF | .3 P2PCR.2 P2PCR | .1 P2PCR.0 |               |         |

| P2SEL EEH   |       | Port 2 output function selection      | 00000                                       | -             |                  |                  | P2SEL.4       | P2SEL.3 P2SEL    | .2         | P2SEL.1       | P2SEL.0 |

| P0OS EFH    |       | Port 0 output function selection      | 0000                                        | -             | -                |                  |               | SDAP             | CLKP       | SMBDP SMBCF   |         |

# Table 6.8 Timer SFRs

| Symbolic  | Address | name                             | PORMOTILVE PORMOTILVE PORMOTILVE PORMOTILVE | No. 7 | No. 6  | No. 5  | No. 4  | No. 3 | No. 2  | No. 1  | No. 0  |

|-----------|---------|----------------------------------|---------------------------------------------|-------|--------|--------|--------|-------|--------|--------|--------|

| TCON 88H  |         | Timer Interrupt Control Register | 0000000                                     | IBT1  | IBT0   | IE2    | IT2    | IE1   | IT1    | AFEIF  | AFEM   |

| BTCON A2H | 1       | Timer Mode Register              | 0000000                                     | ENBT1 | BT1M.2 | BT1M.1 | BT1M.0 | ENBT0 | BT0M.2 | BT0M.1 | BT0M.0 |

| BT1       | A3H     | Timer 1 Control Register         | 0000000                                     | BT1.7 | BT1.6  | BT1.5  | BT1.4  | BT1.3 | BT1.2  | BT1.1  | BT1.0  |

| BT0       | A4H     | Timer 0 Control Register         | 0000000                                     | BT0.7 | BT0.6  | BT0.5  | BT0.4  | BT0.3 | BT0.2  | BT0.1  | BT0.0  |

# Table 6.9 SMBus SFRs

| Symbolic A | Address | name                    | PORWOTLVR FORWOTLVR PORWOTLVR | No. 7          | No. 6         | No. 5         | No. 4         | No. 3         | No. 2   | No. 1   | No. 0      |

|------------|---------|-------------------------|-------------------------------|----------------|---------------|---------------|---------------|---------------|---------|---------|------------|

| SMBCON C1  | ł       | SMBus Control Registers | 0000000                       | ALL            | ENSMB         | STA           | WHAT          | AND           | AA      | TFREE   | FREE       |

| SMBSTA C2H | ±       | SMBus Status Register   | 11111000 SMBS                 | A.7 SMBSTA.6 S | MBSTA.5 SMBST | A.4 SMBSTA.3  |               |               | CR.1    | CR.0    | THIS IS IT |

| SMBADR C3H | Ŧ       | SMBus Data Register     | 0000000                       | SLAVE.6        | SLAVE.5       | SLAVE.4       | SLAVE.3       | SLAVE.2       | SLAVE.1 | SLAVE.0 | GC         |

| SMRDAT C4  | Ŧ       | SMBus Address Register  | 00000000 SMBD                 | T.7 SMBDAT.6 S | MBDAT .5 SMBD | AT.4 SMBDAT.3 | SMBDAT.2 SMBD | AT.1 SMBDAT.0 |         |         |            |

# Table 6.10 SCI SFRs

| Symbolic A | ddress | name                 | PORMOTALUR PORMOTALUR PORMOTALUR PORMOTALUR | No. 7  | No. 6  | No. 5  | No. 4  | No. 3      | No. 2           | No. 1   | No. 0      |

|------------|--------|----------------------|---------------------------------------------|--------|--------|--------|--------|------------|-----------------|---------|------------|

| SCICON C5H |        | SCI Control Register | 000000                                      | SCIEN  | SCIF   | -      | -      | SCIRW SCIS | TA.2 SCISTA.1 S | CISTA.0 |            |

| SCIADR C6H |        | SCI Address Register | 0000000                                     | SCIA.6 | SCIA.5 | SCIA.4 | SCIA.3 | SCIA.2     | SCIA.1          | SCIA.0  | Read/Write |

| SCIDAT C7H |        | SCI Data Register    | 0000000                                     | SCID.7 | SCID.6 | SCID.5 | SCID.4 | SCID.3     | SCID.2          | SCID.1  | SCID.0     |

# Table 6.11 ADC SFRs

| Symbolic A | ddress      | name                                            | PORMOTELIN PORMOTELIN PORMOTELIN PORMOTELIN | No. 7         | No. 6            | No. 5           | No. 4           | No. 3        | No. 2   | No. 1   | No. 0    |

|------------|-------------|-------------------------------------------------|---------------------------------------------|---------------|------------------|-----------------|-----------------|--------------|---------|---------|----------|

| ADCP E7H   |             | VADC Channel Configuration Register             | 00                                          | -             | -                | -               | -               | -            | -       | AN0P    | AN1P     |

| OPDY E6H   | ADC clock   | lelay control register                          | 0000                                        | -             | -                | -               | -               | OPDY.3       | OPDY.2  | OPDY.1  | OPDY.0   |

| VADCON D9H |             | VADC Control Register                           | 0000000                                     | VADCEN VAD    | CIF              | SCH             | VOF             | VCE          | VCR1    | VCR0    | NCH      |

| VADC1 IS D | DNE         | VADC High Byte Register                         | 0000000                                     | VADC.15 VAD   | C.14 VADC.13 VA  | DC.12 VADC.11 V | ADC.10 VADC.9 \ | ADC.8        |         |         |          |

| VADC0 DBH  |             | VADC Low Byte Register                          | 0000000                                     | VADC.7 VADO   | .6               | GUIDE.5         | GUIDE.4         | GUIDE.3      | GUIDE.2 | GUIDE.1 | DRIVER.0 |

| CADCON DC  | H           | CADC Control Register                           | 000-000                                     | CADCEN CAD    | CIF              | MODE            |                 | COF          | CCE     | CCR1    | CCR0     |

| CADC1DDH   |             | CADC High Byte Register                         | 0000000                                     | CADC.15 CAD   | C.14 CADC.13 CA  | DC.12 CADC.11 ( | ADC.10 CADC.9   |              |         |         | CADC.8   |

| CADC0 DEH  |             | CADC Low Byte Register                          | 0000000                                     | CADC.7        | CADC.6           | CADC.5          | CADC.4          | CADC.3 CAD   | C.2     | CADC.1  | CADC.0   |

| UAD2 D1H   | CADC posit  | ive accumulation register high byte             | 0000                                        | -             | -                |                 |                 | UAD.19       | UAD.18  | UAD.17  | UAD.16   |

| UAD1       | D2H CA      | DC positive accumulation register second high b | /te 00000000                                | UAD.15        | UAD.14           | UAD.13          | UAD.12          | UAD.11       | UAD.10  | UAD.9   | UAD.8    |

| UAD0 D3H   | CADC posit  | ive accumulation register low byte 00000000     |                                             | UAD.7         | UAD.6            | UAD.5           | UAD.4           | UAD.3        | UAD.2   | UAD.1   | UAD.0    |

| DAD2 D4H   | CADC nega   | tive accumulation register high byte            | 0000                                        | -             |                  | -               |                 | DAD.19       | DAD.18  | DAD.17  | DAD.16   |

| DAD1       | D5H CA      | DC negative accumulation register second high t | yte 00000000                                | DAD.15        | DAD.14           | DAD.13          | DAD.12          | DAD.11       | DAD.10  | DAD.9   | DAD.8    |

| DAD0 D6H   | CADC nega   | tive accumulation register low byte 00000000    |                                             | DAD.7         | DAD.6            | DAD.5           | DAD.4           | DAD.3        | DAD.2   | DAD.1   | DAD.0    |

| V0OR1 CDH  | VADC offs   | et register high byte                           | 0000000                                     | V0OR.15 V0O   | R.14 V0OR.13 V00 | R.12 V00R.11 V  | OR.10           |              |         | V0OR.9  | V0OR.8   |

| V0OR0 CEH  | VADC offse  | t register low byte                             | 0000000                                     | V0OR.7        | V0OR.6           | V0OR.5          | V0OR.4          | V0OR.3       | V0OR.2  | V0OR.1  | V0OR.0   |

| V0FSR1 CFH | VADC full s | cale calibration register high byte 00000000    |                                             | V0FSR.15 V0FS | R.14 V0FSR.13 \  | 0FSR.12 V0FSR.  | 11 V0FSR.10 V0F | SR.9 V0FSR.8 |         |         |          |

| V0FSR0 D7H | VADC full s | cale calibration register low byte 00000000     |                                             | V0FSR.7 V0FS  | R.6 V0FSR.5 V0F  | SR.4 V0FSR.3 V0 | FSR.2 V0FSR.1   |              |         |         | V0FSR.0  |

| COR1 BCH   |             | CADC Offset Register High Byte                  | 0000000                                     | COR.15        | COR.14           | COR.13          | COR.12          | COR.11       | COR.10  | COR.9   | COR.8    |

| COR0 BDH   |             | CADC Offset Register Low Byte                   | 0000000                                     | COR.7         | COR.6            | COR.5           | COR.4           | COR.3        | COR.2   | COR.1   | COR.0    |

| CFSR1 BEH  | CADC full s | cale calibration register high byte 00000000    |                                             | CFSR.15 CFS   | R.14 CFSR.13 CF  | R.12 CFSR.11 C  | FSR.10          |              |         | CFSR.9  | CFSR.8   |

| CFSR0 BFH  | CADC full s | cale calibration register low byte 00000000     |                                             | CFSR.7        | CFSR.6           | CFSR.5          | CFSR.4          | CFSR.3       | CFSR.2  | CFSR.1  | CFSR.0   |

# Table 6.12 AFE Regs

| Symbolic A     | dress         | name                                           | PORMOTILVR PORMOTILVR PORMOTILVR | No. 7 | No. 6 | No. 5 | No. 4  | No. 3 | No. 2 | No. 1        | No. 0 |

|----------------|---------------|------------------------------------------------|----------------------------------|-------|-------|-------|--------|-------|-------|--------------|-------|

| STATED 00H     |               | AFE Status Register                            | 0000                             |       | -     |       |        | WDF   | OL    | SCCHG SCDS   | 3     |

| AOUTPUT<br>CTL | 01H           | AFE Output Control Register                    | -0000000                         |       | WDDIS | APD   | AIDL   | OF    | CHG   | DSG          | LTCLR |

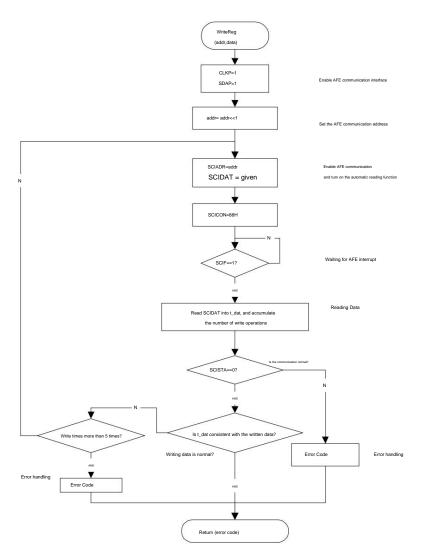

| AFUNCCTL 02H   |               | AFE Function Control Register                  | 000000                           |       | · .   | TEMP  | XSCD   | XSCC  | SCORE | PACKOUT VMEN |       |

| ACELL_SEL 03H  | AFE conver    | sion and balance conduction register           | 0000000                          | CB3   | CB2   | CB1   | CB0    | CAL1  | CAL0  | CELL1        | CELL0 |

| AOLV 04H A     | FE inverse c  | omparator 2 voltage register                   | 00000                            |       |       |       | READ 4 | OLV3  | READ2 | READ 1       | OLV0  |

| AOLT 05H A     | FE reverse c  | omparator 2 time register                      | 0000                             |       | ·     |       | ·      | OLT3  | OLT2  | OLT1         | OLT0  |

| ASCC 06H A     | FE positive o | omparator 1 voltage and time register 00000000 |                                  | SCCT3 | SCCT2 | SCCT1 | SCCT0  | SCCV3 | SCCV2 | SCCV1        | SCCV0 |

| ASCD 07H A     | FE reverse o  | omparator 1 voltage and time register 00000000 |                                  | SCDT3 | SCDT2 | SCDT1 | SCDT0  | SCDV3 | SCDV2 | SCDV1        | SCDV0 |

## SFR video

|        | Bit addressable |             | -              | _             | Not bit addressable |        |            |            |     |

|--------|-----------------|-------------|----------------|---------------|---------------------|--------|------------|------------|-----|

|        | 0/8             | 1/9         | 2/A            | 3/B           | 4/C                 | 5/D    | 6/E        | 7/F        |     |

| F8H    |                 | IB_CLK0     | IB_CLK1 IB_0   | OFFSET IB_DAT | A                   |        |            |            | FFH |

| F0H    | В               | AUXC IB_C   | ON1 IB_CON2 IE | CON3 IB_CON   | 4 IB_CON5 XPA       | GE F7H |            |            |     |

| E8H    |                 | P0PCR P1P   | CR P2PCR       |               |                     |        | P2SEL      | P0OS EFH   |     |

| E0H A0 | ¢C              | P0CR        | P1CR           | P2CR          |                     |        | OPDY       | ADCP E7H   |     |

| D8H    |                 | VADCON VAD  | C1             | VADC0 CAD     | CON CADC1           |        | CAD0       |            | DFH |

| D0H PS | \$W             | UAD2        | UAD1           | UAD0          | DAD2                | DAD1   | DAD0       | V0FSR0 D7H |     |

| C8H    |                 |             |                |               |                     | V0OR1  | V0OR0 V0FS | R1 CFH     |     |

| сон    |                 | SMBCON SM   | BSTA SMBADR S  | SMBDAT SCICO  | N SCIADR SCID       | АТ С7Н |            |            |     |

| B8H    | IPL0            | IPL1        |                |               | COR1                | COR0   | CFSR1      | CFSR0 BFH  |     |

| B0H    |                 | RSTSTAT CLI | CON            |               | IPH0                | IPH1   |            |            | B7H |

| A8H    | IEN0            | IEN1        |                |               |                     |        |            |            | AFH |

| AH     | P2              |             | BTCON          | BT1           | BT0                 |        |            |            | A7H |

| 98H    |                 |             |                |               |                     |        |            |            | 9FH |

| 90H    | P1              |             |                |               |                     |        |            |            | 97H |

| 88H TC | ON              |             |                |               |                     |        | SUSLO      |            | 8FH |

| 80H    | P0              | SP          | DPL            | VAT           | DPL1                | DPH1   | INSCON PCC | N 87H      |     |

|        | 0/8             | 1/9         | 2/A            | 3/B           | 4/C                 | 5/D    | 6/E        | 7/F        |     |

Note: Unused SFR addresses cannot be read or written.

# SH79F329

## 7. Standard Features

## 7.1 CPU

7.1.1 CPU Core Special Function Registers

#### characteristic

ÿ CPU core registers: ACC, B, PSW, SP, DPL, DPH

### accumulator

The accumulator ACC is a commonly used special register, and A is used as the mnemonic of the accumulator in the instruction system.

### B Register

In multiplication and division instructions, register B is used. In other instructions, register B can be used as a temporary register.

### Stack Pointer (SP)

The stack pointer SP is an 8-bit special register. When executing PUSH, various subroutine calls, interrupt response and other instructions, SP first increases by 1 and then pushes the data onto the stack; when executing POP, When RET, RETI and other instructions are executed, SP is decremented by 1 after the data is removed from the stack. The top of the stack can be any address of the on-chip internal RAM (00H-FFH). After the system is reset, SP Initialized to 07H, the stack actually starts at address 08H.

# Program Status Word (PSW) Register

The Program Status Word (PSW) register contains program status information.

### Table 7.1 PSW Register

| DOH                                                   | 7th 6th 5th 4th | n 3rd 2nd 1st 0th |            |            |            |            |            |      |

|-------------------------------------------------------|-----------------|-------------------|------------|------------|------------|------------|------------|------|

| PSW                                                   | С               | AC                | F0         | RS1        | RS0        | OV         | F1         | Р    |

| Read/                                                 | Read/Write      | Read/Write        | Read/Write | Read/Write | Read/Write | Read/Write | Read/Write | read |

| write reset value                                     | 0               | 0                 | 0          | 0          | 0          | 0          | 0          | 0    |

| (POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR/PIN) |                 |                   |            |            |            |            |            |      |

| Bit number | Bit Notation              | illustrate                                                                                                                                                                  |

|------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | С                         | Carry flag<br>0: No carry or borrow occurs in an arithmetic or logical operation.<br>1: A carry or borrow occurs during an arithmetic or logical operation.                 |

| 6          | AC                        | Auxiliary carry flag<br>0: No auxiliary carry or borrow occurs in arithmetic logic operations.<br>1: During arithmetic logic operation, an auxiliary carry or borrow occurs |

| 5          | F0                        | F0 flag<br>User-defined flags                                                                                                                                               |

| 4-3        | গৰ্গৰ প্ৰথম বাগৰে বাগৰে ব | R0-R7 register page select bits<br>00: Page 0 (mapped to 00H-07H)<br>01: Page 1 (mapped to 08H-0FH)<br>10: Page 2 (mapped to 10H-17H)<br>11: Page 3 (mapped to 18H-1FH)     |

| 2          | ov                        | Overflow flag<br>0: No overflow occurred<br>1: Overflow occurs                                                                                                              |

| 1          | F1                        | F1 flag<br>User-defined flags                                                                                                                                               |

| 0          | Ρ                         | Parity bit<br>0: The number of digits with the value 1 in accumulator A is even<br>1: The number of digits with the value 1 in accumulator A is an odd number               |

## Data Pointer (DPTR)

The data pointer DPTR is a 16-bit special register. The high-order byte register is represented by DPH and the low-order byte register is represented by DPL. They can be used as a It can be processed as a 16-bit register DPTR or as two independent 8-bit registers DPH and DPL.

7.1.2 CPU Enhanced Core Special Function Registers

ÿ Extended 'MUL' and 'DIV' instructions: 16 bits \* 8 bits, 16 bits / 8 bits

ÿ Dual data pointer

ÿ CPU enhanced core registers: AUXC, DPL1, DPH1, INSCON

SH79F329 extends the 'MUL' and 'DIV' instructions and uses a new register - AUXC register to store the upper 8 bits of the operation data to achieve 16-bit operation.

The AUXC register is used in multiplication and division instructions. In other instructions, the AUXC register can be used as a temporary register.

The CPU enters standard mode after reset, and the 'MUL' and 'DIV' instruction operations are consistent with the standard 8051 instruction operations. When the corresponding bit of the INSCON register is 1, 'MUL' And the 16-bit operation function of the 'DIV' instruction is turned on.

|        |                                                 |          |                   | result      |                    |

|--------|-------------------------------------------------|----------|-------------------|-------------|--------------------|

|        | operate                                         |          | А                 | В           | AUXC               |

|        | INSCON.2 = 0; 8-bit mode                        | (A)*(B)  | low byte          | high byte   |                    |

| l have | INSCON.2 = 1; 16-bit mode (AUXC A)*(B) low byte |          |                   | middle byte | High Byte          |

|        | INSCON.3 = 0; 8-bit mode                        | (A)/(B)  | Quotient low byte | Remainder   |                    |

| DIV    | INSCON.3 = 1; 16-bit mode (AUXC A)/(B) quotient | low byte |                   | Remainder   | Quotient high byte |

Dual data pointer

Using dual data pointers can speed up data storage movement. The standard data pointer is named DPTR and the new data pointer is named DPTR1.

The data pointer DPTR1 is similar to DPTR and is a 16-bit dedicated register. Its high-order byte register is represented by DPH1 and its low-order byte register is represented by DPL1.

They can be processed as a 16-bit register DPTR1 or as two independent 8-bit registers DPH1 and DPL1.

One of the two data pointers is selected by setting the DPS bit in the INSCON register to 1 or 0. All instructions related to reading or manipulating the DPTR will select the most recent data pointer.

The data pointer for the next selection.

### 7.1.3 Registers

### Table 7.2 Data Pointer Selection Register

| 86H        | 7th 6th 5th 4th | 3rd 2nd 1st 0th |  |            |            |            |

|------------|-----------------|-----------------|--|------------|------------|------------|

| INSCON     |                 |                 |  | DIV        | I have     | DPS        |

| Read/Write |                 |                 |  | Read/Write | Read/Write | Read/Write |

|            |                 |                 |  | 0          | 0          | 0          |

| Bit number | Bit Notation | illustrate                                                                                    |

|------------|--------------|-----------------------------------------------------------------------------------------------|

| 3          | DIV          | 16-bit/8-bit division<br>0: 8-bit division<br>1: 16-bit division                              |

| 2          | l have       | 16-bit/8-bit multiplication select bit<br>0: 8-bit multiplication<br>1: 16-bit multiplication |

| 0          | DPS          | Data pointer select bit<br>0: Data pointer<br>1: Data pointer 1                               |

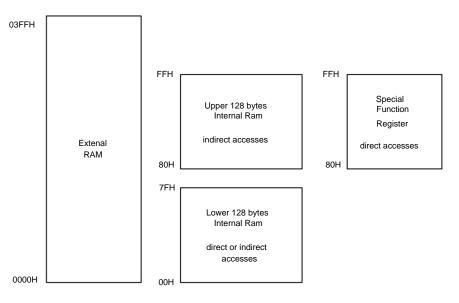

## 7.2 RAM

#### 7.2.1 Features

SH79F329 provides internal RAM and external RAM for data storage. The following is the memory space allocation:

ÿ The lower 128 bytes of RAM (address from 00H to 7FH) can be addressed directly or indirectly

ÿ The upper 128 bytes of RAM (address from 80H to FFH) can only be addressed indirectly

$\ddot{\text{y}}$  Special function registers (SFR, address from 80H to FFH) can only be directly addressed

ÿ External RAM bytes can be indirectly addressed via MOVX instructions

The upper 128 bytes of RAM occupy the same address space as the SFR, but are physically separated from the SFR space.

When the CPU is in the same position as the SFR, it can distinguish whether the high 128 bytes of data RAM or SFR is accessed according to the type of instruction being accessed.

Note: Unused SFR addresses are prohibited from reading and writing

Internal Configuration

SH79F329 supports the traditional method of accessing external RAM. Use MOVXA, @Ri or MOVX@Ri, A to access the external low 256 bytes RAM; use MOVX A, @DPTR or MOVX@DPTR, A to access external 1024 bytes of RAM.

Users can also use the XPAGE register to access external RAM, using the MOVX A, @Ri or MOVX @Ri, A instructions. XPAGE is used to represent a register higher than 256. byte RAM address.

In Flash SSP mode, XPAGE can also be used as a segment selector (see SSP chapter for details).

### 7.2.2 Registers

Table 7.3 Data Storage Page Register

| F7H                                                   | 7th 6th 5th 4th | 3rd 2nd 1st 0th  |                   |                 |            |            |            |            |

|-------------------------------------------------------|-----------------|------------------|-------------------|-----------------|------------|------------|------------|------------|

| XPAGE                                                 | XPAGE.7 XPAGE.  | 6 XPAGE.5 XPAGE. | 4 XPAGE.3 XPAGE.2 | XPAGE.1 XPAGE.0 |            |            |            |            |

| Read/                                                 | Read/Write      | Read/Write       | Read/Write        | Read/Write      | Read/Write | Read/Write | Read/Write | Read/Write |

| write reset value                                     | 0               | 0                | 0                 | 0               | 0          | 0          | 0          | 0          |

| (POR/WDTILVR POR/WDTILVR POR/WDTILVR POR/WDTILVR/PIN) |                 |                  |                   |                 |            |            |            |            |

| Bit number | Bit Notation | illustrate                                                                                                              |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| 7-0        | XPAGE[7:0]   | RAM page select control bits<br>When executing MOVX A, @Ri or MOVX@Ri, A, access beyond the range of 0-3FFH is invalid. |

# SH79F329

#### 7.3 Flash memory SH79F329

has a built-in 32K programmable Flash for storing program code and provides self-programming function.

Note: The last 64 bytes (\$7FC0-\$7FFF) are reserved and cannot be used as programmable memory.

In ICP (In-Circuit Programming) mode, the program can operate all Flash, such as erasing or writing. Flash read or write operations are in bytes, but erase can only be in sectors (2k) or overall erase. In ICP mode, the sector erase

operation can erase any block except sector 15. In self-programming

mode (SSP), except for sector 15, all other sectors can be erased.

### The erase code sectors cannot be erased either.

In ICP mode, you can also perform a global erase, which will erase the entire Flash memory (including sector 15).

#### 7.3.1 Features ÿ

Programmable memory includes 16 x 2KB blocks, totaling 32KB ÿ Programming and erasing

operations can be performed within the operating voltage range  $\ddot{\text{y}}$  ICP operation

supports write, read and erase operations ÿ Fast overall/sector erase and

programming ÿ Minimum program/erase times: 10,000

times v Minimum data retention period: 10 years v Low power

consumption 7.3.2 Flash operation in ICP mode

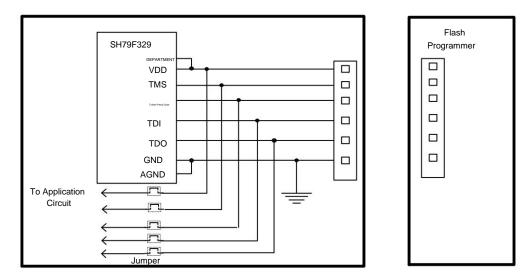

ICP mode is the online programming mode, which means that programming can be done after the CPU is soldered on the user board. In ICP mode, the user system must be shut down before the programmer can refresh the Flash

memory through the ICP programming interface. The ICP programming interface includes 6 wires (VDD, GND, TDO, TDI, TCK, TMS). First use 4 JTAG pins (TDO, TDI, TCK, TMS)

to enter the programming mode. Only when these 4 pins specify the waveform input, the CPU can enter the programming mode .

ICP mode supports the following

#### operations: (1) Code protection control mode programming

The code protection function of SH79F329 provides high-performance security protection for user code. Two modes are available for each partition: Code protection mode 0: Allow/

disable write/read operations by any programmer (excluding overall erase). Code protection mode 1: Allow/disable read operations through

MOVC instructions in other partitions, or erase/write operations through SSP functions. The user must set the corresponding protection bits using the Flash programmer to enter the desired protection mode.

#### (2) Mass Erase

Regardless of the status of the code protection control mode, the mass erase operation will erase all programmed code, code options, code protection bits, and custom ID code contents.

(The Flash programmer provides users with a custom ID code setting function to distinguish their products).

Mass erase can only be performed by a Flash programmer.

### (3) Sector Erase

The sector erase operation will erase the contents of the selected sector except for sector 15. Both the user program and the Flash programming can perform this operation. If the

user program needs to perform this operation, the code protection control mode 1 of the selected sector must be disabled. If the

programmer needs to perform this operation, the code protection control mode 0 of the selected sector must be disabled.

Note: The last sector (sector 15) cannot perform the sector erase function.

#### (4) Write/read code

The read/write code operation can write customer data to the Flash programming memory or read data from the Flash memory. The programmer or the user program can perform this operation. If the user program needs

to perform this operation, the code protection control mode 1 of the selected sector must be disabled. Regardless of whether the security bit is set or not, the user program can read/write the sector where the program itself is

located . If the

programmer needs to perform this operation, the code protection control mode 0 of the selected sector must be disabled

#### Programming clock control register

| Operation       | ICP                              | SSP                                           |

|-----------------|----------------------------------|-----------------------------------------------|

| Code Protection | support                          | Not supported                                 |

| Sector Erase    | Support (no security bit)        | Support (no security bit)                     |

| Mass Erase      | Mass Erase support Not supported |                                               |

| Write/Read      | Support (no security bit)        | Supported (no security bit or native sectors) |

In ICP mode, all Flash operations can be completed through the 6-wire interface programmer. Because the programming signal is very sensitive, the user needs to use 5 jumpers to connect the programming pins (VDD, TDD, TDI, TCK, TMS) are separated from the application circuit. As shown in the figure below.

It is recommended to follow the following steps: (1) Before

connecting the programming interface, you must disconnect the jumper and separate the programming pins from the application circuit before programming can begin. (2)

After the programmer is connected to the programming interface, start

programming. (3) After programming is completed, disconnect the programmer and connect the jumper.

### 7.4 Sector Self-Programming (SSP) Function

SH79F329 provides SSP (Sector Self Programming) function, if the selected sector is not protected, user code can erase all sectors except sector 15 or any sector Execute the burn operation. Once the sector is burned, it cannot be burned again before the sector is erased.

SH79F329 has a built-in complex control flow to prevent the code from being modified by mistake. If the specified conditions (IB\_CON2-5) are not met, the SSP will be terminated.

## 7.4.1 Registers

Table 7.4 Timing control register for programming

| F9H                                                   | 7th 6th 5th 4   | th 3rd 2nd 1st 0th |                |                    |                  |            |            |            |

|-------------------------------------------------------|-----------------|--------------------|----------------|--------------------|------------------|------------|------------|------------|

| IB_CLK0 IB_CLK0 IB_CLK0 IB_CLK0                       | IB_CLK0.7 IB_CL | .K0.6 IB_CLK0.5 IE | CLK0.4 IB_CLK0 | 1.3 IB_CLK0.2 IB_0 | CLK0.1 IB_CLK0.0 |            |            |            |

| FAH                                                   | 7th 6th 5th 4   | th 3rd 2nd 1st 0th |                |                    |                  |            |            |            |

| IB_CLK1 IB_CLK1                                       | IB_CLK1.7 IB_CL | .K1.6 IB_CLK1.5 IE | CLK1.4 IB_CLK1 | .3 IB_CLK1.2 IB_0  | CLK1.1 IB_CLK1.0 |            |            |            |

| IB_CLK1                                               | Read/Write      | Read/Write         | Read/Write     | Read/Write         | Read/Write       | Read/Write | Read/Write | Read/Write |

| IB_CLK1 read/write reset value                        | 0               | 0                  | 0              | 0                  | 0                | 0          | 0          | 0          |

| (POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR/PIN) |                 |                    |                |                    |                  |            |            |            |

| Bit number | Bit Notation                             | illustrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0        | а смраја смраја смраја смрај<br>x = 0, 1 | Flash programming clock selectionThe values in B_CLK1:IB_CLK0 are calculated as follows.programming:65536                                                                                                                                                                                                                                                                                                                                                                  |

|            |                                          | Note:     When using sector errses. We system dock must be less than or equal to 8MHz. If the accilitator frequency is greater than 8MHz, the user must use system dock division to ensure that the system dock is less than or equal to 8MHz       ISYS     Nagenative Programming Programming Programming     Errase       8M     FFE2H     15A0H       4M     FFF1H     8AD0H       2M     FFF8H     C568H       1M     FFFFBH     E2B4H       32K     FFFFFH     F880H |

7-3

2-0

# SH79F329

## Table 7.5 Programming offset register

|            |            |            |            | 000000000000000000000000000000000000000 |                 | h 3rd 2nd 1st 0th | 7th 6th 5th 4t | F7H         |

|------------|------------|------------|------------|-----------------------------------------|-----------------|-------------------|----------------|-------------|

|            |            |            | E.0        | E.2 XPAGE.1 XPAG                        | .4 XPAGE.3 XPAG | .6 XPAGE.5 XPAGE  | XPAGE.7 XPAGE  | XPAGE       |

| Read/Write | Read/Write | Read/Write | Read/Write | Read/Write                              | Read/Write      | Read/Write        | Read/Write     | Read/Write  |

| 0          | 0          | 0          | 0          | 0                                       | 0               | 0                 | 0              | Reset value |

|            | 0          | 0          | 0          | 0                                       | 0               | 0                 | 0              |             |

XPAGE[7:3] The sector number of the memory cell being programmed, 00000 represents sector 0

**XPAGE[2:0]** The upper B bits of the memory cell to be programmed

| Table 7.6 Flash memory offset register for programming |

|--------------------------------------------------------|

| FBH                                     | 7th 6th 5th 4tl | n 3rd 2nd 1st Oth |                 |                 |                 |                 |                 |                 |

|-----------------------------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| IB_OFFSET IB_OFFSET IB_OFFSET IB_OFFSET | IB_OFF<br>SET.7 | IB_OFF<br>SET.6   | IB_OFF<br>SET.5 | IB_OFF<br>SET.4 | IB_OFF<br>SET.3 | IB_OFF<br>SET.2 | IB_OFF<br>SET.1 | IB_OFF<br>SET.0 |

| Read/                                   | Read/Write      | Read/Write        | Read/Write      | Read/Write      | Read/Write      | Read/Write      | Read/Write      | Read/Write      |

| write reset value                       | 0               | 0                 | 0               | 0               | 0               | 0               | 0               | 0               |

| Bit number | Bit Notation                      | illustrate                                                             |

|------------|-----------------------------------|------------------------------------------------------------------------|

| 7-0        | IB_OFFSET[7 IB_OFFSET[7 IB_OFFSET | 7 IB. OFFSET[7:0] The lower 8 bits of the memory cell to be programmed |

## Table 7.7 Data registers for programming

| FCH                                               | 7th 6th 5th 4tl | n 3rd 2nd 1st Oth  |                  |                  |               |            |            |            |

|---------------------------------------------------|-----------------|--------------------|------------------|------------------|---------------|------------|------------|------------|

| IB_DATA IB_DATA IB_DATA                           | IB_DATA.7 IB_DA | FA.6 IB_DATA.5 IB_ | DATA.4 IB_DATA.3 | IB_DATA.2 IB_DAT | A.1 IB_DATA.0 |            |            |            |

| IB_DATA read/write                                | Read/Write      | Read/Write         | Read/Write       | Read/Write       | Read/Write    | Read/Write | Read/Write | Read/Write |

| Reset value                                       | 0               | 0                  | 0                | 0                | 0             | 0          | 0          | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                    |                  |                  |               | a          |            |            |

| Bit number | Bit Notation                      | illustrate                 |

|------------|-----------------------------------|----------------------------|

| 7-0        | IB_DATA[7 IB_DATA[7 IB_DATA[7 IB] | QATA(7:0) programming data |

### Table 7.8 SSP type selection register

| F2H                                               | 7th 6th 5th 4t  | n 3rd 2nd 1st Oth |                  |                   |                |            |            |            |

|---------------------------------------------------|-----------------|-------------------|------------------|-------------------|----------------|------------|------------|------------|

| IB_CON1 IB_CON1                                   | IB_CON1.7 IB_CO | N1.6 IB_CON1.5 IB | _CON1.4 IB_CON1. | 3 IB_CON1.2 IB_CO | N1.1 IB_CON1.0 |            |            |            |

| IB_CON1                                           | Read/Write      | Read/Write        | Read/Write       | Read/Write        | Read/Write     | Read/Write | Read/Write | Read/Write |

| IB_CON1 read/write reset value                    | 0               | 0                 | 0                | 0                 | 0              | 0          | 0          | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                   |                  |                   |                |            |            |            |

| Bit number | Bit Notation                               | illustrate                                                               |

|------------|--------------------------------------------|--------------------------------------------------------------------------|

| 7-0        | IB_CONI[7 IB_CONI[7 IB_CONI[7 IB_CONI[7:0] | SSP Operation Selection<br>0xE6: Sector Erase<br>0x6E: Burn storage unit |

Table 7.9 SSP flow control register 1

| F3H                                                               | 7th 6th 5th 4th | 3rd 2nd 1st 0th |                  |                     |                |   |            |

|-------------------------------------------------------------------|-----------------|-----------------|------------------|---------------------|----------------|---|------------|

| IB_CON2 IB_CON2 IB_CON2                                           |                 |                 | IB_CON2.4 IB_CON | 2.3 IB_CON2.2 IB_CO | N2.1 IB_CON2.0 |   |            |

| IB_CON2 Read/Write                                                |                 | •               | Read/Write       | Read/Write Read/W   | ite Read/Write |   | Read/Write |

| Reset value                                                       |                 |                 | 0                | 0                   | 0              | 0 | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                 |                  |                     |                |   |            |

| Bit number | Bit Notation                            | illustrate                                                                          |

|------------|-----------------------------------------|-------------------------------------------------------------------------------------|

| 4          | IE_CON2.4 IE_CON2.4 IE_CON2.4 IE_CON2.4 | System clock selection<br>0ўfSYS > 1MHz<br>1ÿfSYS < 1MHz                            |

| 3-0        | IB_CON2[3 IB_CON2[3 IB_CON2[3           | IB_CON2[3 IB_CON2[3:0] must be 05H, otherwise the Flash programming will terminate. |

Table 7.10 SSP flow control register 2

| F4H                                                               | 7th 6th 5th 4th | 3rd 2nd 1st 0th |  |                  |                     |            |            |

|-------------------------------------------------------------------|-----------------|-----------------|--|------------------|---------------------|------------|------------|

| IB_CON3 IB_CON3 IB_CON3                                           |                 |                 |  | IB_CON3.3 IB_CON | 3.2 IB_CON3.1 IB_CO | DN3.0      |            |

| IB_CON3 Read/Write                                                |                 |                 |  | Read/Write       | Read/Write          | Read/Write | Read/Write |

| Reset value                                                       |                 |                 |  | 0                | 0                   | 0          | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                 |  |                  | -                   |            |            |

| Bit number | Bit Notation                  | illustrate                                                                          |

|------------|-------------------------------|-------------------------------------------------------------------------------------|

| 3-0        | IB_CON3[3 IB_CON3[3 IB_CON3[3 | IB_CON3[3 IB_CON3[3:0] must be 0AH, otherwise the Flash programming will terminate. |

Table 7.11 SSP flow control register 3

| F5H                                               | 7th 6th 5th 4th | 3rd 2nd 1st 0th |  |                  |                     |            |            |

|---------------------------------------------------|-----------------|-----------------|--|------------------|---------------------|------------|------------|

| IB_CON4 IB_CON4 IB_CON4                           |                 | •               |  | IB_CON4.3 IB_CON | 4.2 IB_CON4.1 IB_CO | DN4.0      |            |

| IB_CON4 Read/Write                                | -               |                 |  | Read/Write       | Read/Write          | Read/Write | Read/Write |

| Reset value                                       |                 | -               |  | 0                | 0                   | 0          | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                 |  |                  |                     |            |            |

| Bit number | Bit Notation             | illustrate                                  |

|------------|--------------------------|---------------------------------------------|

| 3-0        | IB_CON4[3:0] must be 09H | otherwise Flash programming will terminate. |

Table 7.12 SSP flow control register 4

| F6H                                               | 7th 6th 5th 4th | 3rd 2nd 1st 0th |  |                  |                     |            |            |

|---------------------------------------------------|-----------------|-----------------|--|------------------|---------------------|------------|------------|

| IB_CONS IB_CONS IB_CONS                           |                 |                 |  | IB_CON5.3 IB_CON | 5.2 IB_CON5.1 IB_CO | DN5.0      |            |

| IB_CON5 Read/Write                                |                 |                 |  | Read/Write       | Read/Write          | Read/Write | Read/Write |

| Reset value                                       |                 |                 |  | 0                | 0                   | 0          | 0          |

| (POR/WDT/LVR/PIN POR/WDT/LVR/PIN POR/WDT/LVR/PIN) |                 |                 |  |                  |                     |            |            |

| Bit number | Bit Notation             | illustrate                                  |

|------------|--------------------------|---------------------------------------------|

| 3-0        | IB_CON5[3:0] must be 06H | otherwise Flash programming will terminate. |

SH79F329

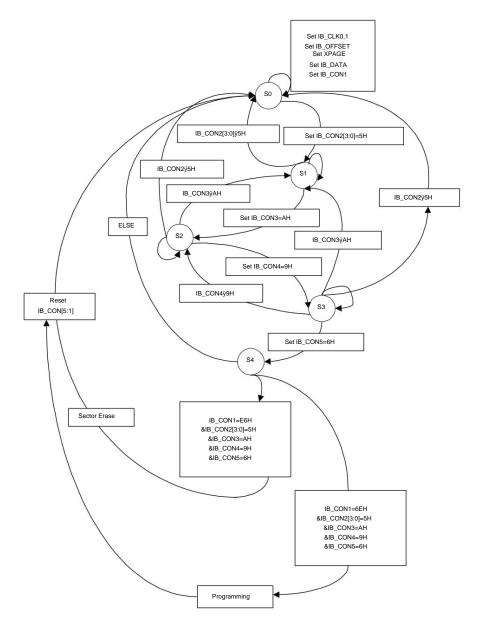

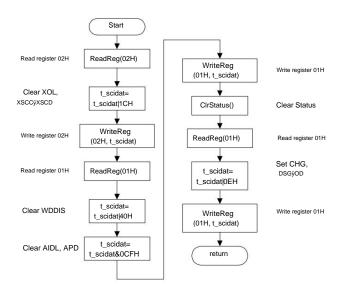

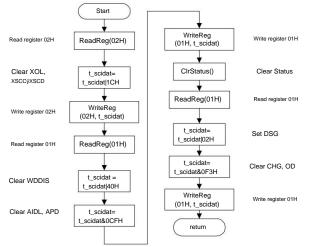

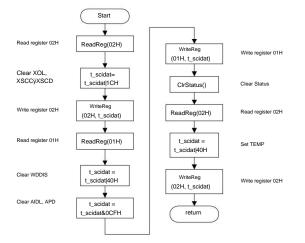

7.4.2 Flash Control Flowchart

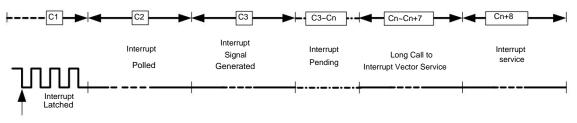

7.4.3 Notes on SSP Programming To ensure that SSP programming is completed successfully, the user software must be set up according to the following steps: (1) Burning: 1. Disable interrupts; 2. Set IB\_CLK1, IB\_CLK0; 3. Set XPAGE, IB\_OFFSET according to the corresponding sector number to be programmed; 4. Set IB\_DATA according to programming requirements; 5. Set IB\_CON1-5 in sequence 6. Add 4 NOP instructions; 7. Start burning, the CPU will enter IDLE mode; automatically exit IDLE mode after burning is completed; 8. If you need to continue writing data, jump to step 3; 9. Clear XPAGE; 10. Restore interrupt and system frequency division settings. (2) Erase: 1. Disable interrupts; 2. Set IB\_CLK1, IB\_CLK0; 3. Set XPAGE according to the corresponding sectors; 4. Set IB\_CON1-5 in order; 5. Add 4 NOP instructions; 6. Start erasing, the CPU will enter IDLE mode; automatically exit IDLE mode after erasing is completed; 7. If more sectors need to be erased, jump to step 3 to continue;

8. Clear XPAGE; 9. Restore interrupts and system frequency division settings. (3) Read: Use "MOVC A, @A + DPTR" or "MOVC A, @A + PC" to read.

7.5 System Clock and Oscillator

#### 7.5.1 Features

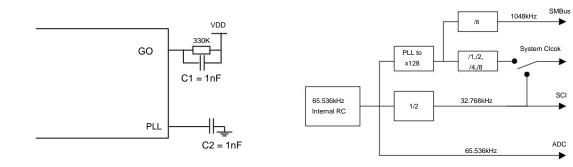

ÿ Built-in 64KHz RC oscillator

ÿ Built-in system clock X128 multiplier

ÿ Built-in 1/1, 1/2, 1/4, 1/8 divider

#### 7.5.2 Overview

SH79F329 uses an internal 64KHz RC oscillator, providing a x128 multiplier and 1/1, 1/2, 1/4, 1/8 dividers. There are 32.768kHz, 1048kHz, 2097kHz,

4194kHz, 8338kHz five frequencies as system clock options.

### 7.5.3 Registers

Table 7.13 System clock control register

| B2H                                                               | 7th 6th 5th 4th | 3rd 2nd 1st 0th |  |            |            |            |            |

|-------------------------------------------------------------------|-----------------|-----------------|--|------------|------------|------------|------------|

| CLKCON                                                            |                 |                 |  | PLLCON     | FS2        | FS1        | FS0        |

| Read/Write                                                        |                 |                 |  | Read/Write | Read/Write | Read/Write | Read/Write |

| Reset value                                                       |                 |                 |  | 0          | 0          | 0          | 0          |

| (POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR POR/WDT/LVR/PIN) |                 |                 |  |            |            |            |            |

| Bit number | Bit Notation                              | illustrate                                                                                                                                                                                                                                             |

|------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | PLLCON                                    | System clock frequency multiplier<br>0: Disable the internal clock multiplier<br>1: Enable the internal clock multiplier                                                                                                                               |

| 2-0        | ર કરવાનાં કરવાનાં કરવાનાં કરવાનાં કરવાનાં | System clock control register<br>0xx: Select 32.768kHz as the system clock<br>100: Select 1048kHz as the system clock<br>101: Select 2097kHz as the system clock<br>110: Select 4194kHz as the system clock<br>111: Select 8338kHz as the system clock |

#### 7.5.4 Oscillator Types

Internal 64KHz RC oscillator and system frequency division circuit

### 7.5.5 System Clock Selection

When selecting the multiplier clock, follow the steps below to set

- 1. Set FS[1:0] to the desired frequency

- 2. Set PLLCON

- 3. Wait for no less than 2ms

- 4. Set FS2

### 7.5.6 AFE Communication Clock

When CLKP in register P0OS is set to 1, an internal 32.768kHz clock is provided to the AFE and is not affected by the internal system clock.

## 7.6 I/O Ports

## 7.6.1 Features

ÿ 13 bidirectional I/O ports

- ÿ 2 bidirectional open-drain I/O ports

- $\ddot{\textbf{y}}$  I/O ports can be shared with other functions

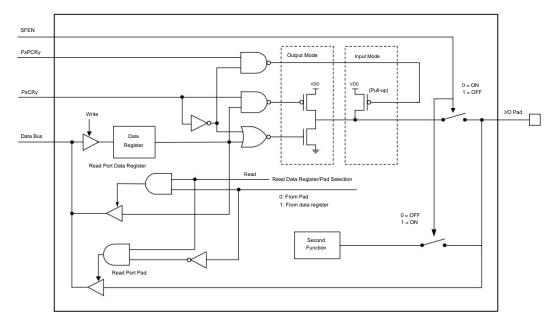

SH79F329 provides 15-bit programmable bidirectional I/O ports. The port data is in register Px. The port control register (PxCRy) controls whether the port is used as input or

Output. Each I/O port has an internal pull-up resistor controlled by PxPCRy (x = 0-2, y = 0-7) when the port is used as an input .

Some I/O pins of the SH79F329 can be shared with selected functions. When all functions are enabled, there is a priority in the CPU to avoid function conflicts. (See Port Sharing for details.) Sharing chapter).

## 7.6.2 Registers

## Table 7.14 Port Control Register