# 集成PWM和流水线ADC的16位DSP+增强型8051双核控制器

#### 1. 特性

#### 双核结构: 16位增强型DSP+8位MCU

#### 系统特件:

- 工作电压: V<sub>DD</sub> = 2.7 5.5V

- 高频振荡器

- 晶体谐振器: 4M 16MHz

- 内部RC高频振荡器: 16MHz(全范围±1%精度)

- 内部集成无需外接电容的PLL,最高输出100MHz

- 停振检测

- 外部晶振失效后切换至内部RC作为系统频率并产生中断

- ISP功能

- 看门狗定时器(WDT)

- 低电压复位LVR

#### DSP及其外设:

- CPU

- 最大100MIPS, 16位宽度数据总线

- 单周期同步执行16位MAC和存取操作

- 32级桶形移位器

- 单周期执行"取双操作数"和"取指令"

- 片上存储器

- 64K X 8bits Flash作为DSP的非易失性存储器

- 16K X 24bits SRAM作为DSP运行程序的Code Memory

- 6K X 16bits SRAM作为DSP的Data Memory

- 512 X 16bits SRAM作为通讯数据存储器(位于DM区)

- 2K X 16bits SRAM作为DSP的Program Memory(位于PM区)

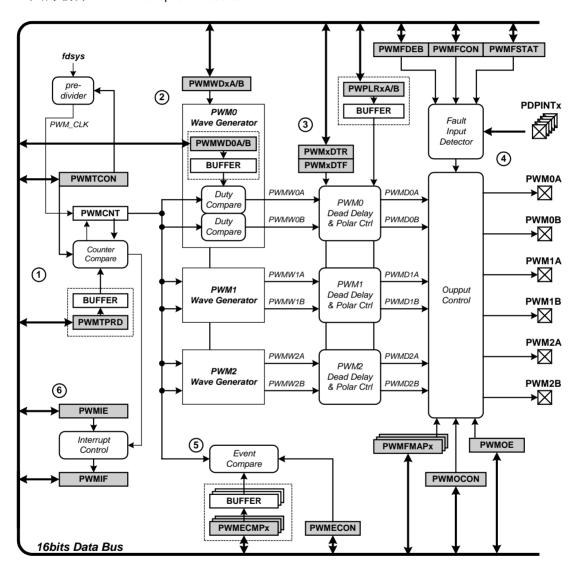

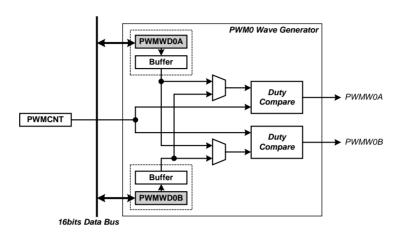

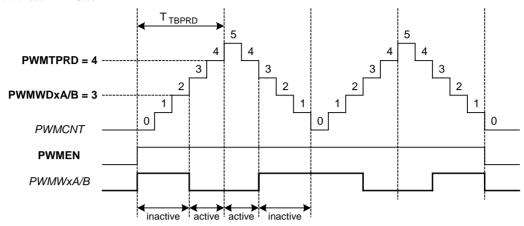

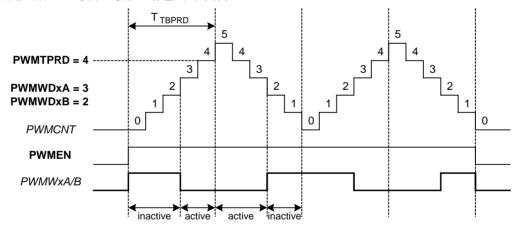

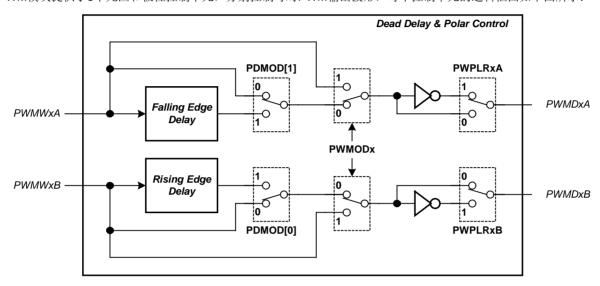

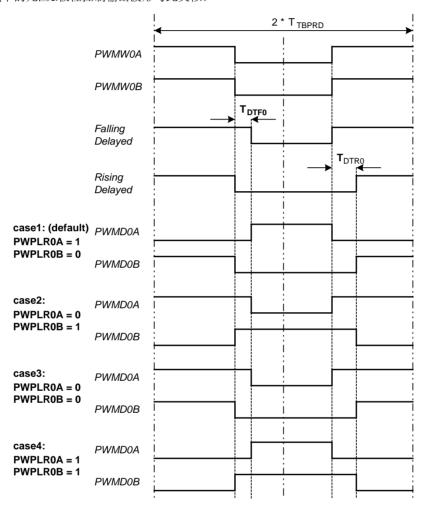

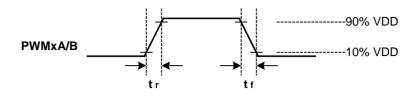

- 脉冲宽度调制 (PWM) 模块

- 6路(3对)16位PWM输出

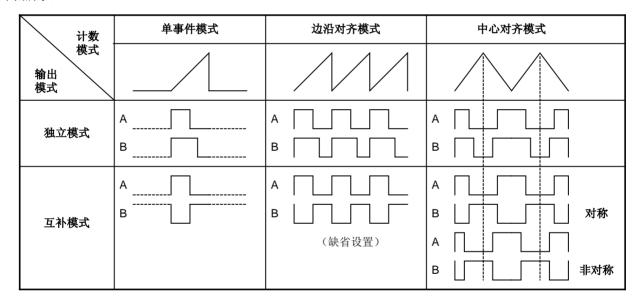

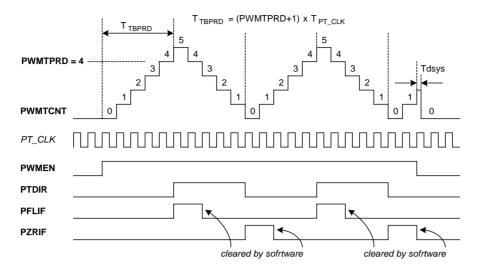

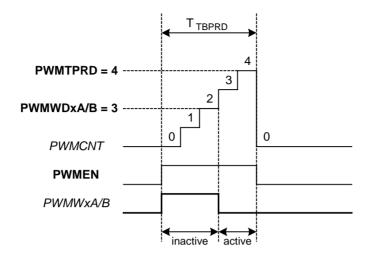

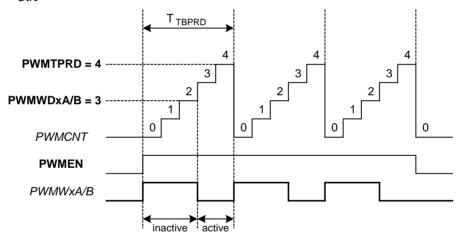

- 3种时基计数模式: 单事件模式、边沿对齐模式与中心 对齐模式

- 每对PWM提供2种输出模式: 互补输出和独立输出

- PWM输出有效极性选择

- 死区产生逻辑

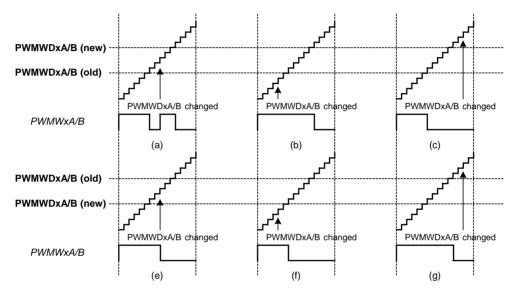

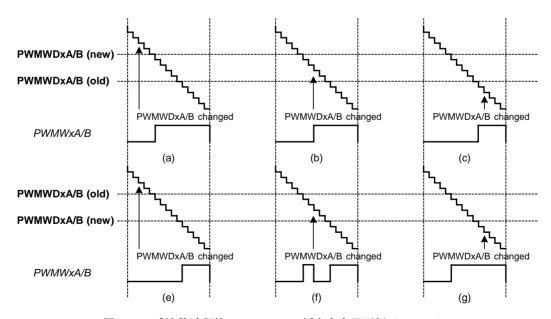

- 自动更新周期、占空比、输出极性以及ADC触发时刻

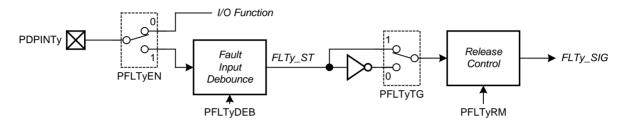

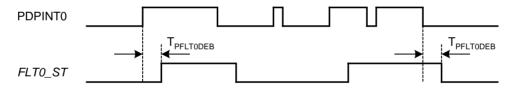

- 5个保护输入引脚

- 每个保护输入引脚上的Debounce时间可设置为八档 (0μs 16μs)

- 后分频系数

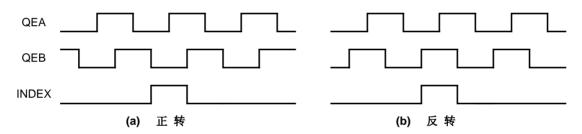

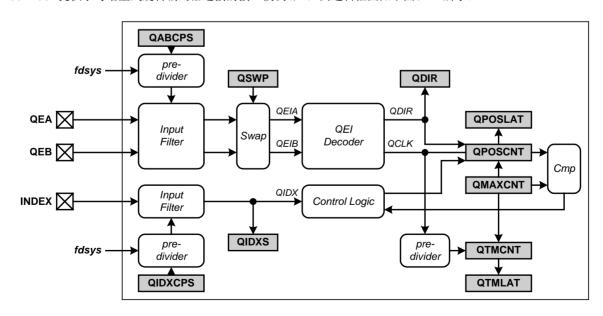

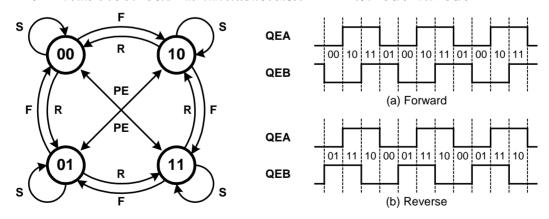

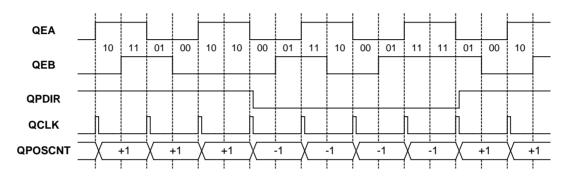

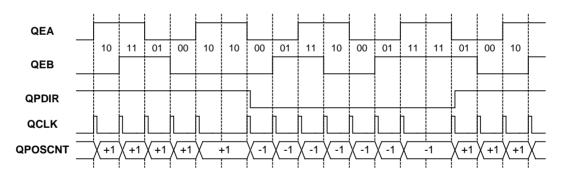

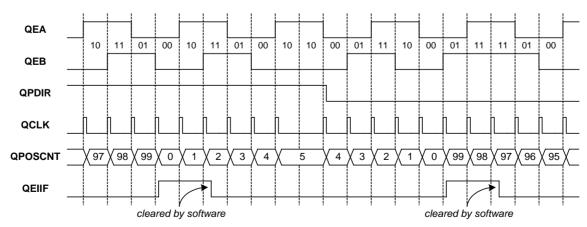

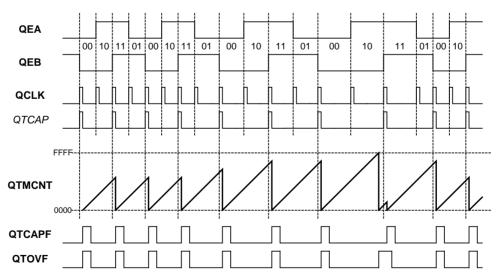

- 正交编码器接口(QEI)

- QEA, QEB, Index三路信号输入

- 16位增/减双向位置计数器

- 5种可屏蔽中断: 计数器重载/Index信号中断; Index信号发生错误中断; QEA/B输入信号相位错误中断; 测速定时器溢出中断; 测速定时器捕捉中断

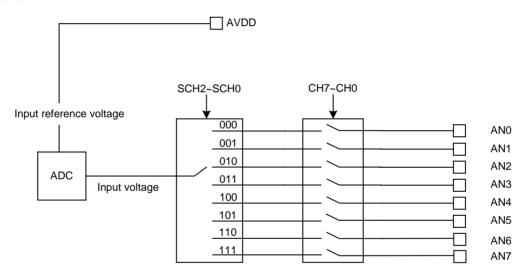

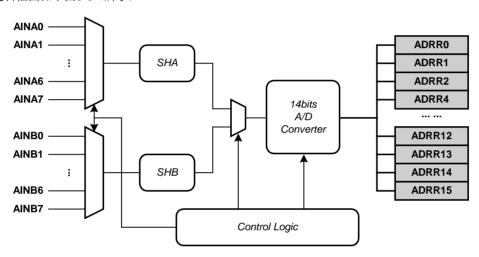

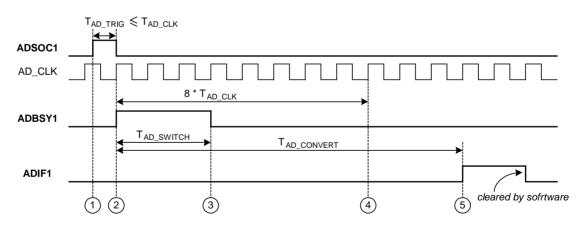

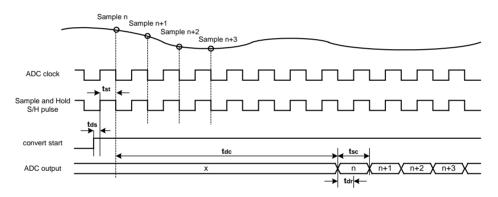

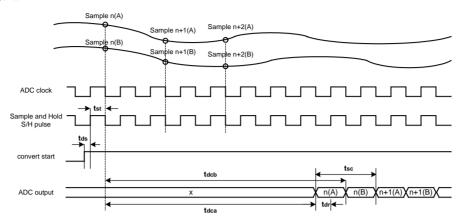

- 2 X 8通道14位模数转换器(ADC)

- 10MSPS转换速率

- 两路同步并行采样模式、两路独立顺序采样模式与单序 列顺序采样模式

- 4个16位定时器DTimer0/1/2/3

- 3个外部中断DXINT0/1/2

- 1个JTAG接口实现DSP的仿真调试

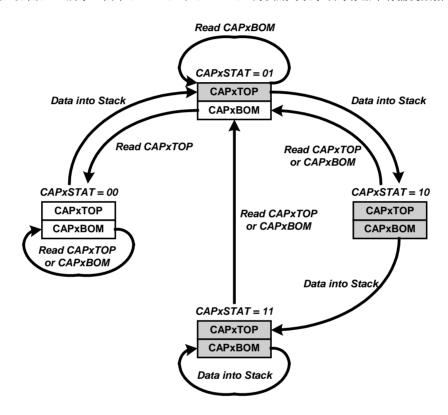

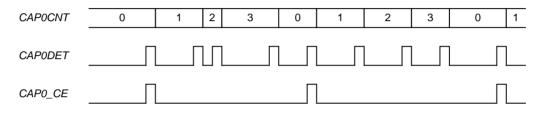

- 4个输入捕捉功能引脚

- 使用DTimer2/3之一作为时基

- 2级FIFO缓冲器

- 捕捉事件可设置为上升沿、下降沿、上升/下降沿

- 输入分频/滤波设置

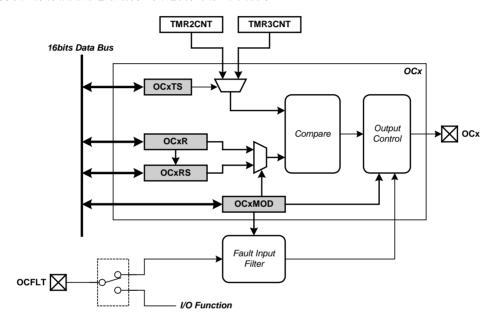

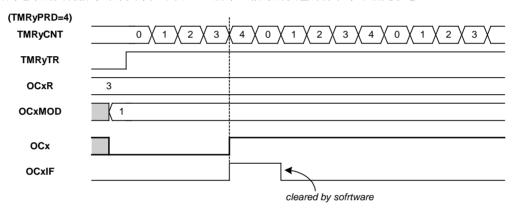

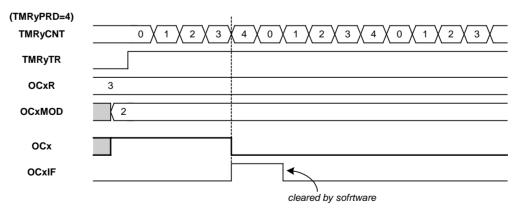

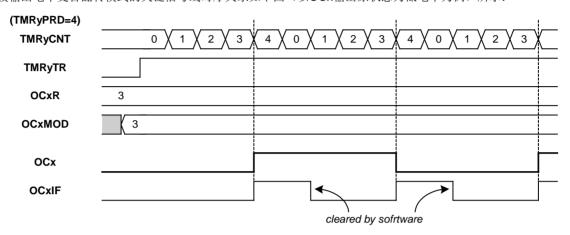

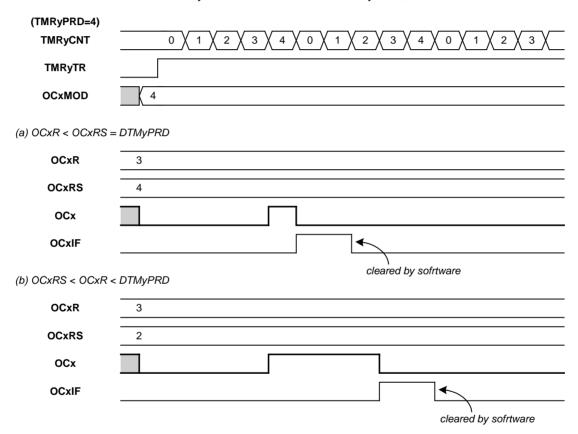

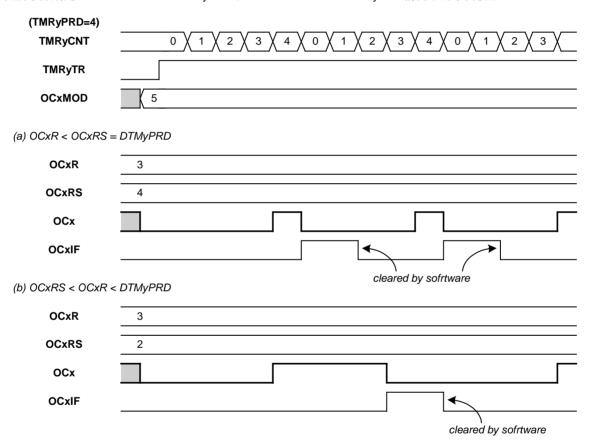

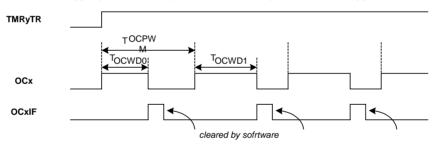

- 3路输出比较引脚

- 使用DTimer3/2之一作为时基

- 单次比较模式、双比较模式、边沿对齐PWM输出模式

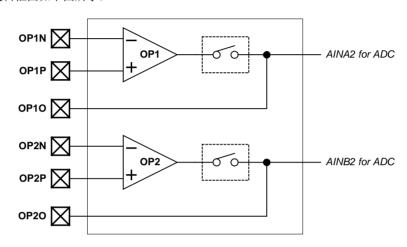

- 2个运算放大器

#### MCU及其外设:

- CPU

- 基于8051指令流水线结构的8位单片机

- 最大工作频率16MHz, CISC指令集

- 片上存储器

- 64KBytes Flash

- 4KBytes SRAM

- 1K X 8bits Flash作为ISP程序存储器

- 56个CMOS双向I/O管脚(功能复用),内建输入上拉电阻

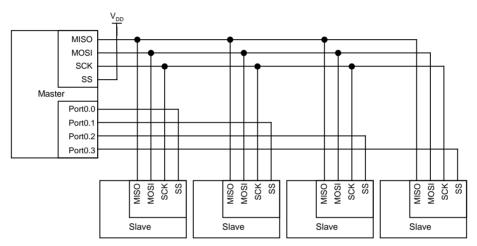

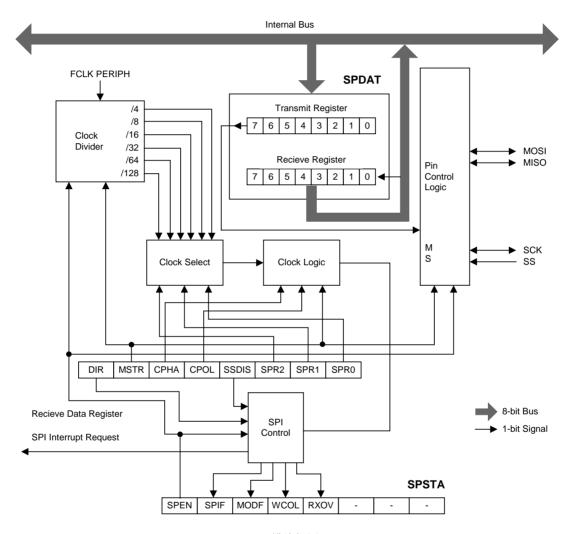

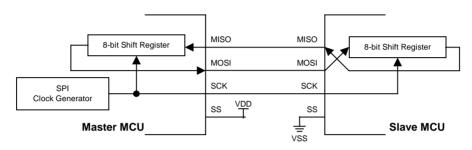

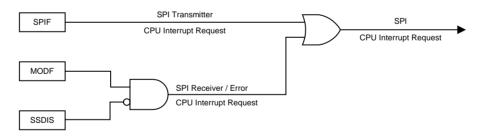

- SPI接口(主/从模式)

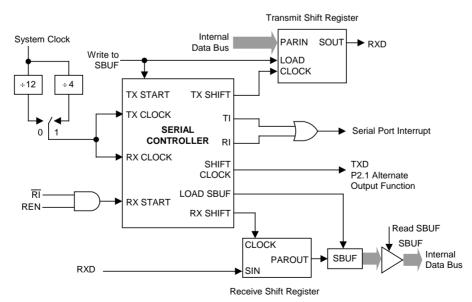

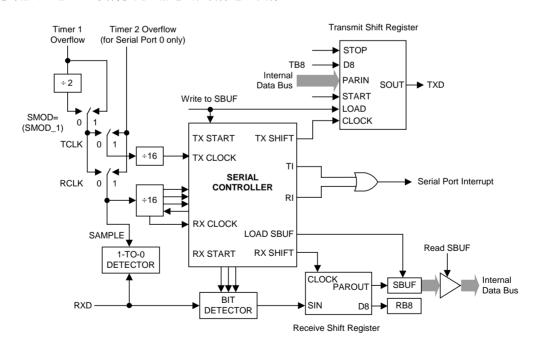

- 2个增强型UART (3V/5V通讯)

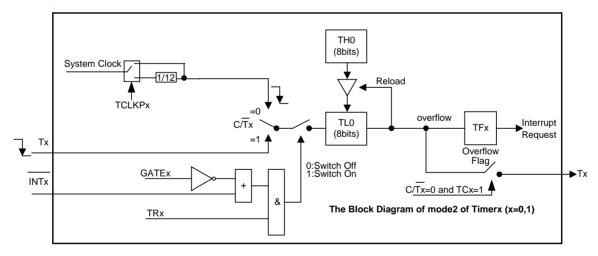

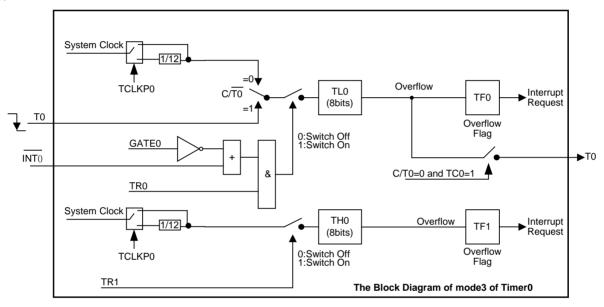

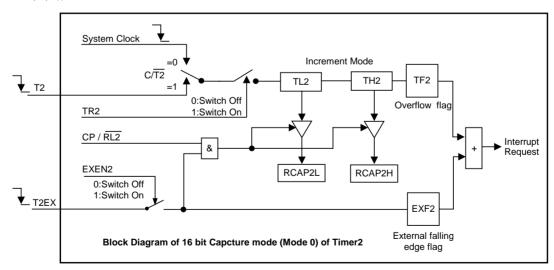

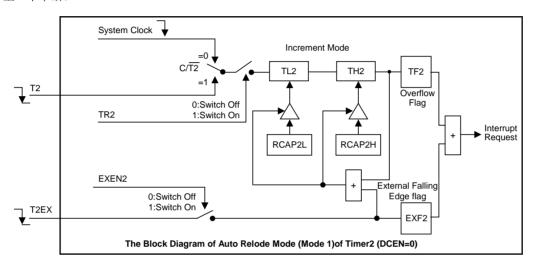

- 3个16位定时器Timer0/1/2

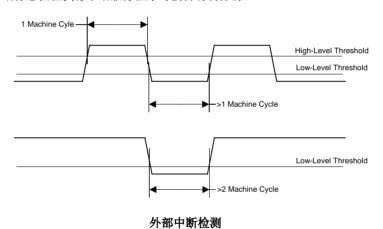

- 3个外部中断INT0/1/2

- 8通道10位逐次逼近型模数转换器(ADC)

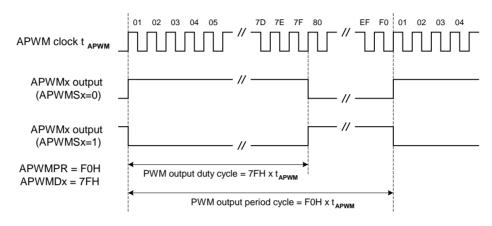

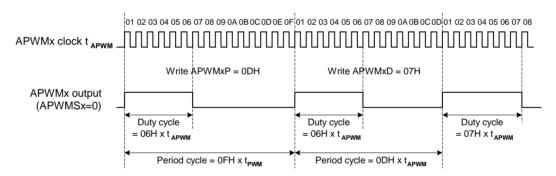

- 3路12位脉冲宽度调制(PWM)输出 1个JTAG接口实现MCU的仿真调试

#### 其他:

1

- 工作环境温度: -40~+105℃

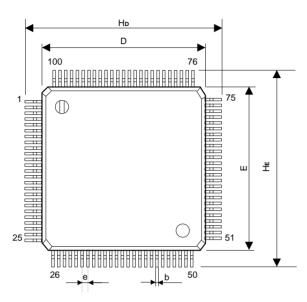

- 封装: LQFP100L (14 X 14)

V1.0

#### 2. 概述

SH99F100A是一款双核(DSP和MCU)芯片,适用于工业控制场合,如电机调速、变频电源等。MCU可以用来处理开关量、输入输出以及通讯,而DSP只需专注于控制算法的运算。

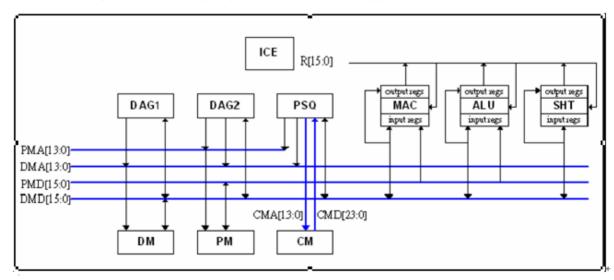

DSP的架构由三个并行的计算单元(ALU,MAC,SHIFTER)、两个独立的地址发生器(DAG)和一个强大的程序序列发生器(PSQ)组成。计算单元提供了所有处理器能够提供的计算功能,包括单周期乘/累加,位操作,移位操作等。双数据地址发生器使得处理器能够在一个周期内从两个数据存储区(Data Memory和Program Memory)同时取出两个数据。程序序列发生器实现了所有指令的单周期操作,快速的中断响应以及嵌套的非CPU干预的循环。16位的PWM模块、正交编码接口(QEI)与14位的流水线型ADC与运算放大器(OP)作为DSP核的内部外设,能够方便地实现多种工业控制算法。

MCU核是一种高速高效率8051兼容核,在同样的振荡频率下,较之传统的8051芯片具有运行更快速,性能更优越的特性,其资源有内置256字节SRAM,外部3840字节SRAM,3个16位定时器和3个外部中断,同时还集成了2个增强型UART,1个SPI接口。

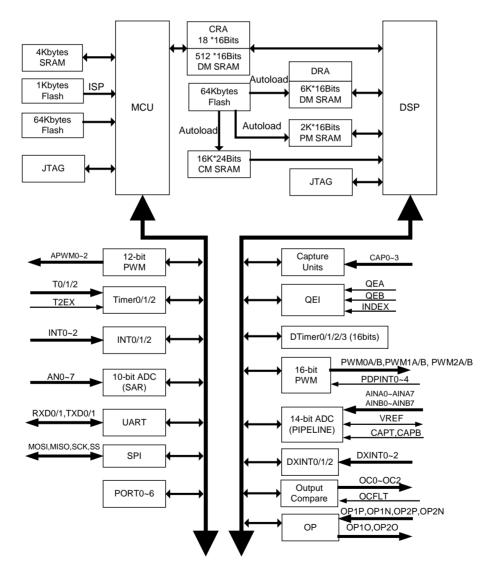

### 3. 方框图

图3-1

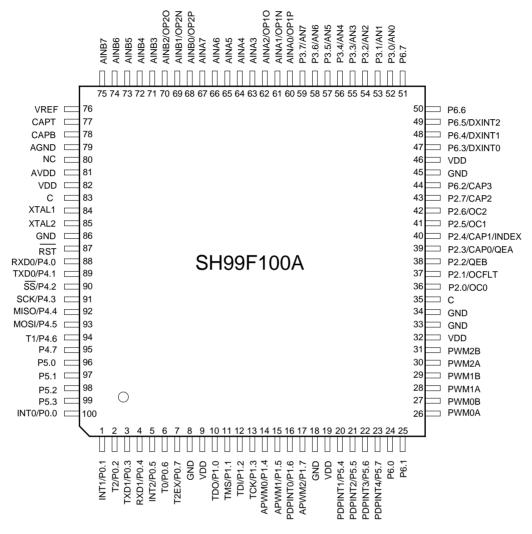

### 4. 引脚配置

#### LQFP100

图4-1

共计100个管脚。

### 引脚功能

| 引脚编号 | 引脚命名            | 默认功能 | 引脚编号          | 引脚命名            | 默认功能      |

|------|-----------------|------|---------------|-----------------|-----------|

| 1    | INT1/P0.1       | P0.1 | 51            | P6.7            |           |

| 2    | T2/P0.2         | P0.2 | 52            | P3.0/AN0        | P3.0      |

| 3    | TXD1/P0.3       | P0.3 | 53            | P3.1/AN1        | P3.1      |

| 4    | RXD1/P0.4       | P0.4 | 54            | P3.2/AN2        | P3.2      |

| 5    | INT2/P0.5       | P0.5 | 55            | P3.3/AN3        | P3.3      |

| 6    | T0/P0.6         | P0.6 | 56            | P3.4/AN4        | P3.4      |

| 7    | T2EX/P0.7       | P0.7 | 57            | P3.5/AN5        | P3.5      |

| 8    | GND             |      | 58            | P3.6/AN6        | P3.6      |

| 9    | $V_{DD}$        |      | 59            | P3.7/AN7        | P3.7      |

| 10   | TDO/P1.0        | P1.0 | 60            | AINA0/OP1P      | AINA0     |

| 11   | TMS/P1.1        | P1.1 | 61            | AINA1/OP1N      | AINA1     |

| 12   | TDI/P1.2        | P1.2 | 62            | AINA2/OP1O      | AINA2     |

| 13   | TCK/P1.3        | P1.3 | 63            | AINA3           |           |

| 14   | APWM0/P1.4      | P1.4 | 64            | AINA4           |           |

| 15   | APWM1/P1.5      | P1.5 | 65            | AINA5           |           |

| 16   | PDPINT0/P1.6    | P1.6 | 66            | AINA6           |           |

| 17   | APWM2/P1.7      | P1.7 | 67            | AINA7           |           |

| 18   | GND             |      | 68            | AINB0/OP2P      | AINB0     |

| 19   | V <sub>DD</sub> |      | 69            | AINB1/OP2N      | AINB1     |

| 20   | PDPINT1/P5.4    | P5.4 | 70            | AINB2/OP2O      | AINB2     |

| 21   | PDPINT2/P5.5    | P5.5 | 71            | AINB3           | 711102    |

| 22   | PDPINT3/P5.6    | P5.6 | 72            | AINB4           |           |

| 23   | PDPINT4/P5.7    | P5.7 | 73            | AINB5           |           |

| 24   | P6.0            | P6.0 | 74            | AINB6           |           |

| 25   | P6.1            | P6.1 | 75            | AINB7           |           |

| 26   | PWM0A           |      | 76            | VREF            |           |

| 27   | PWM0B           |      | 77            | CAPT            |           |

| 28   | PWM1A           |      | 78            | CAPB            |           |

| 29   | PWM1B           |      | 79            | AGND            |           |

| 30   | PWM2A           |      | 80            | AGND            |           |

| 31   | PWM2B           |      | 81            | AVDD            |           |

| 32   | V <sub>DD</sub> |      | 82            | V <sub>DD</sub> |           |

| 33   | GND             |      | 83            | C               |           |

| 34   | GND             |      | 84            | XTAL1           |           |

| 35   | C               |      | 85            | XTAL2           |           |

| 36   | P2.0/OC0        | P2.0 | 86            | GND             |           |

|      |                 |      | <del>- </del> |                 |           |

| 37   | P2.1/OCFLT      | P2.1 | 87            | RST             | <br>D.1.0 |

| 38   | P2.2/QEB        | P2.2 | 88            | RXD0/P4.0       | P4.0      |

| 39   | P2.3/CAP0/QEA   | P2.3 | 89            | TXD0/P4.1       | P4.1      |

| 40   | P2.4/CAP1/INDEX | P2.4 | 90            | SS/P4.2         | P4.2      |

| 41   | P2.5/OC1        | P2.5 | 91            | SCK/P4.3        | P4.3      |

| 42   | P2.6/OC2        | P2.6 | 92            | MISO/P4.4       | P4.4      |

| 43   | P2.7/CAP2       | P2.7 | 93            | MOSI/P4.5       | P4.5      |

| 44   | P6.2/CAP3       | P6.2 | 94            | T1/P4.6         | P4.6      |

| 45   | GND             |      | 95            | P4.7            |           |

| 46   | $V_{DD}$        |      | 96            | P5.0            |           |

| 47   | P6.3/DXINT0     | P6.3 | 97            | P5.1            |           |

| 48   | P6.4/DXINT1     | P6.4 | 98            | P5.2            |           |

| 49   | P6.5/DXINT2     | P6.5 | 99            | P5.3            |           |

| 50   | P6.6            |      | 100           | INT0/P0.0       | P0.0      |

# 5. 引脚描述

| 引脚编号              | 类型  | 说明                 |

|-------------------|-----|--------------------|

| PORT              |     |                    |

| P6.0 - P6.7       | I/O | 8位双向I/O端口          |

| P5.0 - P5.7       | I/O | 8位双向I/O端口          |

| P4.0 - P4.7       | I/O | 8位双向I/O端口          |

| P3.0 - P3.7       | I/O | 8位双向I/O端口          |

| P2.0 - P2.7       | I/O | 8位双向I/O端口          |

| P1.0 - P1.7       | I/O | 8位双向I/O端口          |

| P0.0 - P0.7       | I/O | 8位双向I/O端口          |

| Timer (MCU)       |     |                    |

| T0                | I/O | Timer0外部输入或比较输出    |

| T1                | I/O | Timer1外部输入或比较输出    |

| T2                | I/O | Timer2外部输入/波特率时钟输出 |

| T2EX              | I   | Timer2重载/捕捉/方向控制   |

| PWM控制器 (MCU)      |     |                    |

| APWM2             | 0   | 12位辅助PWM模块2的输出通道   |

| APWM1             | 0   | 12位辅助PWM模块1的输出通道   |

| APWM0             | 0   | 12位辅助PWM模块0的输出通道   |

| EUART (MCU)       |     |                    |

| RXD0              | I/O | EUARTO数据输入/输出引脚    |

| TXD0              | 0   | EUARTO数据输出引脚       |

| RXD1              | I/O | EUART1数据输入/输出引脚    |

| TXD1              | 0   | EUART1数据输出引脚       |

| SPI (MCU)         |     |                    |

| MOSI              | I/O | SPI主输出从输入引脚        |

| MISO              | I/O | SPI主输入从输出引脚        |

| SCK               | I/O | SPI串行时钟引脚          |

| SS                | I   | SPI从属选择引脚          |

| SAR ADC (MCU)     |     |                    |

| ANO - AN7         | I   | MCU中SAR型ADC输入通道    |

| 外部中断 (MCU)        |     |                    |

| INT0 - INT2       | I   | MCU外部中断0,1,2       |

| PWM控制器 (DSP)      |     |                    |

| PWM0A             | 0   | 16位PWM模块的PWM0A通道输出 |

| PWM0B             | 0   | 16位PWM模块的PWM0B通道输出 |

| PWM1A             | 0   | 16位PWM模块的PWM1A通道输出 |

| PWM1B             | 0   | 16位PWM模块的PWM1B通道输出 |

| PWM2A             | 0   | 16位PWM模块的PWM2A通道输出 |

| PWM2B             | 0   | 16位PWM模块的PWM2B通道输出 |

| PDPINT0 - PDPINT4 | I   | 16位PWM模块的功率保护输入引脚  |

### 续上表

| 引脚编 <del>号</del>    | 类型      | 说明                                                                                |

|---------------------|---------|-----------------------------------------------------------------------------------|

| PIPELINE ADC (DSP)  |         |                                                                                   |

| AINA0 - 7、AINB0 - 7 | I       | Pipeline型ADC输入通道                                                                  |

| VREF                | I/O     | Pipeline型ADC外部基准电压输入或内部基准电压输出                                                     |

| CAPT                | 0       | 去耦电容T                                                                             |

| CAPB                | 0       | 去耦电容B                                                                             |

| 运算放大器 (OP)          |         |                                                                                   |

| OP1P                | I       | 运算放大器1正相输入                                                                        |

| OP1N                | I       | 运算放大器1反相输入                                                                        |

| OP1O                | 0       | 运算放大器1输出                                                                          |

| OP2P                | I       | 运算放大器2正相输入                                                                        |

| OP2N                | I       | 运算放大器2反相输入                                                                        |

| OP2O                | 0       | 运算放大器2输出                                                                          |

| 正交编码器接口QEI (DS      | SP)     |                                                                                   |

| QEA                 | I       | 编码器A相输入                                                                           |

| QEB                 | I       | 编码器B相输入                                                                           |

| INDEX               | I       | 编码器索引信号输入                                                                         |

| 输入捕捉CAP (DSP)       |         |                                                                                   |

| CAP0 - CAP3         | I       | 输入捕捉输入引脚                                                                          |

| 输出比较CMPOUT (DS      | P)      |                                                                                   |

| OC0 - OC2           | 0       | 输出比较引脚                                                                            |

| OCFLT               | I       | 输出比较引脚在带保护PWM模式下的保护输入引脚                                                           |

| 外部中断 (DSP)          |         |                                                                                   |

| DXINT0 - DXINT2     | I       | DSP外部中断0,1,2                                                                      |

| 复位、复位、时钟、电池         | <u></u> |                                                                                   |

| RST                 | I       | 该引脚上保持10us以上的低电平,CPU将复位。由于有内建100kΩ上拉电阻连接到<br>V <sub>DD</sub> ,所以仅接一个外部电容即可实现上电复位。 |

| XTAL1               | I       | 振荡器输入                                                                             |

| XTAL2               | 0       | 振荡器输出                                                                             |

| GND                 | Р       | 数字地                                                                               |

| $V_{DD}$            | Р       | 数字电源                                                                              |

| AGND                | Р       | 模拟地                                                                               |

| $AV_DD$             | Р       | 模拟电源                                                                              |

| 稳压源                 |         |                                                                                   |

| С                   | 0       | 内建稳压源滤波电容引脚,推荐选用47μF钽电容接地,LQFP100封装中两个引脚必须<br>有外部PCB连接                            |

| 编程接口 (MCU): JTAG    | i       |                                                                                   |

| TDO                 | 0       | 调试接口:测试数据输出                                                                       |

| TMS                 | I       | 调试接口:测试模式选择                                                                       |

| TDI                 | I       | 调试接口:测试数据输入                                                                       |

| TCK                 | I       | 调试接口:测试时钟输入                                                                       |

#### 6. 寄存器映像

#### 6.1 MCU寄存器映像

MCU內置256字节的直接寻址寄存器,包括通用数据存储器和特殊功能存储器(SFR),MCU的SFR有以下几种:

**CPU**内核寄存器: ACC, B, PSW, SP, DPL, DPH

CPU增强内核寄存器: AUXC, DPL1, DPH1, INSCON, XPAGE1, XPAGE

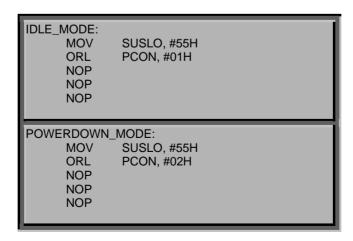

电源和时钟控制寄存器: PCON, SUSLO

Flash寄存器: IB\_OFFSET, XPAGE1, XPAGE, IB\_DATA, IB\_CON1, IB\_CON2, IB\_CON3, IB\_CON4,

IB\_CON5, FLASHCON

数据存储页寄存器: XPAGE1, XPAGE

系统时钟控制寄存器: CLKCON 硬件看门狗定时器寄存器: RSTSTAT

软件复位控制寄存器: SWRCON, DSPRST

通讯寄存器: MCOMIEH, MCOMIEL, MTDCH, MTDCL, MTDIFL, MTDDxH (x = 0-5), MTDDxL

(x = 0.5), DTMCH, DTMCL, DTMIFH, DTMIFL, DTMDxH (x = 0.5), DTMDxL (x = 0.5)

中断系统寄存器: IEN0, IEN1, IPH0, IPL0, IPH1, IPL1, EXF0

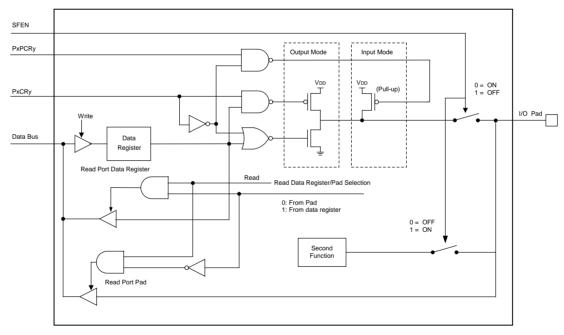

1/0端口寄存器: P0, P1, P2, P3, P4, P5, P6, P0CR, P1CR, P2CR, P3CR, P4CR, P5CR, P6CR,

POPCR, P1PCR, P2PCR, P3PCR, P4PCR, P5PCR, P6PCR

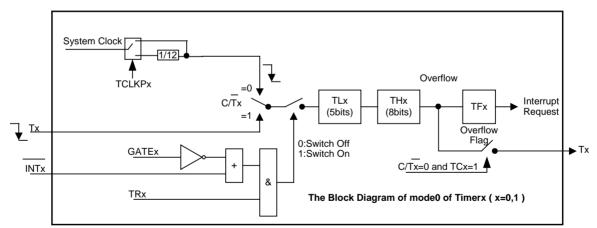

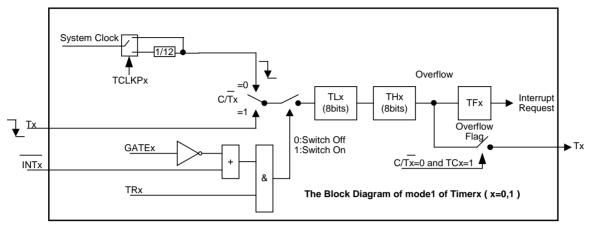

定时器寄存器: TCON, TMOD, TL0, TH0, TL1, TH1, T2CON, T2MOD, TL2, TH2, RCAP2L, RCAP2H,

TCON1

EUARTO寄存器: SCON, SBUF, SADEN, SADDR, PCON, RXDMS

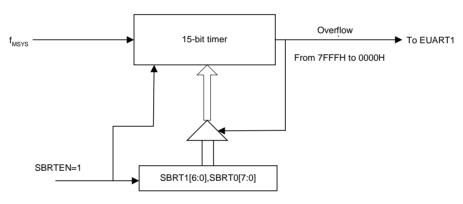

EUART1寄存器: SCON1, SBUF1, SADEN1, SADDR1, SBRT1, SBRT0

SPI寄存器: SPCON, SPSTA, SPDAT

ADC寄存器: ADCON, ADT, ADCH, ADDL, ADDH

辅助PWM寄存器: APWMCON0, APWMCON1, APWMCON2, APWMPL0, APWMPL1, APWMPL2, APWMPH0,

APWMPH1, APWMPH2, APWMDL0, APWMDL1, APWMDL2, APWMDH0, APWMDH1,

APWMDH2

### Bank0

|     | 可位寻址  |         |         |           | 不可位寻址   |          |         |            |     |

|-----|-------|---------|---------|-----------|---------|----------|---------|------------|-----|

|     | 0/8   | 1/9     | 2/A     | 3/B       | 4/C     | 5/D      | 6/E     | 7/F        |     |

| F8H | SPSTA |         |         | IB_OFFSET | IB_DATA |          |         | (Reserved) | FFH |

| F0H | В     | AUXC    | IB_CON1 | IB_CON2   | IB_CON3 | IB_CON4  | IB_CON5 | XPAGE      | F7H |

| E8H | EXF0  | P0PCR   | P1PCR   | P2PCR     | P3PCR   | P4PCR    |         | XPAGE1     | EFH |

| E0H | ACC   | P0CR    | P1CR    | P2CR      | P3CR    | P4CR     |         |            | E7H |

| D8H | SCON1 | SBUF1   | SADDR1  | SADEN1    | MCOMIEL | MCOMIEH  | MTDCL   | MTDCH      | DFH |

| D0H | PSW   |         | MTDIFL  | MTDIFH    | MTDD0L  | MTDD0H   | MTDD1L  | MTDD1H     | D7H |

| C8H | T2CON | T2MOD   | RCAP2L  | RCAP2H    | TL2     | TH2      | TCON1   |            | CFH |

| C0H | P4    |         | MTDD2L  | MTDD2H    | MTDD3L  | MTDD3H   | MTDD4L  | MTDD4H     | C7H |

| B8H | IPL0  | IPL1    | MTDD5L  | MTDD5H    | DTMIFL  | DTMIFH   | DTMD0L  | DTMD0H     | BFH |

| вон | P3    | RSTSTAT | CLKCON  | DSPRST    | IPH0    | IPH1     | DTMD1L  | DTMD1H     | В7Н |

| A8H | IEN0  | IEN1    | DTMD2L  | DTMD2H    | DTMD3L  | DTMD3H   | APWMDL0 | APWMDH0    | AFH |

| A0H | P2    | RXDMS   | SPCON   | SPDAT     | SBRT1   |          | SWRCON  | FLASHCON   | A7H |

| 98H | SCON  | SBUF    | SADDR   | SADEN     | SBRT0   | APWMCON0 | APWMPL0 | APWMPH0    | 9FH |

| 90H | P1    | DTMCL   | DTMCH   | ADCON     | ADT     | ADCH     | ADDL    | ADDH       | 97H |

| 88H | TCON  | TMOD    | TL0     | TL1       | TH0     | TH1      | SUSLO   |            | 8FH |

| 80H | P0    | SP      | DPL     | DPH       | DPL1    | DPH1     | INSCON  | PCON       | 87H |

|     | 0/8   | 1/9     | 2/A     | 3/B       | 4/C     | 5/D      | 6/E     | 7/F        |     |

### Bank1

|     | 可位寻址 |       |       |          | 不可位寻址   |         |         |            |     |

|-----|------|-------|-------|----------|---------|---------|---------|------------|-----|

|     | 0/8  | 1/9   | 2/A   | 3/B      | 4/C     | 5/D     | 6/E     | 7/F        |     |

| F8H |      |       |       |          |         |         |         | (Reserved) | FFH |

| F0H | В    | С     |       |          |         |         |         | XPAGE      | F7H |

| E8H |      | P5PCR | P6PCR |          |         |         |         |            | EFH |

| E0H | ACC  | P5CR  | P6CR  |          |         |         |         |            | E7H |

| D8H |      |       |       |          |         |         |         |            | DFH |

| D0H | PSW  |       |       |          | DTMD4L  | DTMD4H  | DTMD5L  | DTMD5H     | D7H |

| C8H |      |       |       | APWMCON1 | APWMPL1 | APWMPH1 | APWMDL1 | APWMDH1    | CFH |

| C0H |      |       |       | APWMCON2 | APWMPL2 | APWMPH2 | APWMDL2 | APWMDH2    | C7H |

| B8H | IPL0 | IPL1  |       |          |         |         |         |            | BFH |

| вон |      |       |       |          | IPH0    | IPH1    |         |            | В7Н |

| A8H | IEN0 | IEN1  |       |          |         |         |         |            | AFH |

| A0H |      |       |       |          |         |         |         |            | A7H |

| 98H |      |       |       |          |         |         |         |            | 9FH |

| 90H | P6   |       |       |          |         |         |         |            | 97H |

| 88H |      |       |       |          |         |         | SUSLO   |            | 8FH |

| 80H | P5   | SP    | DPL   | DPH      | DPL1    | DPH1    | INSCON  | PCON       | 87H |

|     | 0/8  | 1/9   | 2/A   | 3/B      | 4/C     | 5/D     | 6/E     | 7/F        | _   |

#### 6.2 DSP寄存器映像

DSP寄存器包括非存储器映射的(non-memory mapped)核寄存器和存储器映射(memory mapped)的寄存器。

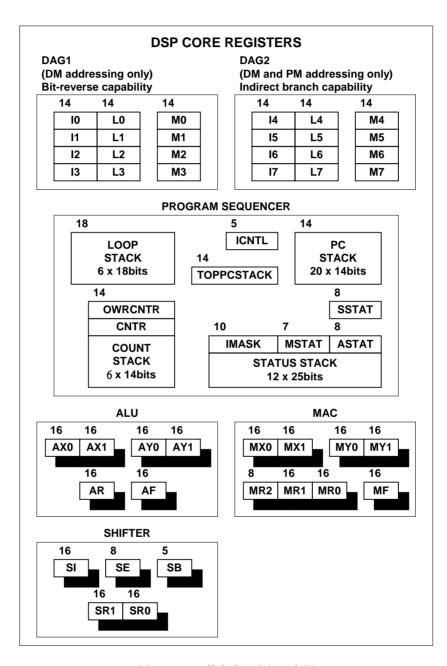

#### 6.2.1 核寄存器 (non-memory mapped)

索引寄存器: 10, 11, 12, 13, 14, 15, 16, 17

长度寄存器: L0, L1, L2, L3, L4, L5, L6, L7

修改寄存器: M0, M1, M2, M3, M4, M5, M6, M7

中断控制寄存器: ICNTL, IMASK

循环控制寄存器: CNTR, OWRCNTR

状态与模式控制寄存器: SSTAT, ASTAT, MSTAT

栈顶寄存器: TOPPCSTACK

计算单元相关寄存器: AX0/1, AY0/1, AR, AF, MX0/1, MY0/1, MR2/1/0, MF, SI, SE, SB, SR1/0

#### 6.2.2 存储器映射寄存器 (memory-mapped)

DSP系统控制寄存器: DSYSR

DSP堆栈状态寄存器: DCCSD, DCLSD, DCSSD, DCPSD

DSP时钟与看门狗控制寄存器: DCLKCON

与MCU通讯寄存器: DCOMIE, DTMC, DTMIF, DTMDx (x = 0-5), MTDC, MTDIF, MTDDx (x = 0-5)

DSP外部中断寄存器: DXINTCON, DXINTIF, INTPR0, INTPR1

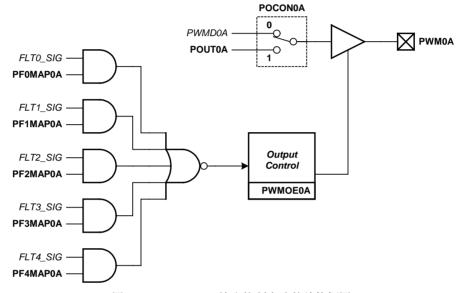

PWMLO, PWMTCON, PWMTCNT, PWMWCON, PWMWDxA (x = 0-2),

PWMWDxB (x = 0-2), PWMxDTR (x = 0-2), PWMxDTF (x = 0-2), PWMECON, PWMECMPx (x = 0-2), PWMFCON, PWMFSTAT, PWMFDEB, PWMFMAPx (x = 0-2),

PWMOCON, PWMOE, PWMIE, PWMIF

QEICON, QFLTCON, QPOSCNT, QPOSLAT, QTMCON, QTMCNT, QTMLAT,

QCNTMAX, QEIINT

ADCN1, ADCON1, ADPTR, ADPCH, ADINT, ADCHSELx (x = 0-3), ADRRx (x = 0-15)

**DSP**定时器寄存器: TMRxPRD (x = 0-3), TMRxPBUF (x = 0-3), TMRxCNT (x = 0-3), TMRMOD, TMRCON,

TMRPSC0, TMRPSC1, TMRINT

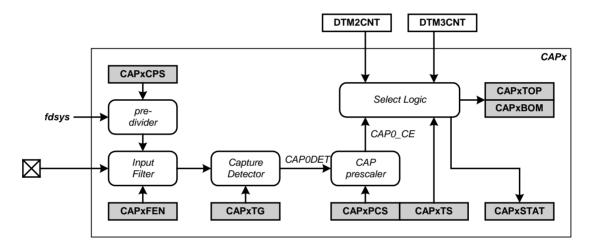

输入捕捉寄存器: CAPxCON (x = 0-3), CAPxTOP (x = 0-3), CAPxBOM (x = 0-3), CAPINT

输出比较寄存器: OCxCON(x = 0-2), OCxR(x = 0-2), OCxRS(x = 0-2), OCINT

运算放大器: OPCON

| 寄存器名      | 地址    | 15        | 14                                              | 13       | 12       | 11        | 10         | 9          | 8                 | 7        | 6                   | 5         | 4                   | 3                   | 2                   | 1           | 0          | 复位值                 |

|-----------|-------|-----------|-------------------------------------------------|----------|----------|-----------|------------|------------|-------------------|----------|---------------------|-----------|---------------------|---------------------|---------------------|-------------|------------|---------------------|

| DSP系统控制   |       |           | 1                                               |          |          | 1         |            |            |                   |          |                     |           | <u> </u>            |                     |                     | ·           |            |                     |

| DSYSR     | 3FFF  | -         | -                                               | -        | -        | -         | -          | -          | -                 | -        | -                   | -         | -                   | -                   | -                   | BIASRND     |            | 0000 0000 0000 0000 |

| DCLKCON   | 3FFE  | DSCMIE    | DSCMST                                          | -        | -        | -         |            | DWDT       |                   | -        | -                   | _         | PLL LOCK            | PLL EN              |                     | PLL MUL     |            | 0000 0000 0000 0000 |

| DCCSD     | 3FFD  | -         | -                                               | -        | -        | _         | -          | -          | -                 | -        | _                   | -         | -                   | -                   |                     | DCCSD       |            | 0000 0000 0000 0000 |

| DCLSD     | 3FFC  | _         | _                                               | -        | -        | _         | _          | -          | _                 | -        | _                   | _         | -                   | -                   |                     | DCLSD       |            | 0000 0000 0000 0000 |

| DCSSD     | 3FFB  | _         | -                                               | -        | -        | _         | _          | -          | -                 | -        | _                   | -         | -                   |                     | DC                  | SSD         |            | 0000 0000 0000 0000 |

| DCPSD     | 3FFA  | -         | -                                               | -        | -        | -         | -          | -          | _                 | _        | -                   | _         |                     |                     | DCPSD               |             |            | 0000 0000 0000 0000 |

| DSP中断     | 1     |           |                                                 |          |          |           |            |            |                   |          |                     |           |                     |                     |                     |             |            |                     |

| INTPR1    | 3FF7  | -         | -                                               | -        | -        | -         | -          | -          | -                 | -        | -                   | -         | -                   | IPR                 | PWM                 | IPR 1       | TMR0       | 0000 0000 0000 0000 |

| INTPR0    | 3FF6  | IPR       | ADC                                             | IPR      | QEI      | IPR D     | XIOC       | IPR        | TMR1              | IPR      | MR2                 | IPR       | TMR3                |                     | CAP                 | IPR C       |            | 0000 0000 0000 0000 |

| DXINTCON  | 3FF5  | -         | -                                               |          | 2MOD     | DXINT     | 1MOD       |            | ГОМОД             | -        | -                   | _         | -                   | -                   | DXINT2IE            | DXINT1IE    | DXINT0IE   | 0000 0000 0000 0000 |

| DXINTIF   | 3FF4  | -         | -                                               | -        |          | -         | -          | -          | -                 | -        | -                   | -         | -                   | -                   | DXINT2IF            | DXINT1IF    | DXINT0IF   | 0000 0000 0000 0000 |

| PWM模块     |       |           |                                                 |          |          |           |            |            |                   |          |                     |           |                     |                     |                     |             |            |                     |

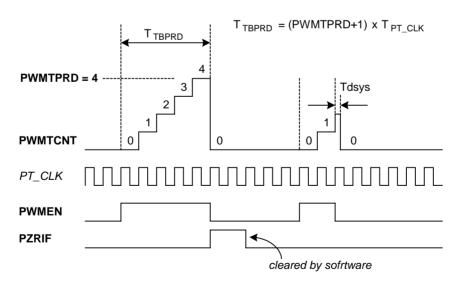

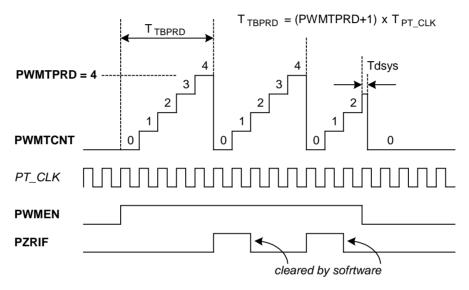

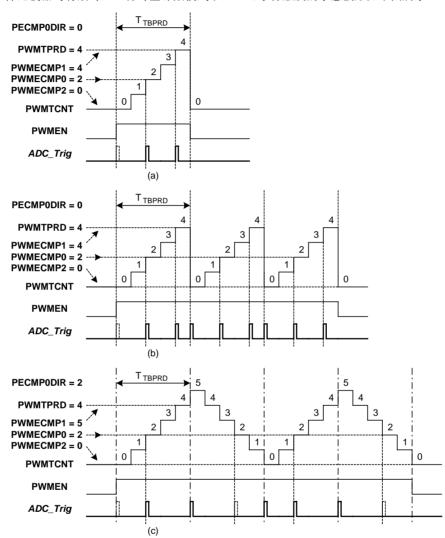

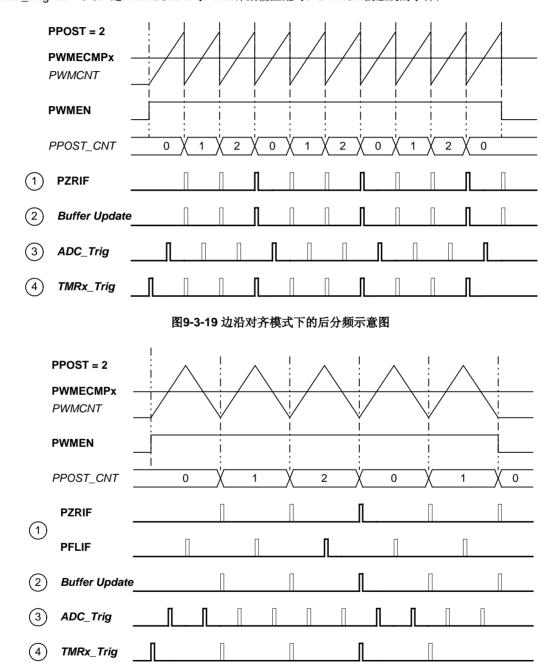

| PWMTCON   | 3FEF  | PWMEN     | PWN                                             | ИЕМU     | PTDIR    |           | PP         | OST        |                   | -        | -                   | -         | PTN                 | MOD                 |                     | PTCLKPS     |            | 0000 0000 0000 0000 |

| PWMTPRD   | 3FEE  | 1 WINIEIV |                                                 | ILIVIO   | TIBIK    |           |            | 301        | PWM时基             | 周期寄存器    |                     |           |                     | 100                 | 1                   | 1 TOLIG     |            | 0000 0000 0000 0000 |

| PWMTCNT   | 3FED  |           |                                                 |          |          |           |            |            |                   | 计数寄存器    |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMWCON   | 3FEC  | _         | I -                                             | -        | PWDLD    | PWSYM     | PWMOD2     | PWMOD1     | PWMOD0            |          | MOD                 | PWPLR2A   | PWPLR2B             | PWPLR1A             | PWPLR1B             | PWPLR0A     | PWPLR0B    | 0000 0000 0010 1010 |

| PWMWD2A   | 3FEB  |           |                                                 |          | 1 111020 | 1 1101111 | 1 WINODE   | 1 11111001 |                   | 空比寄存器    | WOD .               | 1 WI LIKE | 1 WI LIKED          | 1 WI LICIA          | 1 WI LIKID          | 1 WI LIKO/K | 1 WI LIKOD | 0000 0000 0000 0000 |

| PWMWD2B   | 3FEA  |           |                                                 |          |          |           |            |            |                   | 空比寄存器    |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMWD1A   | 3FE9  |           |                                                 |          |          |           |            |            |                   | 空比寄存器    |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMWD1B   | 3FE8  |           |                                                 |          |          |           |            |            |                   | 空比寄存器    |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMWD0A   | 3FE7  |           |                                                 |          |          |           |            |            |                   |          |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMWD0B   | 3FE6  |           | PWM0A占空比寄存器 PWM0B占空比寄存器                         |          |          |           |            |            |                   |          |                     |           |                     | 0000 0000 0000 0000 |                     |             |            |                     |

| PWM2DTR   | 3FE5  |           | PWM2A/B上升沿死区延迟时间寄存器                             |          |          |           |            |            |                   |          |                     |           |                     | 0000 0000 0000 0000 |                     |             |            |                     |

| PWM2DTF   | 3FE4  |           | PWM2A/B下降沿死区延迟时间寄存器                             |          |          |           |            |            |                   |          |                     |           |                     |                     | 0000 0000 0000 0000 |             |            |                     |

| PWM1DTR   | 3FE3  |           | PWM1A/B上升沿死区延迟时间寄存器                             |          |          |           |            |            |                   |          |                     |           |                     | 0000 0000 0000 0000 |                     |             |            |                     |

| PWM1DTF   | 3FE2  |           | PWM1A/B下降沿死区延迟时间寄存器                             |          |          |           |            |            |                   |          |                     |           | 0000 0000 0000 0000 |                     |                     |             |            |                     |

| PWM0DTR   | 3FE1  |           |                                                 |          |          |           |            |            | <b>MOA/B</b> 上升沿列 |          |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWM0DTF   | 3FE0  |           |                                                 |          |          |           |            |            | MOA/B下降沿列         |          |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMECON   | 3FDF  | -         | -                                               | -        | -        | -         |            | PEMOD      | 10,42   1410/     |          | IPODIR              | PECI      | MP2EN               | PECM                | /P1EN               | PECM        | P0FN       | 0000 0000 0000 0000 |

| PWMECMP2  | 3FDE  |           |                                                 |          |          |           |            |            | PWM事件師为           | 发比较寄存器2  | _                   | . 20.     |                     | . 20                |                     | . 20        | . 02.1     | 0000 0000 0000 0000 |

| PWMECMP1  | 3FDD  |           |                                                 |          |          |           |            |            | PWM事件触知           |          |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMECMP0  | 3FDC  |           |                                                 |          |          |           |            |            |                   | 发比较寄存器C  |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| PWMFCON   | 3FDB  | -         | -                                               | -        | PFLT4RM  | PFLT3RM   | PFLT2RM    | PFLT1RM    | PFLT0RM           | -        | -                   | -         | PFLT4EN             | PFLT3EN             | PFLT2EN             | PFLT1EN     | PFLT0EN    | 0000 0000 0000 0000 |

| PWMFSTAT  | 3FDA  | _         | -                                               | -        | PFLT4TG  | PFLT3TG   | PFLT2TG    | PFLT1TG    | PFLT0TG           | -        | _                   | _         | PFLT4ST             | PFLT3ST             | PFLT2ST             | PFLT1ST     | PFLT0ST    | 0000 0000 000u uuuu |

| PWMFDEB   | 3FD9  | _         |                                                 | PFLT4DEB |          |           | PFLT3DEB   |            |                   | PFLT2DEB |                     |           | PFLT1DEB            |                     |                     | PFLT0DEB    |            | 0000 0000 0000 0000 |

| PWMFMAP2  | 3FD8  | -         | -                                               | -        | PF4MAP2A | PF3MAP2A  | PF2MAP2A   | PF1MAP2A   | PF0MAP2A          | -        | -                   | -         | PF4MAP2B            | PF3MAP2B            | PF2MAP2B            | PF1MAP2B    | PF0MAP2B   | 0000 0000 0000 0000 |

| PWMFMAP1  | 3FD7  | _         | -                                               | -        | PF4MAP1A |           | PF2MAP1A   | PF1MAP1A   | PF0MAP1A          | -        | _                   | _         | PF4MAP1B            | PF3MAP1B            | PF2MAP1B            | PF1MAP1B    | PF0MAP1B   | 0000 0000 0000 0000 |

| PWMFMAP0  | 3FD6  | -         | -                                               | -        | PF4MAP0A | PF3MAP0A  | PF2MAP0A   | PF1MAP0A   | PF0MAP0A          | -        | -                   | -         | PF4MAP0B            | PF3MAP0B            | PF2MAP0B            | PF1MAP0B    | PF0MAP0B   | 0000 0000 0000 0000 |

| PWMOCON   | 3FD5  | POSYNC    | -                                               | POCON2A  | POCON2B  | POCON1A   | POCON1B    | POCON0A    | POCON0B           | -        | -                   | POUT2A    | POUT2B              | POUT1A              | POUT1B              | POUT0A      | POUT0B     | 0000 0000 0000 0000 |

| PWMOE     | 3FD4  | -         | PWMOE2A PWMOE1B PWMOE1B PWMOE1B PWMOE0B PWMOE0B |          |          |           |            |            |                   |          | 0000 0000 0000 0000 |           |                     |                     |                     |             |            |                     |

| PWMIE     | 3FD3  | -         | -                                               | -        | -        | -         | -          | -          | -                 | PZRIE    | PFLIE               | -         | PDP4IE              | PDP3IE              | PDP2IE              | PDP1IE      | PDP0IE     | 0000 0000 0000 0000 |

| PWMIF     | 3FD2  | -         | PZRIF PFLIF - PDP4IF PDP3IF PDP1IF PDP0IF       |          |          |           |            |            |                   |          |                     |           |                     |                     | 0000 0000 0000 0000 |             |            |                     |

| PWMLO     | 3FD1  |           |                                                 |          |          |           |            |            | PWM模块             | 锁定寄存器    | 1                   |           |                     |                     | I                   |             |            | 0000 0000 0000 0000 |

| QEI模块     |       | 1         |                                                 |          |          |           |            |            | ,,,,,             | 14 mm    |                     |           |                     |                     |                     |             |            |                     |

| QEICON    | 3FCF  | OPI       | EMU                                             |          | -        | -         | -          | QPDIR      | QIDXS             |          | -                   | QSWAP     | QIDXEN              | QEIEN               | QPCAPEN             | QPN         | MOD        | 0000 0000 0000 0000 |

| QFLTCON   | 3FCE  |           | o                                               | -        | -        | _         |            | -          | -                 | QIDXFEN  |                     | QIDXCPS   | SIDNEN              | QABFEN              | CI O/II LIV         | QABCPS      |            | 0000 0000 0000 0000 |

| QPOSCNT   | 3FCD  |           |                                                 |          |          |           |            |            | QEI位置             | 置计数器     | 1                   | SIDNOI 0  |                     | W.D. LIV            | 1                   | 2,100,0     |            | 0000 0000 0000 0000 |

| QPOSLAT   | 3FCC  |           |                                                 |          |          |           |            |            |                   | 值锁存寄存器   |                     |           |                     |                     |                     |             |            | 0000 0000 0000 0000 |

| QTMCON    | 3FCB  | OTI       | EMU                                             | -        |          | QTIE      | QTCAPIE    | QTIF       | QTCAPIF           | QTEN     | -                   | ОТ        | CPS                 |                     | OT                  | EPS         |            | 0000 0000 0000 0000 |

| Q I NIOON | 31 00 | QII       | _111.0                                          |          |          | Q IIL     | & I OAI IL | QIII       | Q I U/I II        | Q I LIV  |                     | Q i       | J. J                |                     | QI                  |             |            | 0000 0000 0000      |

| QTMCNT    | 3FCA |                       | QTimer计数器      |          |     |          |                        |        |           |         |       |                     | 0000 0000 0000 0000 |                     |        |         |         |                     |

|-----------|------|-----------------------|----------------|----------|-----|----------|------------------------|--------|-----------|---------|-------|---------------------|---------------------|---------------------|--------|---------|---------|---------------------|

| QTMLAT    | 3FC9 |                       |                |          |     |          |                        |        | QTimer计数值 |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| QCNTMAX   | 3FC8 |                       |                |          |     |          |                        |        | 最大计数      |         |       |                     |                     |                     |        |         |         | 1111 1111 1111 1111 |

| QEIINT    | 3FC7 | -                     | -              | -        |     | -        | QEIIE                  | QCEIE  | QPEIE     | -       | -     | -                   | -                   | -                   | QEIIF  | QCEIF   | QPEIF   | 0000 0000 0000 0000 |

| ADC模块     |      |                       |                |          |     |          |                        |        | 1         |         |       |                     |                     |                     |        | 1       | 1       |                     |

| ADCON1    | 3FBF | ADE                   | MU             | ADM      | IOD | -        | -                      | -      | -         | ADEN    | ADREN | ADVRS               | -                   |                     | AD     | CPS     |         | 0000 0000 0000 0000 |

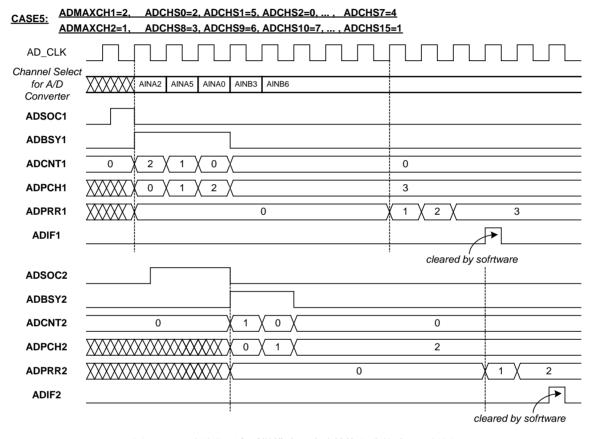

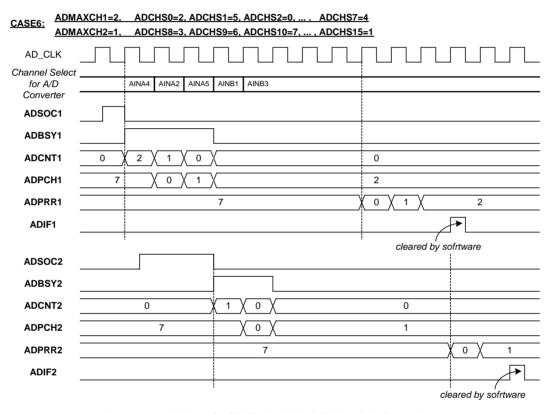

| ADCON2    | 3FBE |                       |                | ADMAXCH2 |     | ADEVTEN2 | ADCTU2                 | ADRST2 | ADSOC2    |         | ADMA  | AXCH1               |                     | ADEVTEN1            | ADCTU1 | ADRST1  | ADSOC1  | 0000 0000 0000 0000 |

| ADPTR     | 3FBD | -                     |                | ADCNT2   |     | -        | - ADPRR2 ADCNT1 ADPRR1 |        |           |         |       | 0000 0000 0000 0000 |                     |                     |        |         |         |                     |

| ADPCH     | 3FBC | -                     | -              | -        | -   | -        |                        |        |           |         |       |                     | 0000 0000 0000 0000 |                     |        |         |         |                     |

| ADINT     | 3FBB | ADIE2                 | -              | -        | -   | -        | -                      | ADBSY2 | ADIF2     | ADIE1   | -     | -                   | -                   | -                   | -      | ADBSY1  | ADIF1   | 0000 0000 0000 0000 |

| ADCHSEL3  | 3FB3 |                       | ADC            | CHS15    |     |          | ADC                    | HS14   |           |         | ADC   | HS13                |                     |                     | ADC    | CHS12   |         | 0000 0000 0000 0000 |

| ADCHSEL2  | 3FB2 |                       | ADC            | CHS11    |     |          | ADC                    | HS10   |           |         | ADO   | CHS9                |                     |                     | ADO    | CHS8    |         | 0000 0000 0000 0000 |

| ADCHSEL1  | 3FB1 |                       | ADO            | CHS7     |     |          | ADC                    | CHS6   |           |         | ADO   | CHS5                |                     |                     | ADO    | CHS4    |         | 0000 0000 0000 0000 |

| ADCHSEL0  | 3FB0 |                       | ADO            | CHS3     |     |          | ADC                    | CHS2   |           |         | ADO   | CHS1                |                     |                     | ADO    | CHS0    |         | 0000 0000 0000 0000 |

| ADRR15    | 3FAF |                       |                |          |     |          |                        |        | AD转换结员    | 果寄存器15  |       |                     |                     | II.                 |        |         |         | 0000 0000 0000 0000 |

| ADRR14    | 3FAE |                       |                |          |     |          |                        |        | AD转换结员    | 果寄存器14  |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR13    | 3FAD |                       |                |          |     |          |                        |        | AD转换结果    | 果寄存器13  |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR12    | 3FAC |                       |                |          |     |          |                        |        | AD转换结点    | 果寄存器12  |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR11    | 3FAB |                       |                |          |     |          |                        |        | AD转换结点    | 果寄存器11  |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR10    | 3FAA |                       |                |          |     |          |                        |        | AD转换结员    | 果寄存器10  |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR9     | 3FA9 |                       |                |          |     |          |                        |        | AD转换结     | 果寄存器9   |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR8     | 3FA8 |                       |                |          |     |          |                        |        | AD转换结     | 果寄存器8   |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR7     | 3FA7 |                       |                |          |     |          |                        |        | AD转换结     | 果寄存器7   |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR6     | 3FA6 |                       | AD转换结果寄存器6     |          |     |          |                        |        |           |         |       |                     | 0000 0000 0000 0000 |                     |        |         |         |                     |

| ADRR5     | 3FA5 |                       | AD转换结果寄存器5     |          |     |          |                        |        |           |         |       |                     |                     | 0000 0000 0000 0000 |        |         |         |                     |

| ADRR4     | 3FA4 |                       | AD转换结果寄存器4     |          |     |          |                        |        |           |         |       |                     | 0000 0000 0000 0000 |                     |        |         |         |                     |

| ADRR3     | 3FA3 |                       | AD转换结果寄存器3     |          |     |          |                        |        |           |         |       |                     |                     | 0000 0000 0000 0000 |        |         |         |                     |

| ADRR2     | 3FA2 |                       |                |          |     |          |                        |        | AD转换结     | 果寄存器2   |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR1     | 3FA1 |                       |                |          |     |          |                        |        | AD转换结     |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| ADRR0     | 3FA0 |                       |                |          |     |          |                        |        | AD转换结     | 果寄存器0   |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

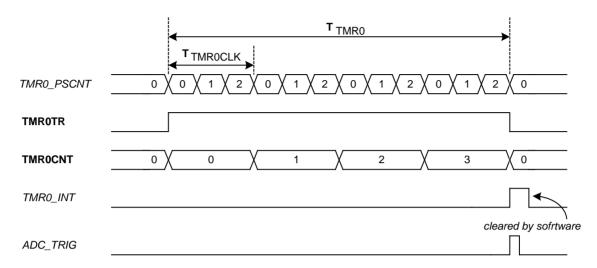

| DSP定时器    |      |                       |                |          |     |          |                        |        |           |         |       |                     |                     |                     |        |         |         |                     |

| TMRMOD    | 3F9F | TMR                   |                | TMR2     |     | TMR′     |                        | TMR    | ROADT     | -       | -     | -                   | -                   |                     |        |         | TMR0MOD | 0000 0000 0000 0000 |

| TMRCON    | 3F9E | TMR                   | BEMU           | TMR2     | EMU | TMR1     | IEMU                   | TMR    | 0EMU      | -       | -     | -                   | -                   | TMR3TR              | TMR2TR | TMR1TR  | TMR0TR  | 0000 0000 0000 0000 |

| TMRPSC1   | 3F9D |                       |                |          |     | 3PSC     |                        |        |           |         |       |                     | TMR                 | 2PSC                |        |         |         | 0000 0000 0000 0000 |

| TMRPSC0   | 3F9C |                       |                |          | TMR | 1PSC     |                        |        |           |         |       |                     | TMR                 | OPSC                |        |         |         | 0000 0000 0000 0000 |

| TMR3CNT   | 3F9B |                       |                |          |     |          |                        |        | DTimer3   |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR2CNT   | 3F9A |                       |                |          |     |          |                        |        | DTimer2i  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR1CNT   | 3F99 |                       |                |          |     |          |                        |        | DTimer1   |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR0CNT   | 3F98 |                       |                |          |     |          |                        |        | DTimer0i  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR3PRD   | 3F97 |                       |                |          |     |          |                        |        | DTimer3月  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR2PRD   | 3F96 |                       |                |          |     |          |                        |        | DTimer2月  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR1PRD   | 3F95 |                       |                |          |     |          |                        |        | DTimer1月  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR0PRD   | 3F94 |                       |                |          |     |          |                        |        | DTimer0月  |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR3PBUF  | 3F93 |                       | DTimer3周期缓存寄存器 |          |     |          |                        |        |           |         |       |                     | 0000 0000 0000 0000 |                     |        |         |         |                     |

| TMR2PBUF  | 3F92 |                       |                |          |     |          |                        |        | DTimer2周其 |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR1PBUF  | 3F91 |                       |                |          |     |          |                        |        | DTimer1周其 |         |       |                     |                     |                     |        |         |         | 0000 0000 0000 0000 |

| TMR0PBUF  | 3F90 |                       |                |          |     |          |                        | 1      | DTimer0周其 | 用缓存寄存器  |       |                     |                     |                     | T      | 1       |         | 0000 0000 0000 0000 |

| TMRINT    | 3F8F | -                     | -              | -        | -   | TMR3IE   | TMR2IE                 | TMR1IE | TMR0IE    | -       | -     | -                   | -                   | TMR3IF              | TMR2IF | TMR1IF  | TMR0IF  | 0000 0000 0000 0000 |

| 输入捕获(CAP) |      |                       | 1              |          |     |          |                        |        |           |         |       |                     |                     |                     | T.     |         |         |                     |

| CAP3CON   | 3F7F | CAP3TS CAP3TG CAP3PSC |                |          |     | -        | -                      |        | 3STAT     | CAP3FEN |       | CAP3CPS             |                     | 0000 0000 0000 0000 |        |         |         |                     |

| CAP2CON   | 3F7E | CAP2TS CAP2TG CAP2PSC |                |          |     | -        | -                      |        | 2STAT     | CAP2FEN |       | CAP2CPS             |                     | 0000 0000 0000 0000 |        |         |         |                     |

| CAP1CON   | 3F7D | CAP1TS                | CAI            | P1TG     |     |          | CAP1PSC                |        |           | -       | -     | CAP <sup>2</sup>    | 1STAT               | CAP1FEN             |        | CAP1CPS |         | 0000 0000 0000 0000 |

| CAP0CON   | 3F7C      | CAP0TS | CAP          | 0TG     |         |         | CAP0PSC |        |          | -                    | -      | CAPO                | STAT   | CAP0FEN |        |        |        | 0000 0000 0000 0000 |

|-----------|-----------|--------|--------------|---------|---------|---------|---------|--------|----------|----------------------|--------|---------------------|--------|---------|--------|--------|--------|---------------------|

| CAPINT    | 3F7B      | CAP3IM | CAP2IM       | CAP1IM  | CAP0IM  | CAP3IE  | CAP2IE  | CAP1IE | CAP0IE   | -                    | -      | -                   | -      | CAP3IF  | CAP2IF | CAP1IF | CAP0IF | 0000 0000 0000 0000 |

| CAP3TOP   | 3F77      |        |              |         |         |         |         |        | CAP3存储栈  | 栈顶寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP3BOM   | 3F76      |        |              |         |         |         |         |        | CAP3存储栈  | 栈底寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP2TOP   | 3F75      |        |              |         |         |         |         |        | CAP2存储栈  | 栈顶寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP2BOM   | 3F74      |        |              |         |         |         |         |        | CAP2存储村  | 栈底寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP1TOP   | 3F73      |        |              |         |         |         |         |        | CAP1存储栈  | 栈顶寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP1BOM   | 3F72      |        |              |         |         |         |         |        | CAP1存储栈  | 栈底寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP0TOP   | 3F71      |        |              |         |         |         |         |        | CAP0存储栈  | 栈顶寄存器                |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| CAP0BOM   | 3F70      |        | CAP0存储栈栈底寄存器 |         |         |         |         |        |          |                      |        | 0000 0000 0000 0000 |        |         |        |        |        |                     |

| 输出比较(OC)植 | <b>莫块</b> |        |              |         |         |         |         |        |          |                      |        |                     |        |         |        |        |        |                     |

| OC2CON    | 3F6F      | -      | -            | -       | -       | -       | -       | -      | -        | -                    | -      | -                   | -      | OC2TS   |        | OC2MOD |        | 0000 0000 0000 0000 |

| OC1CON    | 3F6E      | -      | -            | -       | -       | -       | -       | -      | -        | -                    | -      | -                   | -      | OC1TS   |        | OC1MOD |        | 0000 0000 0000 0000 |

| OC0CON    | 3F6D      | -      | -            | -       | -       | -       | -       | -      | -        | -                    | -      | -                   | -      | OC0TS   |        | OC0MOD |        | 0000 0000 0000 0000 |

| OCINT     | 3F6C      | -      |              | -       | -       | OCFIE   | OC2IE   | OC1IE  | OC0IE    |                      | OCFCPS |                     | OCFST  | OCFIF   | OC2IF  | OC1IF  | OC0IF  | 0000 0000 0000 0000 |

| OC2R      | 3F6B      |        |              |         |         | •       |         |        | 通道2比     | 较寄存器                 |        |                     |        | •       |        |        |        | 0000 0000 0000 0000 |

| OC2RS     | 3F6A      |        |              |         |         |         |         |        | 通道2比较辅   | 前助寄存器 <sup>(2)</sup> |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| OC1R      | 3F69      |        |              |         |         |         |         |        | 通道1比     | 较寄存器                 |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| OC1RS     | 3F68      |        |              |         |         |         |         |        | 通道1比较辅   | 前助寄存器 <sup>(2)</sup> |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| OC0R      | 3F67      |        |              |         |         |         |         |        | 通道0比     | 较寄存器                 |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| OC0RS     | 3F66      |        |              |         |         |         |         |        | 通道0比较辅   | 前助寄存器 <sup>(2)</sup> |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| 运算放大器(OP  | ')模块      |        |              |         |         |         |         |        |          |                      |        |                     |        |         |        |        |        |                     |

| OPCON     | 3F64      |        |              |         |         |         |         |        |          |                      |        |                     |        |         |        | OP2EN  | OP1EN  | 0000 0000 0000 0000 |

| 通信控制(COM  | M)模块      |        |              |         |         |         |         |        |          |                      |        |                     |        |         |        |        |        |                     |

| DCOMIE    | 3F60      | MCMDIE | MFG14IE      | MFG13IE | MFG12IE | MFG11IE | MFG10IE | MFG9IE | MFG8IE   | MFG7IE               | MFG6IE | MFG5IE              | MFG4IE | MFG3IE  | MFG2IE | MFG1IE | MFG0IE | 0000 0000 0000 0000 |

| DTMC      | 3F5F      |        |              |         |         |         |         |        | DSP至MCU  | 的命令寄存器               |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMIF     | 3F5E      | DCMDIF | DFG14IF      | DFG13IF | DFG12IF | DFG11IF | DFG10IF | DFG9IF | DFG8IF   | DFG7IF               | DFG6IF | DFG5IF              | DFG4IF | DFG3IF  | DFG2IF | DFG1IF | DFG0IF | 0000 0000 0000 0000 |

| DTMD5     | 3F5D      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器5              | i      |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMD4     | 3F5C      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器4              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMD3     | 3F5B      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器3              | 1      |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMD2     | 3F5A      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器2              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMD1     | 3F59      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器1              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| DTMD0     | 3F58      |        |              |         |         |         |         |        | DSP至MCU的 | 的数据寄存器0              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDC      | 3F57      |        |              |         |         |         |         |        | MCU至DSP的 | 的命令寄存器               |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDIF     | 3F56      | MCMDIF | MFG14IF      | MFG13IF | MFG12IF | MFG11IF | MFG10IF | MFG9IF | MFG8IF   | MFG7IF               | MFG6IF | MFG5IF              | MFG4IF | MFG3IF  | MFG2IF | MFG1IF | MFG0IF | 0000 0000 0000 0000 |

| MTDD5     | 3F55      |        |              |         |         |         |         |        | MCU至DSP的 | 的数据寄存器5              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDD4     | 3F54      |        |              |         |         |         |         |        | MCU至DSP的 |                      |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDD3     | 3F53      |        |              |         |         |         |         |        | MCU至DSP的 | 的数据寄存器3              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDD2     | 3F52      |        |              |         |         |         |         |        | MCU至DSP的 | 的数据寄存器2              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDD1     | 3F51      |        |              |         |         |         |         |        | MCU至DSP的 | 的数据寄存器1              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

| MTDD0     | 3F50      |        |              |         |         |         |         |        | MCU至DSP的 | 的数据寄存器0              |        |                     |        |         |        |        |        | 0000 0000 0000 0000 |

### 注意:

- (1) 灰底的位置表示只读特性;

- (2) 当OCxMOD = 111时,OCxRS寄存器也为只读特性。

### 7. 系统集成模块SIM(System Integrated Module)

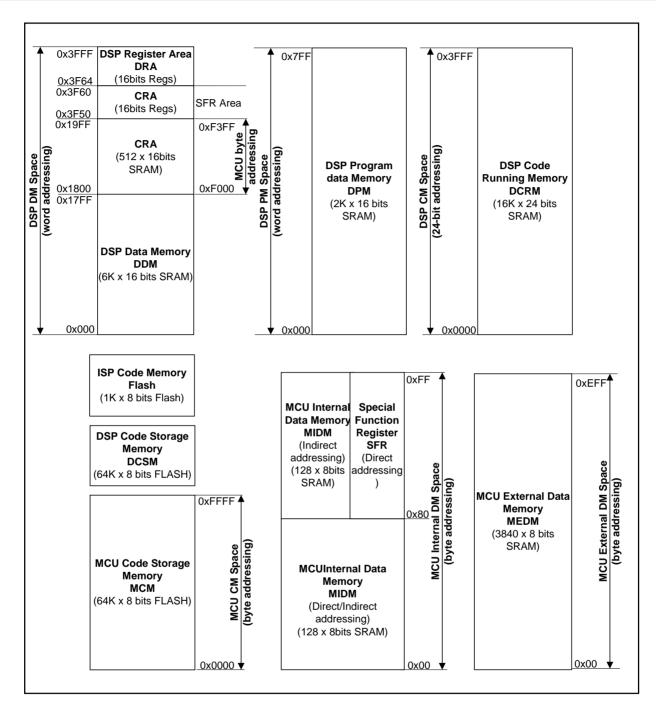

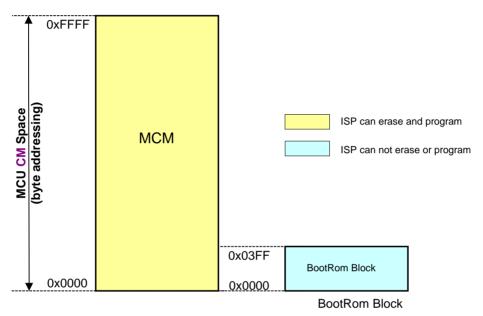

#### 7.1 存储器架构

SH99F100A的片上存储器包括128KBytes Flash、1KBytes BootRom(for ISP)、(12K+4K+48K+1K)Bytes高速SRAM(12Kbytes在DDM空间中,4Kbytes在DPM空间中,48Kbytes在DCM空间中,1KBytes在DDM空间中)以及4KBytes低速SRAM。这些存储器和寄存器分为以下几个部分:

MIDM - MCU Internal Data Memory

MCM - MCU Code Memory

DDM - DSP Data Memory

DPM - DSP Program Data Memory

DPM - DSP Program Data Memory

**DDM** - DSP Data Memory **DRA** - DSP Registers Area **DPM** - DSP Program Data Memory **CRA** - Communication Registers and Data Area

SFR - Special Function Registers for MCU

DCSM - DSP Code Storage Memory

BOOTROM - ISP Code Running Memory

MCM: 64K bytes的Flash, 位于MCU代码空间。存放MCU的代码,并在其中执行代码。

MIDM: 256 bytes的低速SRAM, 位于MCU Internal数据存储器空间。作为MCU的数据存储器。其中低128字节可以直接

与间接寻址,高128字节只能间接寻址。

MEDM: 3840 bytes的低速SRAM,位于MCU External数据存储器空间。作为MCU的数据存储器,只能间接寻址。

SFR: 位于MCU的特殊功能寄存器空间。寻址空间大小是128 bytes。作为MCU的寄存器,其地址与MIDM的高128字节

重合,只能通过直接寻址访问。

**DCRM:** 16K X 24bits的高速SRAM,位于DSP代码存储器空间。DSP在其中执行代码。

**DDM:** 6K X 16bits的高速SRAM, 位于DSP的Data Memory空间中(DSP的Data Memory空间寻址大小是16K X 16bits)。

是DSP的一个数据存储器。

DPM: 2K X 16bits的高速SRAM,位于DSP的Program Memory空间中(DSP的Program Memory空间寻址大小是16K X

16bits)。是DSP的另一个数据存储器。DSP可以同时在DDM与DPM区中取操作数,以实现Multifunction指令。

DRA: 由114 X 16bits个寄存器组成,位于DSP的Data Memory空间中。作为DSP的memory-mapped寄存器。

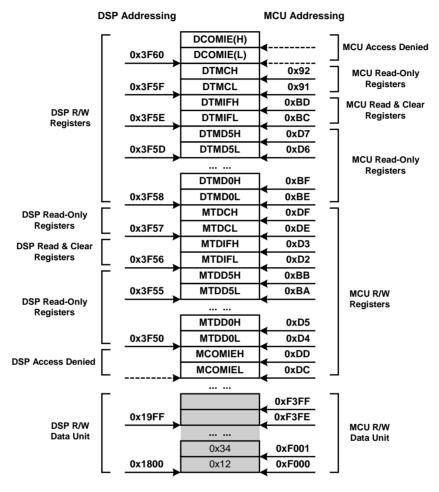

CRA: 由512 X 16bits的高速SRAM和18 X 16bits的寄存器组成,位于DSP的Data Memory空间中。用于DSP与MCU之

间的通信。对于DSP,CRA区中的SRAM位于其Data Memory空间的0x1800 - 0x19FF地址区域中,CRA区中的寄存器位于Data Memory空间的0x3F50 - 0x3F60地址区域中,对于MCU,CRA区中的SRAM位于其外部存储空

间的0xF000 - 0xF3FF地址区域中,CRA区中的寄存器位于SFR(Bank0 & Bank1)区中。

**DCSM:** 64 Kbytes的Flash,作为非易失性存储器,用于存放DSP代码以及变量初始化值。

BOOTROM: 1Kbytes的Flash,储存了ISP代码。

图7-1

### 7.2 复位

一共有五种复位源:上电复位POR、按键复位PIN、看门狗复位WDT、低电压复位LVR和软件复位。前四种复位都将触发将数据从DCSM区加载至DCRM区、DDM区和DPM区的Autoload过程。

Table 7.1 复位控制寄存器

| B1H        | 第7位  | 第6位   | 第5位  | 第4位  | 第3位  | 第2位   | 第1位   | 第0位   |

|------------|------|-------|------|------|------|-------|-------|-------|

| RSTSTAT    | WDOF | DWDOF | PORF | LVRF | CLRF | WDT.2 | WDT.1 | WDT.0 |

| 读/写        | 读/写  | 读/写   | 读/写  | 读/写  | 读/写  | 读/写   | 读/写   | 读/写   |

| 复位值 (POR)  | 0    | 0     | 1    | 0    | 0    | 0     | 0     | 0     |

| 复位值 (WDT)  | 1    | u     | u    | u    | u    | 0     | 0     | 0     |

| 复位值 (DWDT) | u    | 1     | u    | u    | u    | 0     | 0     | 0     |

| 复位值 (LVR)  | u    | u     | u    | 1    | u    | 0     | 0     | 0     |

| 复位值 (PIN)  | u    | u     | u    | u    | 1    | 0     | 0     | 0     |

| 位编号 | 位符号      | 说明                                                                                                                                                                                                                      |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | WDOF     | 看门狗溢出或程式超范围溢出标志位<br>看门狗溢出时由硬件置1,可由软件或上电复位清0<br>0:未发生WDT溢出或程序超范围溢出<br>1:发生WDT溢出或程序超范围溢出                                                                                                                                  |

| 6   | DWDOF    | DSP看门狗定时器溢出标志<br>看门狗溢出时由硬件置1,可由软件或上电复位清0<br>0:未发生DSP的WDT溢出<br>1:发生DSP的WDT溢出                                                                                                                                             |

| 5   | PORF     | 上电复位标志位         上电复位后硬件置1,只能由软件清0         0: 没有发生上电复位         1: 发生过上电复位                                                                                                                                                |

| 4   | LVRF     | 低压复位标志位<br>低压复位后置1,可由软件或上电复位清0<br>0:没有发生低压复位<br>1:发生过低压复位                                                                                                                                                               |

| 3   | CLRF     | Reset引脚复位标志位<br>引脚复位后置1,由软件或上电复位清0<br>0:没有发生引脚复位<br>1:发生过引脚复位                                                                                                                                                           |

| 2-0 | WDT[2:0] | WDT溢出周期控制位 000: 溢出周期最小值 = 4096ms 001: 溢出周期最小值 = 1024ms 010: 溢出周期最小值 = 256ms 011: 溢出周期最小值 = 128ms 100: 溢出周期最小值 = 64ms 101: 溢出周期最小值 = 16ms 110: 溢出周期最小值 = 4ms 111: 溢出周期最小值 = 1ms 注意: 应用中如果看门狗打开,程序清看门狗的最大间隔时间不能大于以上所列最小值。 |

#### 7.2.1 上电复位POR (Power On Reset)

系统工作电压是2.7 - 5.5V。上电复位发生之后,经过的电源预热时间和振荡器预热时间,判断是否执行ISP(详见7.8节)。RSTSTAT寄存器中的PORF位将置1。在振荡器预热的同时进行Autoload过程。

#### 7.2.2 按键复位PIN (Pin Reset)

Reset引脚不与其它功能复用。低电压有效。Pin Reset发生后,经过电源预热时间和振荡器预热时间,判断是否执行ISP(详见7.8节)。RSTSTAT寄存器中的CLRF位将置1。在振荡器预热的同时进行Autoload过程。

#### 7.2.3 看门狗复位WDT (WatchDogTimer Reset)

DSP和MCU都有各自的看门狗,可以分别设置看门狗溢出时间。任何一个看门狗溢出后都将导致系统复位。WDT Reset发生后,经过1000系統時鐘的延時和振荡器预热时间后,系统开始运行。RSTSTAT寄存器中WDOF位(MCU中的看门狗溢出)或DWDOF位(DSP中的看门狗溢出)将置1。在振荡器预热的同时进行Autoload过程。注意,寄存器DSPRST = 0xA5时,DSP的看门狗不工作,详见MCU使DSP复位章节。

#### 7.2.4 低电压复位LVR(Low Voltage Reset)

通过代码选项选择,LVR设定电压 $V_{LVR}$ 可为2.8V或4.3V(SH99F100A的工作电压范围是2.7 - 5.5V)。LVR去抖动时间为30-60 $\mu$ s。当供电电压低于设定电压 $V_{LVR}$ 时,将产生内部复位。LVR发生之后,经过电源预热时间和振荡器预热时间,系统开始运行。RSTSTAT寄存器中的LVRF位将置1。在振荡器预热的同时进行Autoload过程。

#### 7.2.5 软复位SWR (Software Reset)

#### 系统软件复位

Table 7.2 软件复位控制寄存器SWRCON(SoftWare Reset Control)

| A6H                      | 第7位      | 第6位      | 第5位      | 第4位      | 第3位      | 第2位      | 第1位      | 第0位      |

|--------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| SWRCON                   | SWRCON.7 | SWRCON.6 | SWRCON.5 | SWRCON.4 | SWRCON.3 | SWRCON.2 | SWRCON.1 | SWRCON.0 |

| 读/写                      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      |

| 复位值<br>(POR/WDT/LVR/PIN) | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| 位编号 | 位符号         | 说明                                                           |

|-----|-------------|--------------------------------------------------------------|

| 7-0 | SWRCON[7:0] | <b>软件复位控制</b> 5AH: 设置后将发生软件复位 其它: 软件复位不会发生 软件复位只能在BootRom中使用 |

Table 7.3 软件复位标志和指令访问控制寄存器

| A7H                      | 第7位  | 第6位 | 第5位 | 第4位 | 第3位 | 第2位 | 第1位 | 第0位 |

|--------------------------|------|-----|-----|-----|-----|-----|-----|-----|

| FLASHCON                 | SWRF | -   | -   | -   | -   | -   | -   | FAC |

| 读/写                      | 读/写  | -   | -   | -   | -   | -   | -   | 读/写 |

| 复位值<br>(POR/WDT/LVR/PIN) | 0    | -   | -   | -   | -   | -   | -   | 0   |

| 位编号 | 位符号  | 说明                                                                      |

|-----|------|-------------------------------------------------------------------------|

| 7   | SWRF | <b>软件复位标志</b><br>只能在发生软件复位后由硬件自动置 <b>1</b> ;<br>由软件清除或者其它复位清 <b>0</b> 。 |

| 0   | FAC  | 执行区域选择位(详见SSP章节)                                                        |

BootRom是一块大小为1Kbytes的Flash,其中固化了ISP程序。其程序地址空间为0x0000 - 0x03FF段地址。<u>软件复位只能</u>通过MCU在BootRom中执行程序,写寄存器SWRCON为5AH时发生。

用户只需要令SWRCON = 5AH,即可发生软件复位。软件复位发生后,MCU和DSP的所有寄存器都将复位,MCU和DSP都停止运行,并开始执行Autoload过程。Autoload过程结束后,MCU从MCM的0x0000地址开始运行,DSP的PC指针指向DCRM空间的0x0000地址并仍处于停止状态,且FLASHCON寄存器中的SWRF位将置1。

注意:软件复位不清除RSTSTAT寄存器。

#### MCU使DSP复位

### Table 7.4 复位DSP控制寄存器DSPRST

| взн                      | 第7位      | 第6位      | 第5位      | 第4位      | 第3位      | 第2位      | 第1位      | 第0位      |

|--------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| DSPRST                   | DSPRST.7 | DSPRST.6 | DSPRST.5 | DSPRST.4 | DSPRST.3 | DSPRST.2 | DSPRST.1 | DSPRST.0 |

| 读/写                      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      | 读/写      |

| 复位值<br>(POR/WDT/LVR/PIN) | 1        | 0        | 1        | 0        | 0        | 1        | 0        | 1        |

| 位编号 | 位符号          | 说明                                                                  |

|-----|--------------|---------------------------------------------------------------------|

| 7-0 | DSPRST [7:0] | MCU复位DSP控制寄存器<br>A5H: DSP所有寄存器复位,DSP停止运行<br>5AH: DSP开始运行<br>其它值: 无效 |

MCU的SFR区中有一个寄存器DSPRST。向此寄存器写0xA5,将使得DSP的所有寄存器复位,DSP系统时钟被停止;向DSPRST写0x5A将使得DSP脱离上述复位状态,并开始运行。向DSPRST写其它值无意义。上电后该寄存器的值为0xA5,即DSP处于复位状态。此外,DSPRST = 0xA5时,DSP的看门狗计数器将复位,并停止运行;DSPRST = 0x5A时,DSP的看门狗是否工作取决于代码选项OP\_DWDT位(详见10章 代码选项)。

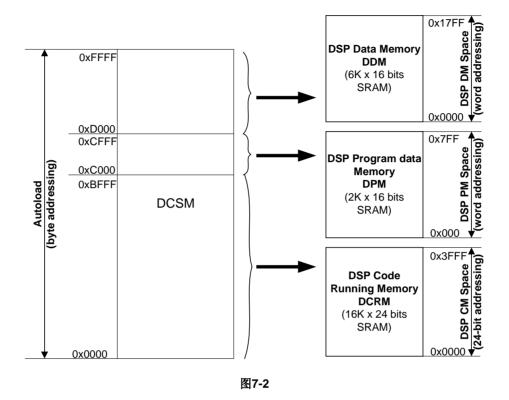

#### 7.2.6 上电Autoload过程

SH99F100A中有一块硬件逻辑,可以将DCSM区中指定区域中的内容自动加载至DCRM、DDM以及DPM区域中。对应关系如图7-2所示。

#### 7.2.7 复位过程综述

SH99F100A发生上电复位、按键复位、看门狗复位和低电压复位之后:

- DSP和MCU均复位其寄存器(RSTSTAT寄存器的状态位会根据不同的复位给出指示),并停止运行(MCU和DSP不执行程序)。

- 若是上电复位、按键复位或低电压复位则将经历一段上电预热时间(详见7.5节),長短约11ms;若是看门狗复位,则将经历一段8000CKs(1CKs指1個16MHz RC振荡器时钟周期)的时间。

- 上电预热或8000CKs时间之后,再经历振荡器预热时间(详见7.5节),在这段时间内同时执行Autoload过程: MCU与DSP 停止运行,DCSM中的数据按照图7-2中的对应关系加载至DCRM、DDM和DPM区中。

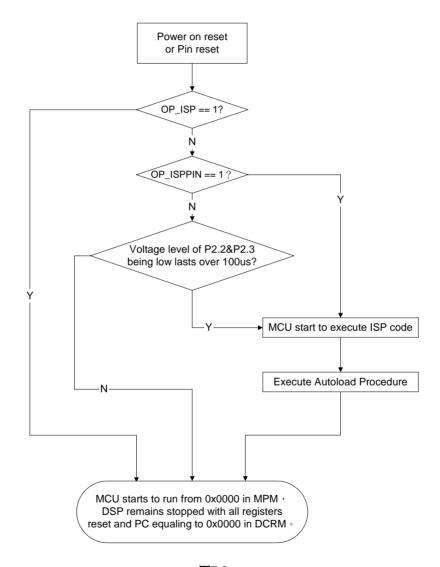

- 所有预热时间结束后,如果是上电复位或按键复位,则MCU通过代码选项中OP\_ISP的值判断是否运行引导扇区中的ISP程序,若OP\_ISP = 0则要执行ISP程序,接下来通过代码选项中OP\_ISPPIN的值判断是否需要判断P2.2和P2.3的电平以确定是否执行ISP程序:若OP\_ISPPIN = 1,则不判断pin的电平而直接执行ISP程序,即只要发生了上电复位/按键复位即执行ISP程序;反之,需要判断P2.2和P2.3的电平是否保持了100us以上的低电平时间,若是则执行ISP程序,否则不执行ISP程序,即发生上电复位/按键复位之后需要用外部的P2.2和P2.3来确定是否执行ISP程序。ISP程序存储在一块BootRom中,由MCU执行。

- ISP程序执行完毕后,将触发Autoload过程(Autoload过程实际上是由BootRom中的程序触发,程序中通过设置寄存器 SWRCON = 0x5A实现(详见7.7节)),Autoload过程结束后,系统即开始运行:MCU从MCM空间0x0000地址开始执行程序,DSP的PC指针指向DCRM空间的0x0000地址并仍处于停止状态。若没有发生过ISP,则预热结束后系统即开始运行。

#### 7.3 系统时钟

#### 7.3.1 特性

- 支持3种高频振荡器类型:晶体谐振器、陶瓷谐振器和内部16M RC振荡器

- 内建倍频系数可选锁相环 (PLL) 振荡器

- 内部16M高频RC振荡器(常温精度±0.5%,全电压全温度范围精度±1%)

- 内建系统时钟分频器

#### 7.3.2 时钟定义

**CRYCLK:** 从XTAL输入的4M~16MHz晶体/陶瓷谐振器的时钟或外部。f<sub>CRY</sub>定义为CRYCLK的频率。t<sub>CRY</sub>定义为CRYCLK的周期。

HRCCLK: 内部16MHz RC振荡器时钟。f<sub>HRC</sub>定义为HRCCLK的频率。t<sub>HRC</sub>定义为HRCCLK的周期。

PLLCLK: 锁相环(PLL)振荡器时钟。fpLL定义为PLLCLK的频率,tpLL定义为PLLCLK的周期。

**SCMCLK:** 内部2MHz时钟监控RC振荡器时钟也用于电源预热计数。f<sub>SCM</sub>定义为SCMCLK的频率。t<sub>SCM</sub>定义为SCMCLK的周期。

WDTCLK: 内部的2kHz看门狗RC振荡器时钟。fwDT定义为WDTCLK的频率。twDT定义为WDTCLK的周期。

**OSCSCLK:** MCU时钟频率分频器的输入时钟。这个时钟可能为HRCCLK或CRYCLK。foscs定义为OSCSCLK的频率。toscs定义为OSCSCLK的周期。

**MSYSCLK:** MCU核的子系统时钟,MCU时钟频率分频器的输出时钟。这个时钟为MCU的CPU指令周期的时钟。f<sub>MSYS</sub>定义为MSYSCLK的频率。t<sub>MSYS</sub>定义为MSYSCLK的周期。

**DSYSCLK:** DSP核的子系统时钟。这个时钟为DSP的CPU指令周期的时钟,可以是**OSCSCLK或者PLLCLK**。F<sub>DSYS</sub>定义为DSYSCLK的频率。T<sub>DSYS</sub>定义为DSYSCLK的周期。

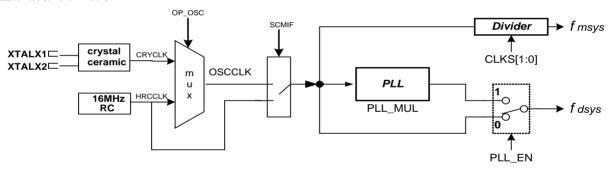

整体结构如图7-3所示。

图7-3

系统正常工作时,使用晶振(Crystal)产生时钟信号fcRYCLK或内部高频RC时钟fHRC通过代码选项中OP\_OSC选择当前使用的高频时钟OSCCLK,在OSCCLK经过MCU的时钟分频器后作为MCU部分的CPU及其外设的子系统时钟,同时OSCCLK也作为系统内建PLL的输入,通过PLL\_EN选择OSCCLK或PLLCLK作为DSP部分的CPU及其外设的子系统时钟。当SCM发生时,OSCCLK会自动切换为内部高频RC的16M HRCCLK,并仍可作为MCU时钟分频器输入时钟及PLL输入时钟,MCU和DSP两个子系统可继续运行。

#### 7.3.3 DSP系统时钟

DSP系统时钟记作f<sub>DSYS</sub>,DSP的最大系统时钟为100MHz。使能内部PLL时(PLL\_EN = 1),用户可以通过PLL\_MUL设置位选择不同的倍频系数,在f<sub>c</sub>基础上产生需要的系统时钟,DSP系统时钟由下式决定:

$f_{DSYS} = f_c X PLL_MUL$

第一次使能PLL或改变PLL的倍频设置值PLL\_MUL后,用户程序需要等待PLL输出稳定。用户程序可以查询PLL输出稳定标志PLL\_LOCK来确认PLL的稳定状态。DSP的时钟只由DSP系统时钟控制寄存器DCLKCON控制,与MCU无关。

Table 7.5 DSP系统时钟控制寄存器DCLKCON (DSP Clock Control Register)

| 15       | 14     |          | 13 - 11  |         | 10 - 8 |  |       |

|----------|--------|----------|----------|---------|--------|--|-------|

| R/W-0    | R-0    |          | R-0      |         | R-0    |  | R/W-0 |

| DSCMIE   | DSCMST |          | Reserved |         | DWDT   |  |       |

|          | 7 - 5  |          | 4        | 3       | 2 - 0  |  |       |

| R-0      |        | R-0      | R/W-0    | R/W-0   |        |  |       |

| Reserved |        | PLL_LOCK | PLL_EN   | PLL_MUL |        |  |       |

| £24,624 □1 | 12x AA+ 171 | \¥ HI                                                                                                                           |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 位编号        | 位符号         | 说明                                                                                                                              |

| 15         | DSCMIE      | DSP中SCM中断使能位<br>0: 禁止发生SCM时触发SCM中断<br>1: 允许发生SCM时触发SCM中断                                                                        |

| 14         | DSCMST      | DSP中SCM中断标志位 0: 没有发生时钟故障 1: 已发生时钟故障 该标志位只能由硬件置位和清除                                                                              |

| 13 - 11    | Reserved    | 保留位                                                                                                                             |

| 10 - 8     | DWDT        | DWDT溢出频率控制                                                                                                                      |

| 7 - 5      | Reserved    | 保留位                                                                                                                             |

| 4          | PLL_LOCK    | DSP锁相环输出稳定指示位<br>0: PLL输出未稳定,此时f <sub>DSYS</sub> = f <sub>c</sub><br>1: PLL输出已稳定,此时f <sub>DSYS</sub> = f <sub>c</sub> X PLL_MUL |

| 3          | PLL_EN      | DSP锁相环(PLL)使能位<br>0:禁止PLL,DSP直接使用时钟信号f <sub>c</sub> 作为f <sub>DSYS</sub><br>1:使能PLL,f <sub>DSYS</sub> = f <sub>c</sub> X PLL_MUL |

| 2 - 0      | PLL_MUL     | PLL倍频系数选择位 000: X 2 001: X 3 010: X 4 011: X 5 100: X 6.25 (for 16MHz) 101: X 8.33 (for 12MHz) 110: X 10 111: X 12.5 (for 8MHz) |

#### 7.3.4 MCU系统时钟

Table 7.6 系统时钟控制寄存器CLKCON

| B2H                      | 第7位 | 第6位   | 第5位   | 第4位   | 第3位 | 第2位 | 第1位 | 第0位 |

|--------------------------|-----|-------|-------|-------|-----|-----|-----|-----|

| CLKCON                   | -   | CLKS1 | CLKS0 | SCMIF | -   | -   | -   | -   |

| 读/写                      | -   | 读/写   | 读/写   | 只读    | -   | -   | -   | -   |

| 复位值<br>(POR/WDT/LVR/PIN) | -   | 0     | 0     | 0     | -   | -   | -   | -   |

| 位编号 | 位符号        | 说明                                                                                                                                                                              |  |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6-5 | CLKS[1: 0] | 系统时钟频率分频器 00: f <sub>MSYS</sub> = f <sub>C</sub> 01: f <sub>MSYS</sub> = f <sub>C</sub> /2 10: f <sub>MSYS</sub> = f <sub>C</sub> /4 11: f <sub>MSYS</sub> = f <sub>C</sub> /12 |  |  |

| 4   | SCMIF      | <b>系统时钟故障MCU标志</b> 0: 系统时钟无故障 1: 发生系统时钟故障,由硬件清0                                                                                                                                 |  |  |

MCU的系统时钟记作f<sub>MSYS</sub>。MCU的最大系统时钟为16MHz。在寄存器CLKCON中可以通过设置CLKS[1:0]将f<sub>MSYS</sub>设置为f<sub>c</sub>的1/1,1/2,1/4,1/12倍。

#### 7.3.5 系统时钟监控模块SCM(System Clock Monitor)

为了增强系统的可靠性,SH99F100A中含有一个系统时钟监控(SCM)模块。如果系统时钟fc出现故障(例如:外部振荡器停振等),内建SCM模块会将fc自动切换到内部RC时钟(16MHz)。在代码选项中可以选择在振荡器预热期间是否使能SCM模块。

#### 检测到时钟故障后,fc自动切换至内部16MHz的RC时钟。

MCU模块中,使用16M RC产生的f<sub>c</sub>在原来的分频系数上产生f<sub>MSYS</sub>运行,同时系统时钟监控中断标志位(SCMIF)被置1。SCMIF位反映了振荡器的工作状态,由硬件控制,SCMIF = 1说明处于时钟故障中、SCMIF = 0说明无时钟故障。当EA和ESCM位均被置1时,SCM模块将会产生中断并跳向处于0073H位置的中断向量。如果外部振荡器恢复工作,SCM将会切换f<sub>c</sub>到外部振荡器,然后SCMIF位自动清0。

DSP模块中,若寄存器DCLKCON中的位DSCMIE = 1时,则发生时钟故障时将触发SCM中断,进入0x002C处的中断向量,相应的中断标志将被硬件自动清0(注意该标志没有开放出来,用户无法软件操作)。DSCMST位指示时钟是否有故障,1表示有故障、0表示无故障,该位由硬件控制。发生时钟故障后,DSP的系统时钟f<sub>DSYS</sub>就是16M RC产生的f<sub>c</sub>。如果外部振荡器恢复工作,SCM将会切换f<sub>c</sub>到外部振荡器,然后DSCMST位自动清0,此时如果DSCMIE使能,则会产生一次中断;如果要使用PLL,必须重新手动设置。

#### 7.4 看门狗

Table 7.7 SH99F100A内部含有两个看门狗定时器,分别给DSP和MCU使用。这两个定时器结构上一样。

| 15       | 14     |          | 13 - 11  |         | 10 - 8 |

|----------|--------|----------|----------|---------|--------|

| R/W-0    | R-0    |          | R-0      |         | R/W-0  |

| DSCMIE   | DSCMST |          | Reserved |         | DWDT   |

|          | 7 - 5  |          | 4        | 3       | 2 - 0  |

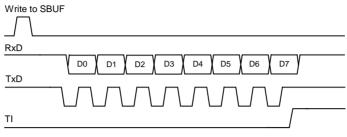

| R-0      |        | R-0      | R/W-0    | R/W-0   |        |