# Half-Bridge N-Channel MOSFET Driver With Break-Before-Make

#### **FEATURES**

- 5-V Gate Drive

- Undervoltage Lockout

- Sub 1-Ω Gate Drivers

- Internal Bootstrap Diode

- Drive MOSFETs In 4.5- to 30-V Systems

- Switching Frequency: 250 kHz to 1 MHz

- Synchronous Enable/Disable Option

#### **APPLICATIONS**

- Multi-Phase DC/DC

- High Current Synchronous Buck Converters

- High Frequency Synchronous Buck Converters

- Asynchronous-to-Synchronous Adaptations

- Mobile Computer DC/DC Converters

- Desktop Computer DC/DC Converters

#### **DESCRIPTION**

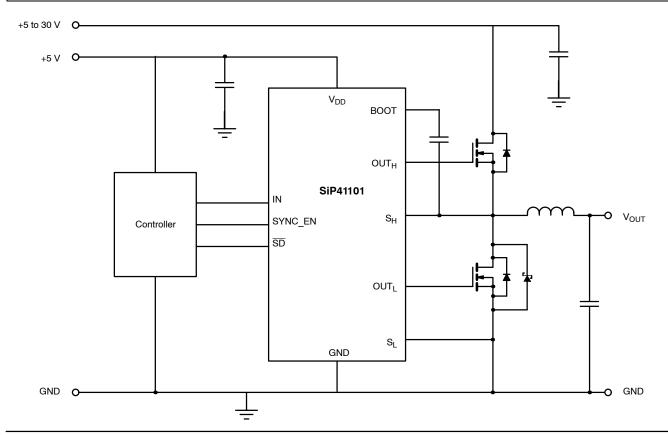

The SiP41101 is a high speed half-bridge driver, with make-before-break, for use in high frequency, high current multiphase dc-to-dc power supplies for supply voltages as high as 30 V. It is designed to operate at frequencies up to 1 MHz. The high-side driver is bootstrapped to allow driving an n-channel high-side MOSFET. The bootstrap diode is internal. The output drivers provide currents up to 4 A, allowing use of low  $r_{DS(on)}$  power MOSFETs.

The SiP41101 comes with internal break-before-make circuitry to prevent shoot-through current in the external

MOSFETs. The  $\overline{\text{SD}}$  control pin is provided to enable the drivers. A Synchronous Enable control pin is provided to disable the the low-side or synchronous MOSFET to maximize efficiency under low output current conditions.

The SiP41101 is available in a 16-pin TSSOP package for operation over the industrial temperature range of -40 to 85°C.

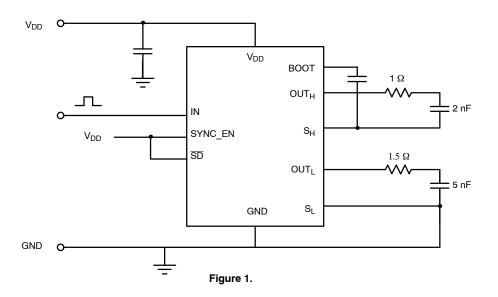

# **TYPICAL APPLICATION DIAGRAM**

Document Number: 72377 S-31578—Rev. A, 11-Aug-03

# **Vishay Siliconix**

#### **New Product**

## ABSOLUTE MAXIMUM RATINGS (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>DD</sub> 7 V                     | Power Dissipation <sup>a</sup>                                                    |

|-----------------------------------------|-----------------------------------------------------------------------------------|

| $V_{\mbox{\scriptsize IN}}$             | TSSOP-16                                                                          |

| V <sub>SH</sub>                         | Thermal Impedance $(\Theta_{JA})_a$                                               |

| V <sub>BOOT</sub> V <sub>SH</sub> + 7 V | TSSOP-16                                                                          |

| Storage Temperature40 to 150°C          | Notes                                                                             |

| Operating Junction Temperature          | <ul> <li>Device mounted with all leads soldered or welded to PC board.</li> </ul> |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# RECOMMENDED OPERATING RANGE (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>DD</sub>   | $C_{BOOT}$                            |

|-------------------|---------------------------------------|

| V <sub>BOOT</sub> | Operating Temperature Range40 to 85°C |

| <b>SPECIFICATIONS</b> <sup>a</sup>   | 1                        |                                                                                               |                  |        |                  |      |

|--------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|------------------|--------|------------------|------|

|                                      |                          | Test Conditions Unless Specified                                                              |                  | Limits |                  |      |

| Parameter                            | Symbol                   | V <sub>DD</sub> = 4.5 to 5.5 V, V <sub>BOOT</sub> = 4.5 to 30 V, T <sub>A</sub> = -40 to 85°C | Min <sup>a</sup> | Typb   | Max <sup>a</sup> | Unit |

| Power Supplies                       |                          |                                                                                               | I                | I      |                  |      |

| Supply Voltage                       | V <sub>DD</sub>          |                                                                                               | 4.5              |        | 5.5              | V    |

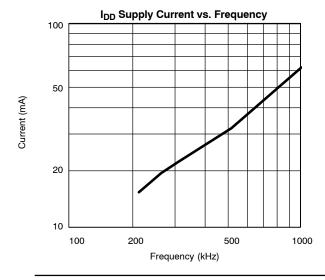

| Supply Current                       | I <sub>DD</sub>          | f <sub>IN</sub> = 300 kHz, $\overline{\text{SD}}$ = H, Sync_en = H<br>see Figure 1            |                  | 25     | 40               | mA   |

| Quiescent Current                    | I <sub>DDQ</sub>         | IN = L, SD = H, Sync_en = H, No Load                                                          |                  | 1.4    | 2.5              | μΑ   |

| Reference Voltage                    |                          |                                                                                               |                  |        |                  |      |

| Break-Before-Make                    | $V_{BBM}$                | V <sub>DD</sub> = 5.5 V                                                                       |                  | 2.5    |                  | V    |

| Logic Inputs — IN, Syn               | c En, SD                 |                                                                                               | I                | · L    |                  |      |

| Input High                           | V <sub>IH</sub>          |                                                                                               | 2.5              |        |                  |      |

| Input Low                            | V <sub>IL</sub>          |                                                                                               |                  |        | 1.0              | · V  |

| Undervoltage Lockout                 |                          |                                                                                               |                  |        |                  |      |

| V <sub>DD</sub> Undervoltage         | V <sub>UVL</sub>         | V <sub>DD</sub> Rising                                                                        |                  | 3.6    | 4.4              | V    |

| Undervoltage Hysteresis              | V <sub>HYST</sub>        |                                                                                               |                  | 400    |                  | mV   |

| Bootstrap Diode                      |                          |                                                                                               |                  |        |                  |      |

| Forward Voltage                      | V <sub>F</sub>           | I <sub>F</sub> = 10 mA                                                                        |                  | 0.65   |                  | V    |

| MOSFET Drivers                       | •                        |                                                                                               | •                | •      |                  |      |

|                                      | I <sub>PKH(source)</sub> | V <sub>BOOT</sub> - V <sub>SH</sub> = 4.5 V, V <sub>OUTH</sub> -V <sub>SA</sub> =2.25V        |                  | 3.0    |                  |      |

| High-Side Drive Current <sup>c</sup> | I <sub>PKH(sink)</sub>   |                                                                                               |                  | 3.0    |                  | A    |

| Laur Cida Duiva Crumant              | I <sub>PKL(source)</sub> | V 45VV 205V                                                                                   |                  | 4.1    |                  | _ A  |

| Low-Side Drive Current <sup>c</sup>  | I <sub>PKL(sink)</sub>   | $V_{DD} = 4.5 \text{ V}, V_{OUTL} = 2.25 \text{ V}$                                           |                  | 4.1    |                  |      |

| High-Side Driver Impedance           | R <sub>DH(source)</sub>  | V <sub>DD</sub> = 4.5 V, S <sub>H</sub> = GND                                                 | _                | 0.75   | 1.3              |      |

| night-side Driver impedance          | R <sub>DH(sink)</sub>    | * DD = 4.0 *, OH = GND                                                                        |                  | 0.75   | 1.3              | Ω    |

| Low-Side Driver Impedance            | R <sub>DL(source)</sub>  | V <sub>DD</sub> = 4.5 V                                                                       |                  | 0.55   | 1.1              | 35   |

| Low-Gide Driver impedance            | R <sub>DL(sink)</sub>    | ν <sub>υυ</sub> – 4.5 ν                                                                       |                  | 0.55   | 1.1              |      |

## **New Product**

# Vishay Siliconix

| SPECIFICATIONS <sup>a</sup>              |                       |                                                                                               |   |        |                  |      |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------|---|--------|------------------|------|

|                                          |                       | Test Conditions Unless Specified                                                              |   | Limits |                  |      |

| Parameter Symbol                         |                       | V <sub>DD</sub> = 4.5 to 5.5 V, V <sub>BOOT</sub> = 4.5 to 30 V, T <sub>A</sub> = -40 to 85°C |   | Typb   | Max <sup>a</sup> | Unit |

| MOSFET Drivers                           |                       |                                                                                               | • |        |                  |      |

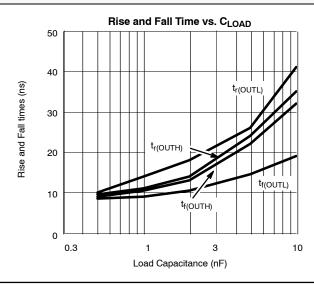

| High-Side Rise Timec                     | t <sub>rH</sub>       | 10% - 90%                                                                                     |   | 15     |                  |      |

| High-Side Fall Time <sup>c</sup>         | t <sub>fH</sub>       | 90% - 10%                                                                                     |   | 15     |                  |      |

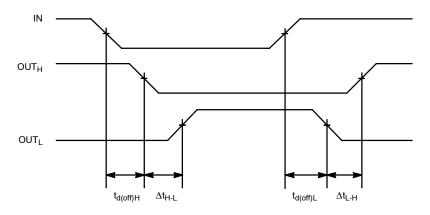

|                                          | t <sub>d(off)</sub> H | - 50% - 50%                                                                                   |   | 25     |                  |      |

| High-Side Propagation Delay <sup>c</sup> | ΔtH-L                 |                                                                                               |   | 5      |                  |      |

| Low-Side Rise Time <sup>c</sup>          | t <sub>rL</sub>       | 10% - 90%                                                                                     |   | 25     |                  | ns   |

| Low-Side Fall Time <sup>c</sup>          | t <sub>fL</sub>       | 90% - 10%                                                                                     |   | 15     |                  | 1    |

| Low-Side Propagation Delay <sup>c</sup>  | t <sub>d(off)L</sub>  | 50% - 50%                                                                                     |   | 10     |                  |      |

|                                          | ΔtL-H                 |                                                                                               |   | 25     |                  | 1    |

- Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum (-40° to 85°C).

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- Guaranteed by design.

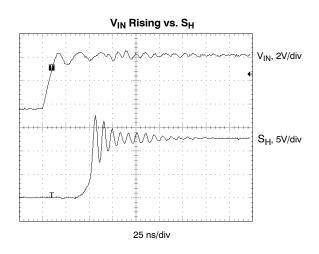

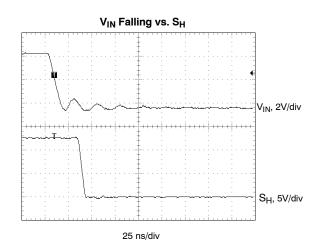

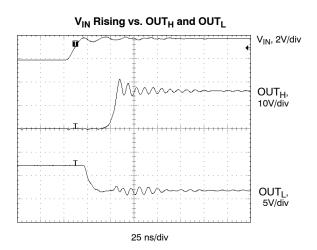

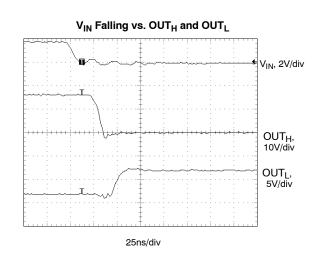

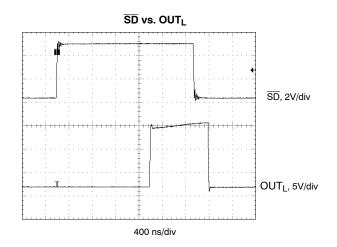

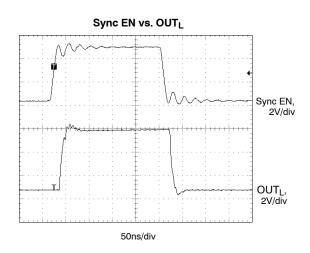

#### **TIMING WAVEFORMS**

#### **TEST SETUP**

# **New Product**

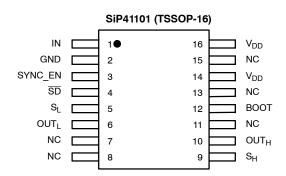

# PIN CONFIGURATION, ORDERING INFORMATION, AND TRUTH TABLE

| ORDERING INFORMATION   |                   |         |

|------------------------|-------------------|---------|

| Part Number            | Temperature Range | Marking |

| SiP41101DQ-T1          | -40 to 85°C       | 41101   |

| 3.1 111012 <u>4</u> 11 | 10 10 00 0        |         |

| Eval Kit Temperature Ra |             |

|-------------------------|-------------|

| SiP41101DB              | -40 to 85°C |

Top View

| TRUTH TABLE |         |    |      |      |

|-------------|---------|----|------|------|

| SD          | SYNC_EN | IN | OUTH | OUTL |

| Н           | Н       | L  | L    | Н    |

| Н           | Н       | Н  | Н    | L    |

| Н           | L       | L  | L    | L    |

| Н           | L       | Н  | Н    | L    |

| L           | Х       | X  | L    | L    |

| PIN DESCRIPTION  |                  |                                           |  |

|------------------|------------------|-------------------------------------------|--|

| Pin              | Name             | Function                                  |  |

| 1                | IN               | Input signal to the MOSFET drivers        |  |

| 2                | GND              | Ground                                    |  |

| 3                | SYNC_EN          | Synchronous MOSFET enable                 |  |

| 4                | SD               | Shutdown                                  |  |

| 5                | S <sub>L</sub>   | Connection to source of low-side MOSFET   |  |

| 6                | OUT <sub>L</sub> | Synchronous or low-side MOSFET gate drive |  |

| 7, 8, 11, 13, 15 | NC               | No Connect                                |  |

| 9                | S <sub>H</sub>   | Connection to source of high-side MOSFET  |  |

| 10               | OUT <sub>H</sub> | Control or high-side MOSFET gate drive    |  |

| 12               | BOOT             | Connection for the bootstrap capacitor    |  |

| 14, 16           | $V_{DD}$         | +5-V supply                               |  |

#### **New Product**

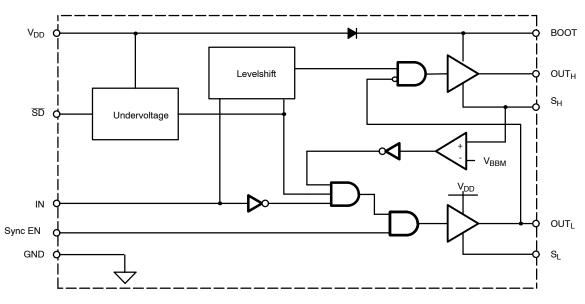

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2.

#### **DETAILED OPERATION**

#### **Break-Before-Make Function**

The SiP41101 has an internal break-before-make function to ensure that both high-side and low-side MOSFETs are not turned on at the same time. The high-side drive (OUT $_{\rm H}$ ) will not turn on until the low-side gate drive voltage (measured at the OUT $_{\rm L}$  pin) is less than V $_{\rm BBM}$ , thus ensuring that the low-side MOSFET is turned off. The low-side drive (OUT $_{\rm L}$ ) will not turn on until the voltage at the MOSFET half-bridge output (measured at the S $_{\rm L}$  pin) is less than V $_{\rm BBM}$ , thus ensuring that the high-side MOSFET is turned

#### **Under Voltage Lockout Function**

The SiP41101 has an internal under-voltage lockout feature to prevent driving the MOSFET gates when the supply voltage (at  $V_{DD}$ ) is less than the under-voltage lockout specification ( $V_{UVL}$ ). This prevents the output MOSFETs from being turned on without sufficient gate voltage to ensure they are fully on. There is hysteresis included in this feature to prevent lockout from cycling on and off.

### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

Document Number: 72377 S-31578—Rev. A, 11-Aug-03

# Vishay Siliconix

## **New Product**

## **TYPICAL WAVEFORMS**