### FEATURES

- ▶ ISO 11898-2:2024, SAE J2284-1~ SAE J2284-5 and SAE J1939-14 compliant;

- > Implements CAN Signal Improvement Capability as defined in CiA 601-4:2019;

- Thermally protected;

- →  $\pm 40$ V BUS protection;

- > Driver (TXD) dominant time-out function;

- > Low power Standby mode with remote and local wake-up capability;

- SIT1462Q/3 I/O pins supports 1.8V, 3.3V and 5V MCU;

- Undervoltage protection on pins VCC and VIO;

- High-speed CAN, support 5Mbps CAN with Flexible Data-Rate and 8Mbps CAN with Flexible Data-Rate in point-to point networks;

- High ElectroMagnetic Immunity;

- Unpowered state disengages from the bus;

- ➢ Available in SOP8 and DFN3\*3-8 packages.

### DESCRIPTION

SIT1462Q is an interface chip applied between the CAN protocol controller and the physical two-wire CAN bus. It features a much tighter bit timing symmetry performance to enable CAN FD communication up to 8Mbit/s, and has the capability of differential signal transmission between bus and CAN protocol controller.

| Parameter                            | Symbol                       | Min | Max | Unit |

|--------------------------------------|------------------------------|-----|-----|------|

| VCC supply voltage                   | VCC                          | 4.5 | 5.5 | V    |

| VIO supply voltage                   | VIO                          | 1.7 | 5.5 | V    |

| CANH, CANL input / output<br>voltage | $V_{can}$                    | -40 | +40 | V    |

| Bus differential voltage             | $\mathrm{V}_{\mathrm{diff}}$ | 1.5 | 3.0 | V    |

| Ambient temperature                  | T <sub>amb</sub>             | -40 | 125 | °C   |

| Storage temperature                  | $T_{stg}$                    | -55 | 150 | °C   |

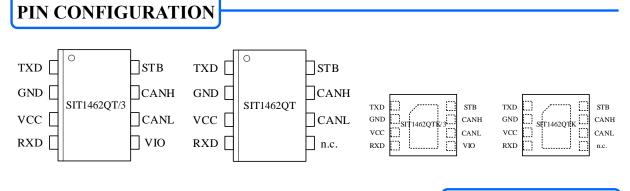

# PIN DESCRIPTION

| Pin | Symbol | Description                                               |

|-----|--------|-----------------------------------------------------------|

| 1   | TXD    | Transmit data input.                                      |

| 2   | GND    | Ground.                                                   |

| 3   | VCC    | 5V supply voltage input.                                  |

| 4   | RXD    | Receive data output.                                      |

| 5   | VIO    | Supply voltage input for I/O level adapter in SIT1462Q/3. |

| 5   | n.c.   | Not connected in SIT1462Q.                                |

| 6   | CANL   | LOW-level CAN bus line.                                   |

| 7   | CANH   | HIGH-level CAN bus line.                                  |

| 8   | STB    | Standby mode control input; active-HIGH.                  |

Note: The metal pad on the back of the DFN3\*3-8 package is recommended to be grounded.

# LIMITING VALUES

| Parameter                                | Symbol                      | Conditions                             | Value     | Unit |

|------------------------------------------|-----------------------------|----------------------------------------|-----------|------|

| Supply voltage                           | $V_{CC}$ , $V_{VIO}$        | pins VCC, VIO                          | -0.3~+7   | V    |

| MCU side ports voltage                   | $V_{TXD}, V_{RXD}, V_{STB}$ | pins TXD, RXD, STB                     | -0.3~+7   | V    |

| Voltage between pin<br>CANH and pin CANL | $V_{CANL}, V_{CANH}$        | pins CANH, CANL                        | -40~+40   | V    |

| Bus differential voltage withstand       | V <sub>CANH</sub> -CANL     |                                        | -40~+40   | V    |

|                                          |                             | IEC 61000-4-2: on pins CANH, CANL      | -10~+10   | kV   |

|                                          |                             | Human-body model (HBM), per AEC Q      | 100-002   |      |

|                                          |                             | all pins                               | -4~+4     | kV   |

| electrostatic discharge<br>voltage       | arge V <sub>ESD</sub>       | pins CANH and CANL with respect to GND | -8~+8     | kV   |

|                                          |                             | Charged Device Model (CDM)             |           |      |

|                                          |                             | on corner pins                         | -750~+750 | V    |

|                                          |                             | on corner pins                         | -500~+500 | V    |

|                                          |                             | Transient Immunity ISO 7637-2 on Bus   | Pins      |      |

|                                          |                             | pulse 1                                | -100      | V    |

| transient voltage                        | Vtrt                        | pulse 2a                               | 75        | V    |

|                                          |                             | pulse 3a                               | -150      | V    |

|                                          |                             | pulse 3b                               | 100       | V    |

| Storage temperature                      | T <sub>stg</sub>            |                                        | -55~150   | °C   |

| Virtual junction temperature             | Tj                          |                                        | -40~150   | °C   |

The maximum limit parameters mean that exceeding these values may cause irreversible damage to the device. Under these conditions, it is not conducive to the normal operation of the device. The continuous operation of the device at the maximum allowable rating may affect the reliability of the device. The reference point for all voltages is ground.

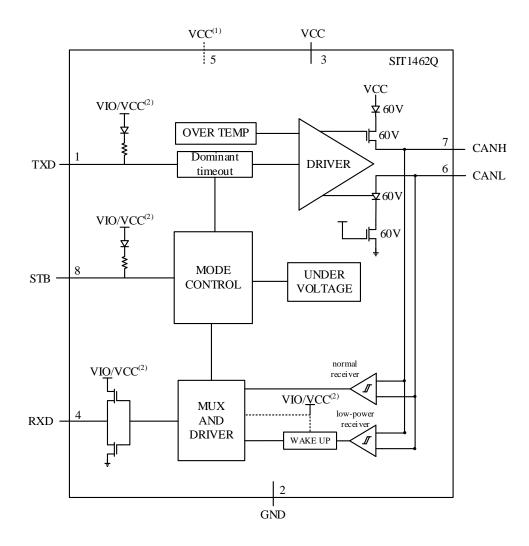

# BLOCK DIAGRAM

- (1) VIO is only available in the SIT1462Q/3, pin 5 is not connected in the SIT1462Q;

- (2) VIO in SIT1462Q/3; VCC in SIT1462Q.

1 芯力特

## STATIC CHARACTERISTICS

Unless specified otherwise; all values are tested in recommended operating conditions:  $T_j$ =-40°C~150°C,  $V_{CC}$ =4.5V~5.5V,  $V_{IO}$ =1.7V~5.5V (SIT1462Q/3),  $R_L$ =60 $\Omega$ .

| Parameter                                  | Symbol                | Condition                                                                                                                            | Min.                              | Тур. | Max.                   | Unit |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------------------------|------|

| Supply characteristics: pin V              | /CC                   |                                                                                                                                      |                                   |      |                        |      |

| Supply voltage                             | Vcc                   |                                                                                                                                      | 4.5                               | -    | 5.5                    | V    |

| Standby undervoltage detection voltage     | Vuvd(stb)             |                                                                                                                                      | 3.4                               | -    | 4.5                    | V    |

| Standby undervoltage<br>hysteresis voltage | Vuvhys(stb)           |                                                                                                                                      | 50                                | -    | -                      | mV   |

| Switch-off undervoltage detection voltage  | Vuvd(swoff)           | SIT1462Q                                                                                                                             | 0.95                              | -    | 1.65                   | V    |

|                                            |                       | Normal mode; dominant;<br>t <t<sub>to(dom)TXD; V<sub>TXD</sub>=0V</t<sub>                                                            | -                                 | 40   | 70                     | mA   |

| VCC supply current                         | Icc                   | Normal mode; dominant;<br>short circuit on bus lines;<br>V <sub>TXD</sub> =0V;<br>-3V< (V <sub>CANH</sub> =V <sub>CANL</sub> ) <+40V | -                                 | -    | 125                    | mA   |

| vee supply current                         | ice                   | Normal mode; recessive;<br>V <sub>TXD</sub> =V <sub>IO</sub> <sup>(1)</sup>                                                          | -                                 | 4.2  | 10                     | mA   |

|                                            |                       | Standby mode; SIT1462Q/3                                                                                                             | -                                 | -    | 2                      | μΑ   |

|                                            |                       | Standby mode; SIT1462Q                                                                                                               | -                                 | -    | 21                     | μΑ   |

| I/O level adapter supply; pir              | n VIO (SIT140         | 52Q/3)                                                                                                                               |                                   |      |                        |      |

| Supply voltage                             | V <sub>IO</sub>       |                                                                                                                                      | 1.7                               |      | 5.5                    | V    |

| Switch-off undervoltage detection voltage  | Vuvd(swoff)           |                                                                                                                                      | 0.95                              |      | 1.65                   | V    |

|                                            |                       | Normal mode; dominant;<br>V <sub>TXD</sub> =0V                                                                                       |                                   | 240  | 760                    | μΑ   |

| VIO supply current                         | I <sub>IO</sub>       | Normal mode; recessive;<br>V <sub>TXD</sub> =V <sub>IO</sub> <sup>(1)</sup>                                                          |                                   | 120  | 460                    | μΑ   |

|                                            |                       | Standby mode                                                                                                                         |                                   |      | 21                     | μΑ   |

| Pin TXD characteristics                    |                       |                                                                                                                                      |                                   |      |                        |      |

| HIGH-level input voltage                   | V <sub>IH</sub>       |                                                                                                                                      | $0.7 V_{IO}{}^{(1)}$              | -    | -                      | V    |

| LOW-level input voltage                    | VIL                   |                                                                                                                                      | -                                 | -    | $0.3 \ V_{IO}{}^{(1)}$ | V    |

| Hysteresis voltage                         | V <sub>hys(TXD)</sub> |                                                                                                                                      | 50                                | -    | -                      | mV   |

| Pull-up resistance                         | R <sub>pu</sub>       |                                                                                                                                      | 20                                | -    | 80                     | kΩ   |

| Input capacitance                          | Ci                    |                                                                                                                                      | -                                 | -    | 10                     | pF   |

| Pin RXD characteristics                    |                       |                                                                                                                                      |                                   |      |                        |      |

| HIGH-level output current                  | IOH(RXD)              | $V_{RXD}=V_{IO}-0.4V^{(1)}$                                                                                                          | -10                               | -    | -1                     | mA   |

| LOW-level output current                   | IOL(RXD)              | Bus dominant;<br>V <sub>RXD</sub> =0.4V                                                                                              | 1                                 | -    | 10                     | mA   |

| Pin STB characteristics                    |                       |                                                                                                                                      |                                   |      |                        |      |

| HIGH-level input voltage                   | V <sub>IH</sub>       |                                                                                                                                      | 0.7V <sub>IO</sub> <sup>(1)</sup> | -    | -                      | V    |

| Parameter                              | Symbol                   | Condition                                                                                                                                                             | Min.               | Тур. | Max.                            | Unit |

|----------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|---------------------------------|------|

| LOW-level input voltage                | V <sub>IL</sub>          |                                                                                                                                                                       | -                  | -    | $0.3 V_{IO}{}^{\left(1\right)}$ | V    |

| Hysteresis voltage                     | V <sub>hys(STB)</sub>    |                                                                                                                                                                       | 50                 | -    | -                               | mV   |

| Pull-up resistance                     | R <sub>pu</sub>          |                                                                                                                                                                       | 20                 | -    | 80                              | kΩ   |

| Input capacitance                      | Ci                       |                                                                                                                                                                       | -                  | -    | 10                              | pF   |

| Overtemperature protection             |                          |                                                                                                                                                                       |                    | •    |                                 |      |

| Shutdown junction temperature          | T <sub>j(sd)</sub>       |                                                                                                                                                                       | 165                | -    | 185                             | °C   |

| Release shutdown junction temperature  | $T_{j(sd)rel}$           |                                                                                                                                                                       | 155                | -    | 175                             | °C   |

| Bus lines; pins CANH and C             | ANL                      |                                                                                                                                                                       |                    |      |                                 |      |

| Dominant output voltage on<br>pin CANH |                          | $t < t_{to(dom)TXD};$                                                                                                                                                 | 2.89               | 3.55 | 4.26                            | V    |

| Dominant output voltage on<br>pin CANL | V <sub>O(dom)</sub>      | $V_{TXD}=0V; R_L=50\Omega \text{ to } 65\Omega$                                                                                                                       | 0.77               | 1.45 | 2.13                            | V    |

| Transmitter voltage<br>symmetry        | V <sub>TXsym</sub>       | V <sub>TXsym</sub> =V <sub>CANH</sub> +V <sub>CANL</sub> ;<br>C <sub>SPLIT</sub> =4.7nF;<br>f <sub>TXD</sub> =250kHz, 1MHz or 2.5MHz                                  | 0.9V <sub>CC</sub> | -    | 1.1Vcc                          | V    |

| Common mode voltage step               | V <sub>cm(step)</sub>    |                                                                                                                                                                       | -150               | -    | 150                             | mV   |

| Peak-to-peak common mode<br>voltage    | V <sub>cm(p-p)</sub>     |                                                                                                                                                                       | -300               | -    | 300                             | mV   |

|                                        |                          | $\begin{array}{c} Normal \ mode; \\ t < t_{to(dom)TXD}; \\ V_{TXD} = 0V; \ V_{CC} = 4.5V \ to \ 5.5V; \\ R_L = 50\Omega \ to \ 65\Omega \end{array}$                  | 1.5                | -    | 3                               | V    |

|                                        |                          | $\begin{array}{c} Normal \mbox{ mode;} \\ t < t_{to(dom)TXD}; \\ V_{TXD} = 0V; \ V_{CC} = 4.5V \mbox{ to } 5.5V; \\ R_L = 45\Omega \mbox{ to } 70\Omega \end{array}$  | 1.4                | -    | 3.3                             | V    |

| Differential output voltage            | $V_{O(diff)}$            | $\label{eq:VTXD} \begin{array}{l} \text{Normal mode; dominant;} \\ t < t_{to(dom)TXD;} \\ V_{TXD} = 0V; \ V_{CC} = 4.5V \ to \ 5.5V; \\ R_L = 2240\Omega \end{array}$ | 1.5                | -    | 5                               | v    |

|                                        |                          | Normal mode;<br>V <sub>TXD</sub> =V <sub>IO</sub> ; <sup>備決:大找到引用額。</sup><br>No load                                                                                  | -500               | -    | +50                             | mV   |

|                                        |                          | Standby mode; No load                                                                                                                                                 | -0.2               | -    | +0.2                            | V    |

| Output voltage                         | V <sub>O(rec)</sub>      | Normal mode;<br>V <sub>TXD</sub> =V <sub>I0</sub> ; <sup>備读</sup> !未找到引用額.<br>No load                                                                                 | 2                  | 2.5  | 3                               | V    |

|                                        |                          | Standby mode; No load                                                                                                                                                 | -0.1               | -    | +0.1                            | V    |

| Differential receiver                  | Variation                | Normal mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                                           | 0.5                | -    | 0.9                             | V    |

| threshold voltage                      | V <sub>th(RX)</sub> diff | Standby mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                                          | 0.4                | -    | 1.1                             | V    |

| racaivar racassivo voltoss             | V                        | Normal mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                                           | -4                 | -    | 0.5                             | V    |

| receiver recessive voltage             | Vrec(RX)                 | Standby mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                                          | -4                 | -    | 0.4                             | V    |

**SIT1462Q**

| Parameter                                   | Symbol                   | Condition                                                                                                                                    | Min. | Тур. | Max. | Unit |

|---------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| · · · · ·                                   |                          | Normal mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                  | 0.9  | -    | 9    | V    |

| receiver dominant voltage                   | V <sub>dom(RX)</sub>     | Standby mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                 | 1.1  | -    | 9    | V    |

| differential receiver<br>hysteresis voltage | V <sub>hys(RX)</sub> dif | Normal mode;<br>-12V≤V <sub>CANH</sub> ≤12V;<br>-12V≤V <sub>CANL</sub> ≤12V                                                                  | 80   | -    | -    | mV   |

| short-circuit output current                | I <sub>O(SC)</sub>       | $V_{CANH}$ =-15V to 40V;<br>V <sub>CANL</sub> =-15V to 40V                                                                                   |      | -    | 115  | mA   |

| recessive short-circuit output<br>current   | I <sub>O(SC)rec</sub>    | V <sub>CANH</sub> =-27V to 32V;<br>V <sub>CANL</sub> =-27V to 32V;<br>V <sub>TXD</sub> =V <sub>I0</sub> for t>t <sub>d</sub> (TXD-busrec)end | -5   |      | 5    | mA   |

| leakage current                             | $I_L$                    | $V_{CC}=V_{IO}=0V$ or pins shorted to<br>GND via 47k $\Omega$ ;<br>$V_{CANH}=V_{CANL}=5V$                                                    | -10  |      | 10   | μΑ   |

| input resistance                            | R <sub>i</sub>           | -2V≤V <sub>CANH</sub> ≤7V;<br>-2V≤V <sub>CANL</sub> ≤7V                                                                                      | 25   | 40   | 50   | kΩ   |

| input resistance deviation                  | $	riangle R_i$           | 0V≤V <sub>CANH</sub> ≤5V;<br>0V≤V <sub>CANL</sub> ≤5V                                                                                        | -3   |      | 3    | %    |

| differential input resistance               | R <sub>ID</sub>          | -2V≤V <sub>CANH</sub> ≤7V;<br>-2V≤V <sub>CANL</sub> ≤7V                                                                                      | 50   | 80   | 100  | kΩ   |

| common-mode input<br>capacitance            | $C_{i(cm)}^{(2)}$        |                                                                                                                                              | -    | -    | 40   | pF   |

| differential input capacitance              | $C_{i(diff)}{}^{(2)}$    |                                                                                                                                              | -    | -    | 20   | pF   |

# DYNAMIC CHARACTERISTICS

Unless specified otherwise; all values are tested in recommended operating conditions:  $T_j$ =-40°C~150°C, V<sub>CC</sub>=4.5V~5.5V, V<sub>IO</sub>=1.7V~5.5V (SIT1462Q/3), R<sub>L</sub>=60\Omega.

| Parameter                                 | Symbol                               | Conditions                                              | Min.        | Тур.       | Max.        | Unit |

|-------------------------------------------|--------------------------------------|---------------------------------------------------------|-------------|------------|-------------|------|

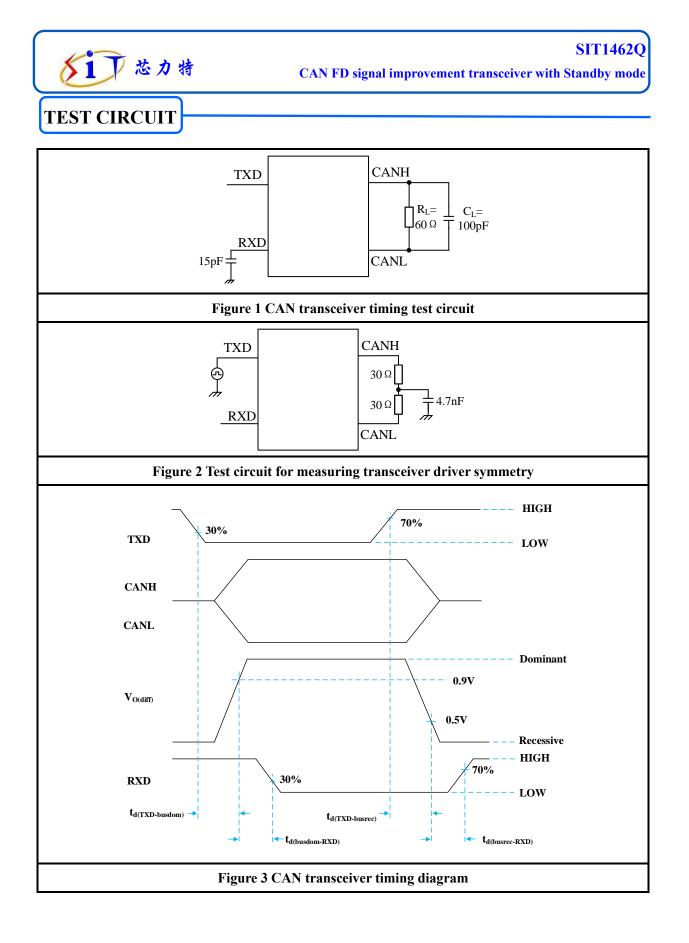

| CAN timing character                      | istics; t <sub>bit(TXD)</sub> ≥1     | 25ns; Figure 1 and Figure 3.                            |             |            |             |      |

| Delay time from TXD<br>to bus dominant    | $t_{d(TXD-busdom)}$                  | Normal mode                                             | -           | -          | 80          | ns   |

| Delay time from TXD<br>to bus recessive   | $t_{d(TXD-busrec)}$                  | Normal mode                                             | -           | -          | 80          | ns   |

| Delay time from bus<br>dominant to RXD    | t <sub>d(busdom-RXD)</sub>           | Normal mode                                             | -           | -          | 110         | ns   |

| Delay time from bus recessive to RXD      | t <sub>d(busrec-RXD)</sub>           | Normal mode                                             | -           | -          | 110         | ns   |

| Delay time from TXD<br>LOW to RXD LOW     | t <sub>d(TXDL-RXDL)</sub>            | Normal mode                                             | -           | -          | 190         | ns   |

| Delay time from TXD<br>HIGH to RXD HIGH   | $t_{d(TXDH-RXDH)}$                   | Normal mode                                             |             |            | 190         | ns   |

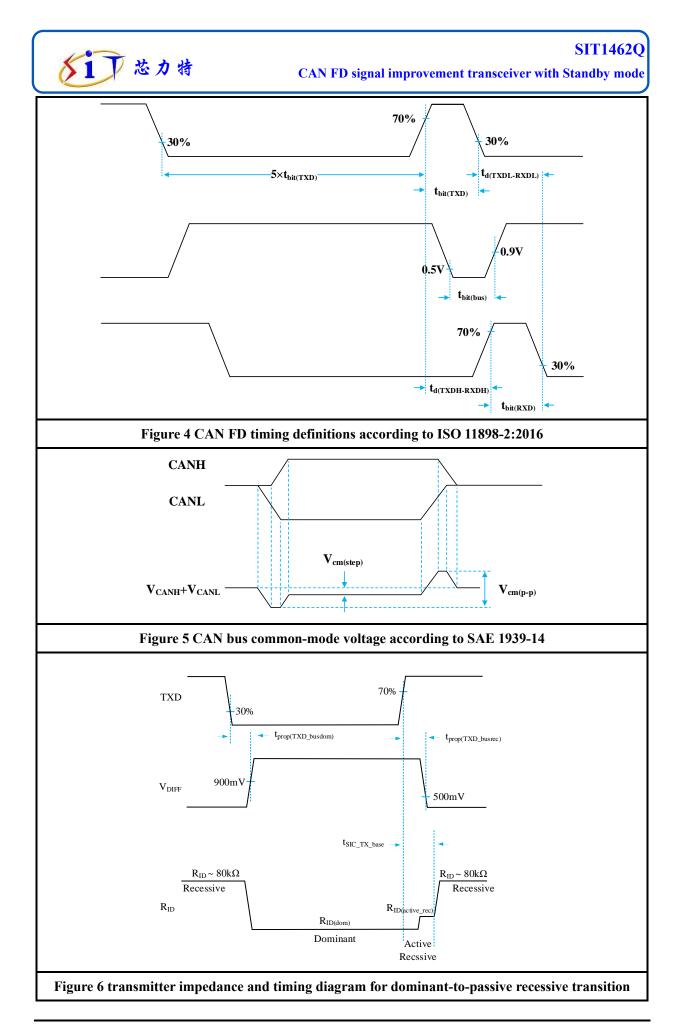

| CAN FD timing characte                    | ristics according                    | to (CiA 601-4:2019); t <sub>bit(TXD)</sub> ≥125ns       | s; Figure 1 | and Figure | e <b>4.</b> |      |

| Signal improvement<br>time                | $t_{\rm SIC_TXD_base}$               |                                                         |             | -          | 530         | ns   |

| Transmitted recessive bit width deviation | $\Delta t_{bit(bus)}$ <sup>(2)</sup> | $\Delta t_{bit(bus)} = t_{bit(bus)} \cdot t_{bit(TXD)}$ | -10         | -          | 10          | ns   |

| Receiver timing symmetry                  | $\Delta t_{\rm rec}^{(2)}$           | $\Delta t_{rec} = t_{bit(RXD)} - t_{bit(bus)}$          | -20         | -          | 15          | ns   |

SIT1462

| Parameter                              | Symbol                               | Conditions                                          | Min.      | Тур.     | Max. | Unit |

|----------------------------------------|--------------------------------------|-----------------------------------------------------|-----------|----------|------|------|

| Received recessive bit width deviation | $\Delta t_{bit(RXD)}$ <sup>(2)</sup> | $\Delta t_{bit(RXD)} = t_{bit(RXD)} - t_{bit(TXD)}$ | -30       | -        | 20   | ns   |

| CAN FD timing charac                   | cteristics accor                     | ding to ISO 11898-2:2016; Figur                     | e 1 and F | igure 4. |      |      |

|                                        |                                      | 2Mbit/s; (t <sub>bit(TXD)</sub> =500ns)             | 480       | -        | 520  | ns   |

| Transmitted recessive<br>bit width     | t <sub>bit(bus)</sub>                | 5Mbit/s; (t <sub>bit(TXD)</sub> =200ns)             | 180       | -        | 210  | ns   |

|                                        |                                      | 8Mbit/s; (t <sub>bit(TXD)</sub> =125ns)             | 115       |          | 135  | ns   |

|                                        |                                      | 2Mbit/s                                             | -65       | -        | 40   | ns   |

| Receiver timing symmetry               | $\Delta t_{rec}$                     | 5Mbit/s                                             | -45       | -        | 15   | ns   |

| <i></i>                                |                                      | 8Mbit/s                                             | -20       |          | 15   | ns   |

|                                        |                                      | 2Mbit/s; (t <sub>bit(TXD)</sub> =500ns)             | 470       | -        | 520  | ns   |

| Bit time on pin RXD                    | $t_{bit(RXD)}$                       | 5Mbit/s; (t <sub>bit(TXD)</sub> =200ns)             | 170       | -        | 220  | ns   |

|                                        |                                      | 8Mbit/s; (t <sub>bit(TXD)</sub> =125ns)             | 95        |          | 145  | ns   |

| TXD dominant time-o                    | ut time                              |                                                     |           |          |      |      |

| TXD dominant time-<br>out time         | t <sub>to(dom)TXD</sub>              | V <sub>TXD</sub> =0V; Normal mode                   | 0.8       | -        | 9    | ms   |

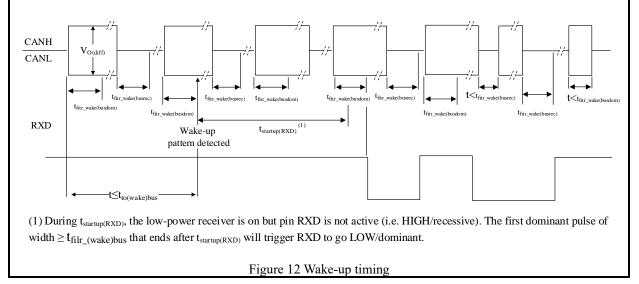

| Bus wake-up times; pi                  | ns CANH and                          | CANL; Figure 12.                                    |           |          |      |      |

| Bus dominant wake-up filter time       | $t_{\rm fitr\_wake(busdom)}$         | Standby mode                                        | 0.5       | -        | 1.8  | μs   |

| Bus recessive wake-up filter time      | $t_{fitr\_wake(busrec)}$             | Standby mode                                        | 0.5       | -        | 1.8  | μs   |

| Bus wake-up time-out<br>time           | t <sub>to(wake)bus</sub>             | Standby mode                                        | 0.8       | -        | 9    | ms   |

| Mode transitions                       |                                      |                                                     |           |          |      |      |

| Mode change transition time            | $t_{t(moch)}$                        |                                                     | -         | _        | 50   | μs   |

| Start-up time                          | t <sub>startup</sub>                 |                                                     | -         | -        | 1.5  | ms   |

| RXD start-up time                      | t <sub>startup(RXD)</sub>            | to Standby mode after wake-up                       | 4         | -        | 50   | μs   |

| Pin STB; IO filter                     |                                      |                                                     |           |          |      |      |

| IO filter time                         | $t_{\mathrm{filter(IO)}}$            |                                                     | 1         |          | 8    | μs   |

| Undervoltage detection                 | 1                                    |                                                     |           |          |      |      |

| Undervoltage detection time            | t <sub>det(uv)</sub>                 | On pin VCC                                          | -         | -        | 50   | μs   |

| Switch-off                             |                                      | On pin VCC; SIT1462Q                                | -         | -        | 50   | μs   |

| undervoltage detection<br>time         | $t_{uvdt(swoff)}$                    | On pin VIO; SIT1462Q/3                              | -         | -        | 50   | μs   |

| Undervoltage recovery time             | $t_{rec(uv)}$                        | On pin VCC                                          | -         | -        | 50   | μs   |

(1)  $V_{IO}\xspace$  only in SIT1462Q/3 version.

(2) Guaranteed by design; not tested in production.

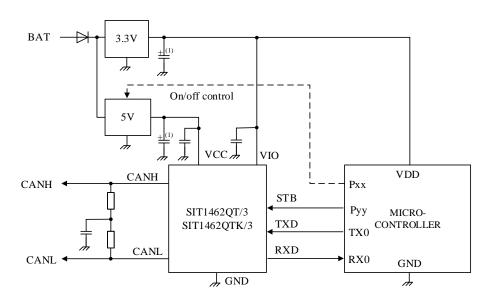

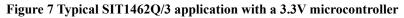

## **APPLICATION INFORMATION**

(1) Optional, depends on regulator.

(1) Optional, depends on regulator.

#### Figure 8 Typical SIT1462Q application with a 5V microcontroller

## ADDITIONAL DESCRIPTION

#### 1 Sketch

SIT1462Q is an interface chip applied between CAN protocol controller and physical bus, features a much tighter bit timing symmetry performance to enable CAN FD communication up to 8 Mbit/s, and has the capability of differential signal transmission between bus and CAN protocol controller. SIT1462Q includes CAN Signal Improvement Capability (SIC), as defined in CiA 601-4. CAN signal improvement significantly reduces signal ringing in a network, allowing reliable CAN FD communication to function in larger topologies. In addition, SIT1462Q features a much tighter number of nodes and stub topologies.

#### 2 Overtemperature protection

The device is protected against overtemperature conditions. If the junction temperature exceeds the shutdown junction temperature,  $T_{j(sd)}$ , the CAN bus drivers are disabled. When the junction temperature drops below  $T_{j(sd)rel}$ , the CAN bus drivers recover once TXD has been reset to HIGH and Normal mode is selected (waiting for TXD to go HIGH prevents output driver oscillation due to small variations in temperature).

#### **3** Undervoltage protection

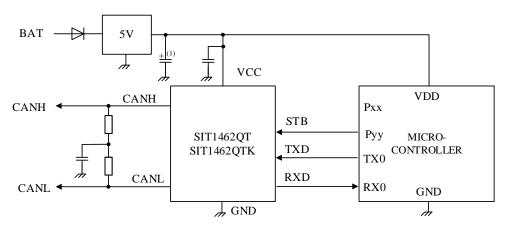

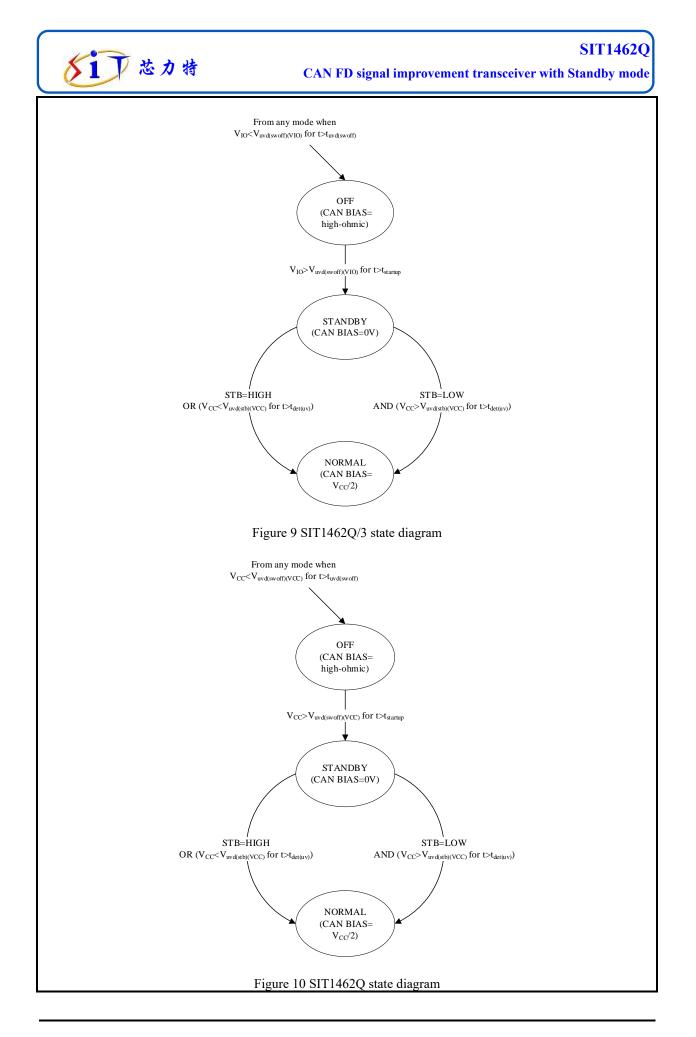

If VCC drops below the standby undervoltage detection threshold ( $V_{uvd(stb)(VCC)}$ ) for  $t_{det(uv)}$ , the transceiver switches to Standby mode. The logic state of pin STB is ignored until VCC has recovered.

In the SIT1462Q/3, if VIO drops below the switch-off undervoltage detection threshold ( $V_{uvd(swoff)(VIO)}$ ) for  $t_{uvd(swoff)}$ , the transceiver switches to Off mode and disengages from the bus (high-ohmic) until VIO has recovered.

In the SIT1462Q, if VCC drops below the switch-off undervoltage detection threshold ( $V_{uvd(swoff)(VCC)}$ ) for  $t_{uvd(swoff)}$ , the transceiver switches to Off mode and disengages from the bus (high-ohmic) until VCC has recovered.

#### 4 Operating modes

SIT1462Q supports three operating modes, Normal, Standby and Off. The operating mode is selected via pin STB. The following table shows the corresponding mode status.

| Mode                | In                   | puts                 |                                | Outputs                        |

|---------------------|----------------------|----------------------|--------------------------------|--------------------------------|

| Widde               | STB                  | TXD                  | CAN driver                     | RXD                            |

|                     |                      | LOW                  | Dominant                       | LOW                            |

| Normal              | LOW                  | HIGH                 | HIGH Recessive                 |                                |

|                     |                      | IIIOII               | Recessive                      | HIGH when bus recessive        |

|                     |                      |                      |                                | Follows BUS when wake-         |

| Standby             | HIGH                 | Х                    | Diagod to ground               | up detected                    |

| Standby             | поп                  | Λ                    | Biased to ground               | HIGH when no wake-up           |

|                     |                      |                      |                                | detected                       |

| Off <sup>(1)</sup>  | Х                    | Х                    | High-ohmic state               | High-ohmic state               |

| ) Off mode is enter | red when the voltage | on pin VIO or pin VO | CC is below the switch-off und | ervoltage detection threshold. |

#### 4.1 Off mode

The SIT1462Q switches to Off mode from any mode when the supply voltage falls below the switch-off undervoltage threshold  $V_{uvd(swoff)}$ .

In Off mode, the pins CAN and RXD are in a high-ohmic state.

#### 4.2 Standby mode

When the supply voltage rises above the switch-off undervoltage detection threshold, the SIT1462Q starts to boot up, triggering an initialization procedure. The SIT1462Q switches to the selected mode after  $t_{starup}$ .

Standby mode is selected when pin STB goes HIGH. In this mode, the transceiver is unable to transmit or receive data and a low-power receiver is activated to monitor the bus for a wake-up pattern. The transmitter and Normal-mode receiver blocks are switched off and the bus pins are biased to ground to minimize system supply current. Pin RXD follows the bus after a wake-up request has been detected.

A transition to Normal mode is triggered when STB is forced LOW.

If the supply voltage is below the Standby undervoltage hysteresis voltage  $V_{uvd(stb)}$  when STB goes LOW, the SIT1462Q will remain in Standby mode.

Pending wake-up events will be cleared and differential data on the bus pins converted to digital data via the low-power receiver and output on pin RXD.

In the SIT1462Q/3, the low-power receiver is supplied from  $V_{IO}$  and can detect CAN bus activity when  $V_{IO}$  is above switch-off undervoltage detection voltage  $V_{uvd(swoff)}$  (even if  $V_{IO}$  is the only available supply voltage).

#### 4.3 Normal mode

A LOW level on pin STB selects Normal mode, provided the supply voltage on pin VCC is above the standby undervoltage detection threshold,  $V_{uvd(std)}$ .

In this mode, the transceiver can transmit and receive data via bus lines CANH and CANL. Pin TXD must be HIGH at least once in Normal Mode before transmission can begin. The differential receiver converts the analog data on the bus lines into digital data on pin RXD. The slopes of the output signals on the bus lines into digital data on pin RXD. The slopes of the output signals on the bus lines into digital data on pin RXD. The slopes of the output signals on the bus lines into digital data on pin RXD. The slopes of the output signals on the bus lines are controlled internally and are optimized in a way that guarantees the lowest possible EME. In order to support high bit rates, especially in CAN FD systems, the Signal Improvement function largely eliminates topology-related reflections and impedance mismatches. In recessive state, the output voltage on the bus pins is  $V_{CC}/2$ .

#### 4.4 Operating modes and gap-free operation

Gap-free operation guarantees defined behavior at all voltage levels. Supply voltage-to-operating mode mapping is detailed in Figure 11 and in the state diagrams (Figure 9 and Figure 10)

|                      |                                              |         |                                    |                                                       | _       |

|----------------------|----------------------------------------------|---------|------------------------------------|-------------------------------------------------------|---------|

|                      | 5.5V - 6V                                    |         |                                    | Fully functional                                      |         |

| Voltage range on VCC | V <sub>CC</sub> operating<br>range(4.5V-5.5V | Off     | Fully functional or<br>off         | Fully functional<br>and characteristics<br>guaranteed |         |

| ltage ran            | $V_{uvd(sb)(VCC)}$ range                     |         | Fully functional or standby or off | Fully functional or standby                           |         |

| Vc                   | -0.3-4V                                      |         | Standby or off                     | Standby                                               |         |

|                      |                                              | -0.3-4V | -0.3-4V                            | V <sub>IO</sub> operating range<br>(2.95V-5.5V        | ۲.۵-۲.۲ |

|                      |                                              |         | Voltage range                      | e on VIO                                              |         |

|                      |                                              |         |                                    |                                                       | _       |

| y functional                                |

|---------------------------------------------|

| y functional<br>haracteristics<br>laranteed |

| functional or<br>standby                    |

| Standby                                     |

| ndby or off                                 |

| Off                                         |

|                                             |

**SIT1462Q**

Figure 11 Supply voltage ranges and gap-free operation

#### 5 Dominant timeout function

A "TXD dominant time-out" timer is started when pin TXD is set LOW. If the LOW state on this pin persists for longer than  $t_{to(dom)TXD}$ , the transmitter is disabled, releasing the bus lines to recessive state. This function prevents a hardware and/or software application failure from driving the bus lines to a permanent dominant state (blocking all network communications). The TXD dominant time-out timer is reset when pin TXD goes HIGH.

#### 6 Remote wake-up

SIT1462Q wakes up from Standby mode when dedicated wake-up pattern is detected on the bus. Wake-up timing is shown in the Figure  $12_{\circ}$

E1 É

CAN FD signal improvement transceiver with Standby mode

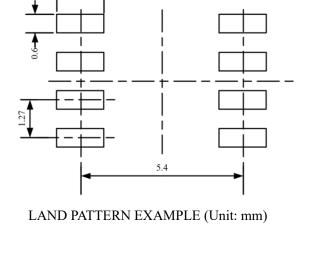

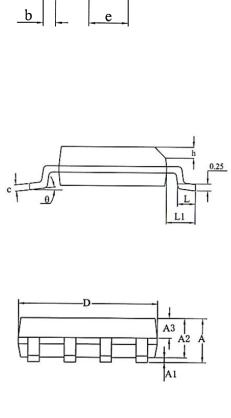

## **SOP8 DIMENSIONS**

| Symbol | Min./mm | Typ./mm | Max./mm |    |

|--------|---------|---------|---------|----|

| А      | -       | -       | 1.75    |    |

| A1     | 0.10    | -       | 0.225   |    |

| A2     | 1.30    | 1.40    | 1.50    |    |

| A3     | 0.60    | 0.65    | 0.70    |    |

| b      | 0.39    | -       | 0.47    |    |

| D      | 4.80    | 4.90    | 5.00    |    |

| Е      | 5.80    | 6.00    | 6.20    |    |

| E1     | 3.80    | 3.90    | 4.00    |    |

| е      |         | 1.27BSC |         |    |

| L      | 0.50    | -       | 0.80    |    |

| L1     |         | 1.05REF |         |    |

| с      | 0.20    | -       | 0.24    |    |

| θ      | 0°      | -       | 8°      | c_ |

Ŧ

4

51 芯力特

1 芯力特

## **DFN3\*3-8 DIMENSIONS**

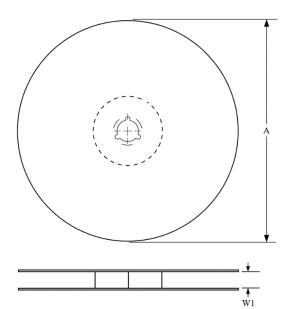

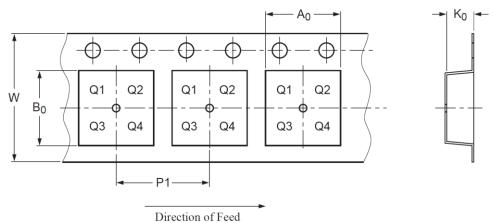

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| К0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### PIN1 is in quadrant 1

| Package<br>Type | Reel<br>Diameter<br>A (mm) | Tape<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) |

|-----------------|----------------------------|--------------------------|------------|------------|------------|------------|-----------|

| SOP8            | 330±1                      | 12.4                     | 6.60±0.1   | 5.30±0.10  | 1.90±0.1   | 8.00±0.1   | 12.00±0.1 |

| DFN3*3-8        | 329±1                      | 12.4                     | 3.30±0.1   | 3.30±0.1   | 1.10±0.1   | 8.00±0.1   | 12.00±0.3 |

# ORDERING INFORMATION

| Type number  | Package  | Packing       |

|--------------|----------|---------------|

| SIT1462QT/3  | SOP8     | Tape and reel |

| SIT1462QT    | SOP8     | Tape and reel |

| SIT1462QTK/3 | DFN3*3-8 | Tape and reel |

| SIT1462QTK   | DFN3*3-8 | Tape and reel |

SOP8 is packed with 2500 pieces/disc in braided packaging; Leadless DFN3\*3-8 is packed with 6000 pieces/disc in braided packaging.

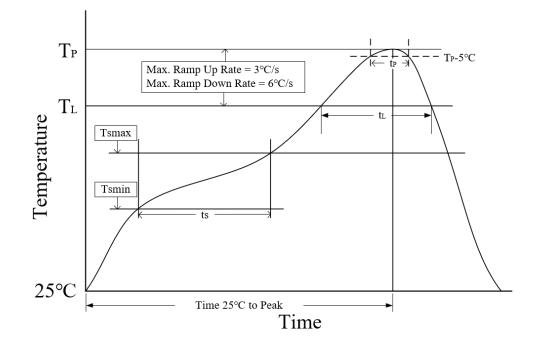

## **REFLOW SOLDERING**

| Parameter                                                   | Lead-free soldering conditions |

|-------------------------------------------------------------|--------------------------------|

| Ave ramp up rate $(T_L \text{ to } T_P)$                    | 3 °C/second max                |

| Preheat time ts ( $T_{smin}$ =150 °C to $T_{smax}$ =200 °C) | 60-120 seconds                 |

| Melting time $t_L(T_L=217 \text{ °C})$                      | 60-150 seconds                 |

| Peak temp T <sub>P</sub>                                    | 260-265 °C                     |

| 5 °C below peak temperature t <sub>P</sub>                  | 30 seconds                     |

| Ave cooling rate $(T_P \text{ to } T_L)$                    | 6 °C/second max                |

| Normal temperature 25°C to peak temperature $T_P$ time      | 8 minutes max                  |

#### Important statement

SIT reserves the right to change the above-mentioned information without prior notice.

## **REVISION HISTORY**

| Version number | Data sheet status | Revision date  |

|----------------|-------------------|----------------|

| V1.0           | Initial version.  | September 2024 |