# SKHI 24 .

## Hybrid Dual IGBT Driver

## **SKHI 24**

**Preliminary Data**

## **Features**

- · Dual driver for halfbridge **IGBT** modules

- For 1700 V IGBT

- · Function compatible to SKHI 22B

- 5 V input level

- CMOS compatible inputs

- · Short circuit protection by V<sub>CE</sub> monitoring and switch off

- Drive interlock top/bottom

- · Isolation by transformers

- Supply undervoltage protection (13 V)

- · Error latch/output

## **Typical Applications**

- Driver for IGBT and MOSFET modules in bridge circuits in choppers, inverter drives, UPS and welding inverters

- DC bus voltage up to 1200 V

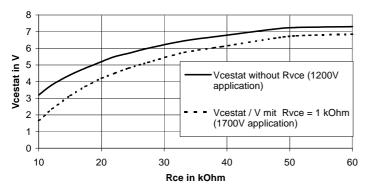

$^{1)}$  At R\_{CE} = 18 kΩ, C\_{CE} = 330 pF  $^{2)}$  At R\_{CE} = 36 k $\Omega,~C_{CE}$  = 470 pF,  $R_{VCE} = 1 \ k\Omega$

2

| <b>Absolute Maximum Ratings</b> $T_{case} = 25$ °C, unless otherwise specified |                                                    |           |       |  |  |

|--------------------------------------------------------------------------------|----------------------------------------------------|-----------|-------|--|--|

| Symbol                                                                         | Conditions                                         | Values    | Units |  |  |

|                                                                                |                                                    |           |       |  |  |

| Vs                                                                             | Supply voltage prim.                               | 18        | V     |  |  |

| V <sub>iH</sub>                                                                | Input signal volt. (High)                          | 5 + 0,3   | V     |  |  |

| I <sub>outPEAK</sub>                                                           | Output peak current                                | 15        | Α     |  |  |

| I <sub>outAVmax</sub>                                                          | Output average current (max.)                      | 80        | mA    |  |  |

| f <sub>max</sub>                                                               | max. switching frequency                           | 50        | kHz   |  |  |

| V <sub>CE</sub>                                                                | Collector emitter voltage sense<br>across the IGBT | 1700      | V     |  |  |

| dv/dt                                                                          | Rate of rise and fall of voltage secondary         | 50        | kV/μs |  |  |

|                                                                                | to primary side                                    |           |       |  |  |

| VisollO                                                                        | Isolation test voltage                             | 4000      | V     |  |  |

|                                                                                | input-output (2 sec. AC)                           |           |       |  |  |

| V <sub>isol12</sub>                                                            | Isolation test voltage output 1 -                  | 1500      | V     |  |  |

| V ISUITZ                                                                       | output 2                                           | 1000      | ľ     |  |  |

|                                                                                | (2 sec. AC)                                        |           |       |  |  |

| R <sub>Gonmin</sub>                                                            | Minimum rating for R <sub>Gon</sub>                | 1,5       | Ω     |  |  |

| R <sub>Goffmin</sub>                                                           | Minimum rating for R <sub>Goff</sub>               | 1,5       | Ω     |  |  |

| Q <sub>out/pulse</sub>                                                         | Max. rating for output charge per                  | 5         | μC    |  |  |

| ∝out/puise                                                                     | pulse                                              | 5         |       |  |  |

| T <sub>op</sub>                                                                | Operating temperature                              | - 25 + 85 | C     |  |  |

| T <sub>stg</sub>                                                               | Storage temperature                                | - 40 + 85 | C     |  |  |

| Symbol         Conditions         min.         typ.         max.         Units           Vs         Supply current primary side (no load)         14,4         15         15,6         V           Supply current primary side (operation)         Input signal voltage on / off         100         550         MA           Vi-         Input treshold voltage (High)         3,4         3,8         4,1         V           Vir-         Input treshold voltage output         1,5         1,9         2,2         V           Rin         Unput resistance         2,2         V         3,3         kΩ           VG(off)         Turn-off gate voltage output         -8         V         22         kΩ           Role         Internal gate-emitter resistance         22         kΩ         MHz           Isolo         Asic system switching frequency         8         MHz         1,25         μs           Iquifino         Input-output turn-off propagation time         1,2         μs         0,85         1         1,25         μs           VCEstat         Coupling capacitance primary secondary         1,8         10°         F         10°         15         20x57x         11°         10°         10°         10° | Characteri                                                                                                                                                   | stics $T_{case} = 25^{\circ}C_{s}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | unles                              | s otherv                                                                              | vise sp                           | ecified                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------|

| $      I_{SO} \qquad \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Symbol                                                                                                                                                       | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | min.                               | typ.                                                                                  | max.                              | Units                                 |

| $ \begin{array}{c c} V_{CEstat} & \text{Reference voltage for } V_{CE}\text{-monitoring} & 5^{1)}/6^{2)} & 10 & V \\ \hline C_{ps} & \text{Coupling capacitance primary secondary} & 18 & pF \\ \text{MTBF} & \text{Mean Time Between Failure } T_a = 40^{\circ}\text{C} & 1,6 & 10^{6} \text{ h} \\ \hline m & \text{weight} & 115 & g \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $V_{S}$ $I_{SO}$ $V_{i}$ $V_{iT+}$ $V_{iT-}$ $R_{in}$ $V_{G(on)}$ $V_{G(off)}$ $R_{GE}$ $f_{ASIC}$ $t_{d(on)IO}$ $t_{d(off)IO}$ $t_{d(err)}$ $t_{pERRRESET}$ | Supply voltage primary side<br>Supply current primary side (no load)<br>Supply current primary side (operation)<br>Input signal voltage on / off<br>Input threshold voltage (High)<br>Input threshold voltage (Low)<br>Input resistance<br>Turn-on gate voltage output<br>Turn-off gate voltage output<br>Internal gate-emitter resistance<br>Asic system switching frequency<br>Input-output turn-on propagation time<br>Input-output turn-off propagation time<br>Error input-output propagation time<br>Error reset time | 14,4<br>3,4<br>1,5<br>0,85<br>0,85 | 15<br>100<br>5 / 0<br>3,8<br>1,9<br>3,3<br>+15<br>-8<br>22<br>8<br>1<br>1<br>1<br>0,6 | 15,6<br>550<br>4,1<br>2,2<br>1,25 | > mA<br>mA > > > Ω<br>MHz<br>μs<br>μs |

| MMN.Datasheeth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>CEstat</sub><br>C <sub>ps</sub><br>MTBF<br>m                                                                                                          | Reference voltage for $V_{CE}$ -monitoring<br>Coupling capacitance primary secondary<br>Mean Time Between Failure $T_a = 40$ °C<br>weight                                                                                                                                                                                                                                                                                                                                                                                   |                                    | 18<br>1,6<br>115                                                                      |                                   | V<br>pF<br>10 <sup>6</sup> h<br>g     |

| table 11-11-2005 © by SEMIKRON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tabla                                                                                                                                                        | MMM.De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2005                               | neet                                                                                  |                                   |                                       |

## **External Components**

| Component          | Function                                                                                     |       | Recommended Value                                              |

|--------------------|----------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------|

| R <sub>CE</sub>    | Reference voltage for V <sub>CE</sub> -monitoring                                            |       | 10kΩ < R <sub>CE</sub> < 100kΩ                                 |

|                    | $V_{CEstat}(V) = \frac{10 \cdot R_{CE}(k\Omega)}{10 + R_{CE}(k\Omega)} - 1.4$                | (1)   | 18kΩ for SKM XX 123 (1200V)<br>36kΩ for SKM XX 173 (1700V)     |

|                    | with $R_{VCE} = 1k\Omega$ (1700V IGBT):                                                      |       |                                                                |

|                    | $V_{CEstat}(V) = \frac{10 \cdot R_{CE}(k\Omega)}{10 + R_{CE}(k\Omega)} - 1.8$                | (1.1) |                                                                |

| C <sub>CE</sub>    | Inhibit time for $V_{CE}$ - monitoring                                                       |       | C <sub>CE</sub> < 2,7nF                                        |

|                    | $t_{min} = \tau_{CE} \cdot \ln \left[ \frac{15 - V_{CEstat}(V)}{10 - V_{CEstat}(V)} \right]$ | (2)   | 0,33nF for SKM XX 123 (1200V)<br>0,47nF for SKM XX 173 (1700V) |

|                    | $\tau_{CE}(\mu s) = C_{CE}(nF) \cdot \frac{10 \cdot R_{CE}(k\Omega)}{10 + R_{CE}(k\Omega)}$  | (3)   | 0,5μs < t <sub>min</sub> < 10μs                                |

| R <sub>VCE</sub>   | Collector series resistance for 1700V<br>IGBT-operation                                      |       | 1kΩ / 0,4W                                                     |

| R <sub>ERROR</sub> | Pull-up resistance at error output<br>$\frac{U_{Pull-Up}}{R_{ERROR}} < 15 \text{mA}$         |       | 1kΩ < R <sub>ERROR</sub> < 10kΩ                                |

| R <sub>GON</sub>   | Turn-on speed of the IGBT <sup>3)</sup>                                                      |       | $R_{GON} > 1.5\Omega$                                          |

| R <sub>GOFF</sub>  | Turn-off speed of the IGBT <sup>4)</sup>                                                     |       | $R_{GOFF} > 1,5\Omega$                                         |

<sup>3)</sup> Higher resistance reduces free-wheeling diode peak recovery current, increases IGBT turn-on time.

<sup>4)</sup> Higher resistance reduces turn-off peak voltage, increases turn-off time and turn-off power dissipation

### PIN array

P14

P15

P20

P16, P17 P18, P19, free

TDT2

SELECT

Fig. 6 shows the pin arrays. The input side (primary side) comprises 10 inputs, forming the interface to the control circuit (see fig.1).

The output side (secondary side) of the hybrid driver shows two symmetrical groups of pins with 5 outputs, each forming the interface to the power module. All pins are designed for a grid of 2,54 mm in two rows.

| PIN No.           | Designation      | Explanation                                                                          |

|-------------------|------------------|--------------------------------------------------------------------------------------|

| P1                | Shield           | internally connected to GND                                                          |

| P2                | V <sub>IN2</sub> | switching signal input 2 (BOTTOM switch); positive 5V logic                          |

| P3                | V <sub>IN1</sub> | switching signal input 1 (TOP switch); positive 5V logic                             |

| P4, P5,<br>P6, P7 | free             | not wired                                                                            |

| P8                | /ERROR           | error output, low = error; open collector output; max 30V / 15mA                     |

| P9, P10           | GND/0V           | ground                                                                               |

| P11, P12          | V <sub>S</sub>   | + 15V ± 4% voltage supply                                                            |

| P13               | TDT1             | signal input for digital adjustment of locking time; to be switched by bridge to GND |

bridge to GND

to GND

not wired

## Primary side PIN array

ATTENTION: The contactor tracks of the digital input signals P13/ P14/ P15 must not be longer than 20 mm to avoid interferences, if no bridges are connected.

signal input for digital adjustment of locking time; to be switched by

signal input for inhibiting locking function; to be connected by bridge

## Secondary side PIN array

| PIN No. | Designation       | Explanation                                                             |

|---------|-------------------|-------------------------------------------------------------------------|

| ST1     | G <sub>OFF1</sub> | gate 1 R <sub>OFF</sub> output (TOP switch)                             |

| ST2     | G <sub>ON1</sub>  | gate 1 R <sub>ON</sub> output (TOP switch)                              |

| ST3     | E1                | emitter output IGBT 1 (TOP switch)                                      |

| ST4     | C <sub>CE1</sub>  | reference voltage adjustment with $R_{CE}$ and $C_{CE}$ (TOP switch)    |

| ST9     | V <sub>CE1</sub>  | collector output IGBT 1 (TOP switch)                                    |

| SB1     | G <sub>OFF2</sub> | gate 2 R <sub>OFF</sub> output (BOTTOM switch)                          |

| SB2     | G <sub>ON2</sub>  | gate 2 R <sub>ON</sub> output (BOTTOM switch)                           |

| SB3     | E2                | emitter output IGBT 2 (BOTTOM switch)                                   |

| SB4     | C <sub>CE2</sub>  | reference voltage adjustment with $R_{CE}$ and $C_{CE}$ (BOTTOM switch) |

| SB9     | V <sub>CE2</sub>  | collector output IGBT 2 (BOTTOM switch)                                 |

ATTENTION: The connector leads to the power module should be as short as possible.

input1

(TOP)

input2

(BOTTOM)

GND/OV

**GND/OV**

<sup>~</sup>\*Error

Rerror

TDT2

TDT1\_P13

SELECT P15

**VS** <sup>C</sup>

input

100

100

P2

**P9**

P10

P14

**P8**

้ ร

P11, P12

3k2

工 3k2

-input buffer -short pulse

supression

-interlock -deadtime

-pulse shaper

**P3**

V<sub>iT</sub>

V<sub>iB</sub> ↔

\* When SKHI 24 is driving 1700V IGBTs, a  $1k\Omega / 0.4W R_{VCE}$ -resistor must be connected in series to the V<sub>CE</sub>-input.

\*\* The V<sub>CE</sub>-terminal is to be connected to the IGBT collector C. If the V<sub>CE</sub>-monitoring is not used, connect ST3 to ST9 or SB3 to SB9 respectively.

Isolation

S

V S over

current

Power driver

Power

driver

secondary side

over

current

ST9 V<sub>CE</sub> \*\*

ST4

ST2

ST1

ST3

SB9

SB4

SB2

SB3

SB3

$R_{on}$

Roff

$V_{CE}$  \*\*

R on

$R_{off}$

output

RVCE

4

\* RVCE

R<sub>CE</sub> C<sub>CE</sub>

6

output1

(TOP)

output2

(BOTTOM)

木

木

**SEMITRANS**

**IGBT-Module**

LOAD

-Vs monitor

intearated in ASIC

primary side

-Error monitor

-Error memory

#### **SEMIDRIVER**<sup>™</sup>

### **SKHI 24**

#### Hybrid dual drivers

The driver generation SKHI 24 is supplementing the SKHI 21/22 and is suitable for all available medium and high power range IGBT and MOSFETs. It can be said that the SKHI 24 is a function-compatible further developed SKHI 22B. It is recommended to use the SKHI 24 for any new design.

#### **General description**

The new driver generation SKHI 22A/B, SKHI 21A and also SKHI 24 are hybrid components which may directly be mounted to the PCB.

All devices necessary for driving, voltage supply, error monitoring and potential separation are integrated in the driver. In order to adapt the driver to the used power module, only very few additional wiring will be necessary.

The forward voltage of the IGBT is detected by an integrated short-circuit protection, which will turn off the module when a certain threshold is exceeded.

In case of short-circuit or too low supply voltage the integrated error memory is set and an error signal is generated.

The driver is connected to a controlled + 15 V-supply voltage. The input signal level is 0/5 V.

## Technical explanations<sup>1</sup>

# Description of the circuit block diagram and the functions of the driver

The block diagram (fig.1) shows the inputs of the driver (primary side) on the left side and the outputs (secondary side) on the right.

## The following functions are allocated to the primary side:

**Input-Schmitt-trigger**, positive logic (input high = IGBT on). It is also possible to drive the circuit input with 15 V logic, but a 6.8 k $\Omega$  resistor has to be connected in series with the input pin (and the internal 100  $\Omega$  resistor).

#### Interlock circuit and deadtime generation of the IGBT

If one IGBT is turned on, the other IGBT of a halfbridge cannot be switched. Additionally, a digitally adjustable interlocking time is generated by the driver (see fig. 2), which has to be longer than the turn-off delay time of the IGBT. This is to avoid that one IGBT is turned on before the other one is not completely discharged. This protection-function may be neutralized by switching the select input (pin15) (see fig. 2). fig. 2 documents possible interlock-times. "High" value can be achieved with no connection and connection to 5 V as well.

| P15 ;<br>SELECT | P13 ;<br>TDT1 | P14 ;<br>TDT2 | interlock time<br>t <sub>TD</sub> /μs |

|-----------------|---------------|---------------|---------------------------------------|

| open / 5V       | GND           | GND           | 1,3                                   |

| open / 5V       | GND           | open / 5V     | 2,3                                   |

| open / 5V       | open / 5V     | GND           | 3,3                                   |

| open / 5V       | open / 5V     | open / 5V     | 4,3                                   |

| GND             | Х             | Х             | no interlock                          |

Fig. 2 SKHI 24 - Selection of interlock-times: "High"-level can be achieved by no connection or connecting to 5 V.

#### Short pulse suppression

The integrated short pulse suppression avoids very short switching pulses at the power semiconductor caused by high-frequency interference pulses at the driver input signals. Switching pulses shorter than 500ns are suppressed and not transmitted to the IGBT.

#### Power supply monitoring (V<sub>S</sub>)

A controlled 15 V-supply voltage is applied to the driver. If it falls below 13 V, an error is monitored and the error output signal switches to low level.

#### Error monitoring and error memory

The error memory is set in case of under-voltage or short-circuit of the IGBTs. In case of short-circuit, an error signal is transmitted by the  $V_{CE}$ -input via the pulse transformers to the error memory. The error memory will lock all switching pulses to the IGBTs and trigger the error output (P8) of the driver. The error output consists of an open collector transistor, which directs the signal to earth in case of error. SEMIKRON recommends the user to provide for a pull-up resistor directly connected to the error evaluation board and to adapt the error level to the desired signal voltage this way. The open collector transistor may be connected to max. 30 V / 15 mA. If several SKHI 24 are used in one device, the error terminals may also be paralleled.

The error memory may only be reset, if no error is pending and both cycle signal inputs are set to low for > 12  $\mu$ s at the same time.

#### Pulse transformer set

The transformer set consists of two pulse transformers. One of them is used bidirectional for turn-on and turn-off signals of the IGBT and the error feedback between primary and secondary side, the other one for the DC/DC-converter. The DC/DC-converter serves as potential-separation and power supply for the two secondary sides of the driver. The isolation voltage is 4000 VAC.

The secondary side consists of two sym-metrical driver switches integrating the following components:

#### Supply voltage

The voltage supply consists of a rectifier, a capacitor, a voltage controller for -8 V and +15 V and a + 10 V reference voltage.

The following descriptions apply to the use of the hybrid driver for IGBTs as well as for power MOSFETs. For the reason of shortness, only IGBTs will be mentioned in the following. The designations "collector" and "emitter" will refer to IGBTs, whereas for the MOSFETs "drain" and "source" are to be read instead.

#### Gate driver

The output transistors of the power drivers are MOSFETs. The sources of the MOSFETs are separately connected to external terminals in order to provide setting of the turn-on and turn-off speed by the external resistors R<sub>ON</sub> and R<sub>OFF</sub>. Do not connect the terminals ST1 with ST2 and SB1 with SB2, respectively. The IGBT is turned on by the driver at +15V by R<sub>ON</sub> and turned off at – 8 V by R<sub>OFF</sub>. R<sub>ON</sub> and R<sub>OFF</sub> may not chosen below 1,5  $\Omega$ . In order to ensure locking of the IGBT even when the driver supply voltage is turned off, a 22 k $\Omega$ -resistor versus the emitter output (E) has been integrated at output G<sub>OFF</sub>.

#### V<sub>CE</sub>-monitoring

The V<sub>CE</sub>-monitoring controls the collector-emitter voltage  $V_{CE}$  of the IGBT during its on-state.  $V_{CE}$  is internally limited to 10 V. If the reference voltage V<sub>CEref</sub> is exceeded, the IGBT will be switched off and an error is indicated. The reference voltage V<sub>CEref</sub> may dynamically be adapted to the IGBTs switching behaviour. Immediately after turn-on of the IGBT, a higher value is effective than in the steady state. This value will, however, be reset, when the IGBT is turned off. V<sub>CEstat</sub> is the steady-state value of V<sub>CEref</sub> and is adjusted to the required maximum value for each IGBT by an external resistor  $\mathsf{R}_{\mathsf{CE}}$  to be connected between the terminals C<sub>CE</sub> (ST4/SB4) and E (ST3/SB3). It may not exceed 10 V. The time constant for the delay of V<sub>CEref</sub> may be increased by an external capacitor C<sub>CE</sub>, which is connected in parallel to R<sub>CE</sub>. It controls the time t<sub>min</sub> which passes after turn-on of the IGBT before the V<sub>CE</sub>-monitoring is activated. This makes possible any adaptation to the switching behavior of any of the IGBTs. After t<sub>min</sub> has passed, the V<sub>CE</sub>-monitoring will be triggered as soon as  $V_{CE} > V_{CEref}$  and will turn off the IGBT.

## External components and possible adjustments of the hybrid driver

Fig. 1 shows the required external components for adjustment and adaptation to the power module.

#### V<sub>CE</sub> - monitoring adjustment

The external components R<sub>CE</sub> and C<sub>CE</sub> are applied for adjusting the steady-state threshold and the short-circuit monitoring dynamic. R<sub>CE</sub> and C<sub>CE</sub> are connected in parallel to the terminals C<sub>CE</sub> (ST4/SB4) and E (ST3/SB3)

Fig. 3 V<sub>CEstat</sub> in dependence of R<sub>CE</sub>

Dimensioning of  $R_{CE}$  and  $C_{CE}$  can be done in three steps:

- Calculate the maximum forward voltage from the datasheet of the used IGBT and determine V<sub>CEstat</sub>.

- 2. Calculate approximate value of R<sub>CE</sub> according to equation (1) or (1.1) from  $V_{CEstat}$  or determine  $R_{CE}$  by using fig. 3.

- 3. Determine t<sub>min</sub> and calculate C<sub>CE</sub> according to equations (2) and (3).

Typical values are

for 1200V IGBT:  $V_{CEstat} = 5 V$ ;  $t_{min} = 1,45 \mu s$ ,

$R_{CE} = 18 \text{ k}\Omega, \text{ } C_{CE} = 330 \text{ pF}$

for 1700V IGBT:  $V_{CEstat} = 6 V$ ;  $t_{min} = 3 \mu s$ ,

$R_{CE} = 36 \text{ k}\Omega, C_{CE} = 470 \text{ pF}$

## Adaptation to 1700 V IGBT

When using 1700 V IGBTs it is necessary to connect a 1 k $\Omega$  / 0,4 W adaptation resistor between the V<sub>CE</sub>-terminal (ST9/ SB9) and the respective collector.

#### Adaptation to error signal level

An open collector transistor is used as error terminal, which, in case of error, leads the signal to earth. The signal has to be adapted to the evaluation circuit voltage level by means of an pull-up resistor. The maximum load applied to the transistor shall be 30 V / 15 mA.

#### IGBT switching speed adjustment

The IGBT switching speed may be adjusted by the resistors R<sub>ON</sub> and R<sub>OFF</sub>. By increasing R<sub>ON</sub> the turn-on speed will decrease. The reverse peak current of the free-wheeling diode will diminish. SEMIKRON recommends to adjust R<sub>ON</sub> to a level that will keep the turn-on delay time  $t_{d(on)}$  of the IGBT < 1 µs. By increasing R<sub>OFF</sub> the turn-off speed of the IGBT will decrease. The inductive peak over voltage during turn-off will diminish.

The minimum gate resistor value for R<sub>OFF</sub> and R<sub>ON</sub> is 1,5  $\Omega$ . Typical values for R<sub>ON</sub> and R<sub>OFF</sub> recommended by SEMIKRON are given in fig. 4.

#### Interlock time adjustment

Fig. 2 shows the possible interlocking times between output1 and output2. Interlocking times are adjusted by connecting the terminals TDT1 (P13), TDT2 (P14) and SELECT (P15) either to earth/ GND (P16) according to the required function or by leaving them open.

| SK-IGBT-Modul | ${\sf R}_{\sf Gon} \ \Omega$ | $\begin{array}{c} R_{Goff} \\ \Omega \end{array}$ | С <sub>СЕ</sub><br>pF | R <sub>CE</sub><br>kΩ | $\begin{array}{c} R_{VCE} \\ k\Omega \end{array}$ |

|---------------|------------------------------|---------------------------------------------------|-----------------------|-----------------------|---------------------------------------------------|

| SKM 50GB123D  | 22                           | 22                                                | 330                   | 18                    | 0                                                 |

| SKM 75GB123D  | 22                           | 22                                                | 330                   | 18                    | 0                                                 |

| SKM 100GB123D | 15                           | 15                                                | 330                   | 18                    | 0                                                 |

| SKM 145GB123D | 12                           | 12                                                | 330                   | 18                    | 0                                                 |

| SKM 150GB123D | 12                           | 12                                                | 330                   | 18                    | 0                                                 |

| SKM 200GB123D | 10                           | 10                                                | 330                   | 18                    | 0                                                 |

| SKM 300GB123D | 8,2                          | 8,2                                               | 330                   | 18                    | 0                                                 |

| SKM 400GA123D | 6,8                          | 6,8                                               | 330                   | 18                    | 0                                                 |

|               |                              |                                                   |                       |                       |                                                   |

| SKM 75GB173D  | 15                           | 15                                                | 470                   | 36                    | 1                                                 |

22-08-2003 © by SEMIKRON

| SKM 100GB173D | 12  | 12  | 470 | 36 | 1 |

|---------------|-----|-----|-----|----|---|

| SKM 150GB173D | 10  | 10  | 470 | 36 | 1 |

| SKM 200GB173D | 8,2 | 8,2 | 470 | 36 | 1 |

Fig. 4 Typical values for external components

A typical interlocking time value is 3,25  $\mu s$  (P14 = GND; P13 and P15 open).

**ATTENTION:** If the terminals TDT1, TDT2 and SELECT are not connected, eventually connected track on PC-board may not be longer than 20 mm in order to avoid interference.

SEMIKRON recommends to start-up operation using the values recommended by SEMIKRON and to optimize the values gradually according to the IGBT switching behaviour and overvoltage peaks within the specific circuitry.

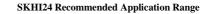

#### Driver performance and application limits

The drivers are designed for application with halfbridges and single modules with a maximum gate charge  $Q_{GE}$  < 5  $\mu C.$

The charge necessary to switch the IGBT is mainly depending on the IGBT's chip size, the DC-link voltage and the gate voltage.

This correlation is also shown in the corresponding module datasheet curves.

It should, however, be considered that the SKHI 24 is turned on at + 15 V and turned off at - 8 V. Therefore, the gate voltage will change by 23 V during each switching cycle.

Unfortunately, most datasheets do not indicate negative gate voltages. In order to determine the required charge, the upper leg of the charge curve may be prolonged to + 23 V for an approximately determination of approximate charge per switch.

The medium output current of the driver is determined by the switching frequency and the gate charge. For the SKHI 24 the maximum medium output current is  $lout_{AVmax} < \pm 80$  mA.

The maximum switching frequency  $f_{MAX}$  may be calculated with the following formula, the maximum value however being 50 kHz due to switching losses:

$$f_{MAX}(kHz) = \frac{8 \cdot 10^4}{Q_{GE}(nC)}$$

Fig. 5 shows the recommended maximum switching frequencies for SEMIKRON Semitrans IGBT modules.

Fig. 5 Maximum switching frequency in dependence of rated current @ 25℃ heatsink temperature.

#### **Further application notes**

The CMOS-inputs of the hybrid driver are extremely sensitive to overvoltage. Voltages higher than  $V_S$  + 0,3 V or below – 0,3 V may destroy these inputs. Therefore, control signal overvoltages exceeding the above values have to be avoided.

Please provide for static discharge protection during handling. As long as the hybrid driver is not completely assembled, the input terminals have to be short-circuited. Persons working with CMOS-devices have to wear a grounded bracelet. Any synthetic floor coverings must not be statically chargeable. Even during transportation the input terminals have to be short-circuited using, for example, conductive rubber. Worktables have to be grounded. The same safety requirements apply to MOSFET- and IGBT-modules!

The connecting leads between hybrid driver and the power module should be as short as possible, the driver leads should be twisted.

Any parasitic inductances within the DC-link have to be minimized. Overvoltages may be absorbed by C- or RCD-snubbers between the main terminals for PLUS and MINUS of the power module.

When first operating a newly developed circuit, SEMIKRON recommends to apply low collector voltage and load current in the beginning and to increase these values gradually, observing the turn-off behaviour of the free-wheeling diode and the turn-off voltage spikes generated accross the IGBT. An oscillographic control will be necessary. In addition to that the case temperature of the module has to be monitored. When the circuit works correctly under rated operation conditions, short-circuit testing may be done, starting again with low collector voltage.

It is important to feed any errors back to the control circuit and to switch off the device immediately in such events. Repeated turn-on of the IGBT into a short circuit with a high frequency may destroy the device.

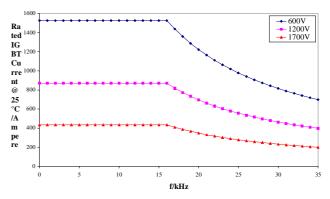

## **Mechanical fixing on PCB**

## Bottom View

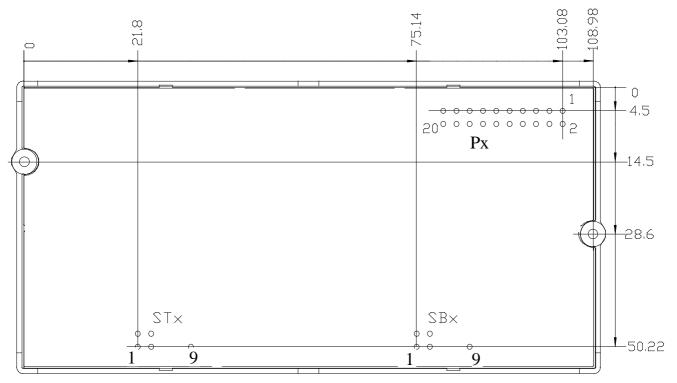

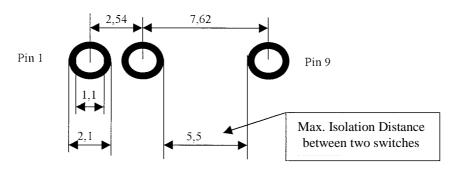

Fig. 6 Dimensional drawing and PIN array

View: bottom side L x B x H: 113,8 x 56,7 x 20 [mm] grid of connector pins; gaps of connector pins: RM 2,54 mm Pin dimensions: 0,64 mm x 0,64 mm; Length 3,2 mm

Fig. 7 Dimensions in [mm] for solder pads (as a proposal for a design) and solder pad gaps (partial drawing) with maximum distance between two switches

This technical information specifies devices but promises no characteristics. No warranty or guarantee expressed or implied is made regarding delivery, performance or suitability.